# **Device Features**

- Fully Qualified Bluetooth system

- Bluetooth v1.2 Specification Compliant

- Kalimba DSP Open Platform Co-Processor

- Full Speed Bluetooth Operation with Full Piconet Support

- Scatternet Support

- Low Power 1.8V Operation

- 10 x 10 x 1.4mm 96-ball LFBGA Package

- Minimum External Components

- Integrated 1.8V regulator

- Dual UART Ports

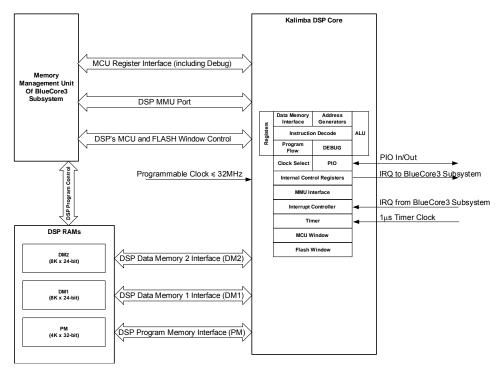

- 16-bit Stereo Audio CODEC

- I<sup>2</sup>S and SPDIF Interfaces

- RF 'Plug 'n' Go' package

- RoHS Compliant

# **General Description**

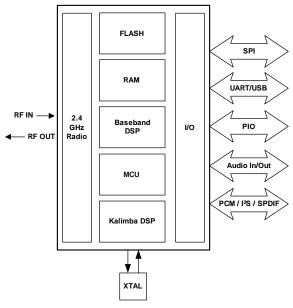

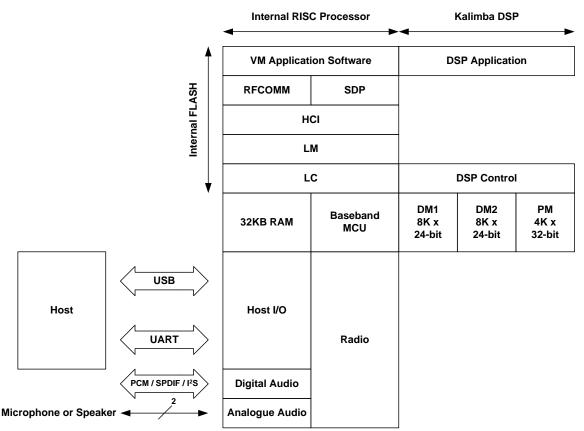

BlueCore3-Multimedia is a single chip radio and baseband IC for Bluetooth 2.4GHz systems.

BC358239A contains 8Mbit of internal Flash memory. When used with the CSR Bluetooth software stack, it provides a fully compliant Bluetooth system to v1.2 of the specification for data and voice communications.

# BlueCore™3-Multimedia

#### Single Chip Bluetooth® v1.2 System

**Production Information Data Sheet For**

BC358239A

October 2006

# Applications

- Stereo Headphones

- Automotive Hands-Free Kits

- Echo Cancellation

- High Performance Telephony Headsets

- Enhanced Audio Applications

- A/V Profile Support

BlueCore3-Multimedia contains the Kalimba DSP which is an open platform digital signal processor (DSP) co-processor allowing for support of enhanced audio applications.

BlueCore3-Multimedia has been designed to reduce the number of external components required which ensures production costs are minimised.

The device incorporates auto-calibration and built-in self-test (BIST) routines to simplify development, type approval and production test. All hardware and device firmware is fully compliant with the Bluetooth v1.2 Specification.

#### BlueCore3-Multimedia System Architecture

# Contents

| Sta | Status Information                    |                                          |    |  |  |  |

|-----|---------------------------------------|------------------------------------------|----|--|--|--|

| 1   | Key Features9                         |                                          |    |  |  |  |

| 2   | 10 x 10mm LFBGA Package Information10 |                                          |    |  |  |  |

|     | 2.1                                   | BC358239A-INN-E4 Pinout Diagram          | 10 |  |  |  |

|     | 2.2                                   | Device Terminal Functions                | 11 |  |  |  |

| 3   | Elec                                  | trical Characteristics                   | 15 |  |  |  |

|     | 3.1                                   | Absolute Maximum Ratings                 | 15 |  |  |  |

|     | 3.2                                   | Recommended Operating Conditions         | 15 |  |  |  |

|     | 3.3                                   | Linear Regulator                         | 16 |  |  |  |

|     | 3.4                                   | Digital Terminals                        | 17 |  |  |  |

|     | 3.5                                   | USB Terminals                            | 18 |  |  |  |

|     | 3.6                                   | Power on Reset                           | 18 |  |  |  |

|     | 3.7                                   | Auxiliary ADC                            | 18 |  |  |  |

|     | 3.8                                   | Auxiliary DAC                            | 19 |  |  |  |

|     | 3.9                                   | Clocks                                   | 19 |  |  |  |

|     | 3.10                                  | Stereo Audio CODEC Characteristics       | 20 |  |  |  |

|     |                                       | Power Consumption                        |    |  |  |  |

| 4   |                                       | io Characteristics                       |    |  |  |  |

|     |                                       | Temperature +20°C                        |    |  |  |  |

|     |                                       | 4.1.1 Transmitter                        |    |  |  |  |

|     |                                       | 4.1.2 Receiver                           |    |  |  |  |

|     | 4.2                                   | Temperature -40°C                        |    |  |  |  |

|     |                                       | 4.2.1 Transmitter                        |    |  |  |  |

|     | 4.3                                   | Temperature -25°C                        |    |  |  |  |

|     | -                                     | 4.3.1 Transmitter                        |    |  |  |  |

|     |                                       | 4.3.2 Receiver                           |    |  |  |  |

|     | 4.4                                   | Temperature +85°C                        |    |  |  |  |

|     |                                       | 4.4.1 Transmitter                        |    |  |  |  |

|     | 4.5                                   | Temperature +105°C                       |    |  |  |  |

|     |                                       | 4.5.1 Transmitter                        |    |  |  |  |

|     |                                       | 4.5.2 Receiver                           |    |  |  |  |

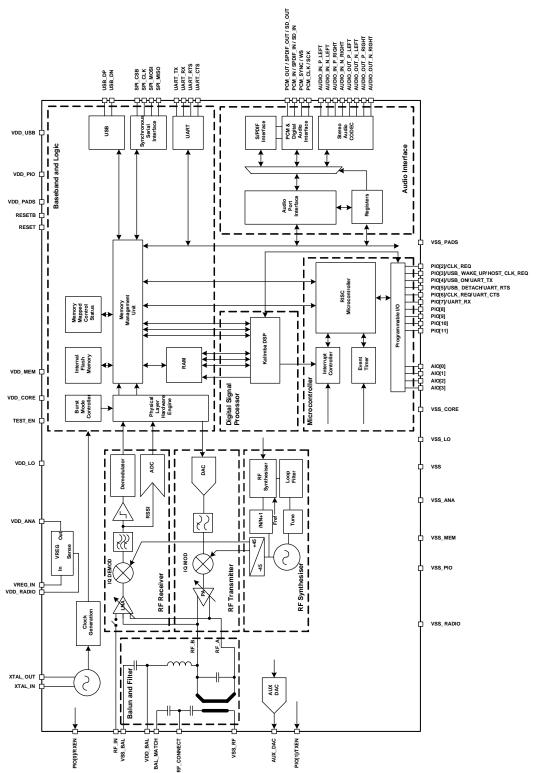

| 5   |                                       | ice Diagram                              |    |  |  |  |

| 6   | Dese                                  | cription of Functional Blocks            |    |  |  |  |

|     | 6.1                                   | RF Receiver                              |    |  |  |  |

|     |                                       | 6.1.1 Low Noise Amplifier                |    |  |  |  |

|     | 6.2                                   | RF Transmitter                           |    |  |  |  |

|     | 0.2                                   | 6.2.1 IQ Modulator                       |    |  |  |  |

|     |                                       | 6.2.2 Power Amplifier                    |    |  |  |  |

|     |                                       | 6.2.3 Auxiliary DAC                      |    |  |  |  |

|     | 6.3 RF Synthesiser                    |                                          |    |  |  |  |

|     | 6.4                                   | Clock Input and Generation               |    |  |  |  |

|     | 6.5                                   | Baseband and Logic                       |    |  |  |  |

|     |                                       | 6.5.1 Memory Management Unit             |    |  |  |  |

|     |                                       | 6.5.3 Physical Layer Hardware Engine DSP | 32 |  |  |  |

|     |                                       | 6.5.4 RAM                                |    |  |  |  |

|     |                                       |                                          | 52 |  |  |  |

|   |      |                | FLASH MemoryUSB                                                                   |      |

|---|------|----------------|-----------------------------------------------------------------------------------|------|

|   |      | 6.5.8          | Synchronous Serial Interface                                                      | . 33 |

|   | 6.6  |                | controller                                                                        |      |

|   |      |                | Programmable I/O                                                                  |      |

|   | 6.7  | Kalimt         | ba DSP                                                                            | . 34 |

|   | 6.8  | Audio          | Interface                                                                         | . 35 |

|   |      | 6.8.1          | Audio Input and Output                                                            | . 35 |

| _ |      |                | Digital Audio Interface                                                           |      |

| 7 |      |                | both Software Stacks                                                              |      |

|   | 7.1  |                | ore HCI Stack<br>Key Features of the HCI Stack - Standard Bluetooth Functionality |      |

|   |      | 7.1.2          | Key Features of the HCI Stack - Extra Functionality                               | . 38 |

|   | 7.2  |                | Alone BlueCore3-Multimedia and Kalimba DSP Applications                           |      |

|   | 7.3  |                | Side Software                                                                     |      |

|   | 7.4  |                | Firmware Upgrade                                                                  |      |

|   | 7.5  | BCHS           | Software                                                                          | . 40 |

|   | 7.6  | Additic        | onal Software for Other Embedded Applications                                     | . 40 |

|   | 7.7  | CSR E          | Development Systems                                                               | .40  |

| 8 | Devi | ce Ter         | minal Descriptions                                                                | . 41 |

|   | 8.1  | RF Po          | rts                                                                               | .41  |

|   |      |                | Single-Ended Input (RF_IN)                                                        |      |

|   |      |                | RF Plug 'n' Go                                                                    |      |

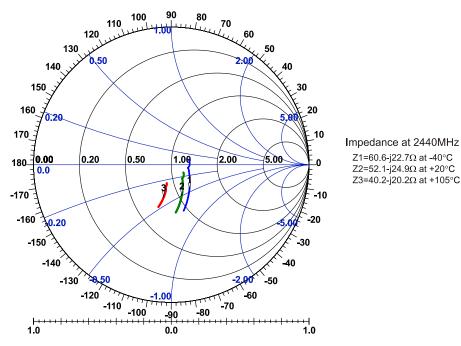

|   |      |                | nit Port Impedances for Plug-n-Go Package                                         |      |

|   |      |                | ve Port Impedances for Plug-n-Go Package                                          |      |

|   | 8.4  |                | al Reference Clock Input (XTAL_IN)                                                |      |

|   |      |                | External Mode<br>XTAL IN Impedance in External Mode                               |      |

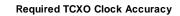

|   |      | 8.4.3          | Clock Timing Accuracy                                                             | . 44 |

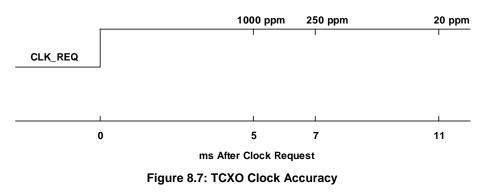

|   |      |                | Clock Start-Up Delay                                                              |      |

|   | 85   |                | Input Frequencies and PS Key Settings<br>I Oscillator (XTAL_IN, XTAL_OUT)         |      |

|   | 0.5  |                | XTAL Mode                                                                         |      |

|   |      |                | Load Capacitance                                                                  |      |

|   |      |                | Frequency Trim                                                                    |      |

|   |      |                | Transconductance Driver Model<br>Negative Resistance Model                        |      |

|   |      |                | Crystal PS Key Settings                                                           |      |

|   |      |                | Crystal Oscillator Characteristics                                                |      |

|   | 8.6  |                | Interface                                                                         |      |

|   |      | 8.6.1<br>8.6.2 | UART Bypass<br>UART Configuration While RESET is Active                           |      |

|   |      |                | UART Bypass Mode                                                                  | . 55 |

|   |      | 8.6.4          | ·····                                                                             |      |

|   | 8.7  |                | nterface                                                                          |      |

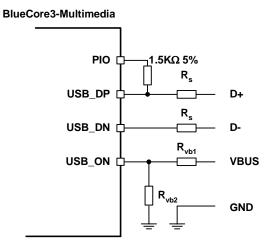

|   |      |                | USB Data Connections<br>USB Pull-Up Resistor                                      |      |

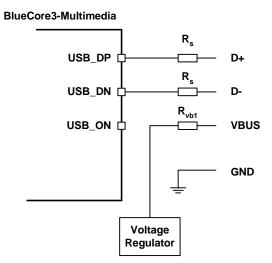

|   |      | 8.7.3          | Power Supply                                                                      | . 56 |

|   |      |                | Self Powered Mode                                                                 |      |

|   |      |                | Bus Powered ModeSuspend Current                                                   |      |

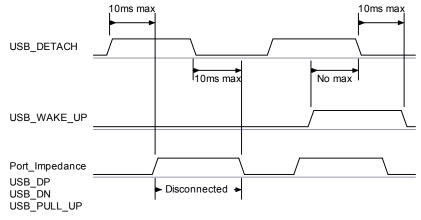

|   |      |                | Detach and Wake_Up Signalling                                                     |      |

|   |      | 8.7.8          | USB Driver                                                                        | . 59 |

|   |      |                | USB 1.1 Compliance USB 2.0 Compatibility                                          |      |

|   | 8.8  |                | Peripheral Interface                                                              |      |

|   | 0.0  |                | Instruction Cycle                                                                 |      |

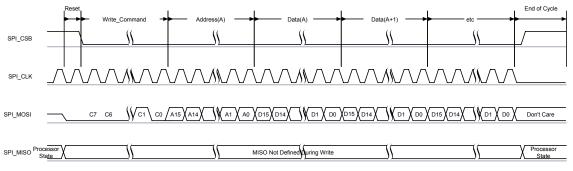

|     | 8.8.2                    | Writing to BlueCore3-Multimedia                                   | 61       |

|-----|--------------------------|-------------------------------------------------------------------|----------|

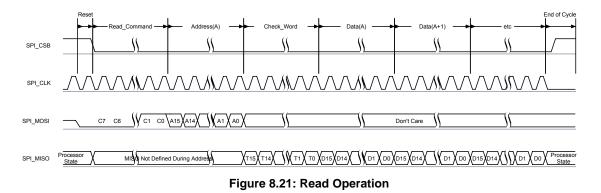

|     |                          | Reading from BlueCore3-Multimedia                                 |          |

|     |                          | Multi Slave Operation                                             |          |

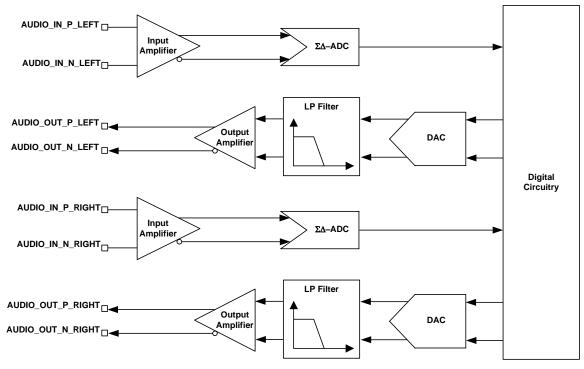

|     |                          | o Audio Interface                                                 |          |

|     | 8.9.1                    |                                                                   |          |

|     | 8.9.2                    | ADC<br>ADC Sample Rate Selection and Warping                      | 63       |

|     | 0.9.3<br>894             | ADC Sample Rate Selection and Warping                             | 03<br>64 |

|     |                          | DAC                                                               |          |

|     | 8.9.6                    | DAC Sample Rate Selection and Warping                             | 66       |

|     | 8.9.7                    | DAC Gain                                                          | 66       |

|     |                          | Mono Operation                                                    |          |

|     | 8.9.9                    | PCM CODEC Interface<br>0 PCM Interface Master/Slave               | 80       |

|     |                          | 1 Long Frame Sync                                                 |          |

|     |                          | 2 Short Frame Sync                                                |          |

|     |                          | 3 Multi Slot Operation                                            |          |

|     |                          | 4 GCI Interface                                                   |          |

|     |                          | 5 Slots and Sample Formats<br>6 Additional Features               |          |

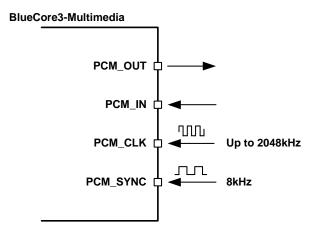

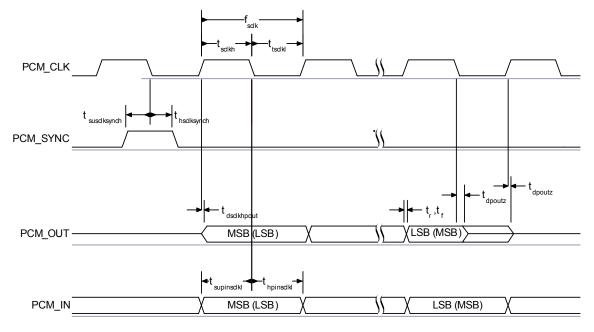

|     | 8.9.1                    | 7 PCM Timing Information                                          | 72       |

|     | 8.9.1                    | 8 PCM Slave Timing                                                | 75       |

|     | 8.9.1                    | 9 PCM_CLK and PCM_SYNC Generation                                 | 77       |

|     | 8.9.2                    | 0 PCM Configuration                                               | 78       |

|     |                          | 1 Digital Audio Bus                                               |          |

|     |                          | 2 IEC 60958 Interface                                             |          |

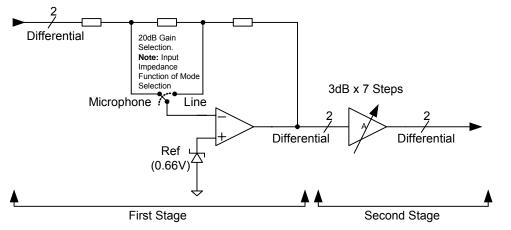

|     |                          | 4 Microphone Input                                                |          |

|     |                          | 5 Line Input                                                      |          |

|     |                          | 6 Output Stage                                                    |          |

|     |                          | arallel Ports                                                     |          |

|     | 8.10.                    | 1 PIO Defaults for BlueCore3-Multimedia                           | 87       |

|     | 8.11 I <sup>2</sup> C In | terface                                                           | 87       |

|     | 8.12 TCX0                | D Enable OR Function                                              | 88       |

|     | 8.13 RESE                | ET and RESETB                                                     | 88       |

|     |                          | 1 Pin States on Reset                                             |          |

|     |                          | 2 Status after Reset                                              |          |

|     | 8.14 Powe                | r Supply                                                          | 90       |

|     |                          | 1 Internal Voltage Regulator                                      |          |

|     |                          | 2 External Voltage Source                                         |          |

|     |                          | 3 Sequencing                                                      |          |

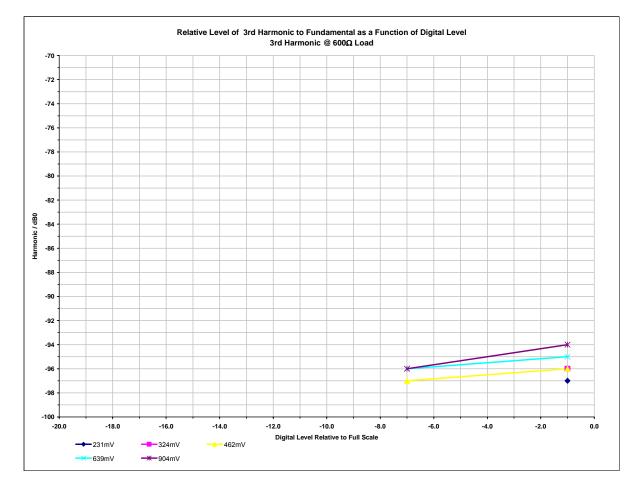

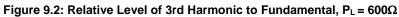

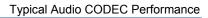

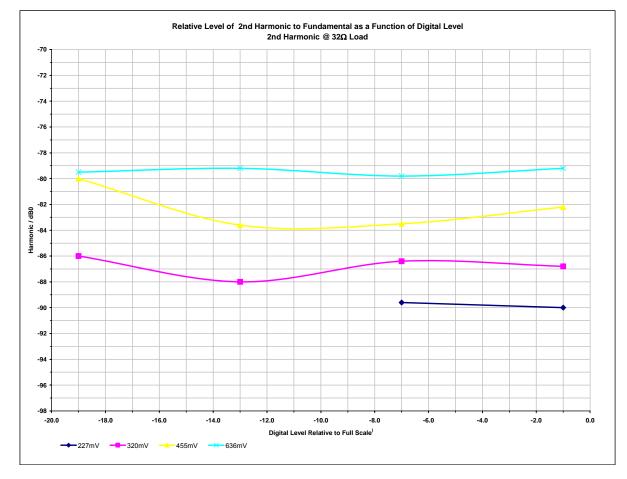

| 9   |                          | Idio CODEC Performance                                            |          |

|     | 9.1 Outpu                | ut                                                                | 91       |

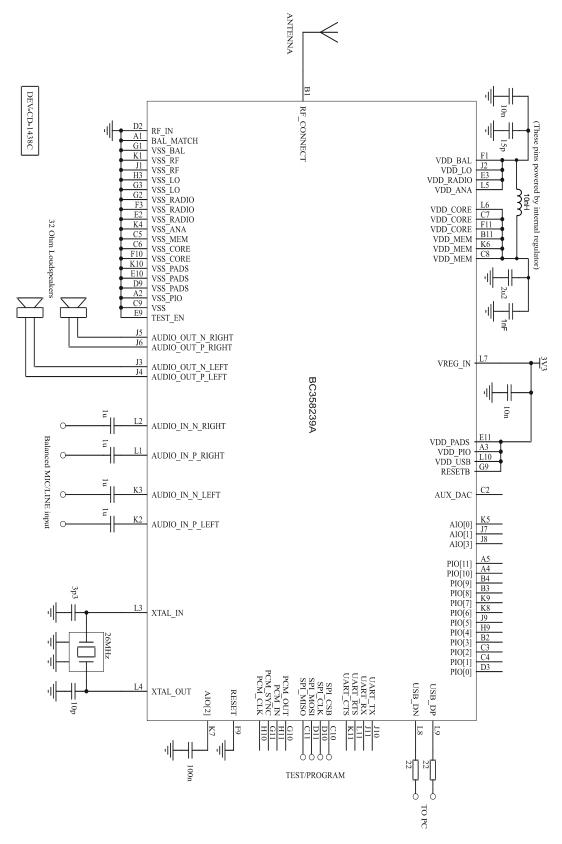

| 10  | Applicatio               | n Schematic                                                       | 99       |

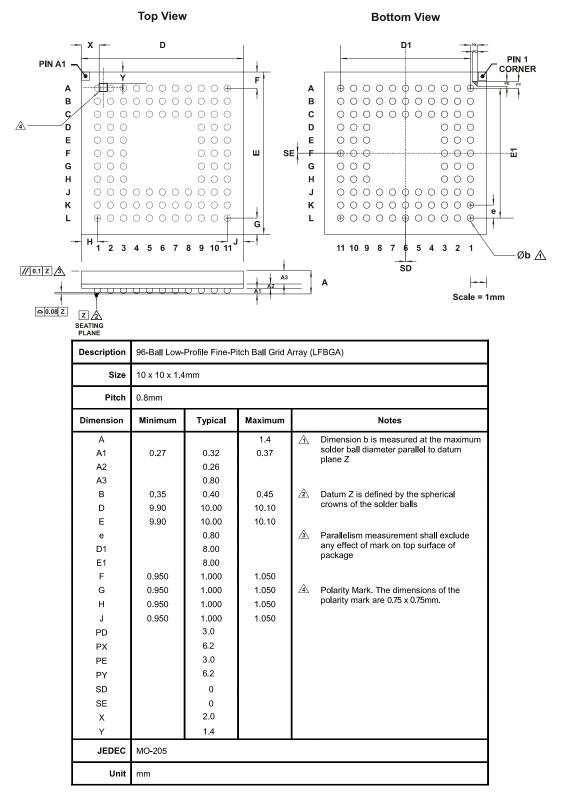

| 11  | Package D                | Dimensions                                                        | 100      |

|     |                          | 10mm LFBGA 96-Ball Package                                        |          |

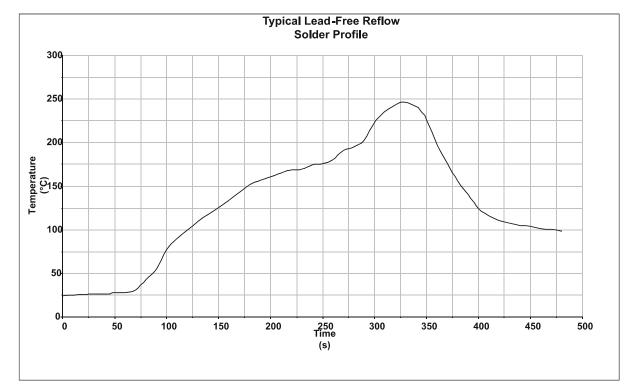

| 12  | Solder Pro               | ofiles                                                            | 101      |

|     |                          | al Solder Re-flow Profile for Devices with Lead-Free Solder Balls |          |

| 13  |                          | nformation                                                        |          |

|     | -                        | Core3-Multimedia                                                  |          |

| 14  |                          | References                                                        |          |

|     |                          | finitions                                                         |          |

|     |                          | tory                                                              |          |

| 200 | -americ 1113             | ····                                                              |          |

#### List of Figures

| Figure 2.1: BC358239A BlueCore3-Multimedia Device Pinout                                  | 10 |

|-------------------------------------------------------------------------------------------|----|

| Figure 5.1: BlueCore3-Multimedia Device Diagram                                           | 30 |

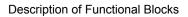

| Figure 6.1: Kalimba DSP Interface to Internal Functions                                   | 34 |

| Figure 6.2: Audio Interface                                                               | 35 |

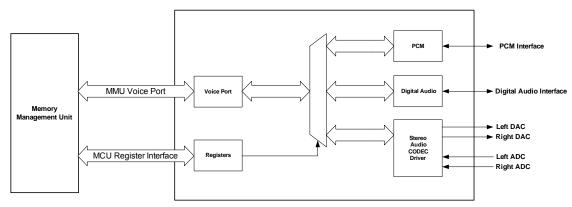

| Figure 7.1: BlueCore HCI Stack                                                            | 36 |

| Figure 7.2: Kalimba DSP Stack                                                             | 39 |

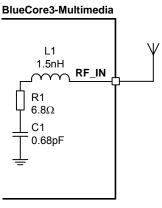

| Figure 8.1: Circuit RF_IN                                                                 | 41 |

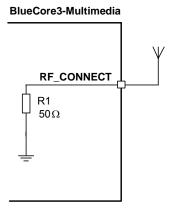

| Figure 8.2: Circuit for RF_CONNECT                                                        | 41 |

| Figure 8.3: RF_CONNECT Output at Power Setting 35                                         | 42 |

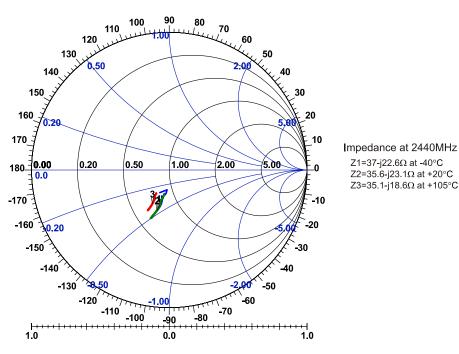

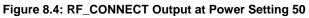

| Figure 8.4: RF_CONNECT Output at Power Setting 50                                         | 42 |

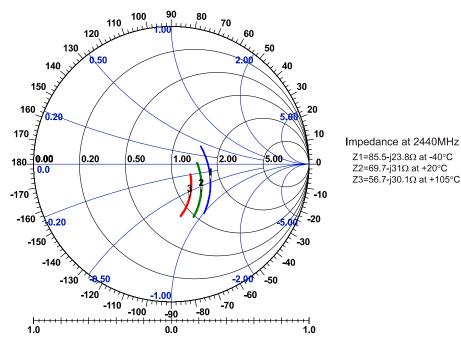

| Figure 8.5: RF_CONNECT Matched in Receive Mode                                            | 43 |

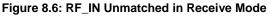

| Figure 8.6: RF_IN Unmatched in Receive Mode                                               | 43 |

| Figure 8.7: TCXO Clock Accuracy                                                           | 44 |

| Figure 8.8: Actual Allowable Clock Presence Delay on XTAL_IN vs. PS Key Setting           | 45 |

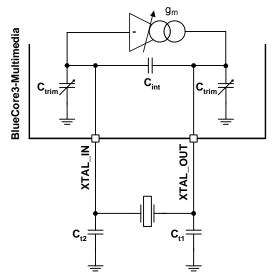

| Figure 8.9: Crystal Driver Circuit                                                        | 47 |

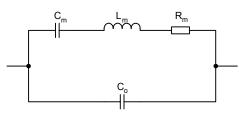

| Figure 8.10: Crystal Equivalent Circuit                                                   | 47 |

| Figure 8.11: Crystal Load Capacitance and Series Resistance Limits with Crystal Frequency | 50 |

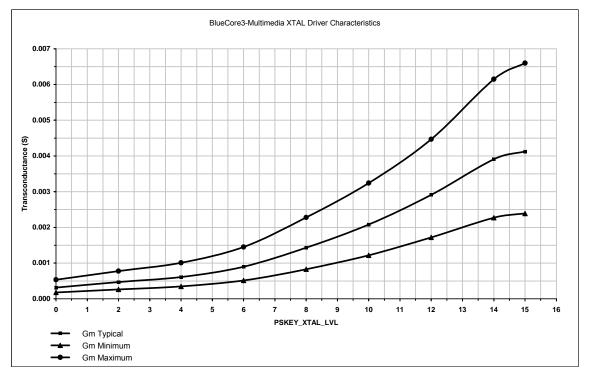

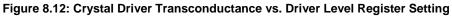

| Figure 8.12: Crystal Driver Transconductance vs. Driver Level Register Setting            | 51 |

| Figure 8.13: Crystal Driver Negative Resistance as a Function of Drive Level Setting      | 52 |

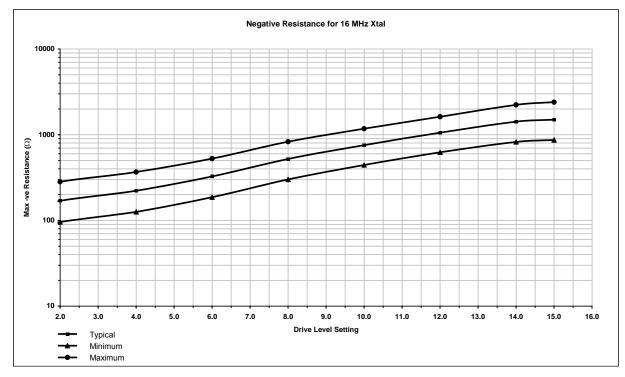

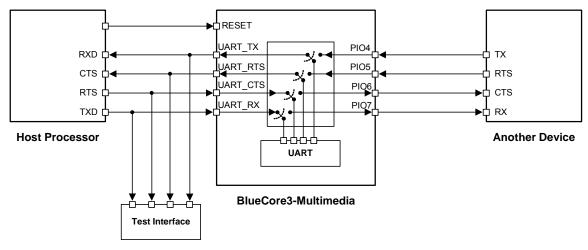

| Figure 8.14: Universal Asynchronous Receiver                                              | 53 |

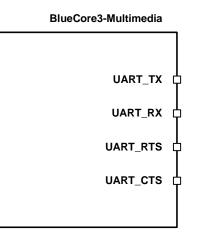

| Figure 8.15: Break Signal                                                                 | 54 |

| Figure 8.16: UART Bypass Architecture                                                     | 55 |

| Figure 8.17: USB Connections for Self Powered Mode                                        | 57 |

| Figure 8.18: USB Connections for Bus Powered Mode                                         | 58 |

| Figure 8.19: USB_DETACH and USB_WAKE_UP Signal                                            | 59 |

| Figure 8.20: Write Operation                                                              | 61 |

| Figure 8.21: Read Operation                                                               | 61 |

| Figure 8.22: Stereo CODEC Audio Input and Output Stages                                   | 62 |

| Figure 8.23: First Stage of ADC Analogue Amplifier Block Diagram                          | 65 |

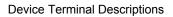

| Figure 8.24: BlueCore3-Multimedia as PCM Interface Master                                 | 69 |

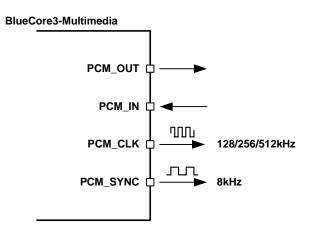

| Figure 8.25: BlueCore3-Multimedia as PCM Interface Slave                                  | 69 |

| Figure 8.26: Long Frame Sync (Shown with 8-bit Companded Sample)                          | 70 |

| Figure 8.27: Short Frame Sync (Shown with 16-bit Sample)                                  | 70 |

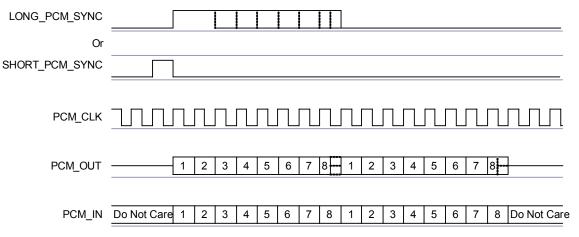

| Figure 8.28: Multi Slot Operation with Two Slots and 8-bit Companded Samples              | 71 |

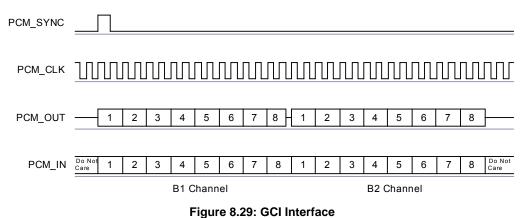

| Figure 8.29: GCI Interface                                                                | 71 |

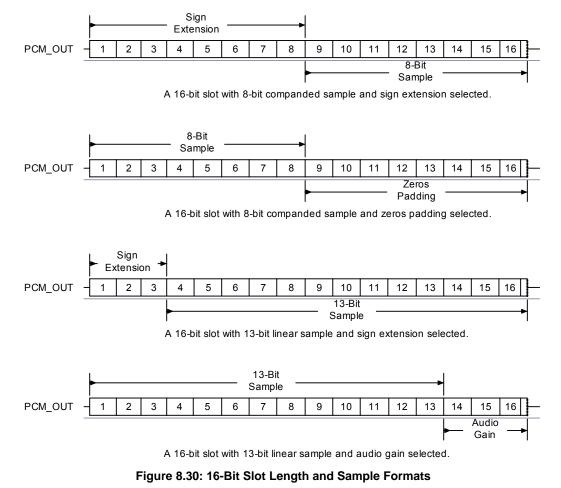

| Figure 8.30: 16-Bit Slot Length and Sample Formats                                        | 72 |

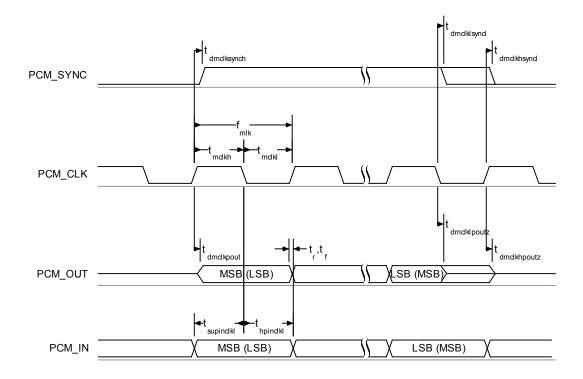

| Figure 8.31: PCM Master Timing Long Frame Sync                                            | 74 |

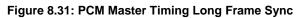

| Figure 8.32: PCM Master Timing Short Frame Sync                                           | 74 |

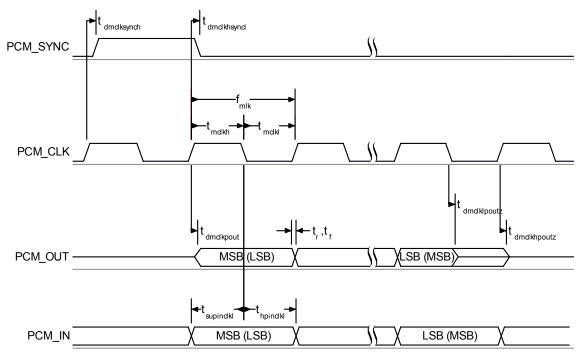

| Figure 8.33: PCM Slave Timing Long Frame Sync                                             | 76 |

| Figure 8.34: PCM Slave Timing Short Frame Sync                                            |    |

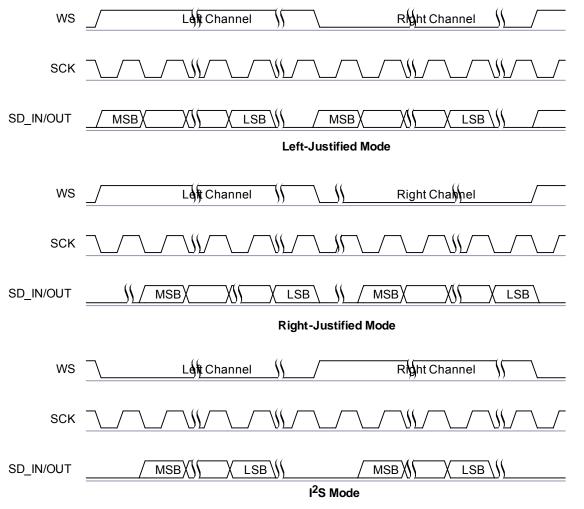

| Figure 8.35: Digital Audio Interface Modes                                                |    |

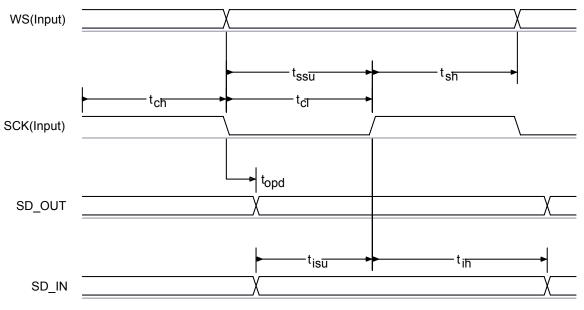

| Figure 8.36: Digital Audio Interface Slave Timing                                         |    |

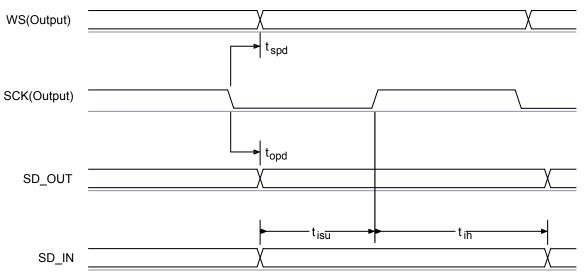

| Figure 8.37: Digital Audio Interface Master Timing                                        | 82 |

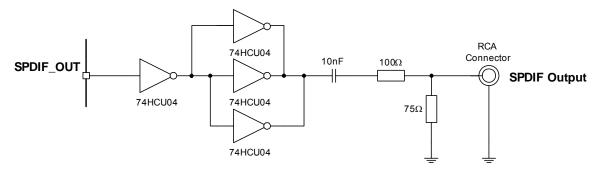

| Figure 8.38: Example Circuit for SPDIF Interface with Coaxial Output                      | 83 |

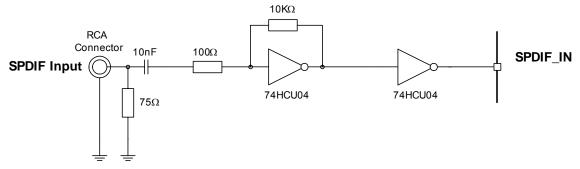

| Figure 8.39: Example Circuit for SPDIF Interface with Coaxial Input                                  | 83  |

|------------------------------------------------------------------------------------------------------|-----|

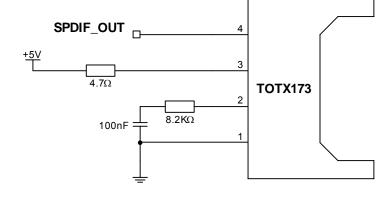

| Figure 8.40: Example Circuit for SPDIF Interface with Optical Output                                 | 84  |

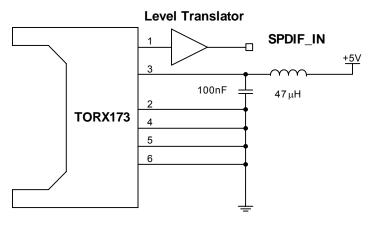

| Figure 8.41: Example Circuit for SPDIF Interface with Optical Input                                  | 84  |

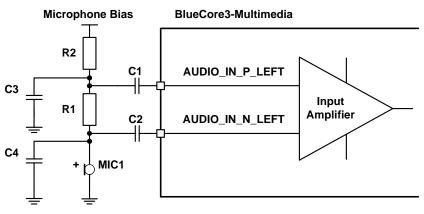

| Figure 8.42: Microphone Biasing (Left Channel Shown)                                                 | 85  |

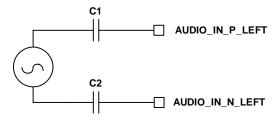

| Figure 8.43: Differential Input (Left Channel Shown)                                                 | 85  |

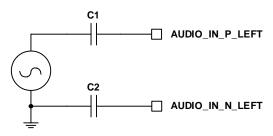

| Figure 8.44: Single Ended Input (Left Channel Shown)                                                 | 85  |

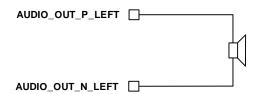

| Figure 8.45: Speaker Output (Left Channel Shown)                                                     |     |

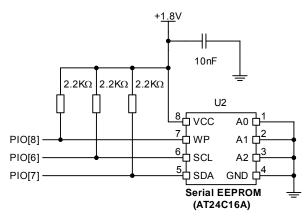

| Figure 8.46: Example EEPROM Connection                                                               | 87  |

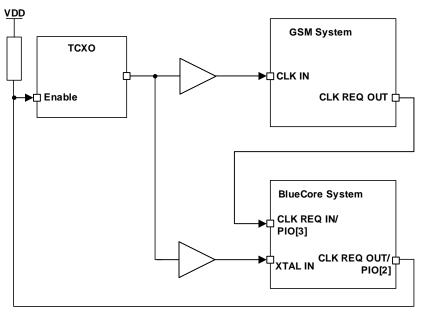

| Figure 8.47: Example TXCO Enable OR Function                                                         | 88  |

| Figure 10.1: Relative Level of $2^{nd}$ Harmonic to Fundamental, P <sub>L</sub> = 600 $\Omega$       | 91  |

| Figure 10.2: Relative Level of 3rd Harmonic to Fundamental, $P_L = 600\Omega$                        | 92  |

| Figure 10.3: Relative Level of $2^{nd}$ Harmonic to Fundamental, P <sub>L</sub> = $32\Omega$         | 93  |

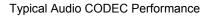

| Figure 10.4: Relative Level of $3^{rd}$ Harmonic to Fundamental, P <sub>L</sub> = $32\Omega$         | 94  |

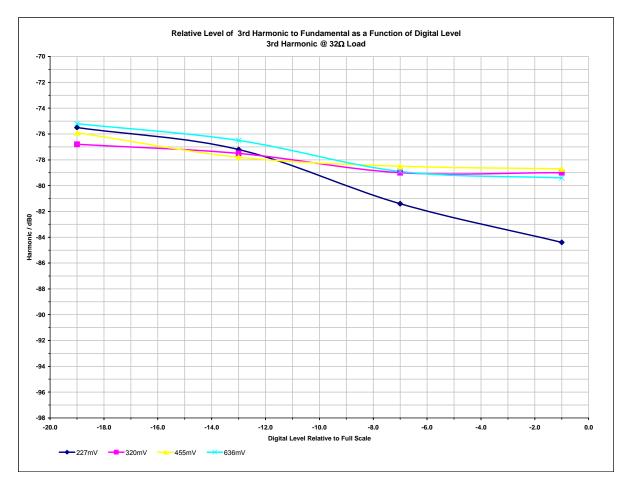

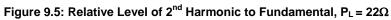

| Figure 10.5: Relative Level of $2^{nd}$ Harmonic to Fundamental, P <sub>L</sub> = $22\Omega$         | 95  |

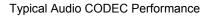

| Figure 10.6: Relative Level of $3^{rd}$ Harmonic to Fundamental, P <sub>L</sub> = $22\Omega$         | 96  |

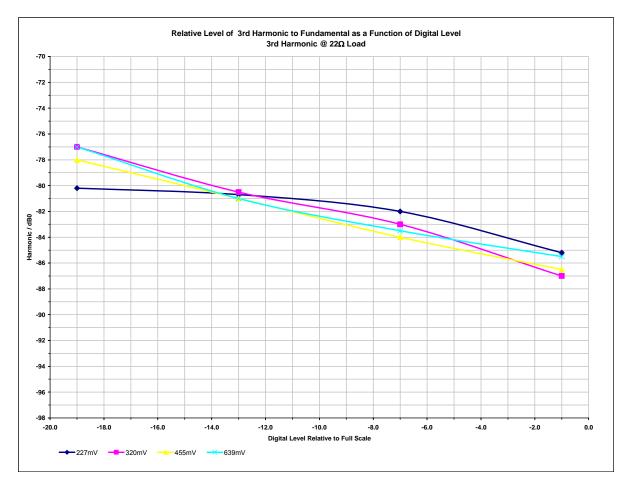

| Figure 10.7: Noise Floor                                                                             | 97  |

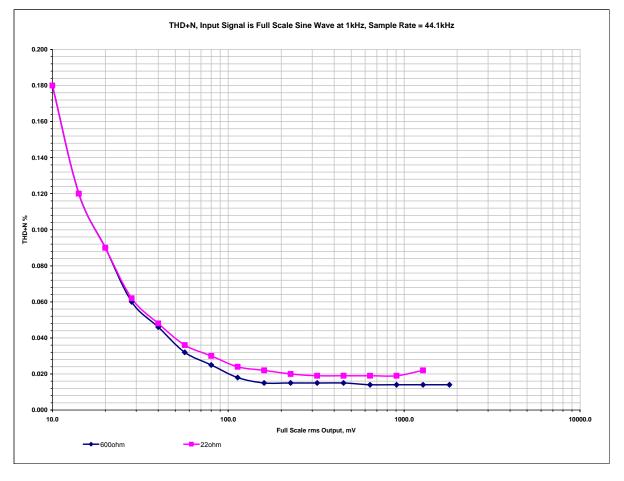

| Figure 10.8: THD+N                                                                                   |     |

| Figure 11.1: Application Circuit for Radio Characteristics Specification for 10 x 10mm LFBGA Package |     |

| Figure 12.1: BlueCore3-Multimedia 96-Ball LFBGA Package Dimensions                                   | 100 |

| Figure 13.1: Typical Lead-Free Re-flow Solder Profile                                                | 102 |

|                                                                                                      |     |

#### List of Tables

| Table 6.1: Alternative Functions of the Digital Audio Bus Interface on the PCM Interface |  |

|------------------------------------------------------------------------------------------|--|

| Table 8.1: External Clock Specifications                                                 |  |

| Table 8.2: PS Key Values for CDMA/3G Phone TCXO Frequencies46                            |  |

| Table 8.3: Crystal Oscillator Specification                                              |  |

| Table 8.4: Possible UART Settings                                                        |  |

| Table 8.5: Standard Baud Rates                                                           |  |

| Table 8.6: USB Interface Component Values58                                              |  |

| Table 8.7: Instruction Cycle for an SPI Transaction60                                    |  |

| Table 8.8: ADC Digital Gain Rate Selection64                                             |  |

| Table 8.9: DAC Digital Gain Rate Selection                                               |  |

| Table 8.10: DAC Analogue Gain Settings67                                                 |  |

| Table 8.11: PCM Master Timing73                                                          |  |

| Table 8.12: PCM Slave Timing75                                                           |  |

| Table 8.13: PSKEY_PCM_CONFIG32 Description78                                             |  |

| Table 8.14: PSKEY_PCM_LOW_JITTER_CONFIG Description79                                    |  |

| Table 8.15: Digital Audio Interface Slave Timing81                                       |  |

| Table 8.16: Digital Audio Interface Master Timing82                                      |  |

| Table 8.17: Pin States of BlueCore3-Multimedia on Reset                                  |  |

| Table 13.1: Solder Profile Zones                                                         |  |

#### List of Equations

| Equation 8.1: Load Capacitance                                                      | 48  |

|-------------------------------------------------------------------------------------|-----|

| Equation 8.2: Trim Capacitance                                                      | .48 |

| Equation 8.3: Frequency Trim                                                        | 48  |

| Equation 8.4: Pullability                                                           | .48 |

| Equation 8.5: Transconductance Required for Oscillation                             | .49 |

| Equation 8.6: Equivalent Negative Resistance                                        | .49 |

| Equation 8.7: Baud Rate                                                             | .54 |

| Equation 8.8: PCM_CLK Frequency When Being Generated Using the Internal 48MHz clock | .77 |

| Equation 8.9: PCM_SYNC Frequency Relative to PCM_CLK                                | 77  |

# **Status Information**

The status of this Data Book is **Production Information.**

CSR Product Data Books progress according to the following format:

#### Advance Information

Information for designers concerning CSR product in development. All values specified are the target values of the design. Minimum and maximum values specified are only given as guidance to the final specification limits and must not be considered as the final values.

All detailed specifications including pinouts and electrical specifications may be changed by CSR without notice.

#### **Pre-Production Information**

Pinout and mechanical dimension specifications finalised. All values specified are the target values of the design. Minimum and maximum values specified are only given as guidance to the final specification limits and must not be considered as the final values.

All electrical specifications may be changed by CSR without notice.

#### **Production Information**

Final Data Book including the guaranteed minimum and maximum limits for the electrical specifications.

Production Data Books supersede all previous document versions.

#### **Trademarks, Patents and Licenses**

Unless otherwise stated, words and logos marked with <sup>™</sup> or <sup>®</sup> are trademarks registered or owned by CSR plc or its affiliates. Bluetooth<sup>®</sup> and the Bluetooth logos are trademarks owned by Bluetooth SIG, Inc. and licensed to CSR. Other products, services and names used in this document may have been trademarked by their respective owners.

Windows®, Windows 98<sup>™</sup>, Windows 2000<sup>™</sup>, Windows XP<sup>™</sup> and Windows NT<sup>™</sup> are registered trademarks of the Microsoft Corporation.

OMAP<sup>™</sup> is a trademark of Texas Instruments Inc.

The publication of this information does not imply that any license is granted under any patent or other rights owned by CSR plc.

CSR reserves the right to make technical changes to its products as part of its development programme.

While every care has been taken to ensure the accuracy of the contents of this document, CSR cannot accept responsibility for any errors.

CSR's products are not authorised for use in life-support or safety-critical applications.

# 1 Key Features

#### Radio

- Common TX/RX terminal simplifies external matching; eliminates external antenna switch

- BIST minimises production test time. No external trimming is required in production

- Full RF reference designs available

- Bluetooth v1.2 Specification compliant

- Antenna matching and filtering within the IC

#### Transmitter

- +6dBm RF transmit power with level control from on-chip 6-bit DAC over a dynamic range >30dB

- Class 2 and Class 3 support without the need for an external power amplifier or TX/RX switch

#### Receiver

- Integrated channel filters

- Digital demodulator for improved sensitivity and co-channel rejection

- Real time digitised RSSI available on HCI interface

- Fast AGC for enhanced dynamic range

#### Synthesiser

- Fully integrated synthesiser requires no external VCO, varactor diode, resonator or loop filter

- Compatible with crystals between 8 and 32MHz (in multiples of 250kHz) or an external clock

- Accepts 7.68, 14.44, 15.36, 16.2, 16.8, 19.2, 19.44, 19.68, 19.8 and 38.4MHz TCXO frequencies for GSM and CDMA devices with sinusoidal or logic level signals

#### **Auxiliary Features**

- Crystal oscillator with built-in digital trimming

- Power management includes digital shut down, and wake up commands with an integrated low power oscillator for ultra-low power Park/Sniff/Hold mode

- 'Clock request' output to control an external clock

- On-chip linear regulator; 1.8V output from a 2.2-4.2V input

- Power-on-reset cell detects low supply voltage

- Arbitrary power supply sequencing permitted

- 8-bit ADC and DAC available to applications

## Kalimba DSP

- DSP co-processor, 32MIPs, 24-bit fixed point core

- Single cycle MAC; 24 x 24-bit multiply and 56-bit accumulator

- 32-bit instruction word, dual 24-bit data memory

- 4Kword program memory, 2 x 8Kword data memory

- Flexible interfaces to BlueCore3 subsystem

#### **Baseband and Software**

- Internal 8Mbit Flash for complete system solution

- Internal 32Kbyte RAM, allows full speed data transfer, mixed voice and data, and full piconet operation

- Logic for forward error correction, header error control, access code correlation, CRC, demodulation, encryption bit stream generation, whitening and transmit pulse shaping

- Transcoders for A-law, μ-law and linear voice from host and A-law, μ-law and CVSD voice over air

#### **Physical Interfaces**

- Synchronous serial interface up to 4Mbaud for system debugging

- UART interface with programmable baud rate up to 1.5Mbaud with an optional bypass mode

- Full speed USB v1.1 interface supports OHCI and UHCI host interfaces

- Bi-directional serial programmable audio interface supporting PCM, I<sup>2</sup>S and SPDIF formats

- Optional I<sup>2</sup>C<sup>™</sup> compatible interface

#### Stereo Audio CODEC

- 16-bit resolution, standard sample rates of 8kHz, 11.025kHz, 16kHz, 22.05kHz, 32kHz, 44.1kHz and 48kHz (DAC only)

- Dual ADC and DAC for stereo audio

- Integrated amplifiers for driving microphone and speakers with minimum external components

#### Bluetooth Stack

CSR's Bluetooth Protocol Stack runs on the on-chip MCU in a variety of configurations:

- Standard HCI (UART or USB)

- Fully embedded RFCOMM

- Customised builds with embedded application code

#### Package Options

96-ball LFBGA, 10 x 10 x 1.4mm, 0.8mm pitch

# 2 10 x 10mm LFBGA Package Information

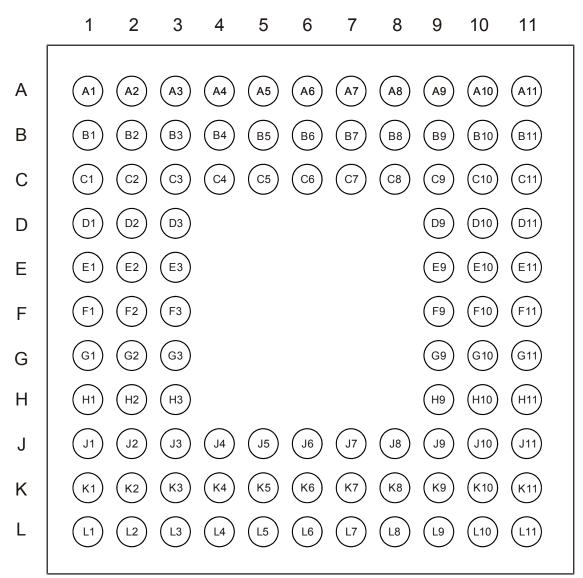

# 2.1 BC358239A-INN-E4 Pinout Diagram

Orientation from top of device

Figure 2.1: BC358239A BlueCore3-Multimedia Device Pinout

Γ

| Radio                        | Ball | Pad Type                                                              | Description                                                   |

|------------------------------|------|-----------------------------------------------------------------------|---------------------------------------------------------------|

| RF_IN                        | D2   | Analogue                                                              | Single ended receiver input                                   |

| PIO[0]/RXEN                  | D3   | Bi-directional with<br>programmable strength<br>internal pull-up/down | Control output for external TX/RX (if fitted)                 |

| PIO[1]/TXEN                  | C4   | Bi-directional with<br>programmable strength<br>internal pull-up/down | Control output for external PA (If fitted)                    |

| BAL_MATCH                    | A1   | Analogue                                                              | Tie to VSS_RADIO                                              |

| RF_CONNECT                   | B1   | Analogue                                                              | $50\Omega$ RF matched I/O                                     |

| AUX_DAC                      | C2   | Analogue                                                              | Voltage DAC output                                            |

| Synthesiser and Oscillator   | Ball | Pad Type                                                              | Description                                                   |

| XTAL_IN                      | L3   | Analogue                                                              | For crystal or external clock input                           |

| XTAL_OUT                     | L4   | Analogue                                                              | Drive for crystal                                             |

|                              |      |                                                                       |                                                               |

| USB and UART                 | Ball | Pad Type                                                              | Description                                                   |

| UART_TX                      | J10  | CMOS output, tri-state, with weak internal pull-up                    | UART data output                                              |

| UART_RX                      | J11  | CMOS input with weak<br>internal pull-down                            | UART data input                                               |

| UART_RTS                     | L11  | CMOS output, tri-state, with weak internal pull-up                    | UART request to send active low                               |

| UART_CTS                     | K11  | CMOS input with weak<br>internal pull-down                            | UART clear to send active low                                 |

| USB_DP                       | L9   | Bi-directional                                                        | USB data plus with selectable internal 1.5kΩ pull-up resistor |

| USB_DN                       | L8   | Bi-directional                                                        | USB data minus                                                |

|                              |      |                                                                       |                                                               |

| PCM Interface <sup>(1)</sup> | Ball | Pad Type                                                              | Description                                                   |

| PCM_OUT                      | G10  | CMOS output, tri-state, with weak internal pull-down                  | Synchronous data output                                       |

| PCM_IN                       | H11  | CMOS input, with weak internal pull-down                              | Synchronous data input                                        |

#### 2.2 Device Terminal Functions

Notes:

PCM\_SYNC

PCM\_CLK

<sup>(1)</sup> Pin names may be redefined dependent on chosen interface, see Table 6.1

internal pull-down Bi-directional with weak

internal pull-down Bi-directional with weak

internal pull-down

G11

H10

Synchronous data sync

Synchronous data clock

| PIO Port                                      | Ball | Pad Type                                                              | Description                                                                                              |

|-----------------------------------------------|------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| PIO[11]                                       | A5   | Bi-directional with<br>programmable strength<br>internal pull-up/down | Programmable input/output line                                                                           |

| PIO[10]                                       | A4   | Bi-directional with<br>programmable strength<br>internal pull-up/down | Programmable input/output line                                                                           |

| PIO[9]                                        | B4   | Bi-directional with<br>programmable strength<br>internal pull-up/down | Programmable input/output line                                                                           |

| PIO[8]                                        | B3   | Bi-directional with<br>programmable strength<br>internal pull-up/down | Programmable input/output line                                                                           |

| PIO[7]/UART_RX <sup>(1)</sup>                 | K9   | Bi-directional with<br>programmable strength<br>internal pull-up/down | Programmable input/output line                                                                           |

| PIO[6]/CLK_REQ/<br>UART_CTS <sup>(1)</sup>    | K8   | Bi-directional with<br>programmable strength<br>internal pull-up/down | PIO line or clock request output to enable external clock for external clock line                        |

| PIO[5]/USB_DETACH/<br>UART_RTS <sup>(1)</sup> | J9   | Bi-directional with<br>programmable strength<br>internal pull-up/down | PIO line or chip detaches from USB when this input is high                                               |

| PIO[4]/USB_ON/<br>UART_TX <sup>(1)</sup>      | H9   | Bi-directional with<br>programmable strength<br>internal pull-up/down | PIO or USB on (input senses when VBUS is high, wakes BlueCore3-Multimedia)                               |

| PIO[3]/USB_WAKE_UP/<br>HOST_CLK_REQ           | B2   | Bi-directional with<br>programmable strength<br>internal pull-up/down | PIO or output goes high to wake up PC<br>when in USB mode or clock request input<br>from host controller |

| PIO[2]/CLK_REQ                                | C3   | Bi-directional with<br>programmable strength<br>internal pull-up/down | PIO or external clock request                                                                            |

| AIO[0]                                        | K5   | Bi-directional                                                        | Programmable input/output line                                                                           |

| AIO[1]                                        | J7   | Bi-directional                                                        | Programmable input/output line                                                                           |

| AIO[2]                                        | K7   | Bi-directional                                                        | Programmable input/output line                                                                           |

| AIO[3]                                        | J8   | Bi-directional                                                        | Programmable input/output line                                                                           |

| Test and Debug    | Ball | Pad Type                                             | Description                                                              |

|-------------------|------|------------------------------------------------------|--------------------------------------------------------------------------|

| RESET             | F9   | CMOS input with weak<br>internal pull-down           | Reset if high. Input debounced so must be high for >5ms to cause a reset |

| RESETB            | G9   | CMOS input, with weak internal pull-up               | Reset if low. Input debounced so must be low for >5ms to cause a reset   |

| SPI_CSB           | C10  | CMOS input with weak<br>internal pull-               | Chip select for Synchronous Serial Interface active low                  |

| SPI_CLK           | D10  | CMOS input with weak<br>internal pull-down           | Serial Peripheral Interface clock                                        |

| SPI_MOSI          | D11  | CMOS input with weak<br>internal pull-down           | Serial Peripheral Interface data input                                   |

| SPI_MISO          | C11  | CMOS output, tri-state, with weak internal pull-down | Serial Peripheral Interface data output                                  |

| TEST_EN           | E9   | CMOS input with strong internal pull-down            | For test purposes only (leave unconnected)                               |

|                   |      |                                                      | 1                                                                        |

| CODEC             | Ball | Pad Type                                             | Description                                                              |

| AUDIO_IN_P_LEFT   | K2   | Analogue                                             | Microphone input positive (left side)                                    |

| AUDIO_IN_N_LEFT   | K3   | Analogue                                             | Microphone input negative (left side)                                    |

| AUDIO_IN_P_RIGHT  | L1   | Analogue                                             | Microphone input positive (right side)                                   |

| AUDIO_IN_N_RIGHT  | L2   | Analogue                                             | Microphone input negative (right side)                                   |

| AUDIO_OUT_P_LEFT  | J4   | Analogue                                             | Speaker output positive (left side)                                      |

| AUDIO_OUT_N_LEFT  | J3   | Analogue                                             | Speaker output negative (left side)                                      |

| AUDIO_OUT_P_RIGHT | J6   | Analogue                                             | Speaker output positive (right side)                                     |

| AUDIO_OUT_N_RIGHT | J5   | Analogue                                             | Speaker output negative (right side)                                     |

| Power Supplies and<br>Control | Ball               | Pad Type             | Description                                                                                                                                     |

|-------------------------------|--------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| VREG_IN                       | L7                 | VDD/Regulator input  | Linear regulator input                                                                                                                          |

| VDD_USB                       | L10                | VDD                  | Positive supply for UART/USB ports                                                                                                              |

| VDD_PIO                       | A3                 | VDD                  | Positive supply for PIO <sup>(2)</sup> and AUX DAC                                                                                              |

| VDD_PADS                      | E11                | VDD                  | Positive supply for all other digital Input/Output ports <sup>(3)</sup>                                                                         |

| VDD_CORE                      | F11,<br>C7,<br>L6  | VDD                  | Positive supply for internal digital circuitry<br>and 1.8V regulated output for digital<br>circuitry. For further information, see<br>Section 3 |

| VDD_RADIO                     | E3                 | VDD/Regulator sense  | Positive supply for RF circuitry                                                                                                                |

| VDD_LO                        | J2                 | VDD                  | Positive supply for local oscillator circuitry                                                                                                  |

| VDD_ANA                       | L5                 | VDD/Regulator output | Positive supply for analogue circuitry and 1.8V regulated output                                                                                |

| VDD_BAL                       | F1                 | VDD                  | Positive supply for balun                                                                                                                       |

| VDD_MEM                       | C8,<br>B11,<br>K6  | VDD                  | Positive supply for internal memory and AIO ports                                                                                               |

| VSS_PADS                      | D9,<br>E10,<br>K10 | VSS                  | Ground connections for input/output                                                                                                             |

| VSS_CORE                      | F10,<br>C6         | VSS                  | Ground connection for internal digital<br>circuitry                                                                                             |

| VSS_RADIO                     | E2,<br>F3,<br>G2   | VSS                  | Ground connections for RF circuitry                                                                                                             |

| VSS_LO                        | G3,<br>H3          | VSS                  | Ground connections for local oscillator                                                                                                         |

| VSS_ANA                       | K4                 | VSS                  | Ground connections for analogue circuitry                                                                                                       |

| VSS                           | C9                 | VSS                  | Ground connection for internal package shield                                                                                                   |

| VSS_PIO                       | A2                 | VSS                  | Ground connection for PIO and AUX DAC                                                                                                           |

| VSS_BAL                       | G1                 | VSS                  | Ground connection for balun                                                                                                                     |

| VSS_MEM                       | C5                 | VSS                  | Ground connection for internal memory, AIO and extended PIO ports                                                                               |

| VSS_RF                        | J1,<br>K1          | VSS                  | Ground connection for RF circuitry                                                                                                              |

Notes:

<sup>(1)</sup> Transparent UART port maps directly to main UART port

- <sup>(2)</sup> Positive supply for PIO[3:0] and PIO[11:8]

- <sup>(3)</sup> Positive supply for SPI/PCM ports and PIO[7:4]

| Unconnected | Ball                                                                         | Description       |

|-------------|------------------------------------------------------------------------------|-------------------|

| Terminals   | A6, A7, A8, A9, A10, A11, B5, B6, B7,<br>B8, B9, B10, C1, D1, E1, F2, H1, H2 | Leave unconnected |

# **3** Electrical Characteristics

### 3.1 Absolute Maximum Ratings

| Rating                                                                    | Min      | Мах      |

|---------------------------------------------------------------------------|----------|----------|

| Storage Temperature                                                       | -40°C    | +150°C   |

| Supply Voltage: VDD_MEM, VDD_RADIO, VDD_LO, VDD_ANA, VDD_BAL and VDD_CORE | -0.4V    | 2.2V     |

| Supply Voltage: VDD_PADS, VDD_PIO and VDD_USB                             | -0.4V    | 3.7V     |

| Supply Voltage: VREG_IN                                                   | -0.4V    | 5.6V     |

| Other Terminal Voltages                                                   | VSS-0.4V | VDD+0.4V |

## 3.2 Recommended Operating Conditions

| Operating Condition                                              | Min   | Мах                 |

|------------------------------------------------------------------|-------|---------------------|

| Operating Temperature Range                                      | -40°C | +105°C              |

| Guaranteed RF performance range (1)                              | -25°C | +85°C               |

| Supply Voltage: VDD_MEM, VDD_RADIO, VDD_LO, VDD_ANA and VDD_CORE | 1.7V  | 1.9V                |

| Supply Voltage: VDD_PADS, VDD_PIO and VDD_USB                    | 1.7V  | 3.6V                |

| Supply Voltage: VREG_IN                                          | 2.2V  | 4.2V <sup>(2)</sup> |

Note:

$^{(1)}$  Typical figures are given for RF performance between -40°C and +105°C

<sup>(2)</sup> The device will operate without damage with VREG\_IN as high as 5.6V, however the RF performance is not guaranteed above 4.2V

## 3.3 Linear Regulator

| Linear Regulator                                  | Min  | Тур  | Max                | Unit   |

|---------------------------------------------------|------|------|--------------------|--------|

| Normal Operation                                  |      |      |                    |        |

| Output Voltage (Iload = 70 mA)                    | 1.70 | 1.78 | 1.85               | V      |

| Temperature Coefficient                           | -250 | -    | +250               | ppm/°C |

| Output Noise <sup>(1)(2)</sup>                    | -    | -    | 1                  | mV rms |

| Load Regulation (Iload < 100 mA)                  | -    | -    | 50                 | mV/A   |

| Settling Time <sup>(1)(3)</sup>                   | -    | -    | 50                 | μS     |

| Maximum Output Current                            | 140  | -    | -                  | mA     |

| Minimum Load Current                              | 5    | -    | -                  | μA     |

| Input Voltage                                     | -    | -    | 4.2 <sup>(6)</sup> | V      |

| Dropout Voltage (Iload = 70 mA)                   | -    | -    | 350                | mV     |

| Quiescent Current (excluding load, lload < 1mA)   | 25   | 35   | 50                 | μA     |

| Low Power Mode <sup>(4)</sup>                     |      |      |                    |        |

| Quiescent Current (excluding load, lload < 100µA) | 4    | 7    | 10                 | μΑ     |

| Disabled Mode <sup>(5)</sup>                      |      |      |                    |        |

| Quiescent Current                                 | 1.5  | 2.5  | 3.5                | μΑ     |

Notes:

For optimum performance the VDD\_ANA ball adjacent to VREG\_IN should be used for regulator ouput

- $^{(1)}$  Regulator output connected to 47nF pure and 4.7  $\mu$ F 2.2  $\Omega$  ESR capacitors

- <sup>(2)</sup> Frequency range 100Hz to 100kHz

- <sup>(3)</sup> 1mA to 70mA pulsed load

- <sup>(4)</sup> Low power mode is entered and exited automatically when the chip enters/leaves Deep Sleep mode

- <sup>(5)</sup> Regulator is disabled when VREG\_EN is pulled low. It can also be disabled by VREG\_IN when it is either open circuit or driven to the same voltage as VDD\_ANA

- <sup>(6)</sup> Operation up to 5.6V is permissible without damage and without the output voltage rising sufficiently to damage the rest of BlueCore3, but output regulation and other specifications are no longer guaranteed at input voltages in excess of 4.2V

# 3.4 Digital Terminals

| Digital Terminals                                                                    | Min               | Тур     | Max  | Unit    |    |

|--------------------------------------------------------------------------------------|-------------------|---------|------|---------|----|

| Input Voltage Levels                                                                 |                   |         |      |         |    |

| V <sub>IL</sub> input logic level low                                                | 2.7V ≤ VDD ≤ 3.0V | -0.4    | -    | +0.8    | V  |

|                                                                                      | 1.7V ≤ VDD ≤ 1.9V | -0.4    | -    | +0.4    | V  |

| V <sub>IH</sub> input logic level high                                               |                   | 0.7VDD  | -    | VDD+0.4 | V  |

| Output Voltage Levels                                                                |                   |         |      |         |    |

| $V_{OL}$ output logic level low,<br>( $I_o = 4.0mA$ ), 2.7V $\leq$ VDD $\leq$ 3      | .0V               | -       | -    | 0.2     | V  |

| $V_{OL}$ output logic level low,<br>( $I_o = 4.0$ mA), 1.7V $\leq$ VDD $\leq$ 1      | .9V               | -       | -    | 0.4     | V  |

| $V_{OH}$ output logic level high,<br>( $I_o = -4.0$ mA), 2.7V $\leq$ VDD $\leq$ 3.0V |                   | VDD-0.2 | -    | -       | V  |

| $V_{OH}$ output logic level high,<br>( $I_o = -4.0$ mA), $1.7V \le VDD \le 1.9V$     |                   | VDD-0.4 | -    | -       | V  |

| Input and Tri-state Current                                                          | with:             |         |      |         |    |

| Strong pull-up                                                                       |                   | -100    | -40  | -10     | μA |

| Strong pull-down                                                                     |                   | +10     | +40  | +100    | μA |

| Weak pull-up                                                                         |                   | -5.0    | -1.0 | -0.2    | μA |

| Weak pull-down                                                                       |                   | +0.2    | +1.0 | +5.0    | μA |

| I/O pad leakage current                                                              |                   | -1      | 0    | +1      | μA |

| C <sub>I</sub> Input Capacitance                                                     |                   | 1.0     | -    | 5.0     | pF |

### 3.5 USB Terminals

| USB Terminals                                              | Min         | Тур | Max         | Unit |

|------------------------------------------------------------|-------------|-----|-------------|------|

| VDD_USB for correct USB operation                          | 3.1         |     | 3.6         | V    |

| Input threshold                                            |             |     |             |      |

| V <sub>IL</sub> input logic level low                      | -           | -   | 0.3 VDD_USB | V    |

| V <sub>IH</sub> input logic level high                     | 0.7 VDD_USB | -   | -           | V    |

| Input leakage current                                      |             |     |             |      |

| VSS_PADS < $V_{IN}$ < $VDD_USB^{(1)}$                      | -1          | 1   | 5           | μA   |

| C <sub>I</sub> Input capacitance                           | 2.5         | -   | 10.0        | pF   |

| Output Voltage levels<br>to correctly terminated USB Cable |             |     |             |      |

| V <sub>OL</sub> output logic level low                     | 0.0         | -   | 0.2         | V    |

| V <sub>OH</sub> output logic level high                    | 2.8         | -   | VDD_USB     | V    |

### 3.6 Power on Reset

| Power-on reset             | Min  | Тур  | Мах  | Unit |

|----------------------------|------|------|------|------|

| VDD_CORE falling threshold | 1.40 | 1.50 | 1.60 | V    |

| VDD_CORE rising threshold  | 1.50 | 1.60 | 1.70 | V    |

| Hysteresis                 | 0.05 | 0.10 | 0.15 | V    |

# 3.7 Auxiliary ADC

| Auxiliary ADC                                   |     | Min  | Тур | Мах     | Unit      |

|-------------------------------------------------|-----|------|-----|---------|-----------|

| Resolution                                      |     | -    | -   | 8       | Bits      |

| Input voltage range<br>(LSB size = VDD_ANA/255) |     | 0    | -   | VDD_ANA | V         |

| Accuracy                                        | INL | -1   | -   | 1       | LSB       |

| (Guaranteed monotonic)                          | DNL | 0    | -   | 1       | LSB       |

| Offset                                          |     | -1   | -   | 1       | LSB       |

| Gain Error                                      |     | -0.8 | -   | 0.8     | %         |

| Input Bandwidth                                 |     | -    | 100 | -       | kHz       |

| Conversion time                                 |     | -    | 2.5 | -       | μS        |

| Sample rate <sup>(2)</sup>                      |     | -    | -   | 700     | Samples/s |

#### Notes:

- <sup>(1)</sup> Internal USB pull-up disabled

- <sup>(2)</sup> Access of ADC is through VM function and therefore sample rate given is achieved as part of this function

## 3.8 Auxiliary DAC

| Auxiliary DAC                                  | Min         | Тур       | Max     | Unit |

|------------------------------------------------|-------------|-----------|---------|------|

| Resolution                                     | -           | _         | 8       | Bits |

| Average output step size <sup>(1)</sup>        | 12.5        | 14.5      | 17.0    | mV   |

| Output Voltage                                 |             | monotonic |         |      |

| Voltage range (I <sub>0</sub> =0mA)            | VSS_PADS    | -         | VDD_PIO | V    |

| Current range                                  | -10.0       | -         | +0.1    | mA   |

| Minimum output voltage (I <sub>O</sub> =100µA) | 0.0         | -         | 0.2     | V    |

| Maximum output voltage (I <sub>O</sub> =10mA)  | VDD_PIO-0.3 | -         | VDD_PIO | V    |

| High Impedance leakage current                 | -1          | -         | +1      | μΑ   |

| Offset                                         | -220        | -         | +120    | mV   |

| Integral non-linearity <sup>(1)</sup>          | -2          | -         | +2      | LSB  |

| Settling time (50pF load)                      | -           | -         | 10      | μS   |

#### 3.9 Clocks

| Crystal Oscillator                 | Min | Тур  | Мах     | Unit    |

|------------------------------------|-----|------|---------|---------|

| Crystal frequency <sup>(2)</sup>   | 8.0 | -    | 32.0    | MHz     |

| Digital trim range <sup>(3)</sup>  | 5.0 | 6.2  | 8.0     | pF      |

| Trim step size <sup>(3)</sup>      | -   | 0.1  | -       | pF      |

| Transconductance                   | 2.0 | -    | -       | mS      |

| Negative resistance <sup>(4)</sup> | 870 | 1500 | 2400    | Ω       |

| External Clock                     |     |      |         |         |

| Input frequency <sup>(5)</sup>     | 7.5 | -    | 40.0    | MHz     |

| Clock input level <sup>(6)</sup>   | 0.2 | -    | VDD_ANA | V pk-pk |

| Allowable Jitter                   | -   | -    | 15      | ps rms  |

| XTAL_IN input impedance            | -   | -    | -       | kΩ      |

| XTAL_IN input capacitance          | -   | 7    | -       | pF      |

#### Notes:

- <sup>(1)</sup> Specified for an output voltage between 0.2V and VDD\_PIO -0.2V. Output is high impedance when chip is in Deep Sleep mode

- (2) Integer multiple of 250kHz

- <sup>(3)</sup> The difference between the internal capacitance at minimum and maximum settings of the internal digital trim

- <sup>(4)</sup> XTAL frequency = 16MHz; XTAL C0 = 0.75pF; XTAL load capacitance = 8.5pF

- <sup>(5)</sup> Clock input can be any frequency between 8 and 40MHz in steps of 250kHz plus CDMA/3G TCXO frequencies of 7.68, 14.44, 15.36, 16.2, 16.8, 19.2, 19.44, 19.68, 19.8 and 38.4MHz

- <sup>(6)</sup> Clock input can either be sinusoidal or square wave. If the peaks of the signal are below VSS\_ANA or above VDD\_ANA a DC blocking capacitor is required between the signal and XTAL\_IN

# 3.10 Stereo Audio CODEC Characteristics

#### ADC

| Parameter                  | Symbol              | Conditions                              |                                 | Min | Тур | Max  | Unit |

|----------------------------|---------------------|-----------------------------------------|---------------------------------|-----|-----|------|------|

| Resolution                 | NOB                 |                                         |                                 | -   | -   | 16   | Bits |

| Input Sample<br>Rate       | F <sub>sample</sub> |                                         |                                 | 8   | -   | 44.1 | kHz  |

|                            |                     |                                         | F <sub>sample</sub> = 8kHz      | -   | 84  | -    | dB   |

|                            |                     |                                         | F <sub>sample</sub> = 11.025kHz | -   | 83  | -    | dB   |

| Signal to<br>Noise Ratio + | SINAD               | $0 \rightarrow \frac{1}{2}F_{sample}$ , | F <sub>sample</sub> = 16kHz     | -   | 84  | -    | dB   |

| Distortion <sup>(1)</sup>  | SINAD               | f <sub>in</sub> = 1kHz                  | F <sub>sample</sub> = 22.050kHz | -   | 83  | -    | dB   |

|                            |                     |                                         | F <sub>sample</sub> = 32kHz     | -   | 80  | -    | dB   |

|                            |                     |                                         | F <sub>sample</sub> = 44.1kHz   | -   | 74  | -    | dB   |

| Digital Gain               |                     |                                         |                                 | -24 |     | 21.5 | dB   |

#### DAC

| Parameter                 | Symbol              | Conditions                         |                                 | Min | Тур | Мах  | Unit |

|---------------------------|---------------------|------------------------------------|---------------------------------|-----|-----|------|------|

| Resolution                | NOB                 |                                    |                                 | -   | -   | 16   | Bits |

| Output<br>Sample Rate     | F <sub>sample</sub> |                                    |                                 | 8   | -   | 48   | kHz  |

| Gain<br>Resolution        |                     |                                    |                                 | -   | 3   | -    | dB   |

|                           |                     | F <sub>sample</sub> = 8kHz         | -                               | 79  | -   | dB   |      |

|                           |                     |                                    | F <sub>sample</sub> = 11.025kHz | -   | 78  | -    | dB   |

| Signal to                 |                     |                                    | F <sub>sample</sub> = 16kHz     | -   | 79  | -    | dB   |

| Noise Ratio +             | SINAD               | 0→20kHz, f <sub>in</sub><br>= 1kHz | F <sub>sample</sub> = 22.050kHz | -   | 88  | -    | dB   |

| Distortion <sup>(1)</sup> |                     | 11112                              | F <sub>sample</sub> = 32kHz     | -   | 90  | -    | dB   |

|                           |                     |                                    | F <sub>sample</sub> = 44.1kHz   | -   | 90  | -    | dB   |

|                           |                     |                                    | F <sub>sample</sub> = 48kHz     | -   | 89  | -    | dB   |

| Digital Gain              |                     |                                    |                                 | -24 | -   | 21.5 | dB   |

#### Note:

<sup>(1)</sup> Measurements refer to digital part only

#### Audio Input, Microphone Amplifier

|                                                          | Min | Тур | Max | Unit   |

|----------------------------------------------------------|-----|-----|-----|--------|

| Input full scale at maximum gain                         | -   | 4   | -   | mV rms |

| Input full scale at minimum gain                         | -   | 400 | -   | mV rms |

| Gain resolution                                          | -   | 3   | -   | dB     |

| Distortion at 1kHz                                       | -   |     | -74 | dB     |

| Input referenced rms noise                               | -   | 8   | -   | μV rms |

| 3dB Bandwidth                                            | -   | 17  | -   | kHz    |

| Input impedance                                          | -   | 20  | -   | kΩ     |

| THD+N (microphone input) @ 30mV rms input                | -   | -66 | -   | dB     |

| THD+N (line input) @ 300mV $\Omega$ input <sup>(1)</sup> | -   | -74 | -   | dB     |

#### Audio Output, Speaker Output

| Parameter                                     | Symbol | Conditions                                                                                                                                        | Min | Тур   | Max  | Unit    |

|-----------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------|---------|

| Allowed                                       |        | Resistive                                                                                                                                         | 16  | -     | 0.C. | Ω       |

| Load                                          |        | Capacitive                                                                                                                                        | -   | -     | 500  | pF      |

| Max<br>output<br>voltage                      |        | R <sub>L</sub> =600Ω                                                                                                                              | -   | 2.0   | -    | V pk-pk |

| Max<br>output<br>current                      |        | R <sub>L</sub> =22Ω                                                                                                                               | -   | 75    | -    | mA      |

| Total<br>Harmonic<br>Distortion<br>plus Noise | THD+N  | $f_{IN}$ =1kHz,<br>BW=22Hz to 22kHz<br>R <sub>L</sub> =600 $\Omega$                                                                               | -   | 0.015 | -    | %       |

| Output<br>noise<br>relative to<br>full scale  | SNR    | A Weighted, Po=digital<br>silence, R∟=600Ω,<br>BW=22Hz to 22kHz                                                                                   | -   | -91   | -    | dB      |

| Channel<br>Separation<br>(Crosstalk)          | CS     | f <sub>IN</sub> =10kHz, analogue output<br>set to maximum gain                                                                                    | -   | -     | -60  | dB      |

| Power<br>Supply<br>Rejection<br>Ratio         | PSRR   | V <sub>ripple</sub> =200mV <sub>pk-pk</sub><br>sinewave, 10kHz at<br>VREG_IN.<br>2.3V ≤ VREG_IN ≤ 4.1V,<br>analogue output set to<br>maximum gain | -   | TBD   | -    | dB      |

| Second<br>Harmonic<br>Level                   |        | 1kHz sinewave, 1dB below full scale $600\Omega$                                                                                                   | -   | <-95  | -    | dB      |

| Third<br>Harmonic<br>Level                    |        | 1kHz sinewave, 1dB below full scale $600\Omega$                                                                                                   | -   | -95   | -    | dB      |

Note:

(1)

Input signal amplitudes are expressed as the differential voltages between the MIC\_P and MIC\_N terminals

#### Typical THD + N Relative to Full Scale

| Full Scale Output, mV rms   | 60    | 600Ω  |       | 2Ω    |  |

|-----------------------------|-------|-------|-------|-------|--|

| i un ocale output, niv inis | %     | dB    | %     | dB    |  |

| 10                          | 0.180 | -54.7 | 0.180 | -54.7 |  |

| 14                          | 0.120 | -58.2 | 0.120 | -58.2 |  |

| 20                          | 0.090 | -60.7 | 0.090 | -60.7 |  |

| 28                          | 0.060 | -64.2 | 0.062 | -63.9 |  |

| 40                          | 0.046 | -66.5 | 0.048 | -66.1 |  |

| 57                          | 0.032 | -69.7 | 0.036 | -68.6 |  |

| 80                          | 0.025 | -71.8 | 0.030 | -70.2 |  |

| 113                         | 0.018 | -74.6 | 0.024 | -72.1 |  |

| 160                         | 0.015 | -76.2 | 0.022 | -72.9 |  |

| 226                         | 0.015 | -76.2 | 0.020 | -73.7 |  |

| 320                         | 0.015 | -76.2 | 0.019 | -74.2 |  |

| 453                         | 0.015 | -76.2 | 0.019 | -74.2 |  |

| 640                         | 0.014 | -76.8 | 0.019 | -74.2 |  |

| 905                         | 0.014 | -76.8 | 0.019 | -74.2 |  |

| 1280                        | 0.014 | -76.8 | 0.022 | -72.9 |  |

| 1810                        | 0.014 | -76.8 |       |       |  |

#### Important Notes:

VDD\_CORE, VDD\_RADIO, VDD\_LO, VDD\_BAL and VDD\_ANA are at 1.8V unless shown otherwise

VDD\_PADS, VDD\_PIO and VDD\_USB are at 3.0V unless shown otherwise

The same setting of the digital trim is applied to both XTAL\_IN and XTAL\_OUT

Current drawn into a pin is defined as positive, current supplied out of a pin is defined as negative

# 3.11 Power Consumption

#### Typical Average Current Consumption

| VDD=1.8V Temperature = +20°C Output Power = 0dBm         |         |         |

|----------------------------------------------------------|---------|---------|

| Mode                                                     | Average | Unit    |

| SCO connection HV3 (30ms interval Sniff Mode) (Slave)    | 21      | mA      |

| SCO connection HV3 (30ms interval Sniff Mode) (Master)   | 21      | mA      |

| SCO connection HV3 (No Sniff Mode) (Slave)               | 28      | mA      |

| SCO connection HV1 (Slave)                               | 42      | mA      |

| SCO connection HV1 (Master)                              | 42      | mA      |

| ACL data transfer 115.2kbps UART no traffic (Master)     | 5       | mA      |

| ACL data transfer 115.2kbps UART no traffic (Slave)      | 22      | mA      |

| ACL data transfer 720kbps UART (Master or Slave)         | 45      | mA      |

| ACL data transfer 720kbps USB (Master or Slave)          | 45      | mA      |

| ACL connection, Sniff Mode 40ms interval, 38.4kbps UART  | 3.2     | mA      |

| ACL connection, Sniff Mode 1.28s interval, 38.4kbps UART | 0.45    | mA      |

| Parked Slave, 1.28s beacon interval, 38.4kbps UART       | 0.55    | mA      |

| Standby Mode (Connected to host, no RF activity)         | 47      | μΑ      |

| Reset (RESET high or RESETB low)                         | 15      | μΑ      |

| DSP                                                      |         |         |

| DSP core (including PM memory access)                    |         |         |

| Minimum (NOP)                                            | 0.25    | mA/MIPS |

| Maximum (MAC)                                            | 0.65    | mA/MIPS |

| DSP memory access (DM1 or DM2)                           | 0.15    | mA/MIPS |

| CODEC                                                    |         |         |

| Microphone inputs and ADC / channel                      | 0.85    | mA      |

| DAC and loudspeaker driver, no signal / channel          | 1.4     | mA      |

| Digital audio processing subsystem                       | 8       | mA      |

# 4 Radio Characteristics

## 4.1 Temperature +20°C

### 4.1.1 Transmitter

| Radio Characteristics VDD = 1.8V Temperature = +20°C                                  |     |      |     |                                                 |           |  |  |  |  |

|---------------------------------------------------------------------------------------|-----|------|-----|-------------------------------------------------|-----------|--|--|--|--|

|                                                                                       | Min | Тур  | Max | Bluetooth<br>Specification                      | Unit      |  |  |  |  |

| Maximum RF transmit power <sup>(1)(2)(3)</sup>                                        | -   | 6.5  | -   | -6 to +4 <sup>(4)</sup>                         | dBm       |  |  |  |  |

| Variation in RF power over temperature range with compensation enabled $(\pm)^{(4)}$  | -   | 0.5  | -   | -                                               | dB        |  |  |  |  |