#

## **18-Line SCSI Terminator**

#### FEATURES

- Complies with SCSI, SCSI-2, SCSI-3, SPI and FAST-20 Standards

- 2pF Channel Capacitance During Disconnect

- 50µA Supply Current in Disconnect Mode

- 110Ω Termination

- SCSI Hot Plugging Compliant, 10nA Typical

- +400mA Sinking Current for Active Negation

- –650mA Sourcing Current for Termination

- Trimmed Impedance to 5%

- Thermal Shutdown

- Current Limit

### DESCRIPTION

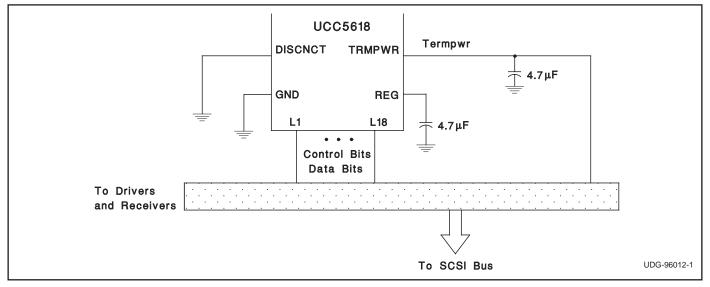

The UCC5618 provides 18 lines of active termination for a SCSI (Small Computers Systems Interface) parallel bus. The SCSI standard recommends and Fast-20 (Ultra) requires active termination at both ends of the cable.

Pin for pin compatible with the UC5601 and UC5608, the UCC5618 is ideal for high performance 5V SCSI systems, Termpwr 4.0-5.25V. During disconnect the supply current is only  $50\mu$ A typical, which makes the IC attractive for lower powered systems.

The UCC5618 is designed with a low channel capacitance of 2pF, which eliminates effects on signal integrity from disconnected terminators at interim points on the bus.

The power amplifier output stage allows the UCC5618 to source full termination current and sink active negation current when all termination lines are actively negated.

The UCC5618, as with all Unitrode terminators, is completely hot pluggable and appears as high impedance at the terminating channels with TRMPWR=0V or open.

Internal circuit trimming is utilized, first to trim the 110 $\Omega$  impedance, and then most importantly, to trim the output current as close to the max SCSI-3 spec as possible, which maximizes noise margin in fast SCSI operation.

This device is offered in low thermal resistance versions of the industry standard 28 pin wide body SOIC, TSSOP and PLCC.

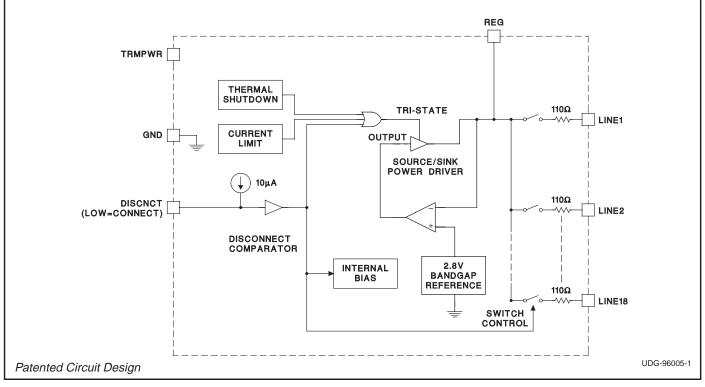

#### **BLOCK DIAGRAM**

#### **ABSOLUTE MAXIMUM RATINGS**

| TEMPWR+7V                                      |

|------------------------------------------------|

| Signal Line Voltage 0V to +7V                  |

| Regulator Output Current                       |

| Storage Temperature65°C to +150°C              |

| Operating Junction Temperature55°C to +150°C   |

| Lead Temperature (Soldering, 10 Seconds) 300°C |

All currents are positive into, negative out of the specified terminal. Consult Packaging Section of Databook for thermal limitations and considerations of packages.

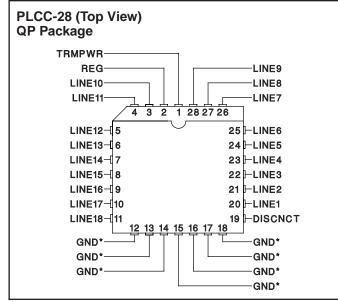

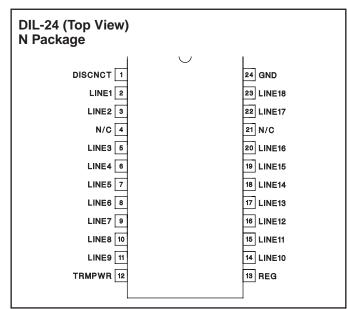

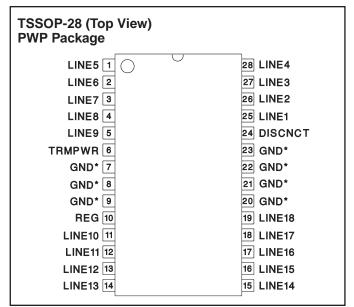

#### **CONNECTION DIAGRAMS**

\* DWP package pins 12–18 serve as both heatsink and signal ground.

Note: Drawings are not to scale.

\* PWP package pin 23 serves as signal ground; pins 7, 8, 9, 20, 21, and 22 serve as heatsink ground.

| SOIC-28 (Top View)<br>DWP Package | )         |

|-----------------------------------|-----------|

| DISCNCT 1                         | 28 GND    |

| LINE1 2                           | 27 LINE18 |

| LINE2 3                           | 26 LINE17 |

| LINE3 4                           | 25 LINE16 |

| LINE4 5                           | 24 LINE15 |

| LINE5 6                           | 23 LINE14 |

| GND* 7                            | 22 GND*   |

| GND* 8                            | 21 GND*   |

| GND* 9                            | 20 GND*   |

| LINE6 10                          | 19 LINE13 |

| LINE7 11                          | 18 LINE12 |

| LINE8 12                          | 17 LINE11 |

| LINE9 13                          | 16 LINE10 |

| TRMPWR 14                         | 16 REG    |

|                                   |           |

\* DWP package pin 28 serves as signal ground; pins 7, 8, 9, 20, 21, 22 serve as heatsink/ground.

**ELECTRICAL CHARACTERISTICS:** Unless otherwise stated these specifications apply for  $T_A = 0^{\circ}C$  to 70°C, TRMPWR = 4.75V, DISCNCT = 0V,  $T_A = T_{,I}$ .

| PARAMETER                          | TEST CONDITIONS                                                                | MIN   | TYP   | MAX   | UNITS |

|------------------------------------|--------------------------------------------------------------------------------|-------|-------|-------|-------|

| Supply Current Section             |                                                                                |       |       |       |       |

| TERMPWR Supply Current             | All Termination Lines = Open                                                   |       | 1     | 2     | mA    |

|                                    | All Termination Lines = 0.2V                                                   |       | 420   | 440   | mA    |

| Power Down Mode                    | DISCNCT = TRMPWR                                                               |       | 50    | 100   | μΑ    |

| Output Section (Termination Lines) |                                                                                |       |       |       |       |

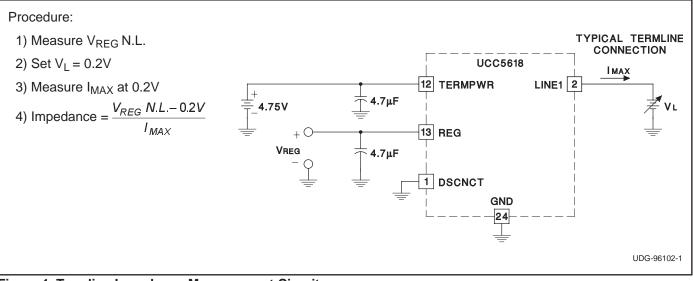

| Termination Impedance              | See Figure 1                                                                   | 104.5 | 110   | 115.5 | Ω     |

| Output High Voltage                | V <sub>TRMPWR</sub> = 4V (Note 1)                                              | 2.6   | 2.8   | 3     | V     |

| Max Output Current                 | $V_{\text{LINE}} = 0.2V, T_{\text{J}} = 25^{\circ}\text{C}$                    | -22.1 | -23.3 | -24   | mA    |

|                                    | $V_{LINE} = 0.2V$                                                              | -20.7 | -23.3 | -24   | mA    |

|                                    | $V_{\text{LINE}} = 0.2V$ , TERMPWR = 4V, T <sub>J</sub> = 25°C<br>(Note 1)     | -21   | -23.3 | -24   | mA    |

|                                    | V <sub>LINE</sub> = 0.2V, TRMPWR = 4V (Note 1)                                 | -20   | -23   | -24   | mA    |

|                                    | $V_{LINE} = 0.5V$                                                              |       |       | -22.4 | mA    |

| Output Leakage                     | DISCNCT = 2.4V, TRMPWR = 0V to 5.25V,<br>REG = 0.2V, V <sub>LINE</sub> = 5.25V |       | 10    | 400   | nA    |

| Output Capacitance                 | DISCNCT = 2.4V (Note 2)                                                        |       | 2     | 3.5   | pF    |

| Regulator Section                  |                                                                                |       |       |       |       |

| Regulator Output Voltage           |                                                                                | 2.6   | 2.8   | 3     | V     |

| Drop Out Voltage                   | All Termination Lines = 0.2V                                                   |       | 0.4   | 0.8   | V     |

| Short Circuit Current              | V <sub>REG</sub> = 0V                                                          | -475  | -650  | -950  | mA    |

| Sinking Current Capability         | V <sub>REG</sub> = 3.5V                                                        | 200   | 400   | 800   | mA    |

| Thermal Shutdown                   |                                                                                |       | 170   |       | °C    |

| Thermal Shutdown Hysteresis        |                                                                                |       | 10    |       | °C    |

| Disconnect Section                 |                                                                                |       |       |       |       |

| Disconnect Threshold               |                                                                                | 0.8   | 1.5   | 2     | V     |

| Input Current                      | DISCNCT = 0V                                                                   |       | -10   | -30   | μA    |

Note 1: Measuring each termination line while other 17 are low (0.2V). Note 2: Guaranteed by design. Not 100% tested in production.

Figure 1. Termline Impedance Measurement Circuit

**LINE1–LINE18:**  $110\Omega$  termination channels.

REG: Output of the internal 2.8V regulator.

TRMPWR: Power for the IC.

#### **PIN DESCRIPTIONS**

**DISCNCT:** Taking this pin high or leaving it open causes the 18 channels to become high impedance and the chip to go into low-power mode; a low state allows the channels to provide normal termination.

**GND:** Ground reference for the IC.

**APPLICATION INFORMATION**

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated