# 2.5-V/3.3-V OSCILLATOR GAIN STAGE/BUFFERS

## **FEATURES**

- Low-Voltage PECL Input and Low-Voltage PECL or LVDS Outputs

- Clock Rates to 2 GHz

- 140-ps Output Transition Times

- 0.11 ps Typical Intrinsic Phase Jitter

- Less than 630 ps Propagation Delay Times

- 2.5-V or 3.3-V Supply Operation

• 2-mm × 2-mm Small-Outline No-Lead Package

### APPLICATIONS

- PECL-to-LVDS Translation

- Clock Signal Amplification

# DESCRIPTION

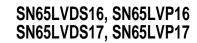

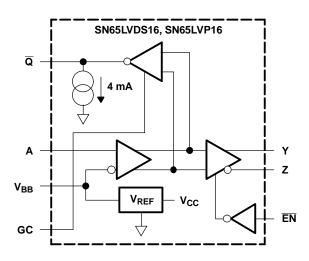

These four devices are high-frequency oscillator gain stages supporting both LVPECL or LVDS on the high gain outputs in 3.3-V or 2.5-V systems. Additionally, provides the option of both single-ended input (PECL levels on the SN65LVx16) and fully differential inputs on the SN65LVx17.

The SN65LVx16 provides the user a Gain Control (GC) for controlling the  $\overline{Q}$  output from 300 mV to 860 mV either by leaving it open (NC), grounded, or tied to V<sub>CC</sub>. (When left open, the  $\overline{Q}$  output defaults to 575 mV.) The  $\overline{Q}$  on the SN65LVx17 defaults to 575 mV as well.

Both devices provide a voltage reference ( $V_{BB}$ ) of typically 1.35 V below  $V_{CC}$  for use in receiving single-ended PECL input signals. When not used,  $V_{BB}$  should be unconnected or open.

All devices are characterized for operation from -40°C to 85°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

A

### SN65LVDS16, SN65LVP16 SN65LVDS17, SN65LVP17 SLLS625B-SEPTEMBER 2004-REVISED NOVEMBER 2005

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### **AVAILABLE OPTIONS(1)**

| INPUT        | OUTPUT | GAIN CONTROL | BASE PART NUMBER | PART MARKING |

|--------------|--------|--------------|------------------|--------------|

| Single-ended | LVDS   | Yes          | SN65LVDS16       | EL           |

| Single-ended | LVPECL | Yes          | SN65LVP16        | EK           |

| Differential | LVDS   | No           | SN65LVDS17       | EN           |

| Differential | LVPECL | No           | SN65LVP17        | EM           |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

## **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted) <sup>(1)</sup>

|                 |                                            | UNIT                                |

|-----------------|--------------------------------------------|-------------------------------------|

| V <sub>CC</sub> | Supply voltage <sup>(2)</sup>              | –0.5 V to 4 V                       |

| VI              | Input voltage                              | –0.5 V to V <sub>CC</sub> + 0.5 V   |

| Vo              | Output voltage                             | –0.5 V to V <sub>CC</sub> + 0.5 V   |

| I <sub>O</sub>  | V <sub>BB</sub> output current             | ±0.5 mA                             |

|                 | HBM electrostatic discharge <sup>(3)</sup> | ±3 kV                               |

|                 | CDM electrostatic discharge <sup>(4)</sup> | ±1500 V                             |

|                 | Continuous power dissipation               | See Power Dissipation Ratings Table |

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values, except differential voltages, are with respect to network ground see Figure 1).

(3) Tested in accordance with JEDEC Standard 22, Test Method A114-A-7

(4) Tested in accordance with JEDEC Standard 22, Test Method C101

### **DISSIPATION RATINGS**

| PACKAGE | CIRCUIT BOARD MODEL   | T <sub>A</sub> ≤ 25°C<br>POWER RATING | DERATING FACTOR<br>ABOVE $T_A = 25^{\circ}C^{(1)}$ | T <sub>A</sub> = 85°C<br>POWER RATING |

|---------|-----------------------|---------------------------------------|----------------------------------------------------|---------------------------------------|

| DRF     | Low-K <sup>(2)</sup>  | 403 mW                                | 4.0 mW/°C                                          | 161 mW                                |

| DKF     | High-K <sup>(3)</sup> | 834 mW                                | 8.3 mW/°C                                          | 333 mW                                |

(1) This is the inverse of the junction-to-ambient thermal resistance when board-mounted and with no air flow.

(2) In accordance with the Low-K thermal metric definitions of EIA/JESD51-3.

(3) In accordance with the High-K thermal metric definitions of EIA/JESD51-7.

# THERMAL CHARACTERISTICS

over operating free-air temperature range (unless otherwise noted)

|                      | PARAMETER                           |           | TEST CONDITIONS                                             | VALUE | UNIT |  |

|----------------------|-------------------------------------|-----------|-------------------------------------------------------------|-------|------|--|

| $\theta_{JB}$        | Junction-to-board thermal resistan  | се        |                                                             | 93.3  | °C/W |  |

| $\theta_{\text{JC}}$ | Junction-to-case thermal resistance | e         |                                                             | 101.7 | C/VV |  |

|                      |                                     | Turnianal | V <sub>CC</sub> = 3.3 V, T <sub>A</sub> = 25°C, 2 GHz, LVDS | 132   |      |  |

| <b>D</b>             | Device power discipation            | Typical   | $V_{CC}$ = 3.3 V, $T_A$ = 25°C, 2 GHz, LVPECL               | 83    | mW   |  |

| PD                   | Device power dissipation            | Maximum   | V <sub>CC</sub> = 3.6 V, T <sub>A</sub> = 85°C, 2 GHz, LVDS | 173   | mvv  |  |

|                      |                                     | waximum   | $V_{CC}$ = 3.6 V, $T_A$ = 85°C, 2 GHz, LVPECL               | 108   |      |  |

### **RECOMMENDED OPERATING CONDITIONS**

|                |                                                                  |                         | MIN                    | NOM        | MAX                    | UNIT |

|----------------|------------------------------------------------------------------|-------------------------|------------------------|------------|------------------------|------|

| $V_{CC}$       | Supply voltage                                                   |                         | 2.375                  | 2.5 or 3.3 | 3.6                    | V    |

| VIC            | Common-mode input voltage (V <sub>IA</sub> + V <sub>IB</sub> )/2 | SN65LVDS17 or SN65LVP17 | 1.2                    |            | $V_{CC} - (V_{ID}/2)$  | V    |

| $ V_{ID} $     | Differential input voltage magnitude $ V_{IA} - V_{IB} $         | SN65LVDS17 or SN65LVP17 | 0.08                   |            | 1                      | V    |

| V              | Ligh lowed input voltage to $\overline{EN}$                      | EN                      | 2                      |            | V <sub>CC</sub>        | V    |

| VIH            | High-level input voltage to EN                                   | SN65LVDS16 or SN65LVP16 | V <sub>CC</sub> - 1.17 |            | V <sub>CC</sub> - 0.44 | v    |

| V              |                                                                  | EN                      | 0                      |            | 0.8                    | V    |

| VIL            | Low-level input voltage to EN                                    | SN65LVDS16 or SN65LVP16 | V <sub>CC</sub> - 2.25 |            | V <sub>CC</sub> - 1.52 | v    |

| I <sub>O</sub> | Output current to V <sub>BB</sub>                                |                         | -400 <sup>(1)</sup>    |            | 400                    | μA   |

| $R_L$          | Differential load resistance,                                    | 90                      |                        | 132        | Ω                      |      |

| T <sub>A</sub> | Operating free-air temperature                                   |                         | -40                    |            | 85                     | °C   |

(1) The algebraic convention, where the least positive (more negative) value is designated minimum, is used in this data sheet.

### **ELECTRICAL CHARACTERISTICS**

over recommended operating conditions (unless otherwise noted)

|                                      | PARAMETER                                                                        | TEST CONDITIONS                                                                     | MIN                    | TYP <sup>(1)</sup>     | MAX                    | UNIT |

|--------------------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------------|------------------------|------------------------|------|

|                                      | Supply surrent                                                                   | $R_L = 100 \Omega$ , $\overline{EN}$ at 0 V,<br>Other inputs open                   |                        | 40                     | 48                     |      |

| Icc                                  | Supply current                                                                   | Outputs unloaded,<br>EN at 0 V, Other inputs open                                   |                        | 25                     | 30                     | mA   |

| V <sub>BB</sub>                      | Reference voltage <sup>(2)</sup>                                                 | I <sub>BB</sub> = -400 μA                                                           | V <sub>CC</sub> - 1.44 | V <sub>CC</sub> - 1.35 | V <sub>CC</sub> - 1.25 | V    |

| I <sub>IH</sub>                      | High-level input current, EN                                                     | V <sub>1</sub> = 2 V                                                                | -20                    |                        | 20                     |      |

| I <sub>IAH</sub> or I <sub>IBH</sub> | High-level input current, A or B                                                 | $V_{I} = V_{CC}$                                                                    | -20                    |                        | 20                     |      |

| IIL                                  | Low-level input current, EN                                                      | V <sub>I</sub> = 0.8 V                                                              | -20                    |                        | 20                     | μA   |

| $I_{IAL}$ or $I_{IBL}$               | Low-level input current, A or B                                                  | V <sub>I</sub> = GND                                                                | -20                    |                        | 20                     |      |

| SN65LVDS1                            | 6/17 Y AND Z OUTPUT CHARACTER                                                    | ISTICS                                                                              |                        |                        |                        |      |

| V <sub>OD</sub>                      | Differential output voltage magnitude, $ V_{OY} - V_{OZ} $                       |                                                                                     | 247                    | 340                    | 454                    | mV   |

| $\Delta  V_{OD} $                    | Change in differential output voltage magnitude between logic states             | See Figure 1 and Figure 2                                                           |                        |                        | 50                     | mv   |

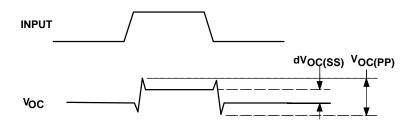

| V <sub>OC(SS)</sub>                  | Steady-state common-mode output voltage (see Figure 3)                           |                                                                                     | 1.125                  |                        | 1.375                  | V    |

| $\Delta V_{OC(SS)}$                  | Change in steady-state common-<br>mode output voltage between logic<br>states    | See Figure 3                                                                        | -50                    |                        | 50                     | mV   |

| V <sub>OC(PP)</sub>                  | Peak-to-peak common-mode output voltage                                          |                                                                                     |                        | 50                     | 100                    |      |

| $I_{\rm OYZ}$ or $I_{\rm OZZ}$       | High-impedance output current                                                    | $\overline{\text{EN}}$ at V <sub>CC</sub> , V <sub>O</sub> = 0 V or V <sub>CC</sub> | -1                     |                        | 1                      | μA   |

| $I_{\rm OYS}$ or $I_{\rm OZS}$       | Short-circuit output current                                                     | $\overline{\text{EN}}$ at 0 V, V <sub>OY</sub> or V <sub>OZ</sub> = 0 V             | -62                    |                        | 62                     |      |

| I <sub>OS(D)</sub>                   | Differential short-circuit<br>output current,  I <sub>OY</sub> - I <sub>OZ</sub> | EN at 0 V, V <sub>OY</sub> = V <sub>OZ</sub>                                        | -12                    |                        | 12                     | mA   |

# SN65LVDS16, SN65LVP16 SN65LVDS17, SN65LVP17

SLLS625B-SEPTEMBER 2004-REVISED NOVEMBER 2005

### **ELECTRICAL CHARACTERISTICS (continued)**

over recommended operating conditions (unless otherwise noted)

| PARAMETER                               |                                                            | TEST CONDITIONS                                                                     | MIN                    | TYP <sup>(1)</sup>     | MAX                    | UNIT |

|-----------------------------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------------|------------------------|------------------------|------|

| SN65LVP16                               | /17 Y AND Z OUTPUT CHARACTERIS                             | TICS                                                                                | <u> </u>               |                        |                        |      |

| V <sub>OYH</sub> or<br>V <sub>OZH</sub> | High-level output voltage                                  | 3.3 V; 50 $\Omega$ from Y and Z                                                     | V <sub>CC</sub> - 1.05 |                        | V <sub>CC</sub> - 0.82 |      |

| V <sub>OYL</sub> or<br>V <sub>OZL</sub> | Low-level output voltage                                   | to V <sub>CC</sub> - 2 V                                                            | V <sub>CC</sub> - 1.83 |                        | V <sub>CC</sub> - 1.57 | V    |

| V <sub>OYL</sub> or<br>V <sub>OZL</sub> | Low-level output voltage                                   | 2.5 V; 50 $\Omega$ from Y and Z to V <sub>CC</sub> – 2 V                            | V <sub>CC</sub> - 1.88 |                        | V <sub>CC</sub> - 1.57 | v    |

| V <sub>OD</sub>                         | Differential output voltage magnitude, $ V_{OH}\!-V_{OL} $ |                                                                                     | 0.6                    | 0.8                    | 1                      |      |

| $I_{OYZ} \text{ or } I_{OZZ}$           | High-impedance output current                              | $\overline{\text{EN}}$ at V <sub>CC</sub> , V <sub>O</sub> = 0 V or V <sub>CC</sub> | -1                     |                        | 1                      | μA   |

|                                         | CHARACTERISTICS (see Figure 1)                             |                                                                                     |                        |                        |                        |      |

| V <sub>OH</sub>                         | High-level output voltage                                  | No load                                                                             |                        | V <sub>CC</sub> - 0.94 |                        | V    |

|                                         |                                                            | GC Tied to GND, No load                                                             |                        | V <sub>CC</sub> - 1.22 |                        |      |

| V <sub>OL</sub>                         | Low-level output voltage                                   | GC Open, No load                                                                    |                        | V <sub>CC</sub> - 1.52 |                        | V    |

|                                         |                                                            | GC Tied to V <sub>CC</sub> , No load                                                |                        | V <sub>CC</sub> - 1.82 |                        |      |

|                                         |                                                            | GC Tied to GND                                                                      |                        | 300                    |                        |      |

| V <sub>O(pp)</sub>                      | Peak-to-peak output voltage                                | GC Open                                                                             |                        | 575                    |                        | mV   |

|                                         |                                                            | GC Tied to V <sub>CC</sub>                                                          |                        | 860                    |                        |      |

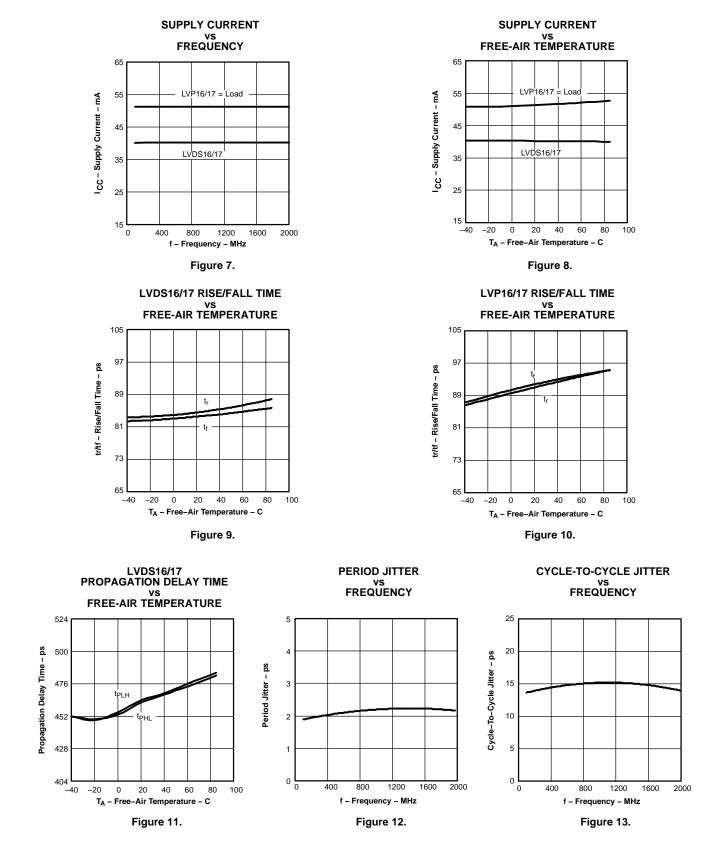

### SWITCHING CHARACTERISTICS

over recommended operating conditions (unless otherwise noted)

|                       | PARAMETER                                                      |             | TEST CONDITIONS                         | MIN | TYP <sup>(1)</sup> | MAX | UNIT |

|-----------------------|----------------------------------------------------------------|-------------|-----------------------------------------|-----|--------------------|-----|------|

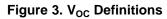

|                       | Propagation dology time to ar t                                | A to Q      |                                         |     | 340                | 460 |      |

| t <sub>PD</sub>       | Propagation delay time, $t_{PLH}$ or $t_{PHL}$                 | D to Y or Z | See Figure 4                            |     | 460                | 630 | ps   |

| t <sub>SK(P)</sub>    | Pulse skew,  t <sub>PLH</sub> t <sub>PHL</sub>                 |             |                                         |     |                    | 20  |      |

| +                     | Part-to-part skew <sup>(2)</sup>                               |             | V <sub>CC</sub> = 3.3 V                 |     |                    | 80  | 20   |

| t <sub>SK(PP)</sub>   | Fait-to-pait skew                                              |             | $V_{CC} = 2.5 V$                        |     |                    | 130 | ps   |

| t <sub>r</sub>        | 20%-to-80% differential signal rise tin                        | ne          | See Figure 4                            |     | 85                 | 140 | ps   |

| t <sub>f</sub>        | 20%-to-80% differential signal fall tim                        | ne          | See Figure 4                            |     | 85                 | 140 | ps   |

| t <sub>jit(per)</sub> | RMS period jitter <sup>(3)</sup>                               |             | 2-GHz 50%-duty-cycle square-wave input, |     | 2                  | 3   | 20   |

| t <sub>jit(cc)</sub>  | Peak cycle-to-cycle jitter <sup>(4)</sup>                      |             | See Figure 5                            |     | 15                 | 23  | ps   |

| t <sub>jit(ph)</sub>  | Intrinsic phase jitter                                         |             | 2 GHz                                   |     | 0.11               |     | ps   |

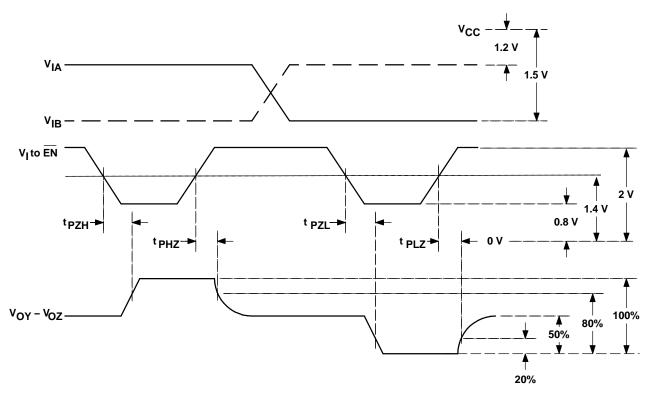

| t <sub>PHZ</sub>      | Propagation delay time,<br>high-level-to-high-impedance output |             |                                         |     |                    | 30  |      |

| t <sub>PLZ</sub>      | Propagation delay time,<br>low-level-to-high-impedance output  |             |                                         |     |                    | 30  |      |

| t <sub>PZH</sub>      | Propagation delay time,<br>high-impedance-to-high-level output |             | - See Figure 6                          |     |                    | 30  | ns   |

| t <sub>PZL</sub>      | Propagation delay time,<br>high-impedance-to-low-level output  |             |                                         |     |                    | 30  |      |

(1)

Typical values are at room temperature and with a  $V_{CC}$  of 3.3 V. Part-to-part skew is the magnitude of the difference in propagation delay times between any specified terminals of two devices when (2) both devices operate with the same supply voltages, at the same temperature, and have identical packages and test circuits.

Period jitter is the deviation in cycle time of a signal with respect to the ideal period over a random sample of 100,000 cycles. Cycle-to-cycle jitter is the variation in cycle time of a signal between adjacent cycles, over a random sample of 1,000 adjacent cycle (3) (4)

pairs.

#### PARAMETER MEASUREMENT INFORMATION

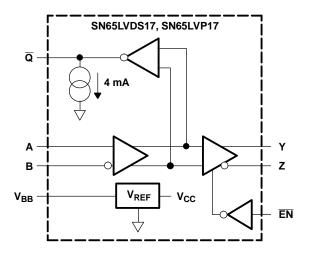

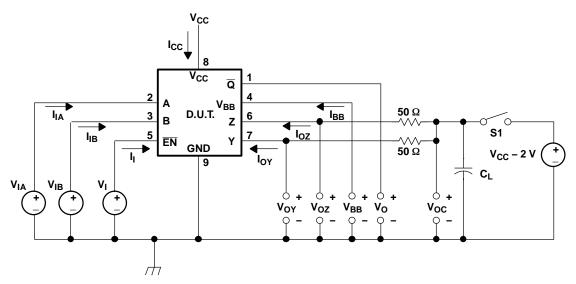

- (1)  $C_L$  is the instrumentation and test fixture capacitance.

- (2) S1 is open for the SN65LVDS16 and closed for the SN65LVP16.

Figure 1. Output Voltage Test Circuit and Voltage and Current Definitions for LVDS/LVP16

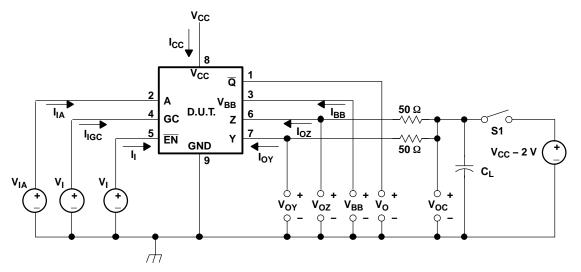

- (1)  $C_L$  is the instrumentation and test fixture capacitance.

- (2) S1 is open for the SN65LVDS17 and closed for the SN65LVP17.

Figure 2. Output Voltage Test Circuit and Voltage and Current Definitions for LVDS/LVP17

SN65LVDS16, SN65LVP16 SN65LVDS17, SN65LVP17 TEXAS INSTRUMENTS www.ti.com

SLLS625B-SEPTEMBER 2004-REVISED NOVEMBER 2005

#### PARAMETER MEASUREMENT INFORMATION (continued)

Figure 4. Propagation Delay and Transition Time Test Waveforms

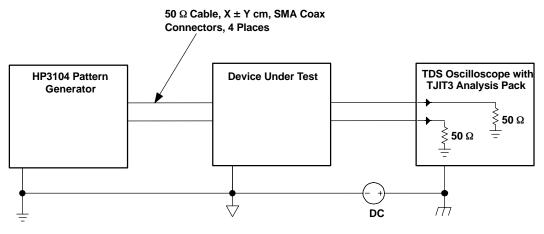

Figure 5. Jitter Measurement Setup

Figure 6. Enable and Disable Time Test Waveforms

TEXAS INSTRUMENTS www.ti.com

SLLS625B-SEPTEMBER 2004-REVISED NOVEMBER 2005

# **DEVICE INFORMATION**

#### **FUNCTION TABLE**

| SN65LVDS16, SN65LVP16 <sup>(1)</sup> |      |   |   |   | SN65LVDS17, SN65LVP17 <sup>(1)</sup> |      |      |   |   |   |

|--------------------------------------|------|---|---|---|--------------------------------------|------|------|---|---|---|

| Α                                    | EN   | Q | Y | Z | Α                                    | В    | EN   | Q | Y | Z |

| Н                                    | L    | L | Н | L | Н                                    | Н    | L    | ? | ? | ? |

| L                                    | L    | Н | L | Н | L                                    | Н    | L    | Н | L | Н |

| Х                                    | Н    | ? | Z | Z | Н                                    | L    | L    | L | н | L |

| Open                                 | L    | ? | ? | ? | L                                    | L    | L    | ? | ? | ? |

| Х                                    | Open | ? | ? | ? | Х                                    | Х    | Н    | ? | Z | Z |

|                                      |      |   |   |   | Open                                 | Open | L    | ? | ? | ? |

|                                      |      |   |   |   | Х                                    | Х    | Open | ? | ? | ? |

(1) H = high, L = low, Z = high impedance, ? = indeterminate

### Package Pin Assignments - Numerical Listing

| SN65LVDS1 | 6, SN65LVP16    | SN65LVDS17 | , SN65LVP17     |

|-----------|-----------------|------------|-----------------|

| PIN       | SIGNAL          | PIN        | SIGNAL          |

| 1         | Q               | 1          | Q               |

| 2         | А               | 2          | А               |

| 3         | V <sub>BB</sub> | 3          | В               |

| 4         | GC              | 4          | V <sub>BB</sub> |

| 5         | EN              | 5          | EN              |

| 6         | Z               | 6          | Z               |

| 7         | Y               | 7          | Y               |

| 8         | V <sub>CC</sub> | 8          | V <sub>CC</sub> |

| 9         | GND             | 9          | GND             |

#### **TYPICAL CHARACTERISTICS**

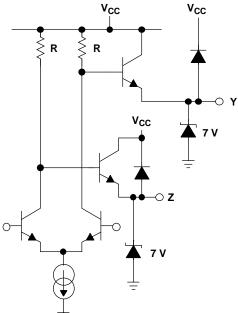

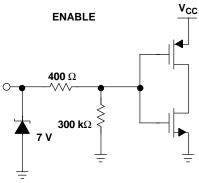

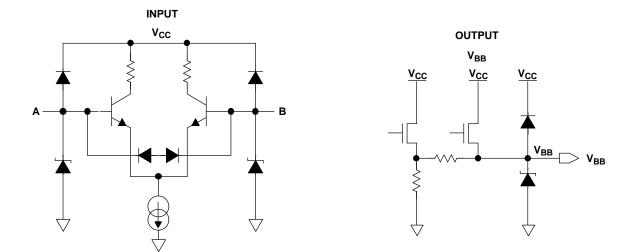

# EQUIVALENT INPUT AND OUTPUT SCHEMATIC DIAGRAMS

#### OUTPUT LVP16/17

#

OUTPUT LVDS16/17

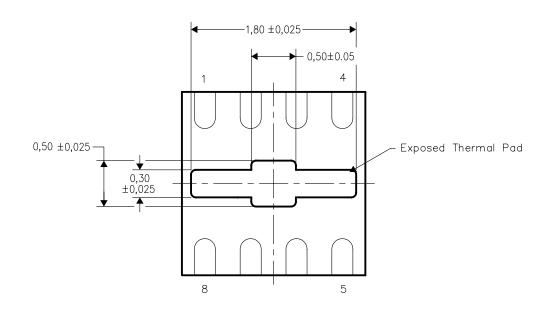

# THERMAL PAD MECHANICAL DATA

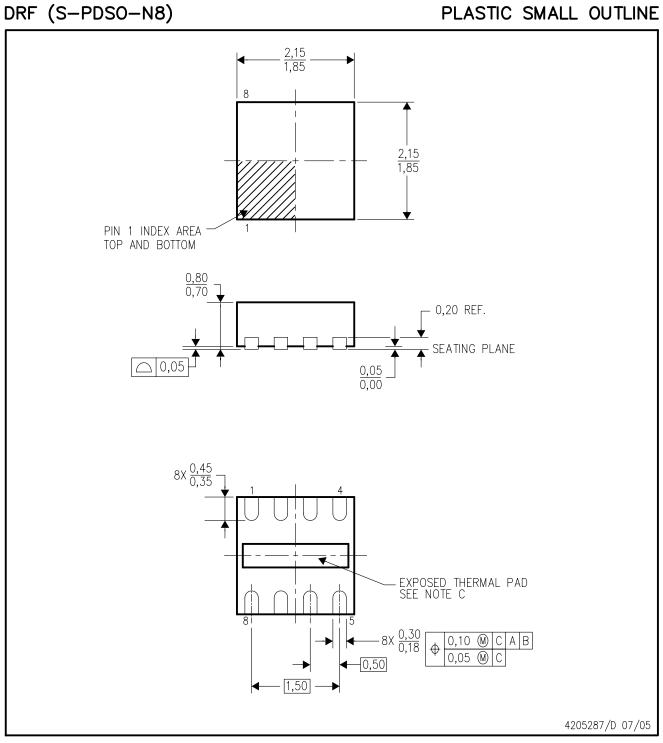

# DRF (S-PDSO-N8)

#### THERMAL INFORMATION

This package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB), the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to a ground plane or special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For information on the Quad Flatpack No-Lead (QFN) package and its advantages, refer to Application Report, Quad Flatpack No-Lead Logic Packages, Texas Instruments Literature No. SCBA017. This document is available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

NOTE: All linear dimensions are in millimeters

Exposed Thermal Pad Dimensions

17-Nov-2005

# **PACKAGING INFORMATION**

MENTS

www ti com

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|---------------------------|------------------|------------------------------|

| SN65LVDS16DRFR   | ACTIVE                | SON             | DRF                | 8    | 3000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| SN65LVDS16DRFRG4 | ACTIVE                | SON             | DRF                | 8    | 3000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| SN65LVDS16DRFT   | ACTIVE                | SON             | DRF                | 8    | 250            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| SN65LVDS16DRFTG4 | ACTIVE                | SON             | DRF                | 8    | 250            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| SN65LVDS17DRFR   | ACTIVE                | SON             | DRF                | 8    | 3000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| SN65LVDS17DRFRG4 | ACTIVE                | SON             | DRF                | 8    | 3000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| SN65LVDS17DRFT   | ACTIVE                | SON             | DRF                | 8    | 250            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| SN65LVDS17DRFTG4 | ACTIVE                | SON             | DRF                | 8    | 250            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| SN65LVP16DRFR    | ACTIVE                | SON             | DRF                | 8    | 3000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| SN65LVP16DRFRG4  | ACTIVE                | SON             | DRF                | 8    | 3000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| SN65LVP16DRFT    | ACTIVE                | SON             | DRF                | 8    | 250            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| SN65LVP16DRFTG4  | ACTIVE                | SON             | DRF                | 8    | 250            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| SN65LVP17DRFR    | ACTIVE                | SON             | DRF                | 8    | 3000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| SN65LVP17DRFRG4  | ACTIVE                | SON             | DRF                | 8    | 3000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| SN65LVP17DRFT    | ACTIVE                | SON             | DRF                | 8    | 250            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| SN65LVP17DRFTG4  | ACTIVE                | SON             | DRF                | 8    | 250            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

<sup>(1)</sup> The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS) or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined. **Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that a

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **MECHANICAL DATA**

PLASTIC SMALL OUTLINE

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. The Package thermal pad must be soldered to the board for thermal and mechanical performance.

- See product data sheet for details regarding the exposed thermal pad dimensions.

- D. Falls within JEDEC MO-229.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address:

Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2005, Texas Instruments Incorporated