## Preliminary

## ULTIMATEBLUE™ RADIO PROCESSOR

#### Features

- Single-chip IC with 2.4 GHz transceiver, baseband processor, and on-chip protocol stack for Bluetooth® wireless technology

- Fully compliant with Bluetooth specification 1.1 and forward compatible via software upgrade with specified 1.2 features.

- Low cost 0.18 µm CMOS process technology.

- 1.8 V analog and digital core voltages; 1.62 V to 3.63 V external I/O interface voltage.

- Typical -85 dBm receiver sensitivity, +2 dBm transmitter power for up to 100 meters nominal range.

- On-chip VCO and PLL support multiple GSM/GPRS and CDMA cellular reference clock frequencies.

- Hardware AGC dynamically adjusts receiver performance in changing environments.

- Integrated 32-bit ARMTDMI® processor for extended features.

- Full piconet connectivity with support for up to 7 active and 8 parked slaves.

- Scatternet compatible with Microsoft® HID devices.

- Supports three SCO voice channels.

- Channel Quality Driven Data Rate (CQDDR) controls multi-slot packets to minimize packet overhead and maximize data throughput.

- Option for Bluetooth + Wi-Fi coexistence.

#### Applications

- Mobile phones.

- Notebook and desktop PCs.

- Cordless headsets.

- Personal digital assistants (PDAs).

- Computer accessories, peripherals, and wireless printers/ keyboards/mice).

Crystal or Reference Clock

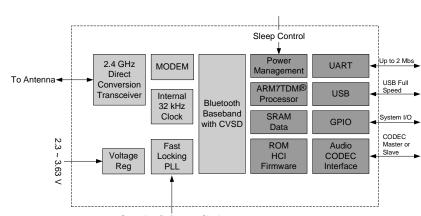

#### **Block Diagram**

## **Product Description**

The SiW3000 UltimateBlue<sup>™</sup> Radio Processor is the most recent innovation for Bluetooth® wireless technology. It combines the industry's best performing and most highly integrated radio design with an ARMTDMI® processor using CMOS technology. The SiW3000 uses direct conversion (zero-IF) architecture. This allows digital filtering for excellent interference rejection as compared to low IF solutions and also results in fewer spurious responses.

The lower-layer protocol stack software is integrated into the on-chip ROM. Optional external Flash memory is also supported. The SiW3000 is compliant with Bluetooth specification 1.1 and forward compatible via software upgrade with specified 1.2 features.

The device is available in a 96-pin thin VFBGA package with by  $6 \times 6 \times 1 \text{ mm}$  dimensions and a guaranteed operating temperature range from -40°C to +85°C and extended high temperature range available to +105°C.

#### **Ordering Information**

SiW3000

UltimateBlue™ Radio Processor

RF Micro Devices, Inc. 7628 Thorndike Road Greensboro, NC 27409, USA Tel (336) 664 1233 Fax (336) 664 0454 http://www.rfmd.com

## Optimum Technology Matching® Applied

□

Si BJT

□

GaAs HBT

□

GaAs MESFET

□

Si Bi-CMOS

□

SiGe HBT

✓

Si CMOS

□

GaInP/HBT

□

GaN HEMT

□

SiGe Bi-CMOS

## Preliminary

# SiW3000

## **Radio Features**

- Direct-conversion architecture with no external IF filter or VCO resonator components.

- Single ended RF I/O reduces system bill of materials (BOM) costs by eliminating the need to use external balun and switch circuits.

- On-chip VCO and PLL support multiple GSM, CDMA, GPRS standard reference clock frequencies.

- Low out-of-band spurious emission transmitter prevents blocking of sensitive mobile phone RF circuits.

- No tuning during production.

- Internal temperature compensation circuit stabilizes performance across wide operating temperature.

- Fast settling synthesizer reduces power consumption.

- Up to 100 meter operating range in standard configuration without using an external PA.

## **Baseband Features**

- ARM7TDMI processor core running at 16 MHz.

- Digital GFSK modem for maximum performance and lower packet error rate.

- On-chip CVSD conversion with hardware based gain adjustments to enhance audio quality.

- Sleep control interface for low power operation modes.

- Software execution from ROM or external FLASH memory.

## **Standard Protocol Stack Features**

- Bluetooth 1.1 compliant with Bluetooth 1.2 features that can be enabled by setting the Bluetooth 1.2 system configuration parameters.

- Full piconet connectivity with support for up to 7 active and 8 parked slaves.

- Able to establish up to 3 SCO connections.

- Scatternet capable and compatible with Microsoft HID devices.

- Standard Bluetooth test modes.

- Low power connection states supported with hold, sniff, and park modes.

## **Additional Protocol Stack Features**

- Channel Quality Driven Data Rate (CQDDR) optimizes data transfer rate in noisy or weak signal environments

- Audio (SCO) routing over HCI interface for VOIP applications.

- Support for Bluetooth + Wi-Fi coexistence technology.

- Verified compatibility with multiple upper-layer stack vendors.

- Extensive vendor specific HCI commands enables hardware specific controls.

- Optional upper-layer stack and profiles can be licensed and integrated into the IC.

## **Bluetooth 1.2 Features**

Forward compatible with the upcoming Bluetooth specification 1.2. When ratified, the additional features found in this specification can be enabled and include the following:

- Adaptive frequency hopping (AFH).

- Faster connections.

- Absence masks.

- LMP improvements.

- Anonymity mode.

### **External System Interfaces**

#### Host HCI Transport (H:2 USB)

The USB device interface provides a physical transport between the SiW3000 and the host for the transfer of Bluetooth control signals and data. This transport layer is fully compliant with Section H:2 of the Bluetooth specification with all end points supported. The SiW3000 USB interface encompasses three I/O signals: USB\_DPLS, USB\_DMNS, and USB\_DPLS\_PULLUP. If the USB transport is not used, the USB\_DPLS and USB\_DMNS pins should be grounded to reduce current consumption.

#### Host HCI Transport (H:4 UART)

The high speed UART interface provides the physical transport between the SiW3000 and the application host for the transfer of Bluetooth control signals and data compliant to Section H:4 of the Bluetooth specification. Table 1 shows the supported baud rates. The default baud rate is 115,200, but can be configured depending on the application.

| SiW3000 Radio Processor HCI UART Parameters         | Required Host Setting                                                                              |

|-----------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Number of data bits                                 | 8                                                                                                  |

| Parity bit                                          | No parity                                                                                          |

| Stop bit                                            | 1 stop bit                                                                                         |

| Flow control                                        | RTS/CTS                                                                                            |

| Host flow-off response requirement from the SiW3000 | 8 bytes                                                                                            |

| SiW3000 IC flow-off response requirement from host  | 2 bytes                                                                                            |

| Supported baud rates                                | 9.6k, 19.2k, 38.4k, 57.6k, <b>115.2k</b> <sup>a</sup> , 230.4k, 460.8k, 500k, 921.6k, 1M, 1.5M, 2M |

#### Table 1. Host HCI Transport

a.Default baud rate.

#### Host HCI Transport (H:5 3-Wire UART)

To reduce the number of signals and to increase the reliability of the HCI UART interface, a 3-wire UART protocol is supported in the SiW3000. The selection between standard H:4 and H:5 is done automatically by the SiW3000. This is compatible with the BCSP interface.

| SiW3000 Radio Processor HCI 3-Wire UART Parameters | Required Host Setting |

|----------------------------------------------------|-----------------------|

| Number of data bits                                | 8                     |

| Parity bit                                         | Even                  |

| Stop bit                                           | 1 stop bit            |

| Error detection                                    | Slip and checksum     |

| Sleep modes                                        | Shallow and deep      |

Table 2. Host HCI 3-Wire UART

#### **Audio CODEC Interface**

The SiW3000 supports direct interface to an external audio CODEC or PCM host device. The interface is easily configured to support:

- Standard 64-kHz PCM clock rate.

- Up to 2-MHz clock rates with support for multi-slot handshakes and synchronization.

- Either master or slave (Motorola SSI) mode.

Configuration of the CODEC interface is done by the firmware during boot-up by reading non-volatile memory (NVM) parameters. The following are examples of supported CODEC modes:

- Generic 64-kHz audio CODEC (e.g., OKI MSM-7702).

- Motorola MC145481 or similar CODEC as master.

- QUALCOMM MSM chip set audio port.

- GSM/GPRS baseband IC audio ports.

#### Programmable I/O (PIO)

Up to twenty-nine (29) programmable IO (PIO) ports are available for customer use in the SiW3000. Three of these PIOs are dedicated and the remaining PIOs are shared with other functions. Availability of PIOs will depend on system configuration. The table below identifies the all twenty-nine PIOs and their usage. The PIO ports can be set to input or output. Reading, writing, and controlling the PIO pins by the host application software can be done via vendor specific HCI commands.

| PIO# | Shared I/O      | Sampled at Reset |

|------|-----------------|------------------|

| 0    | None            | Yes              |

| 1    | None            | Yes              |

| 2    | None            | Yes              |

| 3    | D[8]            | No               |

| 4    | D[4]            | No               |

| 5    | D[5]            | No               |

| 6    | D[6]            | No               |

| 7    | D[7]            | No               |

| 8    | PWR_REG_EN      | No               |

| 9    | D[15]           | No               |

| 10   | WE_N            | No               |

| 11   | A[16]           | No               |

| 12   | A[17]           | No               |

| 13   | A[11]           | No               |

| 14   | USB_DPLS_PULLUP | No               |

| PIO# | Shared I/O   | Sampled at Reset |

|------|--------------|------------------|

| 15   | PCM_OUT      | No               |

| 16   | PCM_IN       | No               |

| 17   | PCM_CLK      | No               |

| 18   | PCM_SYNC     | No               |

| 19   | EXT_WAKE     | No               |

| 20   | HOST_WAKEUP  | No               |

| 21   | UART_RXD     | No               |

| 22   | UART_TXD     | No               |

| 23   | UART_CTS     | No               |

| 24   | UART_RTS     | No               |

| 25   | A[18]        | No               |

| 26   | TX_RX_SWITCH | No               |

| 27   | D[9]         | No               |

| 28   | D[10]        | No               |

#### **External Memory Interface**

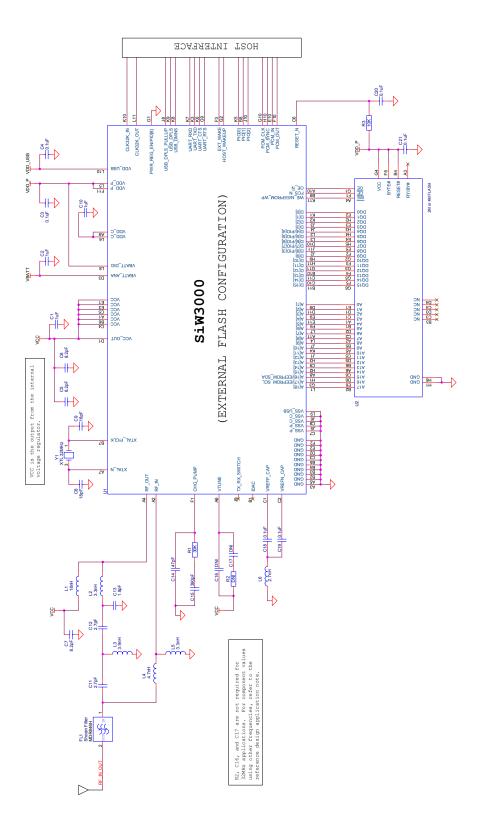

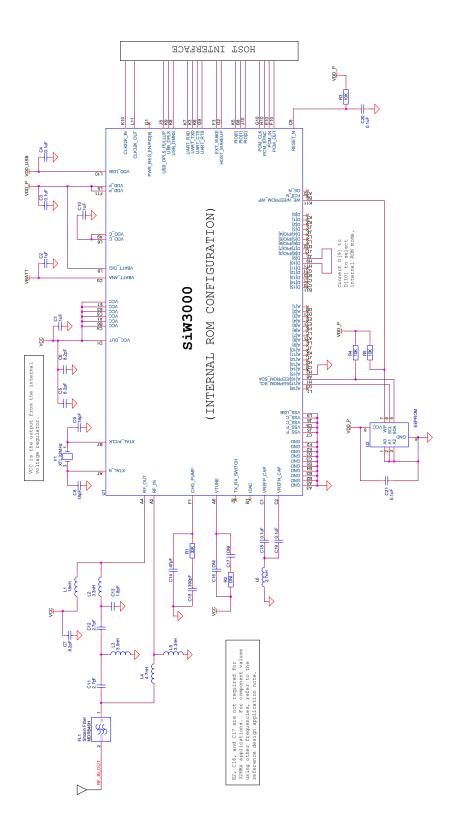

The Ultimate 3000 Radio Processor is a true single chip device and does not require additional memory for standard below HCI protocol functions. An external memory interface is available for adding optional memory. If external Flash memory will be used, the read access time of the device must be 100 ns or less.

The external memory interface permits connection to Flash and SRAM devices. The interface has an 18-bit address bus and a 16-bit data bus for a total addressable memory of 512 KB. In certain embedded applications, both SRAM and Flash can be installed by using the high order address bit as an alternate chip select.

| Signal               | Description        |

|----------------------|--------------------|

| Address A[1] - A[18] | 18-bit address bus |

| Data D[0] - D[15]    | 16-bit data bus    |

| FCS_N                | Chip select        |

| OE_N                 | Output enable      |

| WE_N                 | Write enable       |

#### **External EEPROM Controller and Interface**

This interface is intended for use with ROM-based solutions. The EEPROM is not required for configurations with external flash. The EEPROM is the non-volatile memory (NVM) in the system and contains the system configuration parameters such as the Bluetooth device address, the CODEC type, as well as other parameters. These default parameters are set at the factory, and some parameters will change depending on the system configuration. Optionally, the non-volatile memory parameters can be downloaded from the host processor at boot up eliminating the need for EEPROM. Please consult the application support team for details. The EEPROMs should have a serial I<sup>2</sup>C interface with a minimum size of 2 Kbits and 16-byte page write buffer capabilities.

#### **Power Management**

The HOST\_WAKEUP and EXT\_WAKE signals are used for power management. HOST\_WAKEUP is an output signal used to wake up the host. EXT\_WAKE is an input signal used by the host to wake up the SiW3000 Radio Processor from sleep mode. For more information on the usage of HOST\_WAKE and EXT\_WAKE, please refer to "Using the UART Interface to Silicon Wave Baseband Controllers and Radio Processors" application note.

## **System Requirements**

#### System Reference Clock

The SiW3000 chip can use either an external crystal or a reference clock as the system clock input. The supported frequencies are: 9.6 MHz, 12 MHz, 12.8 MHz, 13 MHz, 14.4 MHz, 15.36 MHz, 16 MHz, 16.8 MHz, 19.2 MHz, 19.68 MHz, 19.8 MHz, 26 MHz, 32 MHz, 38.4 MHz, and 48 MHz. The default reference frequency can be selected by setting the proper system configuration parameter in the non-volatile memory (NVM). If the USB HCI transport will be used, the reference clock must be 32 MHz.

The system reference crystal/clock must have accuracy of  $\pm 20$  PPM or better to meet the specification of Bluetooth. To facilitate design and production, the SIW3000 processor incorporates internal crystal calibration circuits to allow factory calibration of initial crystal frequency accuracy during production.

#### Low Power Clock

For the Bluetooth low power clock, a 32.768-kHz crystal may be used to drive the SiW3000 oscillator circuit, or alternatively, a 32.768-kHz reference clock signal can be used instead of a crystal. If the lowest power consumption is not required during low-power modes such as sniff, hold, park, and idle modes, the 32.768-kHz crystal may be omitted in the design.

If the 32.768-kHz clock source will be used, the clock source should be connected to the CLK32\_IN pin and must meet the following requirements:

- For AC-coupled via 100 pF or greater (peak-to-peak voltage): 400 mV\_{P-P} < CLK32\_IN < V\_{DD\_C}

- For DC-coupled:

$\label{eq:VIL} \begin{array}{l} \mathsf{VIL} < \mathsf{CLK32\_IN} < \mathsf{V_{IH}} \\ \text{Where } \mathsf{VIL} = 0.3 * \mathsf{V_{DD\_C}} \\ \text{Where } \mathsf{VIH} = 0.7 * \mathsf{V_{DD\_C}} \end{array}$

For both cases, the signal is not to exceed:  $-0.3 \text{ V} < \text{CLK32_IN} < \text{V}_{\text{DD} \text{ C}} + 0.3 \text{ V}$

Also, the CLK32\_OUT pin must be coupled to V<sub>DD P</sub> or GND through a 100 nF capacitor.

#### **Power Supply Description**

The SiW3000 Radio Processor operates at 1.8 V core voltage for internal analog and digital circuits. The chip has internal analog and digital voltage regulators simplifying power supply requirements to the chip. The internal voltage regulators can be supplied directly from a battery or from other system voltage sources. Optionally, the internal regulators can be by-passed if 1.8 V regulated source is available on the system.

| Function             | Internal Analog Regulator                         | Internal Digital Regulator     |

|----------------------|---------------------------------------------------|--------------------------------|

| Regulator input pin  | $V_{BATT_{ANA}} = 2.3 \text{ to } 3.63 \text{ V}$ | $V_{BATT_DIG}$ = 2.3 to 3.63 V |

| Regulator output pin | V <sub>CC_OUT</sub> = 1.8 V                       | V <sub>DD_C</sub> = 1.8 V      |

#### Table 3. Internal Regulator Used

| Function                   | Analog Core Circuits    | Digital Core Circuits     |

|----------------------------|-------------------------|---------------------------|

| Circuit voltage supply pin | V <sub>CC</sub> = 1.8 V | V <sub>DD_C</sub> = 1.8 V |

#### Table 4. Internal Regulator Bypassed

Note: When bypassing either the analog or the digital regulators, the  $V_{BATT_ANA}$  or the  $V_{BATT_DIG}$  pins should be tied directly to the 1.8 V source.

The power for the I/Os is taken from a separate source ( $V_{DD_P}$ ).  $V_{DD_P}$  can range from 1.62to 3.63 Volts to maintain compatibility with a wide range of peripheral devices. Please check the pin list for the exact pins that are powered from the  $V_{DD_P}$  source. Power for the USB circuits is taken from a separate source ( $V_{DD_USB}$ ).

#### **RF I/O Description**

The SiW3000 processor employs single-ended RF input and output pins for reduced external components. In typical Class-2 (0 dBm nominal) applications, simple LC network matching circuits will be required to combine the two ports into a single antenna port and provide impedance matching. Please refer to the RF impedance table and the application circuits for values and matching circuit examples. The SiW3000 can be used to design Class-1 (+20 dBm) products with the addition of power amplifier circuits. Control signals are available to facilitate the design of the external PA circuit.

#### Reset

The SiW3000 processor can be reset by asserting the RESET\_N signal to the chip (active low). Upon applying power, the RESET\_N must be asserted until voltage supply and internal voltage regulators have stabilized. A simple RC circuit can be used to provide the power-on reset signal to the SiW3000.

#### **On-Chip Memory**

The SiW3000 Radio Processor integrates both SRAM and ROM. The ROM is pre-programmed with Bluetooth protocol stack software (HCI software) and boot code that executes automatically upon reset. The boot code serves to control the boot sequence as well as to direct the execution to the appropriate memory for continued operation.

### **Configuration Selection**

#### **HCI Transport Interface Selection**

The HCI transport (USB or UART) is selected on power up by sampling PIO2. If UART is selected, the selection of the particular UART transport (H:4 or H:5) is performed automatically by the software.

| Value (PIO 2) | Description |

|---------------|-------------|

| 0             | UART        |

| 1             | USB         |

#### **Reference Frequency Selection**

The SiW3000 radio processor is designed to operate with multiple reference frequencies. During boot up the processor samples PIO pins to determine the default reference frequency. If the USB transport is selected, the default reference frequency will always be 32 MHz. If the UART transport is selected, the reference frequency setting will be set according to the following table:

| PIO 1 | USB_DPLS_PULLUP | Reference Frequency Selection                                                                               |

|-------|-----------------|-------------------------------------------------------------------------------------------------------------|

| 1     | Don't Care      | Reference frequency per NVM system configu-<br>ration setting, or if NVM is not set, defaults to<br>32 MHz. |

| 0     | 0               | 13 MHz                                                                                                      |

| 0     | 1               | 26 MHz                                                                                                      |

#### **Application Software Memory Selection**

The SiW3000 can support application (protocol stack) software execution from internal ROM and external FLASH memory. To run from internal ROM, D[9] and D[10] pins must be connected together as shown in the application circuit section of this document. To run from external FLASH memory the FLASH must be connected as shown in the application circuit diagram and contain valid application code. If an external memory does not have valid program data, the device enters a download mode in which a valid program may be loaded into the external memory through a sequence of commands over the HCI transport layer.

## **Pin Description**

The following table provides detailed listings of pin descriptions arranged by functional groupings.

| Name                | Pad Type            | Ball      | Description                                                                                                                                                                                                                                         |

|---------------------|---------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Radio (Power from   | VCC)                |           |                                                                                                                                                                                                                                                     |

| RF_IN               | Analog              | A2        | RF signal input into the receiver.                                                                                                                                                                                                                  |

| RF_OUT              | Analog              | A4        | RF signal output from the transmitter.                                                                                                                                                                                                              |

| VTUNE               | Analog              | A6        | Pin for reference PLL loop filter, only used if reference frequency is not integer multiples of 4 MHz.                                                                                                                                              |

| CHG_PUMP            | Analog              | F1        | Pin for RF loop filter.                                                                                                                                                                                                                             |

| XTAL_N              | Analog              | A7        | System clock crystal negative input. If a reference clock is used, this pin should be left unconnected.                                                                                                                                             |

| XTAL_P/CLK          | Analog              | B7        | System clock crystal positive input or reference clock input.                                                                                                                                                                                       |

| IDAC                | Analog              | B1        | Power control to external power amplifier. This output provides a variable current source that can be used to control the external power amp. Leave unconnected if not used.                                                                        |

| VREFP_CAP           | Analog              | C1        | Decoupling capacitor for internal A/D converter voltage reference.                                                                                                                                                                                  |

| VREFN_CAP           | Analog              | C2        | Decoupling capacitor for internal A/D converter voltage reference.                                                                                                                                                                                  |

| Low Power Oscillat  | or and Reset (Powe  | r from VD | D_P)                                                                                                                                                                                                                                                |

| CLK32K_IN           | Analog              | K10       | For crystal or external clock input (32.768 kHz).                                                                                                                                                                                                   |

| CLK32K_OUT          | Analog              | L11       | Drive for crystal.                                                                                                                                                                                                                                  |

| RESET_N             | Analog              | C6        | System level reset (active low).                                                                                                                                                                                                                    |

| Power Control Inter | face (Power from VI | DD_P)     |                                                                                                                                                                                                                                                     |

| PWR_REG_EN/PIO[8]   |                     | G1        | Enable for an external voltage regulator. Programmable active high or active low. Also used as PIO[8], which is the default mode until the appropriate configuration bit is set. Tie to ground if not used.                                         |

| TX_RX_SWITCH        | CMOS output         | Jð        | Output signal used to indicate the current state of the radio. This could be<br>used as a direction control for an external power amplifier. The polarity is<br>programmable with the default set as:<br>Low = Transmit mode<br>High = Receive mode |

Table 5. SiW3000 Radio Processor Pin List

# SiW3000

| Name               | Pad Type            | Ball | Description                                                                                                                                                                                                                                                         |

|--------------------|---------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Programmable I/O   | (Power from VDD_P)  | )    | · · ·                                                                                                                                                                                                                                                               |

|                    |                     |      | Programmable input/output.                                                                                                                                                                                                                                          |

| PIO[0]             | CMOS bi-directional | K5   | Needs to be low until internal reset goes high or tie to ground if not used.                                                                                                                                                                                        |

|                    |                     |      | Programmable input/output.                                                                                                                                                                                                                                          |

|                    |                     |      | Sampled following reset for frequency selection:                                                                                                                                                                                                                    |

| PIO[1]             | CMOS bi-directional | B8   | If UART transport is selected and PIO[1] = 0, frequency is selected by the state of USB_DPLS_PULLUP pin.                                                                                                                                                            |

|                    |                     |      | If UART transport is selected and $PIO[1] = 1$ , frequency is selected by NVM parameter. Default for proper UART operation will be configured as 32 MHz.                                                                                                            |

|                    |                     |      | If USB transport is selected, PIO[1] is ignored and the frequency will be configured as 32 MHz.                                                                                                                                                                     |

|                    |                     |      | Programmable input/output.                                                                                                                                                                                                                                          |

| PIO[2]             | CMOS bi-directional | J10  | Sampled following reset for transport selection:<br>PIO[2] = 0, selects UART transport<br>PIO[2] = 1, selects USB transport                                                                                                                                         |

| PCM Interface (Por | wer from VDD P)     | •    |                                                                                                                                                                                                                                                                     |

| PCM_IN             | CMOS output         | E10  | PCM data to the PCM CODEC.                                                                                                                                                                                                                                          |

| PCM_OUT            | CMOS input          | F10  | PCM data from the remote device. Normally an input.                                                                                                                                                                                                                 |

| PCM_CLK            | CMOS bi-directional | G10  | PCM synchronous data clock to the remote device.<br>Normally an output. Input for Motorola SSI slave mode.                                                                                                                                                          |

| PCM_SYNC           | CMOS bi-directional | H10  | PCM synchronization data strobe to the remote device. Normally an output. Input for Motorola SSI slave mode.                                                                                                                                                        |

| UART Interface (Po | ower from VDD_P)    |      |                                                                                                                                                                                                                                                                     |

| UART_RXD           | CMOS input          | K7   | UART receive data.                                                                                                                                                                                                                                                  |

| UART_TXD           | CMOS output         | K3   | UART transmit data.                                                                                                                                                                                                                                                 |

| UART_CTS           | CMOS input          | K6   | UART flow control clear to send.                                                                                                                                                                                                                                    |

| UART_RTS           | CMOS output         | G9   | UART flow control ready to send.                                                                                                                                                                                                                                    |

| EXT_WAKE           | CMOS input          | F3   | Wake up signal from host.                                                                                                                                                                                                                                           |

| HOST_WAKEUP        | CMOS output         | G2   | Wake up signal to host.                                                                                                                                                                                                                                             |

| USB Interface (Pow | wer from VDD_USB)   |      |                                                                                                                                                                                                                                                                     |

| USB_DPLS           | Analog              | K9   | USB differential pair positive signal.                                                                                                                                                                                                                              |

| USB_DMNS           | Analog              | K8   | USB differential pair negative signal.                                                                                                                                                                                                                              |

| USB_DPLS_PULLUP    | CMOS bi-directional | J8   | Output signal for controlling the on/off of the pull-up of the USB_DPLS<br>line.<br>For UART transport, this pin is sampled following reset for frequency<br>selection if PIO[1] = 0:<br>USB_DPLS_PULLUP = 0, selects 13 MHz<br>USB_DPLS_PULLUP = 1, selects 26 MHz |

Table 5. SiW3000 Radio Processor Pin List (Continued)

## Preliminary

| SiW3000 |

|---------|

|---------|

| Name                                                                                                                                                                        | Pad Type                                       | Ball                                                                                                               | Description                                                                                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| External Memory In                                                                                                                                                          | terface (power from                            | VDD_P)                                                                                                             |                                                                                                                                                                                                                  |

| A[18]<br>A[17]/EEPROM_SCL<br>A[16]/EEPROM_SDA<br>A[15]<br>A[14]<br>A[13]<br>A[12]<br>A[11]<br>A[10]<br>A[9]<br>A[8]<br>A[7]<br>A[6]<br>A[5]<br>A[4]<br>A[3]<br>A[2]<br>A[1] | CMOS output                                    | L1<br>G3<br>H1<br>A8<br>H2<br>C9<br>H3<br>J1<br>K4<br>J7<br>L4<br>A11<br>L7<br>F9<br>E11<br>E9<br>D11<br>D9<br>D11 | Address lines.<br>Note: A[17] and A[16] can be used to support an optional external serial<br>EEPROM when using the internal ROM in place of the external Flash<br>memory.                                       |

| D[15]<br>D[14]<br>D[13]<br>D[12]<br>D[11]<br>D[10]<br>D[9]<br>D[8]/PI0[3]<br>D[7]/PI0[7]<br>D[6]/PI0[6]<br>D[5]/PI0[5]<br>D[4]/PI0[4]<br>D[3]<br>D[2]<br>D[1]<br>D[0]       | CMOS bi-directional<br>with internal pull-down | B11<br>C10<br>C11<br>B10<br>G11<br>H11<br>H9<br>J2<br>J11<br>D10<br>L3<br>L2<br>J4<br>J3<br>K2<br>K1               | Data lines.<br><b>Note</b> : D[4] through D[8] can be used as programmable I/O when using<br>the internal ROM in place of the external Flash memory.<br><b>Note</b> : Connect D[9] to D[10] to use internal ROM. |

| OE_N                                                                                                                                                                        | CMOS output                                    | A10                                                                                                                | Output enable for external memory (active low).                                                                                                                                                                  |

| WE_N/EEPROM_WP                                                                                                                                                              | CMOS output                                    | K11                                                                                                                | Write enable for external memory (active low).<br>Note: Can be used to support an optional external serial EEPROM when<br>using the internal ROM in place of external Flash memory.                              |

| FCS_N                                                                                                                                                                       | CMOS output                                    | B9                                                                                                                 | Chip select for external memory (active low).                                                                                                                                                                    |

| Power and Ground                                                                                                                                                            |                                                |                                                                                                                    |                                                                                                                                                                                                                  |

| VBATT_ANA                                                                                                                                                                   | Power                                          | D3                                                                                                                 | Positive supply to internal analog voltage regulator.                                                                                                                                                            |

| VBATT_DIG                                                                                                                                                                   | Power                                          | L8                                                                                                                 | Positive supply to internal digital voltage regulator.                                                                                                                                                           |

| VCC_OUT                                                                                                                                                                     | Power                                          | D1                                                                                                                 | Regulated output from internal analog voltage regulator.                                                                                                                                                         |

| VDD_P                                                                                                                                                                       | Power                                          | F11<br>L5                                                                                                          | Positive supply for digital input/output ports including peripheral interface, external memory interface, and UART interface.                                                                                    |

| VDD_USB                                                                                                                                                                     | Power                                          | L10                                                                                                                | Positive supply for USB Interface.                                                                                                                                                                               |

| VDD_C                                                                                                                                                                       | Power                                          | A9                                                                                                                 | Positive supply for digital circuitry or output of internal digital voltage.                                                                                                                                     |

|                                                                                                                                                                             | Power                                          | L6<br>A1<br>B6<br>C4<br>C5                                                                                         | Positive supply for RF and analog circuitry.                                                                                                                                                                     |

| VSS_P                                                                                                                                                                       | GND                                            | C7<br>J5                                                                                                           | Ground connections for digital input/output ports including peripheral interface, external memory interface, and UART Interface.                                                                                 |

| VSS_C                                                                                                                                                                       | GND                                            | C8<br>J6                                                                                                           | Ground connections for internal digital circuitry.                                                                                                                                                               |

| VSS_USB                                                                                                                                                                     | GND                                            | L9                                                                                                                 | Ground connections for USB Interface.                                                                                                                                                                            |

Table 5. SiW3000 Radio Processor Pin List (Continued)

# SiW3000

| Name | Pad Type | Ball                                                     | Description                                     |

|------|----------|----------------------------------------------------------|-------------------------------------------------|

| GND  | GND      | A3<br>A5<br>B2<br>B3<br>B4<br>B5<br>C3<br>D2<br>E2<br>F2 | Ground connections for RF and analog circuitry. |

Table 5. SiW3000 Radio Processor Pin List (Continued)

## System Specifications Recommended Operating Conditions

| Parameter             | Description                                                                          | Min  | Max  | Unit |

|-----------------------|--------------------------------------------------------------------------------------|------|------|------|

| T <sub>OP</sub>       | Operating temperature (industrial grade)                                             | -40  | +85  | °C   |

| T <sub>EOP</sub>      | Extended operating temperature                                                       | -40  | +105 | °C   |

| T <sub>STG</sub>      | Storage temperature                                                                  | -55  | +125 | °C   |

| V <sub>BATT_ANA</sub> | Unregulated supply voltage into internal analog regulator                            | 2.3  | 3.63 | V    |

| V <sub>BATT_DIG</sub> | Unregulated supply voltage into internal digital regulator                           | 2.3  | 3.63 | V    |

| V <sub>CC</sub>       | Regulated supply voltage directly into analog circuits                               | 1.71 | 1.89 | V    |

| V <sub>DD_C</sub>     | Regulated supply voltage directly into digital circuits                              | 1.71 | 1.89 | V    |

| V <sub>DD_P</sub>     | Digital interface I/O supply voltage                                                 | 1.6  | 3.63 | V    |

| V <sub>DD_USB</sub>   | Regulated supply voltage for USB Interface to meet USB specification<br>requirements | 3.1  | 3.63 | V    |

| RF_MAX                | Maximum input level                                                                  | -    | +5   | dBm  |

### **ESD** Rating

| Symbol | Description               | Rating |

|--------|---------------------------|--------|

| ESD    | ESD protection - all pins | 2000 V |

**Note:** This device is a high performance RF integrated circuit with an ESD rating of 2,000 volts (HBM conditions per Mil-Std-883, Method 3015). Handling and assembly of this device should only be done using appropriate ESD controlled processes.

## **Electrical Characteristics**

#### DC Specification (T<sub>OP</sub>=+25°C, V<sub>DD\_P</sub>=3.0V)

| Symbol           | Description                   | Min.                               | Тур. | Max.                               | Unit |

|------------------|-------------------------------|------------------------------------|------|------------------------------------|------|

| V <sub>IL</sub>  | Input low voltage             | GND-0.1                            | -    | $0.3 \cdot V_{DD_P}$               | V    |

| V <sub>IH</sub>  | Input high voltage            | 0.7 <sup>.</sup> V <sub>DD_P</sub> | -    | V <sub>DD_P</sub>                  | V    |

| V <sub>OL</sub>  | Output low voltage            | GND                                | -    | 0.2 <sup>.</sup> V <sub>DD_P</sub> | V    |

| V <sub>OH</sub>  | Output high voltage           | 0.8 <sup>.</sup> V <sub>DD_P</sub> | -    | V <sub>DD_P</sub>                  | V    |

| 1.               | Output high current           | -                                  | 1    | -                                  | μA   |

| ЮН               | Output high current (ball J8) | -                                  | 4    | -                                  | mA   |

| le.              | Output low current            | -                                  | 1    | -                                  | μA   |

| IOL              | Output low current (ball J8)  | -                                  | 4    | -                                  | mA   |

| I <sub>ILI</sub> | Input leakage current         | —                                  | 1    | —                                  | μΑ   |

#### AC Characteristics (T<sub>OP</sub>=+25°C, V<sub>DD P</sub>=3.0V, C<sub>LOAD</sub>=15pF)

| Symbol         | Description | Max. | Unit |

|----------------|-------------|------|------|

| t <sub>r</sub> | Rise time   | 30   | ns   |

| t <sub>f</sub> | Fall time   | 24   | ns   |

#### Current Consumption (T<sub>OP</sub>=+25°C, V<sub>BATT</sub>=3.0V using internal regulators)

| Operating Mode                                     | Average | Unit |

|----------------------------------------------------|---------|------|

| Parked slave, 1.28 sec. interval                   | 260     | μΑ   |

| Page/Inquiry scan, 1.28 sec. interval              | 1.6     | mA   |

| ACL connection, sniff mode, 40 ms interval         | 3.8     | mA   |

| ACL connection, sniff mode, 100 ms interval        | 1.4     | mA   |

| ACL data transfer 720 kbps, DH5 continuous packets | 62      | mA   |

| SCO connection, HV1 packets                        | 55      | mA   |

| SCO connection, HV3 packets                        | 32      | mA   |

## Digital Regulator Specification ( $T_{OP}$ = 25°C)

| Parameter                 | Description                                                        | Min  | Тур  | Max  | Unit |

|---------------------------|--------------------------------------------------------------------|------|------|------|------|

| Output voltage            | (I <sub>OUT</sub> = 10 mA)                                         | 1.71 | 1.80 | 1.89 | V    |

| Line regulation           | (I <sub>OUT</sub> = 0 mA, V <sub>BATT_DIG</sub> = 2.3 V to 3.63 V) | -    | 8.0  | -    | mV   |

| Load regulation           | (I <sub>OUT</sub> = 3 mA to 80 mA)                                 | -    | 9.0  | -    | mV   |

| Dropout voltage           | (I <sub>OUT</sub> = 10 mA)                                         | -    | _    | 250  | mV   |

| Output maximum<br>current | -                                                                  | -    | _    | 80   | mA   |

| Quiescent current         | -                                                                  | -    | 10   | -    | μA   |

| Ripple rejection          | f <sub>RIPPLE</sub> = 400 Hz                                       | -    | 40   | -    | dB   |

#### **Radio Specification**

| Parameter              | Description | Min  | Тур | Max  | Unit |

|------------------------|-------------|------|-----|------|------|

| VCO Operating<br>Range | Frequency   | 2402 | -   | 2480 | MHz  |

| PLL lock time          | -           | -    | 60  | 100  | μs   |

#### **RF Impedances**

| Parameter <sup>a</sup> | Description | Min | Тур      | Max | Unit |

|------------------------|-------------|-----|----------|-----|------|

|                        | TX on       | -   | 769//1.1 | -   | Ω/pF |

| RF impedance           | TX off      | -   | 26//2.4  | -   | Ω/pF |

| KF impedance           | RX on       | -   | 142//1.8 | -   | Ω/pF |

|                        | RX off      | -   | 45.7//0  | _   | Ω/pF |

a.The impedance values are for typical samples in 96-pin VFBGA package.

### Receiver Specification ( $V_{BATT}$ =3.3V, $V_{CC}$ =int. analog reg. output, nominal Bluetooth test conditions)

| Parameter                                                                                                                                                                                                                                 | Description                                                                            | Min | Тур   | Max   | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----|-------|-------|------|

| Receiver sensitivity                                                                                                                                                                                                                      | BER < 0.1%                                                                             | -   | -85   | -80   | dBm  |

| Maximum<br>usable signal                                                                                                                                                                                                                  | BER < 0.1%                                                                             | -   | 0     | _     | dBm  |

| C/I co-channel<br>(0.1% BER)                                                                                                                                                                                                              | Co-channel selectivity                                                                 | -   | 8.0   | 10.0  | dB   |

| C/I 1 MHz<br>(0.1% BER)                                                                                                                                                                                                                   | Adjacent channel selectivity                                                           | -   | -4.0  | -3.0  | dB   |

| C/I 2 MHz<br>(0.1% BER)                                                                                                                                                                                                                   | 2nd adjacent channel selectivity                                                       | -   | -38.0 | -35.0 | dB   |

| C/I ≥ 3 MHz<br>(0.1% BER)                                                                                                                                                                                                                 | 3rd adjacent channel selectivity                                                       | -   | -43.0 | -40.0 | dB   |

|                                                                                                                                                                                                                                           | 30 MHz - 2000 MHz                                                                      | -   | -10   | -     | dBm  |

| Out-of-band                                                                                                                                                                                                                               | 2000 MHz - 2399 MHz                                                                    | -   | -27   | -     | dBm  |

| blocking                                                                                                                                                                                                                                  | 2498 MHz - 3000 MHz                                                                    | _   | -27   | -     | dBm  |

|                                                                                                                                                                                                                                           | 3000 MHz - 12.75 GHz                                                                   | -   | -10   | -     | dBm  |

| Intermodulation                                                                                                                                                                                                                           | Max interferer level to maintain 0.1% BER, interference signals at 3 and 6 MHz offset. | -39 | -36   | _     | dBm  |

| Receiver spurious                                                                                                                                                                                                                         | 30 MHz to 1 GHz                                                                        | -   | -     | -57   | dBm  |

| Receiver sensitivity<br>Maximum<br>Isable signal<br>C/I co-channel<br>0.1% BER)<br>C/I 1 MHz<br>0.1% BER)<br>C/I 2 MHz<br>0.1% BER)<br>C/I ≥ 3 MHz<br>0.1% BER)<br>C/I ≥ 3 MHz<br>0.1% BER)<br>Dut-of-band<br>blocking<br>Intermodulation | 1 GHz to 12.75 GHz                                                                     | -   | -     | -47   | dBm  |

|                                                                                                                                                                                                                                           |                                                                                        |     |       | 1     |      |

Note: Nominal and extreme Bluetooth test conditions as defined by the Bluetooth Test and Interoperability Working Group published RF Test Specification 1.1.

## Transmitter Specification (V<sub>BATT</sub>=3.3V, V<sub>CC</sub>=int. analog reg. output, nom. Bluetooth test conditions)

| Parameter                                                                                                                                                  | Description                                     | Min  | Тур   | Max                                                   | Units |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------|-------|-------------------------------------------------------|-------|

| Output RF transmit<br>power                                                                                                                                | At maximum power output level                   | 0    | +2    | +4                                                    | dBm   |

| Modulation index                                                                                                                                           | -                                               | 0.28 | 0.306 | 0.35                                                  | -     |

| Initial carrier fre-<br>quency accuracy                                                                                                                    | -                                               | -75  | -     | +75                                                   | kHz   |

|                                                                                                                                                            | One slot packet                                 | -25  | -     | +25                                                   | kHz   |

| Carrier frequency                                                                                                                                          | Two slot packet                                 | -40  | -     | +40                                                   | kHz   |

| drift                                                                                                                                                      | Five slot packet                                | -40  | -     | +40                                                   | kHz   |

|                                                                                                                                                            | Max drift rate                                  | -    | -     | 400                                                   | Hz/µs |

| 20 dB occupied<br>bandwidth                                                                                                                                | Bluetooth specification                         | -    | -     | 1000                                                  | kHz   |

| In-band spurious                                                                                                                                           | 2 MHz offset                                    | -    | -     | -40                                                   | dBm   |

| emission                                                                                                                                                   | >3 MHz offset                                   | -    | -     | +4<br>0.35<br>+75<br>+25<br>+40<br>+40<br>400<br>1000 | dBm   |

|                                                                                                                                                            | 30 MHz to 1 GHz, operating mode                 | -    | -     | -55                                                   | dBm   |

|                                                                                                                                                            | 30 MHz to 1 GHz, idle mode                      | -    | -     | -57                                                   | dBm   |

| Out-of-band                                                                                                                                                | 1 GHz to 12.75 GHz, operating mode <sup>a</sup> | -    | -     | -50                                                   | dBm   |

| ower<br>Modulation index<br>initial carrier fre-<br>uency accuracy<br>Carrier frequency<br>rift<br>0 dB occupied<br>andwidth<br>n-band spurious<br>mission | 1 GHz to 12.75 GHz, idle mode                   | -    | -     | -47                                                   | dBm   |

|                                                                                                                                                            | 1.8 GHz to 1.9 GHz                              | -    | -     | -62                                                   | dBm   |

|                                                                                                                                                            | 5.15 GHz to 5.3 GHz                             | -    | -     | -47                                                   | dBm   |

a.Except transmit harmonics.

### **System Requirements**

#### **Analog Voltage Supply Requirements**

The SiW3000 processor is designed for use with integrated low noise analog voltage regulator and is recommended for all applications. If necessary, the internal digital regulator can be bypassed. In situations where bypassing the internal analog regulator is required, the supply voltage to the analog circuit must satisfy the following requirements to preserve the RF performance characteristics.

| Parameter                                     | Description                                 | Min  | Max  | Unit   |

|-----------------------------------------------|---------------------------------------------|------|------|--------|

| VCC                                           | Analog supply voltage to all VCC input pins | 1.71 | 1.89 | V      |

| Minimum<br>load current                       | External regulator current                  | 80   | _    | mA     |

| Minimum<br>ripple rejection                   |                                             |      | -    | dB     |

| Output noise Integrated 10 Hz to 80 kHz noise |                                             | 1    | 22   | mV RMS |

#### **External Reference Requirements**

It is possible to provide a number of reference frequencies that are typical on most cellular phones directly into ball B7 (XTAL\_P/CLK) of the device. The following reference frequencies (in MHz) can be used:

3.84, 9.6, 12, 12.8, 13, 14.4, 15.36, 16, 16.8, 19.2, 19.68, 19.8, 26, 32, 38.4, and 48 MHz. For other frequencies, please contact Silicon Wave.

| Parameter   | Description           | Min | Max             | Units            |

|-------------|-----------------------|-----|-----------------|------------------|

|             | 100 Hz offset         | -   | -100            | dBc/Hz           |

| Phase noise | 1 kHz offset          | _   | -120            | dBc/Hz           |

|             | 10 kHz offset         | -   | -140            | dBc/Hz           |

| Drive level | AC amplitude          | 0.5 | V <sub>CC</sub> | V <sub>P-P</sub> |

| Drive level | DC level <sup>a</sup> | 0.3 | V <sub>CC</sub> | V                |

a.lf DC-coupled, the external reference signal voltage must stay within this range at all times.

#### **Reference Crystal Requirements**

Many reference frequencies are supported by the device. If a crystal is used as the reference frequency source, the typical required parameters are listed below:

| Parameter      | Description                              | Min | Тур | Max | Unit |

|----------------|------------------------------------------|-----|-----|-----|------|

| Drive level    | -                                        | -   | -   | 0.3 | mW   |

| ESR            | Effective serial resistance <sup>a</sup> | -   | _   | 150 | W    |

| C <sub>O</sub> | Holder capacitance <sup>b</sup>          | -   | 3   | 5   | pF   |

| CL             | Load capacitance <sup>b</sup>            | -   | 12  | 18  | pF   |

| C <sub>M</sub> | Motional capacitance                     | -   | 6   | -   | fF   |

a.For 32-MHz crystal.

b. The actual values for C<sub>O</sub> and C<sub>L</sub> are dependent on the crystal manufacturer and can be compensated for by an internal crystal calibration capability.

## **Application Circuit for External Flash-based Products**

## **Application Circuit for Internal ROM-based Products**

|   | 1                     | 2              | 3                    | 4      | 5         | 6        | 7          | 8            | 9           | 10          | 11          |

|---|-----------------------|----------------|----------------------|--------|-----------|----------|------------|--------------|-------------|-------------|-------------|

| A | A1                    | (A2)           | A3                   | (A4)   | A5        | (A6)     | (A7)       | (A8)         | A9          | (A10)       | (A11)       |

|   | VCC                   |                | GND                  | RF_OUT | GND       | VTUNE    | XTAL_N     | A[15]        | VDD_C       | OE_N        | A[7]        |

| В | (B1)                  | B2             | B3                   | B4     | <b>B5</b> | B6       | (В7)       | (B8)         | (B9)        | (B10)       | (B11)       |

| - | IDAC                  | GND            | GND                  | GND    | GND       | VCC      | XTAL_P/CLK |              | FCS_N       | D[12]       | D[15]       |

| С |                       | C2<br>VREFN_CA | C3                   | C4     | C5        |          | C7         | C8           | (C9)        | (C10)       |             |

| D | VREFP_CAP             | D2             | GND<br>D3            | VCC    | vcc       | RESET_N  | VSS_P      | VSS_C        | A[13]       | D[14]       | D[13]       |

|   | VCC_OUT               | GND            |                      | IA     |           |          |            |              | A[1]        | D[6]/PIO[6] | A[2]        |

| Е | E1                    | E2             | E3                   |        |           |          |            |              | (E9)        | (E10)       | (E11)       |

|   | VCC                   | GND            | VCC                  |        | <u> </u>  |          | ~ ~        |              | A[3]        | PCM_IN      | A[4]        |

| F | (F1)                  | F2             | (F3)                 |        |           | W30      |            |              | <b>F</b> 9  | (F10)       | F11         |

|   | CHP_PUMP              | GND            |                      | E      | ТО        | P VI     | EW         |              | A[5]        | PCM_OUT     | VDD_P       |

| G | (G1)                  | G2             | G3                   |        |           |          |            |              | (G9)        | (G10)       | (G11)       |

|   | PWR_REG_EN/<br>PIO[8] | WAKEUP         | A[17]/<br>EEPROM_SCL |        |           |          |            |              | UART_RTS    | $\bigcirc$  | D[11]       |

| н | (H1)<br>A[16]/        | (H2)           | НЗ                   |        |           |          |            |              | (H9)        | (H10)       | (H11)       |

|   | EEPROM_SDA            | A[14]          | A[12]                |        |           |          |            |              | D[9]        | PCM_SYNC    | D[10]       |

| J | J1                    | (J2)           | J3                   | (J4)   | J5        | J6       | (J7)       | USB_DPLS_    | (J9)        | (J10)       | (J11)       |

| к | A[11]                 | D[8]/PIO[3]    | D[2]                 | D[3]   | VSS_P     | VSS_C    | A[9]       | PULLUP<br>K8 | TX_RX_SWITC | (K10)       | D[7]/PIO[7] |

| ĸ |                       | $\smile$       |                      | A[10]  | PIO[0]    | $\smile$ | UART_RXD   | $\smile$     | $\smile$    | $\bigcirc$  | WE_N/       |

| L | (L1)                  | (L2)           | (L3)                 | (L4)   | L5        | L6       | (L7)       | L8           | L9          | L10         | L11         |

|   | A[18]                 | D[4]/PIO[4]    | D[5]/PIO[5]          | A[8]   | VDD_P     | VDD_C    | A[6]       | VBATT_DIG    | VSS_US<br>B | VDD_USB     | CLK32K_OUT  |

|   | P                     | OWER           |                      |        |           |          |            |              |             |             |             |

|   |                       | IGITAL GF      |                      |        |           |          |            |              |             |             |             |

|   |                       | IGHAL GP       |                      |        |           |          |            |              |             |             |             |

## I/O Configuration (Top View)

RF GROUND

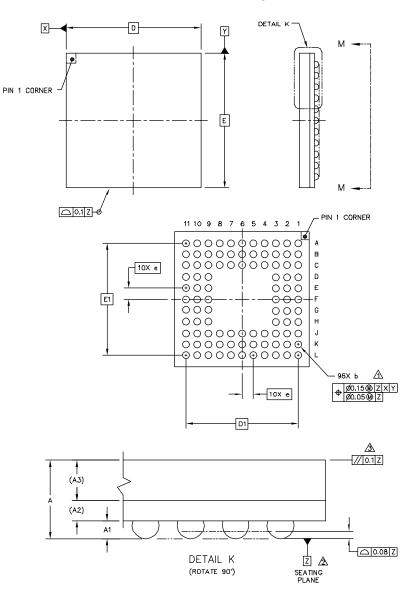

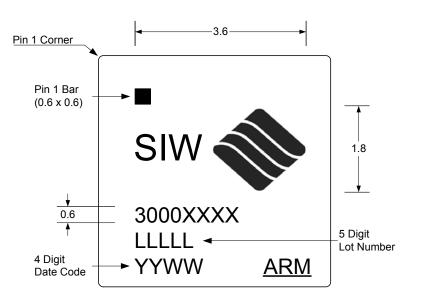

## Packaging and Product Marking Package Drawing

96-Pin, 6mmx6mm, VFBGA Drawing and Dimensions

| Symbol | Min      | Max  |  |  |  |

|--------|----------|------|--|--|--|

| A      | 0.8      | 1.0  |  |  |  |

| A1     | 0.2      | 0.3  |  |  |  |

| A2     | 0.22 REF |      |  |  |  |

| A3     | 0.45 REF |      |  |  |  |

| b      | 0.25     | 0.35 |  |  |  |

| D      | 6 BSC    |      |  |  |  |

| E      | 6 BSC    |      |  |  |  |

| е      | 0.5 BSC  |      |  |  |  |

| D1     | 5 BSC    |      |  |  |  |

| E1     | 5 BSC    |      |  |  |  |

SiW3000

#### Notes:

- 1. Dimension b is measured at the maximum solder ball diameter, parallel to datum plane Z.

- 2. Datum Z is defined by the spherical crowns of the solder balls.

- 3. Parallelism measurement shall exclude any effect of mark on top surface of package.

- 4. All dimensions are in millimeters.

**Product Marking**

Unit: mm

## **Ordering Information**

| Part Number     | Operational Temperature Range <sup>1</sup> | Package        | Ordering Quantity |  |

|-----------------|--------------------------------------------|----------------|-------------------|--|

| SiW3000GIP1     | Industrial                                 | 96-pin VFBGA   | 429 pcs. per tray |  |

| SiW3000GIP1-T13 | Industrial                                 | 96-pin VFBGA   | 2500 on 13" reel  |  |

| SiW3000BIA1     | Industrial                                 | Known good die | Waffle pack       |  |

| SiW3000BIA1-H   | Industrial                                 | Known good die | Whole wafer       |  |

<sup>1</sup> Industrial temperature range: -40°C to +85°C

# SiW3000

RF Micro Devices and Silicon Wave believe the furnished information is correct and accurate at the time of this printing. Silicon Wave reserves the right to make changes to its products without notice and advises customers to verify that the information being used is current. The described products are not designed, manufactured or intended for use in equipment for medical, life support, aircraft control or navigation, or any other applications that require failsafe operation. RF Micro Devices and Silicon Wave do not assume responsibility for the use of the described products.

RF MICRO DEVICES®, RFMD® and Providing Communication Solutions™ are trademarks of RFMD, LLC. The diamond logo design, Silicon Wave, and the SiW product name prefix are registered trademarks and UltimateBlue is a trademark of Silicon Wave, Inc. BLUETOOTH® is a trademark owned by Bluetooth SIG, Inc., U.S.A. and licensed for use by RF Micro Devices, Inc. and Silicon Wave. Manufactured under license from ARM Limited. ARM, ARM/TDMI and the ARM logo are the registered trademarks of ARM Limited in the EU and other countries. All other product, service, and company names are trademarks, registered trademarks or service marks of their respective owners.