# **TP3465 MICROWIRE™ Interface Device (MID)**

# **General Description**

The MICROWIRETM Interface Device MID gives a general microprocessor (such as National Series 32000® processors, Intel 80C188, 80C86 or 80286, Motorola 6800 and 68000 family of processors) the ability to communicate efficiently with up to eight peripheral devices via the serial MI-CROWIRE interface. The MID causes each of the peripheral devices to appear to the µP as memory mapped locations, by performing all the data serialization and transfer protocols to and from the peripherals.

# **Applications**

- ISDN Terminal Adapters

- Digital Line cards (ISDN and Non ISDN)

- Analog Linecards using National COMBO®

- Interfacing to industry standard serial EEPROMs

- Interfacing to industry standard MICROWIRE peripheral devices such as Analog to Digital Converters, LCD drivers, clock generators

## **Features**

- Multiplexed and Non-multiplexed microprocessor bus

- National/Intel and Motorola microprocessor bus compatible

- Microprocessor Clock (CKIN) up to 20 MHz

- MICROWIRE clock speeds up to 5 MHz

- Directly compatible with 8- and 16-bit MICROWIRE peripherals

- Commercial temperature range 0C to +70C

- TP3465 for 8 Chip Select output

- Memory mapped peripherals

- Programmable MICROWIRE Clock to communicate with devices of different speeds

- Operates as MICROWIRE bus master or slave

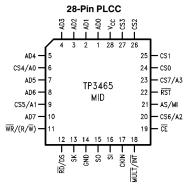

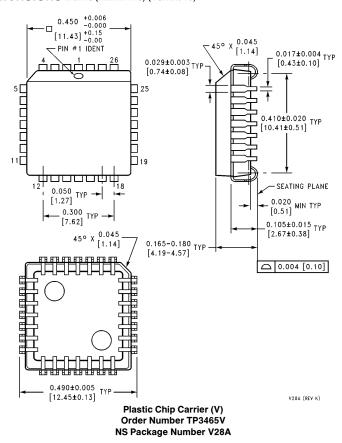

- 28-pin PLCC Package

- CMOS, Low Power

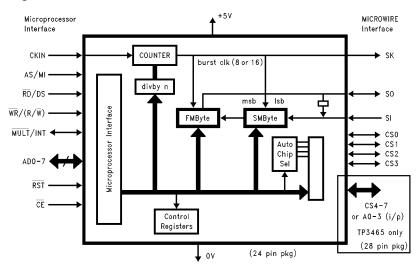

# **Block Diagram**

FIGURE 1. MICROWIRE Interface Device MID

TI /H/10803-1

COMBO®, Series 32000® and TRI-STATE® are registered trademarks of National Semiconductor Corporation. MICROWIRE™ is a trademark of National Semiconductor Corporation.

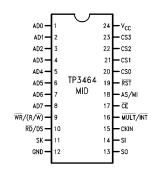

# **Connection Diagrams**

TL/H/10803-3 **Top View**

Order Number TP3465V See NS Package Number V28A

FIGURE 2. MICROWIRE Interface Device MID TP3465 Pinouts

# **Pin Description**

| Name            | Pin No.<br>28 Pkg. | Туре | Function                                       |

|-----------------|--------------------|------|------------------------------------------------|

| V <sub>CC</sub> | 28                 | I    | +5V Supply                                     |

| GND             | 14                 | I    | 0V                                             |

| CKIN            | 17                 | I    | Master Clock Input Used to Derive the SK Clock |

# **MICROWIRE Interface**

The MICROWIRE Interface consists of SK (clock out), SO (data out), SI (data in) and up to 8 chip select output lines.

| Name    | Pin No.<br>28 Pkg. | Туре | Function                                                                                                                           |  |

|---------|--------------------|------|------------------------------------------------------------------------------------------------------------------------------------|--|

| SK      | 13                 | 0    | MICROWIRE clock output.                                                                                                            |  |

| SO      | 15                 | O/I  | MICROWIRE data output. Can also be used for MICROWIRE data input when communicating with special devices. See application section. |  |

| SI      | 16                 | 1    | MICROWIRE data input.                                                                                                              |  |

| CS0-CS3 | 24-27              | I/O  | Four input/output lines, normally used as outputs for chip selects to MICROWIRE peripherals                                        |  |

| CS4±CS7 | 6, 9, 20,<br>23    | I/O  | Four chip select lines accessible when using the Multiplexed bus mode.                                                             |  |

# MultiplexedMicroprocessoBus Interface

The MULT/INT pin is sampled on power-up and, if LOW, the microprocessor bus format is assumed to be Multiplexed and the pin is considered an input pin to indicate Multiplexed bus format. The pin has an internal pull-up and thus if pin is left floating, it will be considered as in Non-multiplexed mode. The interface consists of an eight bit multiplexed Address/Data microprocessor bus (only the A0, A1, A2 and A3 address lines are decoded), and six control lines (CE, RST, AS/MI, RD/DS, WR/(R/W) and the MULT input) which should be tied LOW.

| Name         | Pin No.<br>28 Pkg.         | Туре | Function                                                                                                                                                                                                                                       |

|--------------|----------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD0-AD7      | 1, 2, 3, 4,<br>5, 7, 8, 10 | I/O  | Address/Data bus. Transfers addresses and data between the microprocessor and the MID.                                                                                                                                                         |

| CE           | 19                         | I    | Chip Enable. A LOW on this signal selects the MID for a Read/Write operation.                                                                                                                                                                  |

| WR/<br>R/W   | 11                         | I    | Write or Read-Write direction. This signal indicates a Write operation or Read/Write direction signal.                                                                                                                                         |

| RD/DS        | 12                         | I    | Read or Data Strobe. With an Intel mP this signal indicates a Read operation (active low polarity signal) or with a Motorola $\mu$ P, a Data strobe (active high polarity signal).                                                             |

| AS/MI        | 21                         | ı    | Address Latch Enable or Address Strobe. A HIGH on this line indicates an address on the external A/D bus. When MULT = 1 (non-multiplexed bus), the pin indicates the type of bus, MI = 1 for NSC/Intel format and MI = 0, for Motorola format. |

| RST          | 22                         | I    | The RST is the master Reset input, when LOW forces the device in the RESET condition (same as Power-on-Reset).                                                                                                                                 |

| MULT/<br>INT | 18                         | I    | Multiplexed Bus input or INTerrupt output. It is internally pulled HIGH to indicate a Non-Multiplexed bus format and needs to be pulled LOW externally to indicate the Multiplexed bus format.                                                 |

# **Non-Multiplexed Microprocessor Interface**

The  $\overline{\text{MULT}/\overline{\text{INT}}}$  pin is sampled on power-up and, if not LOW, the microprocessor bus format is assumed to be Non-multiplexed. This interface consists of a four-bit Address bus, an eight-bit Data bus and six control lines ( $\overline{\text{CE}}$   $\overline{\text{RST}}$ , AS/MI,  $\overline{\text{RD}}/\text{DS}$ ,  $\overline{\text{WR}}/(R/\overline{\text{WR}})$ ) and the  $\overline{\text{INT}}$  signal if enabled).

| Name         | Pin No.<br>28 Pkg.         | Туре | Function                                                                                                                                                                                                                                      |

|--------------|----------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0-A3        | 6, 9,<br>20, 23            | 1    | Address bus. These 4 pins (accessible in the 28-pin package) are used to address the 16 registers.                                                                                                                                            |

| D0-D7        | 1, 2, 3, 4,<br>5, 7, 8, 10 | 1/0  | Data bus for data transfer between the microprocessor and the MID.                                                                                                                                                                            |

| CE           | 19                         | I    | Chip Enable. A LOW on this signal selects the MID for a Read/Write operation.                                                                                                                                                                 |

| WR/<br>(R/W) | 11                         | I    | Write or Read-Write direction. This signal indicates a Write operation or Read/Write direction signal.                                                                                                                                        |

| RD/DS        | 12                         | I    | Read or Data Strobe. With an Intel $\mu P$ this signal indicates a Read operation (active low polarity signal) or with a Motorola $\mu P$ , a Data Strobe (active high polarity signal).                                                      |

| AS/MI        | 21                         | I    | Address Latch Enable or Address Strobe. A HIGH on this line indicates an address on the external A/D bus. When MULT = 1 (non-multiplexed bus), the pin indicates the type of bus, MI = 1 for NSC/Intel format and MI = 0 for Motorola format. |

# Non-Multiplexed Microprocessor Interface (Continued)

The  $\overline{\text{MULT}/\overline{\text{INT}}}$  pin is sampled on power-up and, if not LOW, the microprocessor bus format is assumed to be Non-multiplexed. This interface consists of a four-bit Address bus, an eight-bit Data bus and six control lines ( $\overline{\text{CE}}$   $\overline{\text{RST}}$ , AS/MI,  $\overline{\text{RD}}/\text{DS}$ ,  $\overline{\text{WR}}/(\text{R/WR})$ ) and the  $\overline{\text{INT}}$  signal if enabled).

| Name         | Pin No.<br>28 Pkg. | Туре | Function                                                                                                                                                                                                                                                                                   |

|--------------|--------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RST          | 22                 | I    | The RST is the master Reset input; when LOW, it forces the device in the RESET condition (same as Power-on-Reset).                                                                                                                                                                         |

| MULT/<br>INT | 18                 | 0    | Multiplexed Bus input or INTerrupt output. It is internally pulled HIGH to indicate a Non-multiplexed bus format and the pin can be an INT output pin if enabled by setting the Inten bit in the CKR register. INT pulls low to indicate the completion of a MICROWIRE transfer operation. |

# **Functional Description**

The block diagram of the MICROWIRE Interface Device (MID) is shown in *Figure 1*. It essentially consists of a very flexible microprocessor bus interface, a serial MICROWIRE interface and a Chip Select (output) port. Internally it contains a programmable clock divider to derive the MICROWIRE clock speed from a system clock.

#### **MICROPROCESSOR INTERFACE**

The Microprocessor bus interface supports both National/Intel and Motorola bus formats in the Multiplexed and Non-multiplexed bus modes.

The MULT/INT pin is sampled on power-up and, if LOW, the microprocessor bus format is assumed to be Multiplexed and the pin is considered an input pin to indicate Multiplexed bus format. The pin is internally pulled HIGH. Upon sampling, if the pin is not LOW, the bus format is assumed to be Non-multiplexed.

The microprocessor interface supports multiplexed Address/Data Formats for the Intel 8088/80188 and Motorola 6803 families to work in 8-bit mode. Non-multiplexed busses of the National 32000, Intel 80286 and Motorola 68000, series processors and similar are supported in the TP3465 28-pin part. Four address lines allow access to all MID registers

The MID incorporates a flexible bus interface logic to support the different address and data strobes required by the different bus formats. The timing specifications are shown in a later section. The following table shows microprocessor bus control pin functions:

| MID Pin  | NSC   | /Intel Bus | Motorola Bus |           |  |

|----------|-------|------------|--------------|-----------|--|

| MILETIN  | MUXed | Non-MUXed  | MUXed        | Non-MUXed |  |

| AS/MI    | ALE   | MI = 1     | AS           | MI = 0    |  |

| RD/DS    | RD    | RD         | DS           | DS        |  |

| WR/(R/W) | WR    | WR         | (R/W)        | (R/W)     |  |

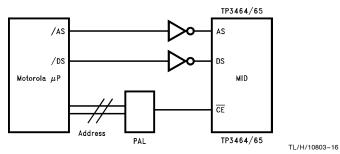

See Figure 7 for connection of the AS and DS signals to Motorola  $\mu \mbox{Ps}.$

#### MICROWIRE COMMUNICATION MODES

The MID provides a MICROWIRE port to the main processor having two modes of operation with the MICROWIRE peripherals; software-controlled chip select and hardware-generated chip select modes.

In the first scheme, besides the 2 data byte registers, there is a third register which maps directly with the output CS Chip Selects pins, which there eight pins for this function in the TP3465 28-pin package . The software in the microprocessor then writes to the CS register to select and deselect individual bits (corresponding to pins).

In the second scheme, the CS pins are activated by a hardware state machine when triggered, by accessing the data registers through other address locations (see section on Register description). In this case the hardware will activate the chip select pin, send the appropriate number of MICRO-WIRE data bits (8 or 16) and then deselect the pin. This enhanced mode of communication allows the MICRO-WIRE peripheral devices to appear as if I/O mapped in the micro-processor's memory space.

#### **CONTROL AND DATA REGISTERS**

There are 6 control registers (PD, MWM, SKP, SKR, ST and CS), and 1 set of Data registers (First MICROWIRE Byte FMB and Second MICROWIRE Byte SMB) for data communication to MICROWIRE devices. In normal mode, the Chip select pins CS0–C7 are controlled (via the CS register) by software and data is transferred via the FMB and SMB registers located at address 01h and 00h (see Table I).

Eight additional addresses (FMBD0-7) access the same data register (FMB) but provide additional information to an internal state machine which drives appropriate chip select pins (e.g., FMBD0 at address 02h controls CS0 pin, FMBD1 at address 03h controls CS1 pin etc.). There is only 1 set of Data registers (FMB and SMB) which handle the MICROWIRE communication. This latter method of allocating special addresses to provide pin-select information facilitates an enhanced MICROWIRE interface to the host processor.

Table I summarizes the Control and Data Registers and the addresses at which they are accessed.

# Functional Description (Continued)

**TABLE I. Control and Data Registers**

| TABLE II GOILL BALL HOSIOLO |          |        |      |      |      |      |      |      |      |

|-----------------------------|----------|--------|------|------|------|------|------|------|------|

| Address                     | Register | Bit7   | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

| 00h                         | SMB      | d7     | d6   | d5   | d4   | d3   | d2   | d1   | d0   |

| 01h                         | FMB      | d7     | d6   | d5   | d4   | d3   | d2   | d1   | d0   |

| 02h                         | FMBD0    | d7     | d6   | d5   | d4   | d3   | d2   | d1   | d0   |

| 03h                         | FMBD1    | d7     | d6   | d5   | d4   | d3   | d2   | d1   | d0   |

| 04h                         | FMBD2    | d7     | d6   | d5   | d4   | d3   | d2   | d1   | d0   |

| 05h                         | FMBD3    | d7     | d6   | d5   | d4   | d3   | d2   | d1   | d0   |

| 06h                         | FMBD4    | d7     | d6   | d5   | d4   | d3   | d2   | d1   | d0   |

| 07h                         | FMBD5    | d7     | d6   | d5   | d4   | d3   | d2   | d1   | d0   |

| 08h                         | FMBD6    | d7     | d6   | d5   | d4   | d3   | d2   | d1   | d0   |

| 09h                         | FMBD7    | d7     | d6   | d5   | d4   | d3   | d2   | d1   | d0   |

| 0Ah                         | CS       | cs7    | cs6  | cs5  | cs4  | cs3  | cs2  | cs1  | cs0  |

| 0Bh                         | SKP      | skp7   | skp6 | skp5 | skp4 | skp3 | skp2 | skp1 | skp0 |

| 0Ch                         | MWM      | mwm7   | mwm6 | mwm5 | mwm4 | mwm3 | mwm2 | mwm1 | mwm0 |

| 0Dh                         | SKR      | inten  | soi  | ms   | 0    | 0    | div2 | div1 | div0 |

| 0Eh                         | ST       | uwdone | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| 0Fh                         | PD       | pd7    | pd6  | pd5  | pd4  | pd3  | pd2  | pd1  | pd0  |

#### PD-Pin Definition Register: W Register

RESET condition is FFhex (all pins as Inputs)

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------|------|------|------|------|

| pd7  | 6bq  | pd5  | pd4  | pd3  | pd2  | pd1  | 0ba  |

pd0-7 bits configure the CS0-7 pins as inputs or outputs. For example pd0=1, sets the CS0 pin as an input; pd0=0, sets CS0 pin as an output. Upon chip RESET, the pd0-7 bits are set to 1.

# SKP-MICROWIRE Clock (SK) Polarity: W Register

RESET condition is 00hex (Normal MICROWIRE clock)

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------|------|------|------|------|

| skp7 | skp6 | skp5 | skp4 | skp3 | skp2 | skp1 | skp0 |

**skp 0-7** bits set the polarity of the SK MICROWIRE clock when communicating with device connected to each of the pins CS0-7. For example **skp0** = 0, normal MICROWIRE mode (i.e., SO data output on negative edge of SK clock) when sending data to device controlled by CS0 pin; **skp1** = 1, NSC COMBO II clock format for device controlled by CS1 (i.e., SO data output on the positive edge of SK clock).

# MWM—MICROWIRE Mode Register: W Register

RESET condition is 00hex

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------|------|------|------|------|

| mwm7 | mwm6 | mwm5 | mwm4 | mwm3 | mwm2 | mwm1 | mwm0 |

mwm0-7 bits specify whether 8 or 16 clocks are generated for devices connected to CS0-7 pins. For example mwm1 = 1, 16 clocks will be generated for device controlled by CS1, (16 data bits will be shifted out and 16 data bits will be strobed in); mwm0 = 0, 8 clocks will be generated for device controlled by CS0 (8 data bits will be shifted out and strobed in).

# SKR—MICROWIRE Clock (SK) Rate Register: W Register

| Bit7  | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|-------|------|------|------|------|------|------|------|

| inten | soi  | ms   | 0    | 0    | div2 | div1 | div0 |

The 3 bits div0-2 give the divide-by value for deriving the SK clock output rate from the CKIN. The maximum CKIN rate is 20 MHz, and the slowest MICROWIRE peripheral works at 256 kHz. Table 2 below gives the division ratios and some examples:

| div2 | div1 | div0 | SK Ratio      | e.g., CKIN = 5 MHz | e.g., CKIN = 20 MHz |

|------|------|------|---------------|--------------------|---------------------|

| 0    | 0    | 0    | SK = CKIN     | SK = 5 MHz         |                     |

| 0    | 0    | 1    | SK = CKIN/2   | SK = 2.5 MHz       |                     |

| 0    | 1    | 0    | SK = CKIN/4   | = 1.25 MHz         | SK = 5 MHz          |

| 0    | 1    | 1    | SK = CKIN/8   | = 625 kHz          | = 2.5 MHz           |

| 1    | 0    | 0    | SK = CKIN/16  | = 312.5 kHz        | = 1.25 MHz          |

| 1    | 0    | 1    | SK = CKIN/32  | = 156.25 kHz       | = 625 kHz           |

| 1    | 1    | 0    | SK = CKIN/64  | = 78.125 kHz       | = 312.5 kHz         |

| 1    | 1    | 1    | SK = CKIN/128 | = 39.06 kHz        | = 156.25 kHz        |

TABLE 2. SK Clock Rate Control

# Functional Description (Continued)

The **uwdone** bit in the ST register can be connected to the  $\overline{\text{INT}}$  pin of the MID to alert the host processor when MICROWIRE transmission is completed by setting the **inten** bit in this SKR register. The  $\overline{\text{INT}}$  pin will only be functional as an interrupt in the Non-multiplexed bus mode in the 28-pin TP3465 device.

The  $\mathbf{soi}$  bit configures the SO pin to be output ( $\mathbf{soi}=0$ ) or input ( $\mathbf{soi}=1$ ). This bit function is used to perform a Read operation on a device such as NSC TP3071 COMBO II because the TP3071 sends data back on the SO pin. When  $\mathbf{soi}=1$ , the SO pin functions as the SI input pin, internally, and feeds the data registers. See applications diagrams and software procedures for more details.

The ms bit configures the MID device as a Master of MICROWIRE (ms=0) or Slave of MICROWIRE (ms=1). MICROWIRE Slave mode is described and illustrated in the applications section.

#### CS-Chip Select Port Register: R/W Register

RESET condition, CS pins are inputs and the register contains the state of these pins.

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------|------|------|------|------|

| cs7  | cs6  | cs5  | cs4  | cs3  | cs2  | cs1  | cs0  |

The **cs0-7** bits control the 8, CS input/output port pins. However, only the **cs0-3** control bits are available in the TP3465 device when used in the non-multiplexed bus format. In the multiplexed bus format in TP3465, all 8 CS pins are accessible

Writing to this register will affect the pins (configured as outputs in PD register) directly. Similarly, the state of the pins which are configured as inputs in the PD registers can be Read via the same (CS) register. When reading the pins designated as outputs, the bits will have a "1" condition. Writing to bits corresponding to input pins will have no effect on the pins.

The state of an output chip select pin may also be controlled by the chip hardware state machine if the user writes to the FMBD0-7 registers. The hardware can only bring the appropriate pin LOW for the duration of the MICROWIRE transfer and will attempt to set it HIGH at the end of the transfer. If the user has, however, set this pin to be LOW by writing to this register, it will over-ride the action of the hardware and the pin will remain LOW. Thus the user must write a "1" in the bits that will be controlled by hardware, and the pins must be set as outputs in the PD register.

#### ST-MICROWIRE Status Register: R Register

RESET Condition. Read 80 Hex

| Bit7   | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|--------|------|------|------|------|------|------|------|

| uwdone | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

The **uwdone** bit (read only) in the ST register can be polled by the software to determine the end of the MICROWIRE transmission (uwdone=1). uwdone=0 during transmission.

#### FMB—First MICROWIRE Byte: R/W Register

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------|------|------|------|------|

| d7   | d6   | d5   | d4   | d3   | d2   | d1   | d0   |

#### SMB—Second MICROWIRE Byte: R/W Register

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------|------|------|------|------|

| d7   | d6   | d5   | d4   | d3   | d2   | d1   | d0   |

The SMB and the FMB data registers are used to communicate to any MICROWIRE device 0–7 (connected to pins CS0–7) when controlling the chip select lines via CS register (using software). The MICROWIRE parameters for this mode of operation are defined by the parameters for device 7, i.e., skp7 in SKP register, and mwm7 in MWM register. So when communicating with peripherals requiring different formats, the skp7 and mwm7 bits may need to be re-configured before sending data to each of these devices. Example of communication to 8-bit and 16-bit peripherals are described below:

Example 1: Communicating with an 8-bit MICROWIRE peripheral at CS1:

Set the **skp7** bit to 0 (normal MICROWIRE polarity), and set the **mwm7** to 0 for 1 byte operation. Set **cs1** bit to 0 to select the device. Write the data into the FMB byte location so it will be shifted out after the trailing edge of the Write strobe signal. At the end of the MICROWIRE transmission set the **cs1** bit to 1 to de-select the device. The 8-bit STATUS from the peripheral is read from the FMByte location.

Example 2: Communicating with a 16-bit MICROWIRE peripheral at CS3:

MICROWIRE protocol specifies that the Most Significant Bit is transmitted first. Thus the HIGH byte of data becomes the First MICROWIRE Byte to be sent out.

Set the **skp7** bit to 0 (normal MICROWIRE polarity), and set the **mwm7** to 1 for 2 byte operation. Set **cs3** bit to 0 to select the device. Write the LOW data byte in the SMB register and then write the HIGH data byte into the FMB byte location. All 16 data bits are shifted out after the trailing edge of the Write strobe for the FMB register. At the end of the MICROWIRE transmission set the **cs3** bit to 1 to deselect the device. The 16-bit STATUS from the peripheral is read from the FMB (HIGH data byte) and the SMB (LOW data byte) locations.

#### FMBD0—First MICROWIRE Byte Dev0: R/W Register

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------|------|------|------|------|

| d7   | d6   | d5   | d4   | d3   | d2   | d1   | d0   |

There is only one set of data registers (FMB and SMB) which handle the MICROWIRE data communication. The FMBD0 address accesses the data register FMB but also provides information for the internal state machine to control the CS0 pin. The MICROWIRE parameters for device 0 are indicated by the state of bits skp0 and mwm0, etc.

# Functional Description (Continued)

Example 1: Communicating with 8-bit peripheral—device 0: The **mwm0** bit must be set to 0. Write the MICROWIRE data in to the FMBD0 address. The 8-bit data is then shifted out after the trailing edge of the write pulse. The Chip Select (CS0) is automatically activated (LOW) and deactivated (HIGH) by hardware before and after the data transfer (see timing diagrams). The 8-bit STATUS from the peripheral is read from the FMBD0 byte location.

Example 2: Communicating with 16-bit peripheral—device 0:

The **mwm0** bit must be set to 1. Write the LOW byte of MICROWIRE data into the SMB data register and then write the HIGH byte in to the FMBD0 address. The 16-bit data is then shifted out after the trailing edge of the write strobe signal for this FMBD0 address. The Chip Select 0 (CS0) pin is automatically activated (LOW) and deactivated (HIGH) by hardware before and after the data transfer (see timing diagrams). The 16-bit STATUS from the peripheral is read from the FMBD0 (HIGH data byte) and the SMB (LOW data byte) locations.

#### FMBD1—First MICROWIRE Byte Dev1: R/W Register

Same function as FMBD0 except this refers to Device 1 and Chip Select 1 (CS1).

#### FMBD2—First MICROWIRE Byte Dev2: R/W Register

Same function as FMBD0 except this refers to Device 2 and Chip Select 2 (CS2).

#### FMBD3—First MICROWIRE Byte Dev3: R/W Register

Same function as FMBD0 except this refers to Device 3 and Chip Select 3 (CS3).

#### FMBD4—First MICROWIRE Byte Dev4: R/W Register

Same function as FMBD0 except this refers to Device 4 and Chip Select 4 (CS4).

## FMBD5—First MICROWIRE Byte Dev5: R/W Register

Same function as FMBD0 except this refers to Device 5 and Chip Select 5 (CS5).

#### FMBD6—First MICROWIRE Byte Dev6: R/W Register

Same function as FMBD0 except this refers to Device 6 and Chip Select 6 (CS6).

# FMBD7—First MICROWIRE Byte Dev7: R/W Register

Same function as FMBD0 except this refers to Device 7 and Chip Select 7 (CS7).

#### **MICROWIRE Master/Slave Modes**

#### MICROWIRE MASTER MODE

The primary application for MID is as a master of MICRO-WIRE bus (ms bit in CKR register set to 0), and as such it provides the SK clock out to the peripheral devices. It transmits data on the SO pin and receives data on the SI pin. The CS0-7 pins are used as chip select pins for the peripherals and have a predefined relationship with the SK clock output. Writing to the FMB pin causes the most significant bit to be output immediately to the SO pin, and the uwdone bit is automatically reset to 0. Upon completion of transfer of either 8 bits (mwm7 = 0) or 16 bits (mwm7 = 1), the uwdone bit is set to 1. The SO pin is then set to the TRI-STATE® condition. Note that when using the FMB and SMB registers, the communication mode is determined by the parameters for channel 7 (mwm7 and skp7).

#### MICROWIRE SLAVE MODE

The MID can be set to work in MICROWIRE Slave mode by setting the **ms** bit to 1. The MICROWIRE clock from the master is connected to the CKIN pin of this MID device. The SK output is ignored. Normally the SO pin is in TRI-STATE condition and, while the uwdone bit is 1, any CKIN clock inputs are ignored. Writing to the FMB register causes the most significant bit to be output immediately to the SO pin and the **uwdone** bit is reset to 0 by hardware. The SK clock input is then enabled to clock data into SI and out of SO. After receiving SK clock pulses; either 8 (**mwm7** = 0) or 16 bits (**mwm7** = 1), the **uwdone** bit is set to 1 by hardware. The SO pin is then set to TRI-STATE condition. Note that when using the FMB and SMB registers, the communication mode is determined by the parameters of channel 7 (mwm7 and skp7).

FMBD0-7 addresses are not used in the slave mode. The CS register, however, can be used as a general I/O port control register.

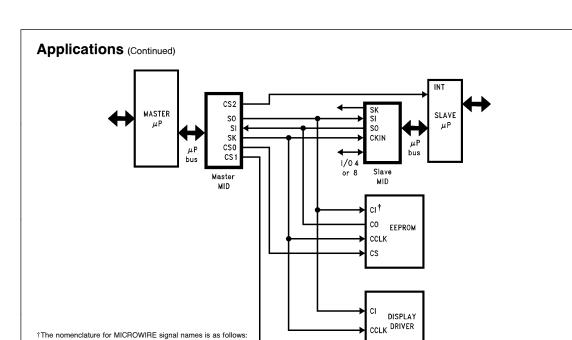

See applications section for an example of the Slave operation (Figure 6).

#### MICROWIRE BUS FORMATS

MID supports devices which implement either of the two MICROWIRE bus formats; a 3-pin format and a 4-pin format. Figure  $\it 3$  shows a MID connected to devices supporting each of these formats.

The standard 4-pin format consists of the CCLK clock pin, CO and Cl as the data out and data in pins, and CS to select the MICROWIRE peripheral. ISDN transceivers and other intelligent peripherals also have an INTerrupt signal from the peripheral to the local microprocessor. NSC MICROWIRE devices with this 4-pin format include ISDN transceivers, COMBO II, LCD display drivers and EEPROMs.

There are, however, some MICROWIRE peripherals (e.g., TP3071 COMBO II, and some EEPROMs) which support a 3-pin bus format because of package pin limitations. The format consists of the CCLK clock signal, a bi-directional data signal CO/CI, and a CS chip select signal. The direction of the data transferred on the CO/CI pin is determined by a protocol between the Master and the Slave of the MICROWIRE bus. For example, the TP3071 implements a two-byte protocol. The first byte into the TP3071 indicates a Read or a Write operation and thus defines the direction of the next byte to the device.

### **Software Driver Procedures**

This section describes the steps for software driver routines to communicate with different MICROWIRE devices (8-bit, 16-bit, or more) and those supporting the 3-pin or 4-pin MICROWIRE bus formats.

#### INITIALIZATION

- Write to PD (Pin Definition) register to set the desired chip select control pins (CS0-7) as outputs. (All CS pins are set to inputs on chip RESET.)

- Write to SKP (SK polarity), to select the polarity of the SK clock for each of the MICROWIRE devices connected to CS0-7 pins.

- 3. Write to MWM (MICROWIRE Mode) register to select whether 8- or 16-bit devices are attached to the CS0-7 pins. Devices needing more than 16-bits may still be configured as 8-bit mode (if multiple of 8) or 16-bit mode (if multiple of 16 bits).

## **Software Driver Procedures (Continued)**

4. Write to SKR to set the **div** bits to support the fastest SK clock rate supported by the peripherals. Set **inten** = 1 if the **uwdone** status is to set an INTerrupt to the host processor (available only in the Non-multiplexed bus implementation of TP3465, 28-pin package). The **ms** and the **soi** bit are set to 0 upon power up and indicate that the MID is in MICROWIRE Master mode, with SO as an output pin as normal.

#### SENDING DATA TO PERIPHERALS (Normal Mode)

Assume sending 16-bit data to a MICROWIRE based device connected to any one of CS0 to CS7.  $\label{eq:connected}$

- 1. Write to CS (Chip Select) register and reset the appropriate bit and thus activate the corresponding CS pin.

- Write LOW byte data to SMB (Second MICROWIRE Byte) register and then HIGH byte data to FMB (First MICRO-WIRE Byte) register.

- Read the ST (Status) register and stay in a loop until uwdone bit is set.

- Write to CS register and set the bit to deactivate the appropriate chip select pin.

# SENDING DATA TO PERIPHERALS (Hardware Assisted Chip Select)

Assuming sending 16-bit data to dev3 connected to CS3 pin.

- Write LOW byte data to address SMB and then HIGH byte data to FMBD3.

- Read the ST register and stay in a loop until uwdone bit is set.

# Communicating with an NSC TP3071 COMBO II Type Device

The NSC TP3071 COMBO II device has a modified MICRO-WIRE port. It shares a single pin (called CO/CI) for incoming and outgoing data. The MID's SO pin may be tied to this pin, as shown in *Figure 3*, and the following steps are followed to Read from and Write to this device. Assume that the chip select for TP3071 is connected to CS1 pin.

#### TP3071 Write Operation:

- a. Initialization states:  $\mathbf{skp1} = 1$ ,  $\mathbf{mwm1} = 1$ , and  $\mathbf{soi} = 0$

- b. Data transfer options:

- i. Set cs1 bit to 0, write LOW byte to SMB, and HIGH byte to FMB and then set cs1 bit to 1 after uwdone bit is set to 1.

OF

ii. Write LOW byte to SMB, and HIGH byte to FMBD1.

#### TP3071 Read Operation:

a. Initialization states: skp1 = 1, mwm1 = 0, and soi = 0.

- b. Data transfer options:

- i. Set cs1 bit to 0, write HIGH byte to FMB, wait until uwdone bit is set to 1 by hardware. Set soi bit to 1. Write dummy LOW byte (e.g., 00h) to FMB, wait until uwdone bit is set to 1 by hardware. Read STATUS from FMB address. Set soi to 0 and cs1 to 1.

OR

ii. Write HIGH byte to FMBD1, wait until uwdone bit is set to 1 by hardware. Set soi bit to 1. Write a dummy LOW byte (e.g., 00h) to FMBD1 and wait until uwdone bit is set to 1 by hardware. Read STATUS from FMBD1 address. Set soi bit to 0.

# **Applications**

The versatile TP3465 MICROWIRE Interface Device can be used in a number of applications involving MICROWIRE peripheral devices that need to be controlled using a standard microprocessor which only has a parallel bus structure.

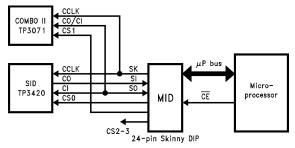

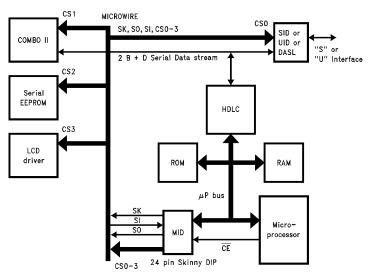

#### **ISDN TERMINAL ADAPTER**

The MID can be used in ISDN terminal adapters (see *Figure 4*) interfacing to ISDN components such as TP3420 SID, as well as non-ISDN components such as LCD display drivers (e.g., COP470) and serial EEPROMs (COP494). In this application the MID signals SK, SO and SI are bussed to all peripheral devices. The device chip selects control lines a total of 8 in the 28-pin package are individually connected to each of the devices. Status Interrupt from the peripherals such as SID are connected directly to the main processor.

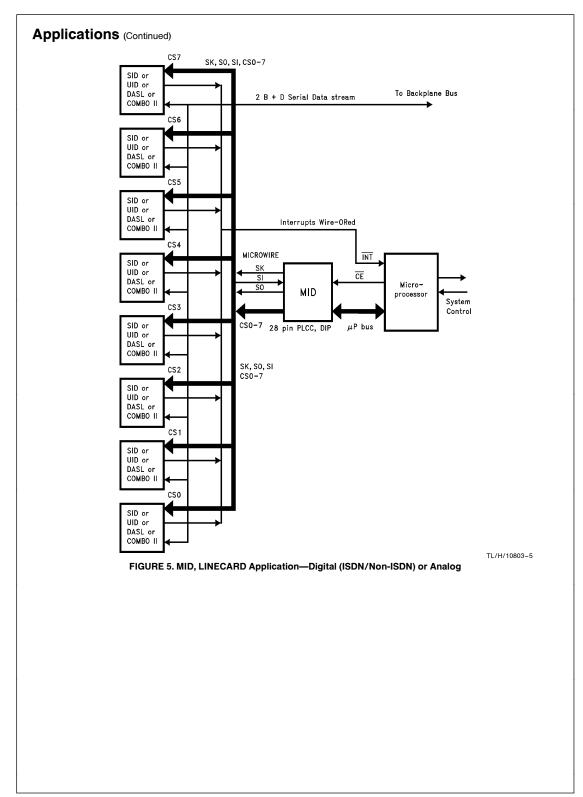

#### **ANALOG OR DIGITAL LINECARDS**

The MID can also be used in analog and digital (ISDN and Non-ISDN) linecard applications (see *Figure 5*). Up to 8 MICROWIRE peripheral devices (TP3070 COMBO II, or TP3420 SIDs, TP3410 UIDs or TP3401 DASLs) can be connected to one MID device. The Interrupts from the transceivers may be wire-ORed and fed into one interrupt line of the main processor, in which case all the devices will need to be polled after an interrupt. The efficient interface between the MID and microprocessor allows this process to be accomplished with minimum overhead.

In a given application, if any of the chip select pins are not used to perform chip select for peripherals, then it may be used as a general purpose input/output pin under software control.

# MID SUPPORTING MASTER AND SLAVE MICROWIRE OPERATION

The MICROWIRE serial data bus is often used as a means of inter-processor communication. The MID may be used either as the Master of the MICROWIRE clock SK or as a Slave to the SK clock fed via CKIN pin. Figure 6 shows an application in which two general microprocessors communicate with each other over the MICROWIRE bus. At the same time other peripherals are also connected to the serial bus. External handshaking between the two processors is required before the MICROWIRE Byte data transfer is executed by the master of the MICROWIRE bus.

# Applications (Continued)

FIGURE 3. MID, Two Types of Microwire Formats; 3-Pin (e.g., TP3071 COMBO II) and 4-Pin (e.g., TP3420, SID)

TL/H/10803-15

TL/H/10803-4

FIGURE 4. MID, TERMINAL EQUIPMENT Application

†The nomenclature for MICROWIRE signal names is as follows:

MICROWIRE controller—SK (clock), SO (data out), SI (data in)

MICROWIRE peripheral—CCLK (clock), CO (data out), CI (data in).

FIGURE 6. Example of MID in Master or Slave MICROWIRE Operation

TL/H/10803-6

Note: For TP3465, the AS (Address Strobe) and DS (Data Strobe) are active high polarity signals. For non-multiplexed busses, AS = 0. FIGURE 7. MID, Connecting to Motorola  $\mu$ Ps.

MICROWIRE controller—SK (clock), SO (data out), SI (data in)

MICROWIRE peripheral—CCLK (clock), CO (data out), CI (data in).

# **Device Electrical Characteristics**

# **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

$\begin{array}{lll} \text{V}_{CC} \text{ to GND} & 7\text{V} \\ \text{Input Voltage} & -0.3\text{V to V}_{CC} + 0.3\text{V} \\ \text{DC Input Current} & I_{\text{I}} \pm 50 \text{ mA} \\ \text{Storage Temperature Range} & -65^{\circ}\text{C to} + 150^{\circ}\text{C} \\ \text{Lead Temperature} \end{array}$

(Soldering, 10 Sec.) 300°C ESD Rating ≥ 1500V

# **Electrical Characteristics**

Unless otherwise noted, limits in **BOLD** characters are electrical testing limits at  $V_{CC}=5.0V$  and  $T_A=\pm25^{\circ}C$ . All other limits are assured by correlation with other production tests and/or product design and characterization for  $V_{CC}=5.0V\pm5\%$  and  $T_A=0^{\circ}C$  to  $\pm70^{\circ}C$ . All signals are referenced to GND.

| Symbol          | Parameter                | Conditions                                                                                            | Li  | imits    | Units |

|-----------------|--------------------------|-------------------------------------------------------------------------------------------------------|-----|----------|-------|

| Cymbol          | rarameter                | Conditions                                                                                            | Min | Max      | Omis  |

| $V_{IL}$        | Input Low Voltage        | All Inputs                                                                                            |     | 0.8      | V     |

| $V_{IH}$        | Input High Voltage       | All Inputs                                                                                            | 2.0 |          | V     |

| V <sub>OL</sub> | Output Low Voltage       | $CS0-7: I_{OL} = 1 \text{ mA}$<br>$SK, SO: I_{OL} = 4 \text{ mA}$<br>$AD(7:0): I_{OL} = 2 \text{ mA}$ |     | 0.4      | V     |

| V <sub>OH</sub> | Output High Voltage      | $CS0-7$ : $I_{OH}=1$ mA<br>SK, SO: $I_{OH}=4$ mA<br>AD(7:0): $I_{OH}=2$ mA                            | 2.4 |          | V     |

| I <sub>IH</sub> | High Level Input Current | All Inputs,<br>GND < V <sub>IN</sub> < V <sub>CC</sub>                                                |     | -10      | μΑ    |

| l <sub>IL</sub> | Low Level Input Current  | All Inputs                                                                                            |     | + 10     | μА    |

| loz             | Output Current in High-Z | AD(7:0), SO                                                                                           |     | ± 20     | μΑ    |

| I <sub>CC</sub> | Dynamic Supply Current   | CKIN = SK = 1 MHz<br>CKIN = SK = 20 MHz                                                               |     | 0.7<br>4 | mA    |

**Timing Characteristics**This section contains timing diagrams for the microprocessor bus interface, MICROWIRE port interface and the Control and Clock timings relationships.

Timing characteristics are derived from worst-case simulations plus guardbanding. Production testing is limited to device functionality.

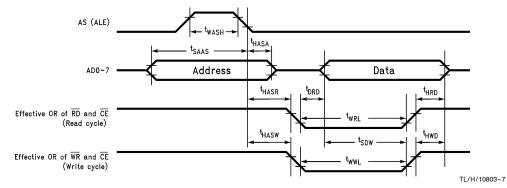

# **NSC/Intel Bus Format**

## **MULTIPLEXED MICROPROCESSOR BUS**

## NON-MULTIPLEXED MICROPROCESSOR BUS

TL/H/10803-8

| Symbol            | Parameter                           | Conditions        | Min | Max | Units |

|-------------------|-------------------------------------|-------------------|-----|-----|-------|

| t <sub>WASH</sub> | Width, Address Strobe High          |                   | 20  |     | ns    |

| t <sub>SAAS</sub> | Setup, Address to Address Strobe    |                   | 10  |     | ns    |

| t <sub>HASA</sub> | Hold, Address Strobe Low to Address |                   | 10  |     | ns    |

| t <sub>HASR</sub> | Hold, Address Strobe to Read Strobe |                   | 10  |     | ns    |

| t <sub>DRD</sub>  | Delay, Read Low to Data             | 100 pF Load       |     | 70  | ns    |

| t <sub>HRD</sub>  | Hold, Read High to Data             |                   | 5   | 40  | ns    |

| t <sub>WRL</sub>  | Width, Read Strobe Low              |                   | 20  |     | ns    |

| t <sub>SDW</sub>  | Setup, Data to Write High           |                   | 30  |     | ns    |

| t <sub>HWD</sub>  | Hold, Write High to Data            |                   | 10  |     | ns    |

| t <sub>WWL</sub>  | Width, Write Strobe Low             |                   | 20  |     | ns    |

| t <sub>SAR</sub>  | Setup, Address to Read Low          | Non-Muxed, MI = 1 | 10  |     | ns    |

| t <sub>HRA</sub>  | Hold, Read High to Address          | Non-Muxed, MI = 1 | 10  |     | ns    |

| t <sub>SAW</sub>  | Setup, Address to Write Low         | Non-Muxed, MI = 1 | 10  |     | ns    |

| t <sub>HWA</sub>  | Hold, Write High to Address         | Non-Muxed, MI = 1 | 10  |     | ns    |

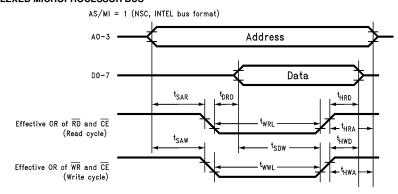

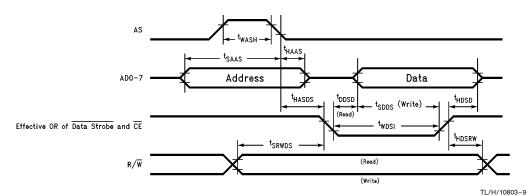

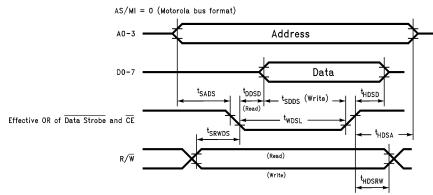

# **Motorola Bus Format**

# MULTIPLEXED MICROPROCESSOR BUS

# NON-MULTIPLEXED MICROPROCESSOR BUS

TL/H/10803-10

Note: For TP3465 MID, the AS (Address Strobe) and DS (Data Strobe) are active high polarity signals. For Non-multiplexed busses AS = 0. See Figure 7 for connection diagram.

| Symbol             | Parameter                               | Conditions        | Min | Max | Units |

|--------------------|-----------------------------------------|-------------------|-----|-----|-------|

| twash              | Width, Address Strobe High              |                   | 20  |     | ns    |

| t <sub>SAAS</sub>  | Setup, Address to Address Strobe        |                   | 10  |     | ns    |

| t <sub>HASA</sub>  | Hold, Address Strobe Low to Address     |                   | 10  |     | ns    |

| t <sub>HASDS</sub> | Hold, Address Strobe to Data Strobe     |                   | 10  |     | ns    |

| t <sub>DDSD</sub>  | Delay, Data Strobe Low to Data (Read)   | 100 pF Load       |     | 70  | ns    |

| t <sub>HDSD</sub>  | Hold, Data Strobe High to Data          |                   | 5   | 40  | ns    |

| t <sub>WDSL</sub>  | Width, Data Strobe Low                  |                   | 20  |     | ns    |

| t <sub>SDDS</sub>  | Setup, Data to Data Strobe High (Write) |                   | 30  |     | ns    |

| tsRWDS             | Setup, R/W Strobe to Data Strobe        |                   | 10  |     | ns    |

| t <sub>HDSRW</sub> | Hold, Data Strobe to R/W                |                   | 10  |     | ns    |

| t <sub>SADS</sub>  | Setup, Address to Data Strobe Low       | Non-Muxed, MI = 0 | 10  |     | ns    |

| t <sub>HDSA</sub>  | Hold, Data Strobe High to Address       | Non-Muxed, MI = 0 | 10  |     | ns    |

| Symbol            | Parameter                              | Conditions        | Min | Max | Units |

|-------------------|----------------------------------------|-------------------|-----|-----|-------|

| f <sub>CKIN</sub> | CKin Frequency                         |                   |     | 20  | MHz   |

| f <sub>SK</sub>   | SK Frequency                           |                   |     | 5   | MHz   |

| t <sub>SKD</sub>  | SK Clock Duration                      |                   | 200 |     | ns    |

| t <sub>SKH</sub>  | SK High Duration                       |                   | 70  |     | ns    |

| t <sub>SKL</sub>  | SK Low Duration                        |                   | 70  |     | ns    |

| t <sub>RSK</sub>  | Rise Time, SK                          | 100 pF Load       |     | 30  | ns    |

| t <sub>FSK</sub>  | Fall Time, SK                          | 100 pF Load       |     | 30  | ns    |

| t <sub>SISK</sub> | Setup Time, SI Valid to SK Edge        |                   | 20  |     | ns    |

| t <sub>HSKI</sub> | Hold Time, SK High to SI Invalid       |                   | 20  |     | ns    |

| t <sub>DSKO</sub> | Delay, SK Edge to SO Data Valid Output |                   |     | 20  | ns    |

| t <sub>DSKZ</sub> | Delay, Last SK to SO TRI-STATE         |                   |     | 30  | ns    |

| t <sub>DWOV</sub> | Delay, WR to SO Valid                  | FMB or<br>FMBD0-7 |     | 50  | ns    |

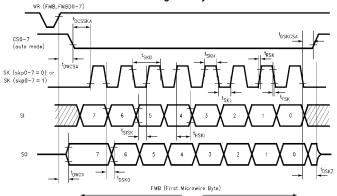

# MICROWIRE Timing for 1 Byte Transfer

TL/H/10803-11

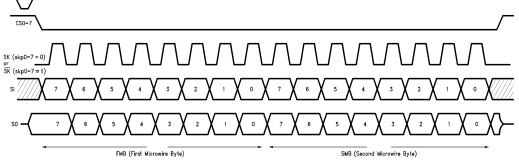

# **MICROWIRE Timing for 2 Byte Transfers**

WR (FMB, FMBD0-7)

TL/H/10803-12

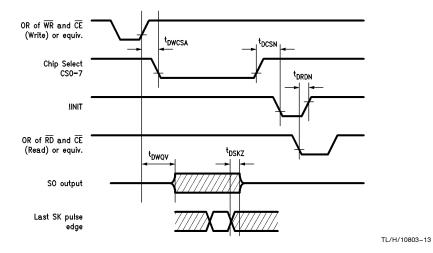

| Symbol              | Parameter                                                              | Conditions  | Min               | Max    | Units    |

|---------------------|------------------------------------------------------------------------|-------------|-------------------|--------|----------|

| t <sub>DWCSA</sub>  | Delay, Write Strobe to CS Asserted                                     | Auto Mode   |                   | 2      | SK Cycle |

| t <sub>DCSSKA</sub> | Delay, CS Active to first SK Edge                                      | Auto Mode   | 0.5 SK<br>- 50 ns | 0.5 SK | ns       |

| <sup>t</sup> DSKCSA | Delay, Last SK Edge to CS Inactive<br>CS Load = 10 pF; SK Load = 50 pF | Auto Mode   | 2.8               | 7.3    | ns       |

| t <sub>DWCSS</sub>  | Delay, Write Strobe (CS Register) to CS Asserted                       | Software    |                   | 30     | ns       |

| t <sub>DCSN</sub>   | Delay, CS High to INT Low                                              |             |                   | 50     | ns       |

| t <sub>DRDN</sub>   | Delay, RD Low to INT High                                              | ST Register |                   | 80     | ns       |

# Physical Dimensions inches (millimeters) (Continued)

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

**National Semiconductor**

National Semiconducto Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018

**National Semiconductor** Europe

Fax: (+49) 0-180-530 85 86 Fax: (+49) U-18U-35U oo oo Email: onjwege etevm2.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tei: (+49) 0-180-532 78 32 Français Tel: (+49) 0-180-532 93 58 Italiano Tel: (+49) 0-180-534 16 80 **National Semiconductor** Hong Kong Ltd.

13th Floor, Straight Block,

Ocean Centre, 5 Canton Rd.

Tsimshatsui, Kowloon

Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960

National Semiconductor

Japan Ltd.

Tel: 81-043-299-2309

Fax: 81-043-299-2408