# BIPOLAR ANALOG INTEGRATED CIRCUIT $\mu PC1854A$

# I<sup>2</sup>C BUS-COMPATIBLE US MTS PROCESSING LSI

The  $\mu$ PC1854A is an integrated circuit for US MTS (Multichannel Television Sound) system with the addition of the I<sup>2</sup>C bus interface. All functions required for US MTS system are incorporated on a single chip.

The  $\mu$ PC1854A allows users to switch modes and adjust filter and separation circuits through the I<sup>2</sup>C bus.

# FEATURES

- Stereo demodulation, SAP (Sub Audio Program) demodulation, dbx noise reduction decoding, and I<sup>2</sup>C bus interface incorporated on a single chip

- Mode switching and filter/separation adjustments through the I<sup>2</sup>C bus

- Power supply: 8 V to 10 V

- On-chip input attenuator for simple interface with intermediate frequency processing IC (I<sup>2</sup>C bus control)

- Output level: 1.4  $V_{p-p}$  (with L+R signals, 100% modulation)

# **APPLICATIONS**

• TV sets and VCRs for north America

#### **ORDERING INFORMATION**

| Part Number     | Package                              |

|-----------------|--------------------------------------|

| $\mu$ PC1854ACT | 28-pin plastic SDIP (10.16 mm (400)) |

| $\mu$ PC1854AGT | 28-pin plastic SOP (9.53 mm (375))   |

The  $\mu$ PC1854A is available only to licensees of THAT Corporation. For information, please call: (508) 229-2500 (U.S.A.), or (03) 5790-5391 (Tokyo).

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version. Not all devices/types available in every country. Please check with local NEC representative for availability and additional information.

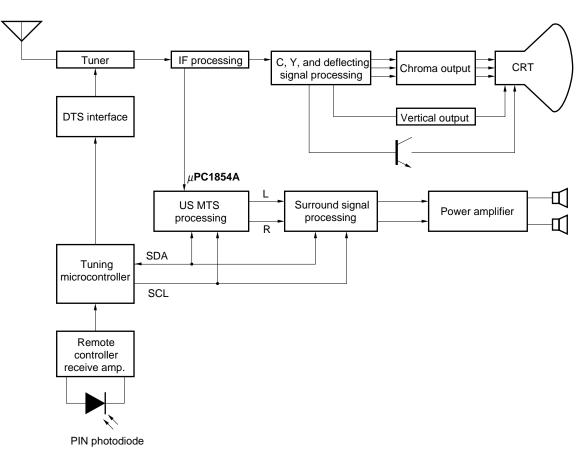

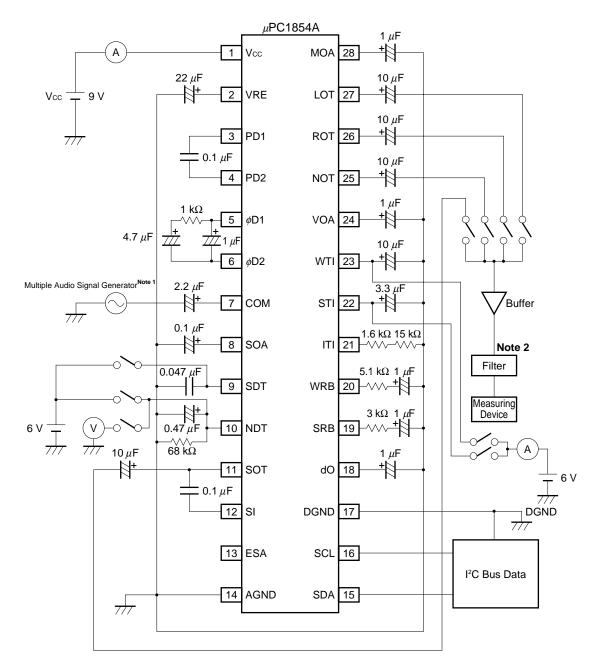

# SYSTEM BLOCK DIAGRAM

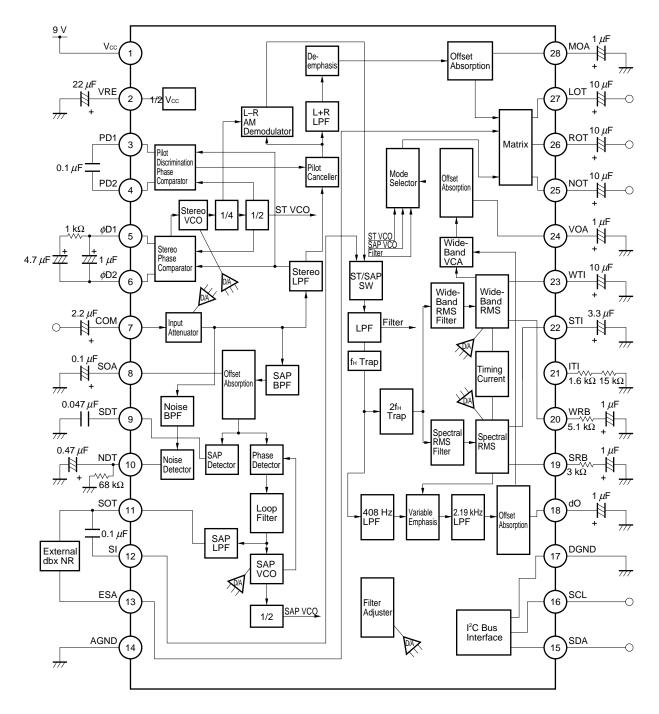

# **BLOCK DIAGRAM**

**Remark** Use the following for external parts.

Resistor : Metal film resistor ( $\pm$ 1 %) for an ITI pin (pin 21). Unless otherwise specified;  $\pm$ 5 % Capacitor : Tantalum capacitor ( $\pm$ 10 %) for STI and WTI pins (pins 22 and 23). Unless otherwise specified;  $\pm$ 20 %

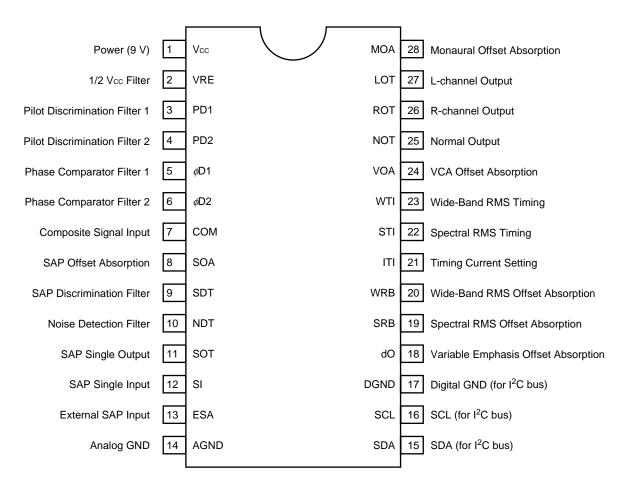

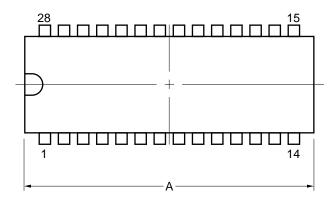

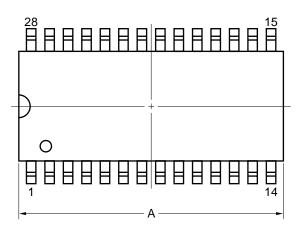

# **PIN CONFIGURATION (Top View)**

### 28-pin plastic SDIP (10.16 mm (400))

• μPC1854ACT

#### 28-pin plastic SOP (9.53 mm (375))

• μPC1854AGT

# CONTENTS

| 1.  | PIN I              | EQUIVALENT CIRCUITS                                         | 6    |

|-----|--------------------|-------------------------------------------------------------|------|

| 2.  | BLO                | CK FUNCTIONS                                                | . 13 |

|     | 2.1                | Stereo Demodulation Block                                   | . 14 |

|     | 2.2                | SAP Demodulation Block                                      | . 15 |

|     | 2.3                | dbx Noise Reduction Block                                   | . 16 |

|     | 2.4                | Matrix Block                                                | . 17 |

| 3.  | I <sup>2</sup> C E | SUS INTERFACE                                               | . 18 |

|     | 3.1                | Data Transfer                                               | . 19 |

|     | 3.2                | Data Transfer Format                                        | . 20 |

| 4.  | I <sup>2</sup> C E | BUS COMMANDS                                                | . 22 |

|     | 4.1                | Subaddress List                                             | . 22 |

|     | 4.2                | Setting Procedure                                           | . 23 |

|     | 4.3                | Explanation of Write Register                               | . 25 |

|     | 4.4                | Explanation of Read Register                                | . 28 |

| 5.  | MOD                | E MATRIX                                                    |      |

|     | 5.1                | L-, R-Channel Output (LOT, ROT pins) Matrix                 | . 30 |

|     | 5.2                | Normal Output (NOT pin) Matrix                              | . 31 |

| 6.  | USA                | GE CAUTIONS                                                 | . 32 |

|     | 6.1                | Caution on Shock Noise Reduction                            | . 32 |

|     | 6.2                | Supply Voltage                                              | . 32 |

|     | 6.3                | Impedance of Input and Output Pins                          | . 32 |

|     | 6.4                | Drive Capability of Output Pins                             | . 32 |

|     | 6.5                | Caution on External Components                              | . 33 |

|     | 6.6                | Change of Electrical Characteristics by External Components | . 33 |

| 7.  | ELE                | CTRICAL SPECIFICATIONS                                      | . 34 |

| 8.  | MEA                | SURING CIRCUIT                                              | . 44 |

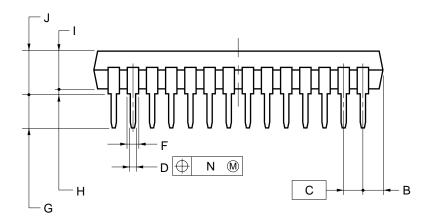

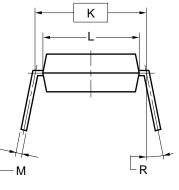

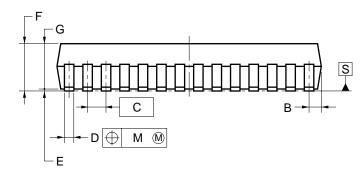

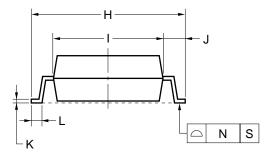

| 9.  | PAC                | KAGE DRAWINGS                                               | . 45 |

| 10. | REC                | OMMENDED SOLDERING CONDITIONS                               | . 47 |

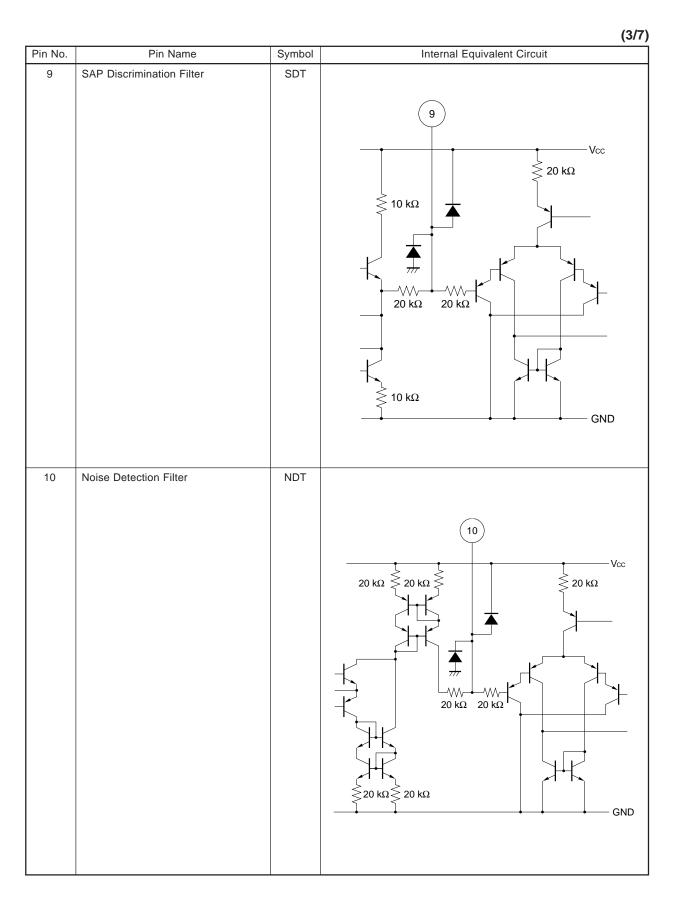

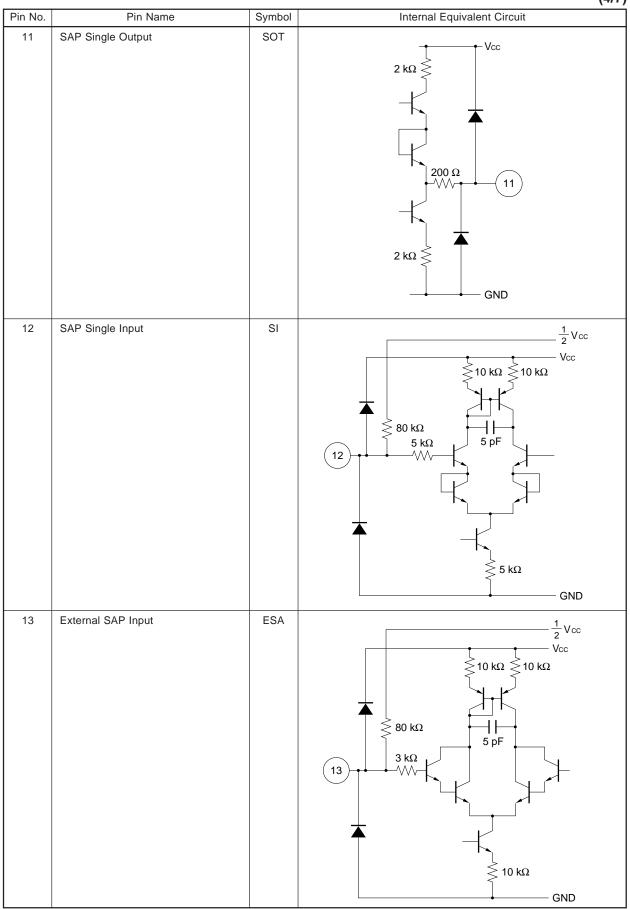

# **1. PIN EQUIVALENT CIRCUITS**

| Pin No. | Pin Name                      | Symbol | Internal Equivalent Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|-------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | Power (9 V)                   | Vcc    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2       | 1/2 Vcc Filter                | VRE    | $(2) K\Omega + (10) $ |

| 3       | Pilot Discrimination Filter 1 | PD1    | $3 \xrightarrow{V_{CC}} 15 \text{ k}\Omega \xrightarrow{5 \text{ k}\Omega} 5 \text{ k}\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4       | Pilot Discrimination Filter 2 | PD2    | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         |                           |             | (2/7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------|---------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No. | Pin Name                  | Symbol      | Internal Equivalent Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5       | Phase Comparator Filter 1 | <i>φ</i> D1 | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 6       | Phase Comparator Filter 2 | <i>φ</i> D2 | $\begin{array}{c} & & & \frac{1}{2} V_{CC} \\ & & & & & \frac{1}{2} V_{CC} \\ & & & & & \frac{1}{2} V_{CC} \\ & & & & & $ |

| 7       | Composite Signal Input    | СОМ         | $7$ $17 \text{ k}\Omega$ $5 \text{ k}\Omega$ $5 \text{ k}\Omega$ $GND$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 8       | SAP Offset Absorption     | SOA         | $\begin{array}{c} & & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & & \\ & & & \\ & & & \\ & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & & \\ & & & & \\ & & & & \\ & & & & & \\ & & & & \\ & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\$                                                                                                                                                                    |

(4/7)

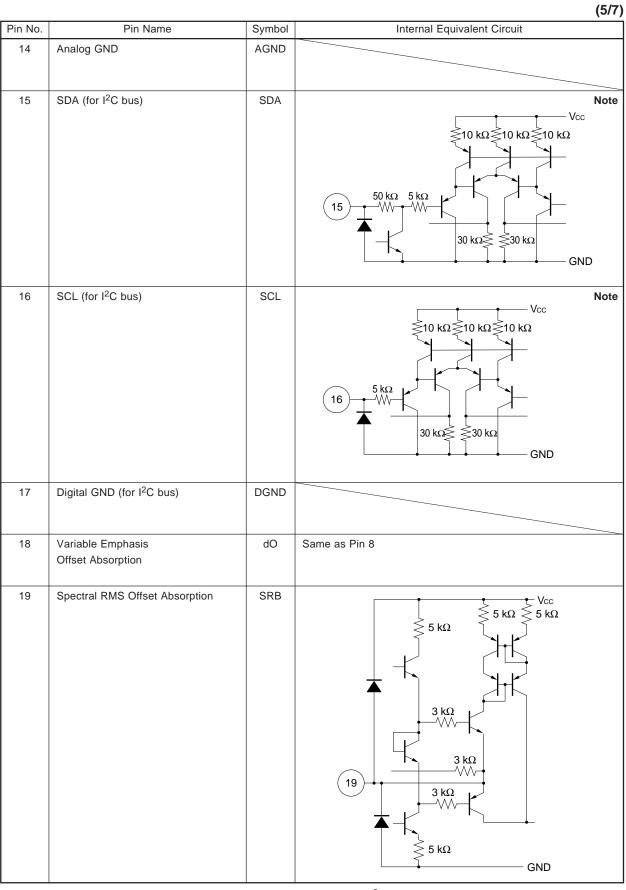

**Note** No protection diode is provided on the Vcc side so that the  $I^2C$  bus line is not pulled to 0 V when the power is OFF (Vcc = 0 V).

(6/7)

|         |                                 |        | (6/7                        |

|---------|---------------------------------|--------|-----------------------------|

| Pin No. | Pin Name                        | Symbol | Internal Equivalent Circuit |

| 20      | Wide-Band RMS Offset Absorption | WRB    | Same as pin 19              |

| 21      | Timing Current Setting          | ITI    | (21)                        |

| 22      | Spectral RMS Timing             | STI    | 22                          |

| 23      | Wide-Band RMS Timing            | WTI    | Same as pin 22              |

| 24      | VCA Offset Absorption           | VOA    | Same as pin 8               |

|         |                            |        | (7/7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------|----------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No. | Pin Name                   | Symbol | Internal Equivalent Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 25      | Normal Output              | NOT    | $ \begin{array}{c}  & 1 \\  & 10 \\  & 10 \\  & 10 \\  & 10 \\  & 10 \\  & 200 \\  & 200 \\  & 200 \\  & 200 \\  & 200 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\  & 1 \\ $ |

| 26      | R-channel Output           | ROT    | Same as pin 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 27      | L-channel Output           | LOT    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 28      | Monaural Offset Absorption | MOA    | Same as pin 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

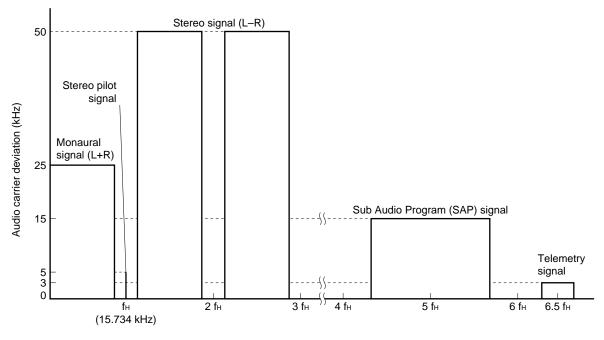

# 2. BLOCK FUNCTIONS

In the US, TV audio signals are broadcast in FM modulation. The stereo (L–R), Sub Audio Program (SAP) and telemetry signals are multiplexed in a higher frequency band than the monaural (L+R) signal (50 Hz to 15 kHz). The US MTS system base-band spectrum is described before:

Modulation frequency (Hz)

|                                   |       | Signal frequency band | Signal processing system                                                                                         | Maximum audio<br>carrier deviation (kHz) |  |

|-----------------------------------|-------|-----------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------|--|

| Monaural signal (L                | _+R)  | 50 Hz to 15 kHz       |                                                                                                                  | 25                                       |  |

| Stereo pilot signal               |       | 15.734 kHz            | Only stereo broadcasting                                                                                         | 5                                        |  |

| Stereo signal (L-F                | ?)    | 50 Hz to 15 kHz       | AM modulation (carrier frequency 2 fH),<br>dbx noise reduction processing                                        | 50                                       |  |

| Sub Audio Program (SAP)<br>signal |       | 50 Hz to 10 kHz       | FM modulation (carrier frequency 5 fH),<br>maximum frequency deviation 10 kHz)<br>dbx noise reduction processing | 15                                       |  |

| Telemetry signal                  | Audio | 0 to 3.4 kHz          | FM modulation (carrier frequency 6.5 fH                                                                          | 3                                        |  |

|                                   | Data  | 0 to 1.5 kHz          | maximum frequency deviation 3 kHz)                                                                               |                                          |  |

#### 2.1 Stereo Demodulation Block

### (1) Stereo LPF

This filter eliminates signals in the vicinity of 5 fH to 6 fH, such as SAP (Sub Audio Program) (5 fH) and telemetry signals (6.5 fH). The  $\mu$ PC1854A's internal L–R demodulator, which uses a double-balanced circuit, demodulates L–R signals by multiplication of the L–R signal with the signal at the L–R carrier frequency (2 fH). The L–R signal tends to receive interference from the 6 fH signal because a square waveform is used as the switching carrier in this method. To eliminate this interference, the  $\mu$ PC1854A incorporates traps at 5 fH and 6 fH. The filter response is adjusted by setting the Filter setting bits (write register, subaddress 02H, bits D0 to D5).

#### (2) Stereo phase comparator

The 8 fH signal generated at the stereo VCO is divided by 8 (4  $\times$  2) and then multiplied by the pilot signal passed through the stereo LPF. The two signals differ from each other by 90 degrees in terms of phase. The resistor and capacitor connected to Pins  $\phi$ D1 and  $\phi$ D2 form a filter that smooths the phase error signal output from the stereo phase comparator, converting the error signal to the DC voltage. When the voltage difference between pins  $\phi$ D1 and  $\phi$ D2 becomes 0 V (strictly speaking, not 0 V by the internal offset voltage), the VCO runs at 8 fH.

The lag/lead filter externally connected to the pins  $\phi$ D1 and  $\phi$ D2 determines the capture range.

## (3) Stereo VCO

The VCO runs at 8 fH with the internal capacitor. The frequency is adjusted by setting the Stereo VCO setting bits (write register, subaddress 01H, bits D0 to D5).

#### (4) Divider (Flip-flop)

Produces two separate fH signals: the inphase fH signal, and the fH signal differing by 90 degrees from the input pilot signal by dividing the 8 fH frequency from the stereo VCO by 8 (4  $\times$  2).

#### (5) Pilot discrimination phase comparator (Level detector)

Multiplies the pilot signal from the COM pin with the inphase fH signal from the divider. The resulting signal is smoothed by passing it through the external filter connected to the PD1 and PD2 pins and converted into DC voltage value that is used to determine whether or not a stereo pilot signal (read register, bit D6) is present.

#### (6) Pilot canceler

The  $f_H$  signal from the divider is added to the stereo signal in resistor matrix depending on the level of the input pilot signal to cancel the pilot signal.

#### (7) L+R LPF

This LPF which has traps at  $f_{H}$  and 24 kHz, allows only the monaural signal to pass through. The filter response is adjusted by setting the Filter setting bits (write register, subaddress 02H, bits D0 to D5).

#### (8) De-emphasis

The filter is a 75- $\mu$ s de-emphasis filter for the monaural signal. The response is adjusted by setting the Filter setting bits (write register, subaddress 02H, bits D0 to D5).

#### (9) L-R AM demodulator

Demodulates the L–R AM-DSB modulated signal by multiplying with the  $2f_H$  signal which is synchronized to the pilot signal. The 2-f\_H square wave is used as the switching carrier.

### 2.2 SAP Demodulation Block

#### (1) SAP BPF

Picks up the SAP signal by the 50-kHz and 102-kHz traps and a response peak at 5 fH. The filter response is adjusted by setting the Filter setting bits (write register, subaddress 02H, bits D0 to D5).

# (2) Noise BPF

The  $\mu$ PC1854A monitors signals picked up by the noise band-pass filter (fo  $\cong$  180 kHz), and distinguishes noise from signals. By this method, the  $\mu$ PC1854A prevents faulty SAP detection in a weak electric field. The filter response is adjusted by setting the Filter setting bits (write register, subaddress 02H, bits D0 to D5).

#### (3) Noise detector

Performs full-wave rectification of noise from noise band-pass filter, changes it to the DC voltage, and inputs it to the comparator. When the noise level exceeds the reference level, the detector recognizes noise, and the noise detection bit (read register, bit D4) is set "1".

The sensitivity and time constant of the circuit are adjusted by setting the values of the resistor and capacitor connected to the NDT.

#### (4) SAP detector

Detects the signal from the SAP band-pass filter and smooths it through the SDT pin and inputs it to the comparator. When the SAP signal is detected, the SAP signal bit (read register, bit D5) is set "1".

## (5) SAP demodulation circuit

The SAP demodulator consists of a phase detector, a loop filter and an SAP VCO (PLL detection circuit). The SAP VCO oscillates at 10 f<sub>H</sub>, and performs phase comparison between the signal divided by 2 of the VCO frequency and the SAP signal to make the PLL. The SAP VCO oscillating frequency is adjusted by setting the SAP VCO setting bits (write register, subaddress 05H, bits D0 to D5).

#### (6) SAP LPF

Eliminates the SAP carrier and high-frequency buzz. The filter consists of a 2nd-order low-pass filter and  $f_H$  trap filter. The filter response is adjusted by setting the Filter setting bits (write register, subaddress 02H, bits D0 to D5).

#### 2.3 dbx Noise Reduction Block

All the filters required for TV-dbx noise reduction are incorporated. The response to these filters is adjusted by setting all the Filter setting bits (write register, subaddress 02H, bits D0 to D5).

#### (1) LPF

This LPF has traps at  $f_H$  and 24 kHz each. The  $f_H$  trap filter minimizes interference by the  $f_H$  signal which is not synchronized with the pilot signal (for example, leakage of the synchronous idle and buzz from the video signal).

#### (2) 408-Hz LPF

This filter is a de-emphasis filter. Its transfer function is as follows:

$$T(f) = \frac{1 + j \frac{f}{5.23k}}{1 + j \frac{f}{408}}$$

#### (3) Variable emphasis

Also called the spectral VCA. It is controlled by the spectral RMS. The transfer function is as follows:

S<sup>-1</sup> (f, b) =

$$\frac{1 + j \frac{f}{20.1k} \times \frac{1 + 51b}{b + 1}}{1 + j \frac{f}{20.1k} \times \frac{1 + 51}{b + 1}}$$

where "b" is the variable transferred from the spectral RMS for controlling.

#### (4) Wide-band VCA

A VCA whose operating frequency range is mainly low to mid frequencies and controlled by the wide-band RMS. The transfer function is as follows:

$$W^{-1}(a) = a$$

where "a" is the variable transferred from the wide-band RMS for controlling.

#### (5) 2.19-kHz LPF

This filter is a de-emphasis filter. Its transfer function is as follows:

$$T(f) = \frac{1 + j \frac{f}{62.5k}}{1 + j \frac{f}{2.19k}}$$

### (6) Spectral RMS filter

A filter that limits the band width of the signal input to the RMS which controls the variable emphasis. The transfer function is as follows:

T (f) =

$$\frac{(j\frac{f}{7.66k})^2}{1+j\frac{f}{7.31k} + (j\frac{f}{7.66k})^2} \times \frac{j\frac{f}{3.92k}}{1+j\frac{f}{3.92k}}$$

#### (7) Wide-band RMS filter

A filter that limits the band width of the signal input to the wide-band RMS which controls the wide-band VCA. The transfer function is as follows:

$$T(f) = \frac{1}{1 + j \frac{f}{2.09k}}$$

#### (8) Spectral RMS

Detects the RMS value of the signal passed through the spectral RMS filter, and converts the signal to the DC voltage. The release time is set by adjusting the current I<sub>T</sub> of the  $\mu$ PC1854A and the capacitance of the external capacitor connected to the STI pin. The current I<sub>T</sub> is set by the current value output from the ITI pin.

#### (9) Wide-band RMS

Detects the RMS value of the signal passed through the wide-band RMS filter, and converts the signal to the DC voltage. The release time is set by adjusting the current  $I_T$  of the  $\mu$ PC1854A and the capacitance of the external capacitor connected to the WTI pin. The current  $I_T$  is set by the current value output from the ITI pin.

#### 2.4 Matrix Block

#### (1) Matrix

Adds L+R signal and L-R signal to output L signal, and subtracts L+R signal from L-R signal to output R signal.

#### (2) Mode selector

Selects the user-selected mode among the monaural, stereo, SAP, external SAP input signals, and mute, then outputs it from the NOT, ROT and LOT pins.

# 3. I<sup>2</sup>C BUS INTERFACE

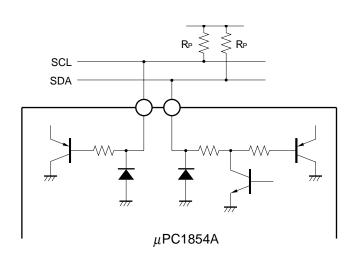

The  $\mu$ PC1854A uses the I<sup>2</sup>C bus interface that is developed by Philips. The serial clock line (SCL) and serial data line (SDA) employ the 2-wire configuration as shown in **Figure 3-1**.

The  $\mu$ PC1854A contains seven (1 byte 8 bits) write registers and one read register through the I<sup>2</sup>C bus interface circuit.

#### Serial Clock Line (SCL)

The master CPU outputs a serial clock to achieve data synchronization. The  $\mu$ PC1854A receives serial data based on this clock. The input level is CMOS-compatible. The clock frequency is from 0 to 100 kHz.

#### Serial Data Line (SDA)

The master CPU outputs data synchronously with the serial clock. The  $\mu$ PC1854A receives this data based on the serial clock. The input level is CMOS-compatible.

No protection diode is provided on the Vcc side for the SCL and SDA pins so that the  $l^2C$  bus line is not pulled to 0 V when the power is OFF (Vcc = 0 V).

#### 3.1 Data Transfer

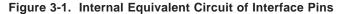

#### (1) Start condition

The start condition is created when SDA changes from high to low while SCL is high, as shown in **Figure 3-2**. When the  $\mu$ PC1854A receives this information, it captures data sent in synchronization with the clock.

#### (2) Stop condition

The stop condition is created when SDA changes from low to high while SCL is high, as shown in **Figure 3-2**. When the  $\mu$ PC1854A receives this information, it stops receiving or outputting data.

Figure 3-2. Data Transfer Start/Stop Condition

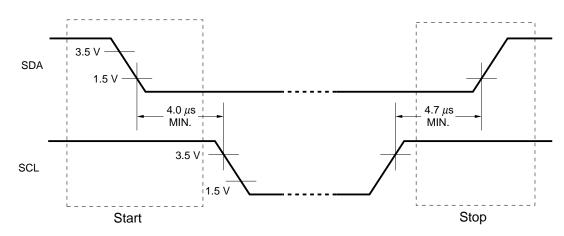

#### (3) Data transfer

When transferring data, be sure to switch data only when SCL is low, as shown in **Figure 3-3**. When SCL is high, the data must not be changed.

★

#### Figure 3-3. Data Transfer

#### Notes 1. Data hold time: 300 ns MIN.

- 2. Data setup time: 250 ns MIN.

- 3. Interval when data cannot be changed

- 4. Interval when data can be changed

#### 3.2 Data Transfer Format

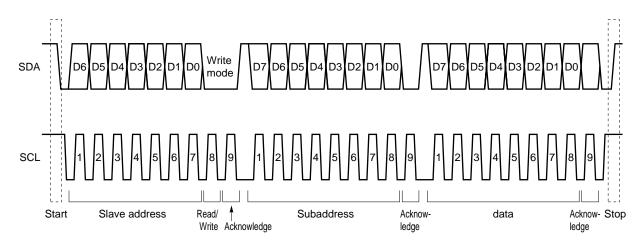

An example of data transfer in the write mode is shown in Figure 3-4.

Data consists of 8-bit units. This 8-bit data must always be followed by an acknowledge bit. Data transfer must be done on an MSB-first basis.

The first byte after a start condition specifies the slave address. The slave address consists of 7 bits. Table 3-1 shows the slave addresses of the  $\mu$ PC1854A. These slave addresses are registered by Philips.

| Slave address<br>Mode | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Read/Write |

|-----------------------|----|----|----|----|----|----|----|------------|

| Write                 | 1  | 0  | 0  | 0  | 1  | 1  | 1  | 0          |

| Read                  | 1  | 0  | 0  | 0  | 1  | 1  | 1  | 1          |

Table 3-1. Slave Addresses of µPC1854A

The bit following the slave address is the read/write bit specifying the direction of the data to be transferred. During the read operation, data is transferred from the  $\mu$ PC1854A to the master CPU. During the write opera-

tion, data is transferred from the master CPU to the  $\mu$ PC1854A. "0" and "1" are written to the Read/Write bit during the Write and Read modes, respectively.

The byte following the slave address is the subaddress of the  $\mu$ PC1854A in the write mode.

The  $\mu$ PC1854A has seven subaddresses, SA<sub>0</sub> to SA<sub>6</sub>, which are made up of 8 bits. Following the subaddress byte is the data to be set to the subaddress.

۱ ۱

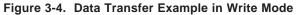

## (1) 1-byte data transfer

The format for 1-byte data transfer is the following:

#### (2) Continuous data transfer

The format when transferring multiple (7) bytes of data at one time is the following:

|  | Start | Slave<br>address | Write<br>mode | Acknow<br>-ledge | Subaddress | Acknow<br>-ledge | Data1 | Acknow<br>-ledge | Data2 | Acknow<br>-ledge | · |  | Data7 | Acknow<br>-ledge | Stop |

|--|-------|------------------|---------------|------------------|------------|------------------|-------|------------------|-------|------------------|---|--|-------|------------------|------|

|--|-------|------------------|---------------|------------------|------------|------------------|-------|------------------|-------|------------------|---|--|-------|------------------|------|

The master CPU transfers "00H" as subaddress SA0 following the start condition and slave address. After the subaddress SA0, the master CPU transfers the SA0 data, and continues with SA1, SA2, ..., SA6 data without transferring stop conditions in between.

The subaddress is automatically incremented. Finally, the stop condition is transferred and the transfer is completed.

#### (3) Data read

The  $\mu$ PC1854A has one read register. The contents of this register can be read by the master CPU. The format when data is read is the following:

| Start | Slave<br>address | Read | Acknow<br>-ledge | Data | Non-<br>acknow<br>-ledge | Stop |

|-------|------------------|------|------------------|------|--------------------------|------|

|-------|------------------|------|------------------|------|--------------------------|------|

#### (4) Acknowledge

In the case of the I<sup>2</sup>C bus, an acknowledge bit is added to the data as the 9th bit to determine whether data transfer was successful. The master determines the success or failure of data transfer based on whether this acknowledge bit is a logical low or high.

If the acknowledge interval is a logical low, this indicates that data transfer was successful. If it is a logical high, this indicates that data transfer was unsuccessful or that the slave side forcibly released the bus as a non-acknowledge state.

# 4. I<sup>2</sup>C BUS COMMANDS

# 4.1 Subaddress List

## (1) Write register (command list)

| Subaddress | MSB |                |                 |                     |                        |                  |                 | LSB         |  |  |  |  |

|------------|-----|----------------|-----------------|---------------------|------------------------|------------------|-----------------|-------------|--|--|--|--|

| Subaddress | D7  | D6             | D5              | D4                  | D3                     | D2               | D1              | D0          |  |  |  |  |

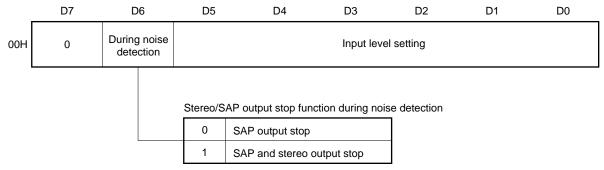

| 00H        | 0   | During noise   |                 | Input level setting |                        |                  |                 |             |  |  |  |  |

|            |     | detection      |                 |                     |                        |                  |                 |             |  |  |  |  |

|            |     | Stereo/SAP     |                 |                     |                        |                  |                 |             |  |  |  |  |

|            |     | output stop    |                 |                     |                        |                  |                 |             |  |  |  |  |

|            |     | 0: SAP OFF     |                 |                     |                        |                  |                 |             |  |  |  |  |

|            |     | 1: Stereo,     |                 |                     |                        |                  |                 |             |  |  |  |  |

|            |     | SAP OFF        |                 |                     |                        |                  |                 |             |  |  |  |  |

| 01H        | 0   | fH monitor     |                 |                     | Stereo VC              | CO setting       |                 |             |  |  |  |  |

|            |     | ON/OFF         |                 |                     |                        |                  |                 |             |  |  |  |  |

|            |     | 0: OFF         |                 |                     |                        |                  |                 |             |  |  |  |  |

|            |     | 1: ON          |                 |                     |                        |                  |                 |             |  |  |  |  |

| 02H        | 0   | Pilot canceler |                 |                     | Filter                 | setting          |                 |             |  |  |  |  |

|            |     | ON/OFF         |                 |                     |                        |                  |                 |             |  |  |  |  |

|            |     | 0: ON          |                 |                     |                        |                  |                 |             |  |  |  |  |

|            |     | 1: OFF         |                 |                     |                        |                  |                 |             |  |  |  |  |

| 03H        | 0   | 0              |                 |                     | Low-band sep           | aration setting  |                 |             |  |  |  |  |

| 04H        | 0   | 0              |                 |                     | High-band sep          | paration setting |                 |             |  |  |  |  |

| 05H        | 0   | 5 fH monitor   |                 |                     | SAP VC                 | O setting        |                 |             |  |  |  |  |

|            |     | ON/OFF         |                 |                     |                        |                  |                 |             |  |  |  |  |

|            |     | 0: OFF         |                 |                     |                        |                  |                 |             |  |  |  |  |

|            |     | 1: ON          |                 |                     |                        |                  |                 |             |  |  |  |  |

| 06H        | 0   | 0              | Normal track    | Normal track        | SAP1/SAP2              | Stereo/SAP       | Forced monaural | Mute ON/OFF |  |  |  |  |

|            |     |                | output select 1 | output select 2     | switch <sup>Note</sup> | switch           | ON/OFF          |             |  |  |  |  |

|            |     |                | 0: SAP          | 0: SAP              | 0: SAP1                | 0: Stereo        | 0: OFF          | 0: ON       |  |  |  |  |

|            |     |                | 1: External SAP | 1: Monaural         | 1: SAP2                | 1: SAP           | 1: ON           | 1: OFF      |  |  |  |  |

Note Output when SAP1 or SAP2 is selected is as follows:

| $\backslash$ | LOT pin (L-channel output) | ROT pin (R-channel output) |

|--------------|----------------------------|----------------------------|

| SAP1         | SA                         | ۱P                         |

| SAP2         | Monaural (L+R)             | SAP                        |

Remark The initial value of write register after power-on reset

- Mute register (subaddress 06H, bit D0) = 0 (Mute: ON)

- Other registers = undefined (setting properly after power-on reset)

# (2) Read register

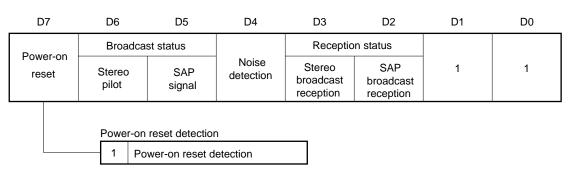

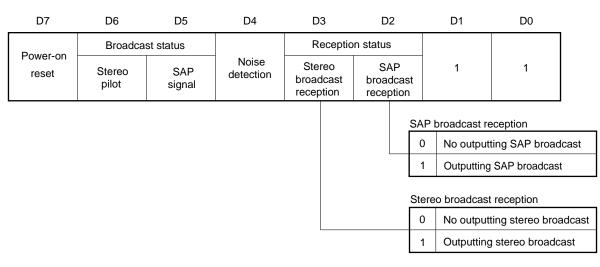

| MSB<br>D7      | D6                                               | D5                                             | D4                               | D3                                                                | D2                                                             | D1 | LSB<br>D0 |

|----------------|--------------------------------------------------|------------------------------------------------|----------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------|----|-----------|

| Power-on reset | Broadcast status                                 |                                                | Noise detection                  | Receptio                                                          | on status                                                      | 1  | 1         |

| 1: Detection   | Stereo pilot<br>0: Not available<br>1: Available | SAP signal<br>0: Not available<br>1: Available | 0: Not available<br>1: Available | Stereo broadcast<br>reception<br>0: Not available<br>1: Available | SAP broadcast<br>reception<br>0: Not available<br>1: Available |    |           |

#### 4.2 Setting Procedure

Precise adjustment of the dbx decoder is absolutely critical for optimum performance. Where possible, the adjustment should be performed after the  $\mu$ PC1854A is mounted on the chassis and with the video system active.

Set the data of write register as follows before the adjustment, because the registers other than the Mute register are defined.

| Bit<br>Subaddress | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|-------------------|----|----|----|----|----|----|----|----|

| 00H               | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  |

| 01H               | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  |

| 02H               | 0  | 0  | 1  | 1  | 1  | 1  | 1  | 1  |

| 03H               | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  |

| 04H               | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  |

| 05H               | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  |

| 06H               | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  |

#### Table 4-1. Default Setting of Write Register

#### (1) Input level setting (write register, subaddress 00H, bits D5 to D0)

- <1> Write "1" to bit D0 (Mute: OFF) of subaddress 06H.

- <2> Input sine wave of 300 Hz, 150 mVrms to COM pin.

- <3> Set bits D5 to D0 (Input level setting bits) of subaddress 00H so that the output level of ROT pin is 500 mVrms (±10 mVrms).

#### (2) Stereo VCO setting (write register, subaddress 01H, bits D6 to D0)

Perform this adjustment with no signal applied.

- <1> Write "1" to bit D0 (Mute: OFF) of subaddress 06H.

- <2> Write "1" to bit D6 (fH monitor: ON) of subaddress 01H.

- <3> Connect frequency counter to ROT pin, and set bits D5 to D0 (Stereo VCO setting bits) of subaddress 01H so that frequency counter displays 15.73 kHz (±0.1 kHz).

- <4> When setting is completed, write "0" to bit D6 (fH monitor: OFF) of subaddress 01H.

#### (3) Filter setting (write register, subaddress 02H, bits D6 to D0)

- <1> Write "1" to bit D6 (Pilot canceler: OFF) of subaddress 02H.

- <2> Input pilot signal (15.734 kHz, 30 mV<sub>rms</sub> or higher<sup>Note</sup>) to COM pin and set data of bits D5 to D0 (Filter setting bits) of subaddress 02H so that the output level of the ROT pin becomes as small as possible (Decrease the set data from 63 (decimal)).

- <3> When setting is completed, write "0" to bit D6 (Pilot canceler: ON) of subaddress 02H.

Note 100 mVrms is recommended.

#### (4) Separation setting (write register, subaddresses 03H and 04H, bits D5 to D0)