# MXT3020

## reference manual

version 4.0

Order Number: 100107-04 Revision C of the MXT3020

#### July 1999

Copyright (c) 1999 by Maker Communications, Inc. All rights reserved.

Printed in the United States of America.

The information in this document is believed to be correct, however, the information can change without notice. Maker Communications, Inc. disclaims any responsibility for any consequences resulting from the use of the information contained in this document.

The hardware, software, and the related documentation is provided with RESTRICTED RIGHTS. Use, duplication, or disclosure by the U.S. Government is subject to restrictions as set forth in subparagraph (c)(1) (ii) of The Rights in Technical Data and Computer Program Product clause at DFARS 252.227-7013 or subparagraphs (c)(1) and (2) of the Commercial Computer Software-Restricted Rights at 48 CFR 52.227-19, as applicable.

Contractor/manufacturer is: Maker Communications, Inc. 73 Mount Wayte Avenue, Framingham, MA 01702

CellMaker and BridgeMaker are registered trademarks of Maker Communications, Inc. AccessMaker, High-Intensity Communications Processor, High-Intensity Communications Processing, PortMaker, Octave, and SimMaker are trademarks of Maker Communications, Inc.

All other trademarks are owned by their respective companies.

This manual supercedes and obsoletes the following Maker Communications publication:

100107-03 - MXT3020 Reference Manual, dated July 1998 100350-01 - MXT3020 Reference Manual, errata sheet, Sept/Oct 1998

# CONTENTS

#### Preface xi

Maker Products xii Traffic Stream Processing Solutions xii ATM Cell Processing Solutions xiii Using this Manual xiv Additional Document References xiv Organization of this manual xvii

#### CHAPTER 1

#### Device Overview 1

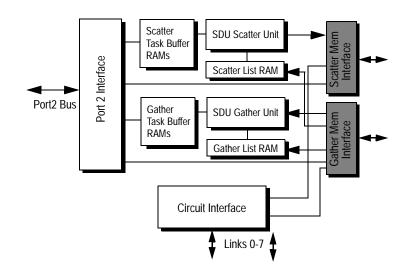

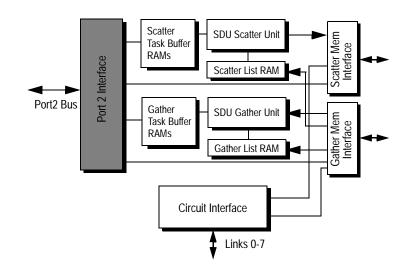

Circuit Interface 4 The Data Mover (Scatter/Gather) Units 5 Scatter and Gather Memory Interfaces 6 Port2 Interface 7

#### **CHAPTER 2**

#### Circuit Interface 9

Circuit Interface registers 11 Per-Link registers 11 Global registers 11 Link Configuration register 12 Added detail: Bits 12-10 – clock source control 15 Added detail: Bit 6 – link pair mode 19 Added detail: BSCE pin 21 Link Buffer Address counters 23

Link Rx Buffer Address counter 23 Link Tx Buffer Address counter 24 Details of the Link Tx/Rx Buffer Address counters 25 Link Tri-state Control Address counter 27 An example of the tri-state control process 27 The tri-state enable control map 28 Summary of tri-state control operation 32 Link service clock generation registers 33 Link Service Clock N register 34 Link Service Clock K register 35 Link Service Clock L counter 35 Link FTC counter 36 Link SRTS Value register 36 CI Tri-state Control Base Address register 37 CI Configuration register 37 MAXDS0, MAXTBS, and MAXRBS and buffer sizing 40 CI Quiet Frame Base Address register 42 Quiet Logic 43 CI SRTS FTC register 45 CI SRTS Valid Status register 45 CI Status register 46 Interface Pins 47

#### **CHAPTER 3**

#### Data Mover Units and Task Buffer RAMs 49

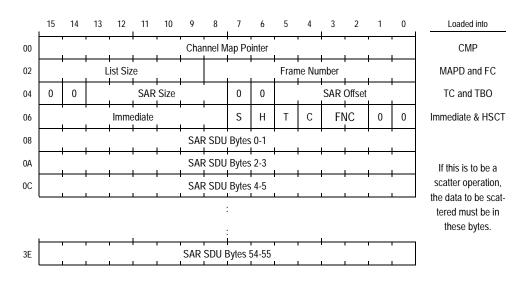

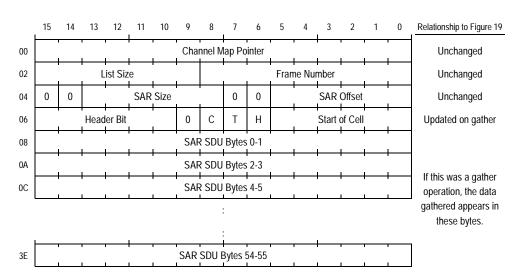

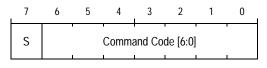

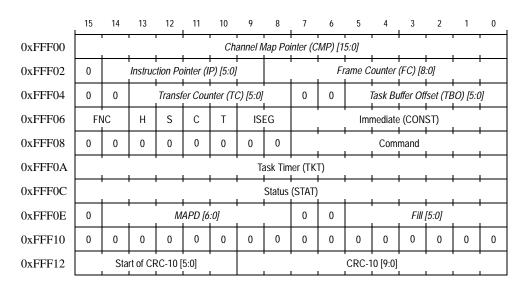

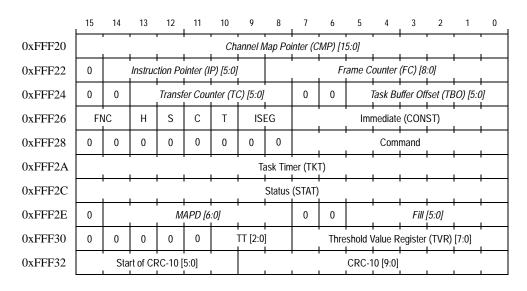

Lists and Tasks 50 Activating the Data Mover Unit 51 Loading list blocks 51 Loading the Task Buffer RAM 53 Data Mover Unit Instruction Set 54 Task Buffer Format 55 Channel Map Pointer 56 List Size 57 Frame Number 57 SAR Size 57 SAR Offset 57 Register 06 (write) - Additional control bits 58 Register 06 (read) - Additional status bits 60 Data Mover Unit Registers 61

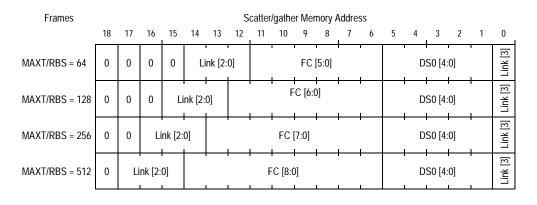

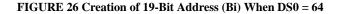

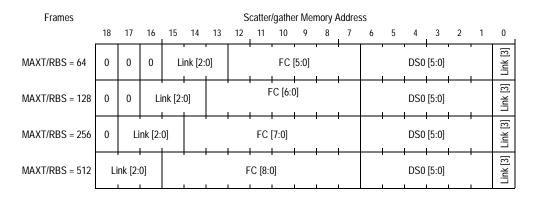

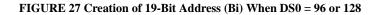

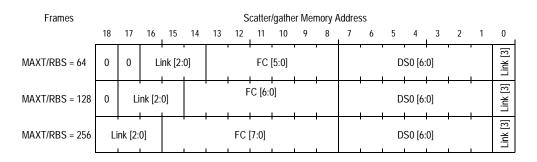

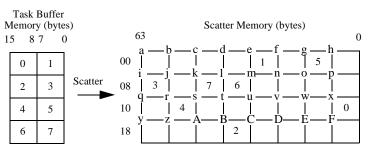

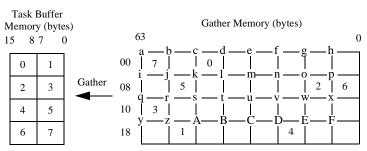

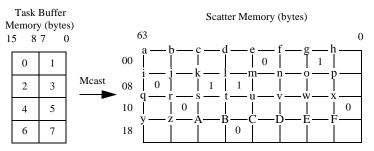

Channel Map Pointer (CMP) 62 Instruction Pointer (IP) 63 Frame Counter (FC) 63 Transfer Counter (TC) 63 CRC Function Code (FNC) 63 HSCT Control Flags 63 Instruction Segment (ISEG) 64 Immediate (CONST) 64 Command (CMD) 64 Task Timer (TKT) 65 Status (STAT) 65 MAPD and Fill 65 TT register 66 TVR register 66 CRC-10 [9:0] 66 Start of CRC-10 [5:0] 66 Address Generation 67 List Block Address Generation 67 List RAM Address Generation 67 Scatter/Gather Memory Address Generation 68 Task Buffer RAM Address Generation 71 Interface Pins 71 Examples of Scatter and Gather Operations 72 Scatter 72 Gather 73 Multicast 74

CHAPTER 4

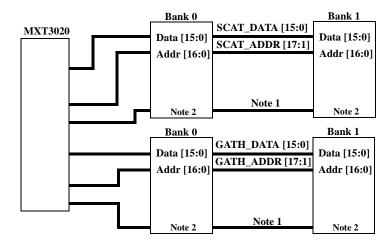

#### Scatter and Gather Memory Interfaces 75

Scatter Memory Controller 76 Gather Memory Controller 77 Determining Scatter and Gather Memory requirements 78 *Scatter Memory* 78 *Gather Memory* 78 Interface Pins 79

CHAPTER 5

#### Port2 Interface 81

MXT3020 addressing 82 MXT3020 address space 83 Interface Pins 86

#### **CHAPTER 6**

### Register Reference 87

Channel Map Pointer (TBR and DMU) 89 CI Configuration register 90 CI Quiet Frame Base Address register 92 CI SRTS FTC register 93 CI SRTS Valid Status register 94 CI Status register 95 CI Tri-state Control Base Address register 96 Command register 97 CRC-10 register 98 Immediate and Control Flags register (TBR and DMU) 99 Instruction Pointer and Frame Counter 102 Link Configuration register 103 Link FTC counter 105 Link Rx Buffer Address counter 106 Link Service Clock K register 107 Link Service Clock L counter 108 Link Service Clock N register 109 Link SRTS Value register 110 Link Tri-state Control Address counter 111 Link Tx Buffer Address counter 112 List Size and Frame Number 113 MAPD and FILL registers 114 SAR SDU registers 115 SAR Size and SAR Offset 116 TT and TVR registers 117 Status register 118 Task Timer register 119 Transfer Counter and Task Buffer Offset registers 120

#### CHAPTER 7

Interfacing Guidelines 123

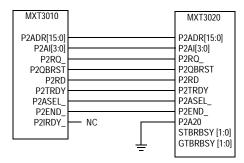

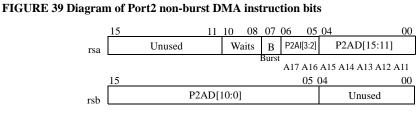

Interfacing to Scatter/Gather Memory 124 Interfacing the MXT3020 to the MXT3010 126 Port2 Burst and Non-Burst Operation 127 The DMA2 instructions 128

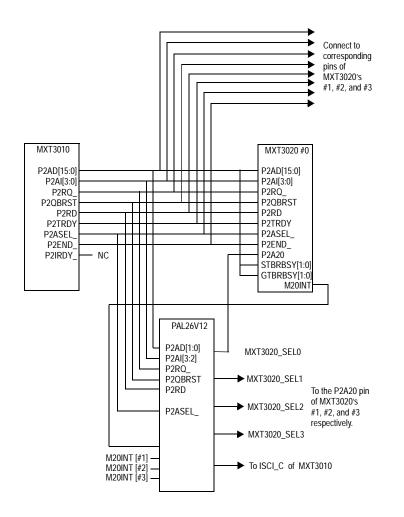

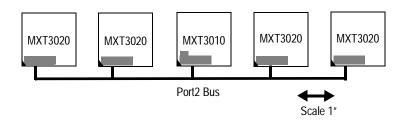

Multiple MXT3020 implementation 130

Device selection code example 132

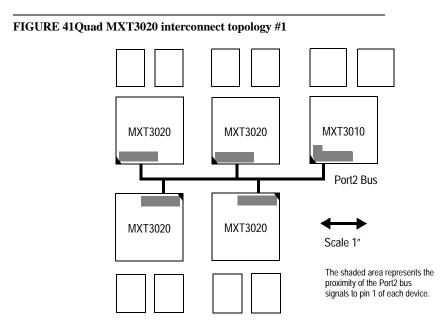

Scatter/Gather Task Buffer Busy flags 134 Quad MXT3020 layout considerations 135 Timing analysis of quad MXT3020 on Port 2 136 PCB Design Concerns for quad MXT3020 137

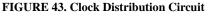

Clock tree distribution 138

CHAPTER 8

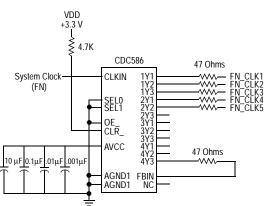

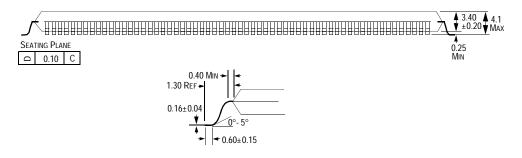

#### Timing 139

MXT3020 timing - general information 139 Definition of switching levels 139 Input clock details 140 Timing 141 Circuit Interface 142 Port2 Interface timing 144 Scatter/Gather Memory Interface 149 Status Interface 153 SCSA Bus Timing 154 MVIP Bus Timing 157 MXT3020 Assistance to Non-burst Devices 158 MXT3020 reset timing 159

#### **CHAPTER 9**

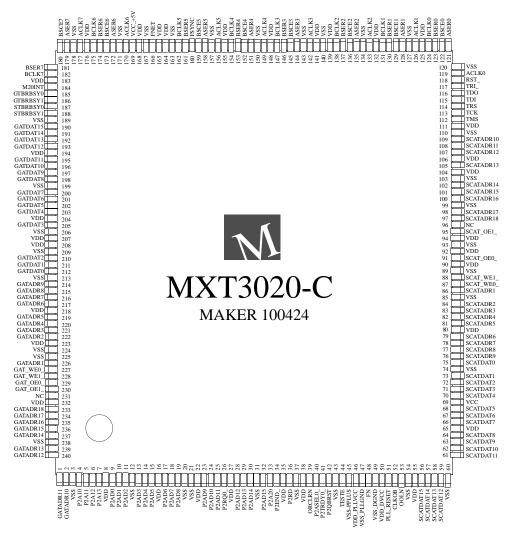

#### Pin Information 161

MXT3020 pinout 162 MXT3020 signal descriptions 163 JTAG/PLL Miscellaneous pin terminations 170 Pin Listing 171

### CHAPTER 10 Electrical Parameters 177

MXT3020 maximum ratings and operating conditions 178 DC electrical characteristics 179

MXT3020 power sequencing 179

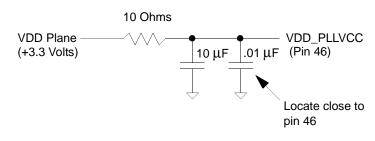

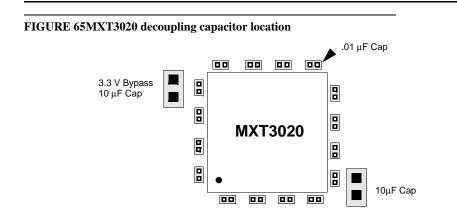

MXT3020 PLL considerations 180 Overview 180 VDD\_PLLVCC decoupling 180 General decoupling 181 Reference clock jitter 182

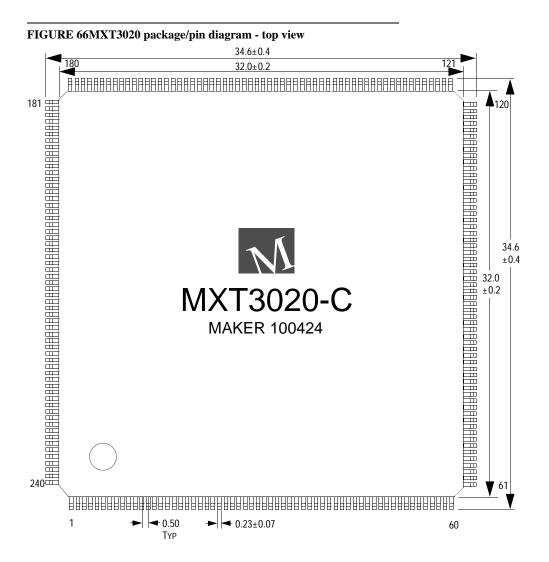

| CHAPTER 11 | Mechanical and Thermal Information                                   | 185 |

|------------|----------------------------------------------------------------------|-----|

|            | MXT3020 mechanical/thermal information 186<br>Storage conditions 187 |     |

| APPENDIX A | Acronyms 189                                                         |     |

| APPENDIX B | Registered Decoder PAL Source Code 191                               |     |

## **List of Figures**

Figure 1 T1/E1/ATM Interface Using the MXT3010 and MXT3020 2 Figure 2 Block diagram of the MXT3020 3 Figure 3 Link Configuration register bit assignments 12 Figure 4 SRTS support hardware 14 Figure 5 Configuration Uni-1 17 Figure 6 Configuration Uni-2 17 Figure 7 **Configuration Uni-3** 18 Figure 8 **Configuration Uni-4** 18 Figure 9 Configuration Bi-1 18 Figure 10 **Configuration Bi-2** 19 19 Figure 11 **Configuration Bi-3** Figure 12 MXT3020 operating modes - eight link pairs 20 Figure 13 MXT3020 operating modes - ASER and BSER 21 Figure 14 Tri-state enable for the ASER pins 28 Figure 15 ASER and BSER tri-state enable bit usage (bidirectional) 29 Figure 16 ASER and BSER tri-state enable bit usage (unidirectional) 31 Figure 17 Link service clock generation registers 33 Figure 18 Ouiet Frame Allocation Map 44 Figure 19 Pre-Scatter/Gather Task Buffer Register Format 55 Figure 20 Post-Scatter/Gather Task Buffer Register Format 56 Figure 21 DMU register set organization 62 Figure 22 Creation of 19-Bit Address (Uni) When DS0 = 24 or 32 69 Figure 23 Creation of 19-Bit Address (Uni) When DS0 = 64 69 Creation of 19-Bit Address (Uni) When DS0 = 96 or 128 Figure 24 69 Figure 25 Creation of 19-Bit Address (Bi) When DS0 = 24 or 3270 Figure 26 Creation of 19-Bit Address (Bi) When DS0 = 64 70 Figure 27 Creation of 19-Bit Address (Bi) When DS0 = 96 or 128 70 Figure 28 Example of a Scatter Operation 72 Figure 29 Example of a Gather Operation 73 Figure 30 Example of an Mcast Operation 74 Figure 31 MXT3020 address space 83 Figure 32 Scatter Data Mover Unit Register Map 84 Figure 33 Gather Data Mover Unit Register Map 84 Figure 34 Circuit Interface per-link registers 85 Figure 35 Circuit Interface global and SRTS value registers 86 Schematic of MXT3020C to Scatter/Gather Memories Figure 36 124 Figure 37 MXT3020 to MXT3010 interconnection schematic 126 Figure 38 Diagram of Port2 burst DMA instruction bits 128 Figure 39 Diagram of Port2 non-burst DMA instruction bits 129 Figure 40 Schematic of circuit for interfacing quad MXT3020's 131

- Figure 41 Quad MXT3020 interconnect topology #1 135

- Figure 42 Quad MXT3020 interconnect topology #2 135

- Figure 43 Clock Distribution Circuit 138

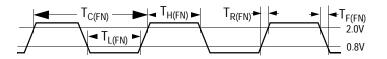

- Figure 44 Switching level voltages 139

- Figure 45 Input clock waveform (pin FN) 140

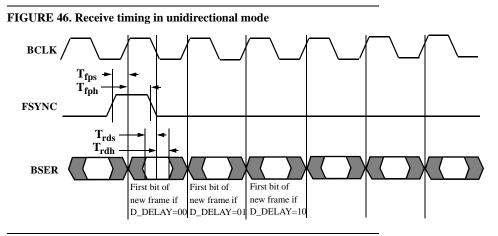

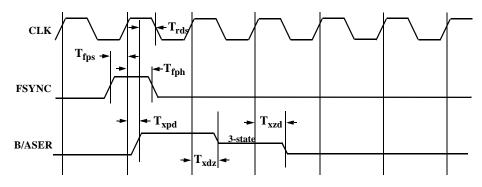

- Figure 46 Receive timing in unidirectional mode 143

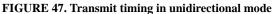

- Figure 47 Transmit timing in unidirectional mode 143

- Figure 48 Receive/Transmit timing in bidirectional mode 143

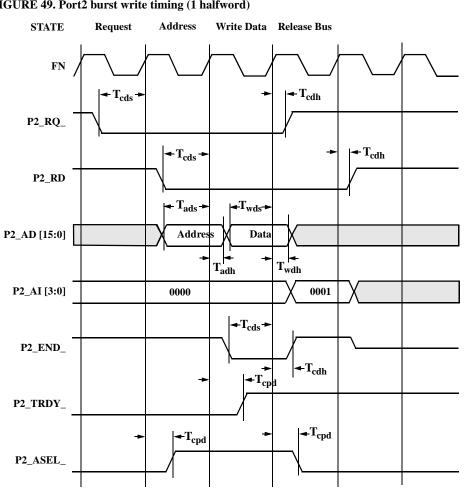

- Figure 49 Port2 burst write timing (1 halfword) 145

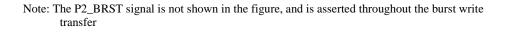

- Figure 50 Port2 burst write timing (4 halfwords) 146

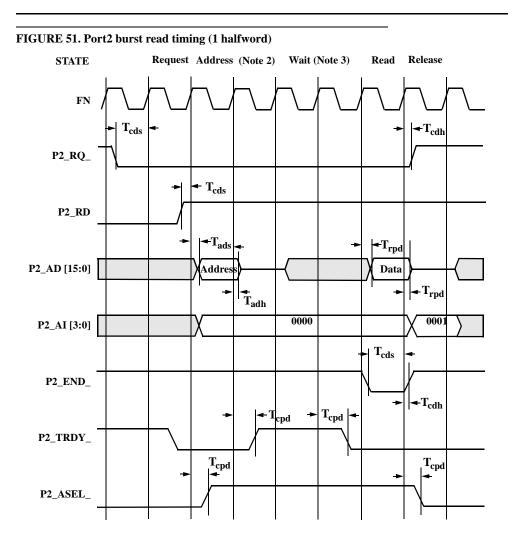

- Figure 51 Port2 burst read timing (1 halfword) 147

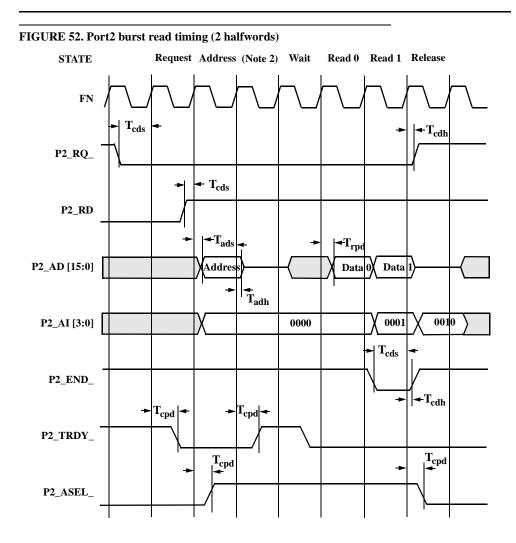

- Figure 52 Port2 burst read timing (2 halfwords) 148

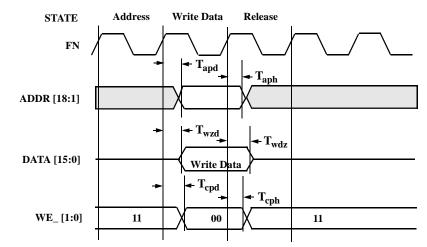

- Figure 53 Scatter/Gather Memory Halfword Write Timing 150

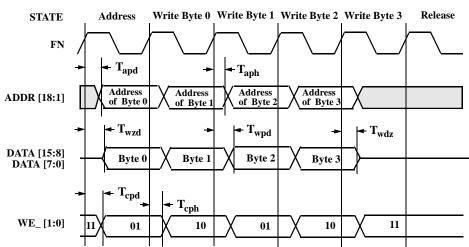

- Figure 54 Scatter/Gather Memory Burst Write (Byte) Timing 151

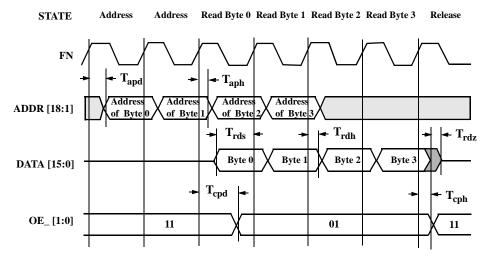

- Figure 55 Scatter/Gather Memory Burst Read (Byte/Halfword) Timing 152

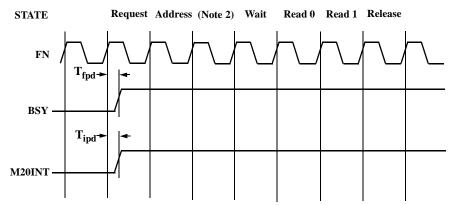

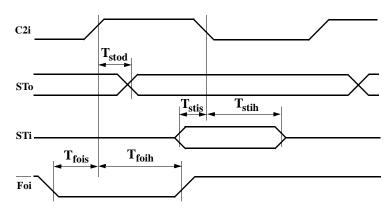

- Figure 56 Status interface timing 153

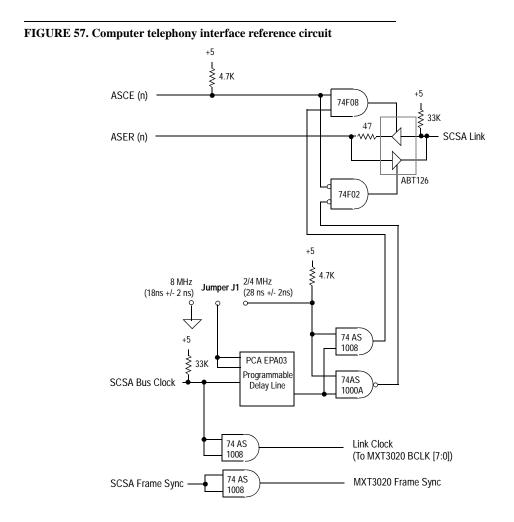

- Figure 57 Computer telephony interface reference circuit 154

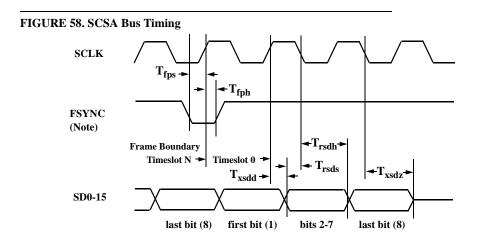

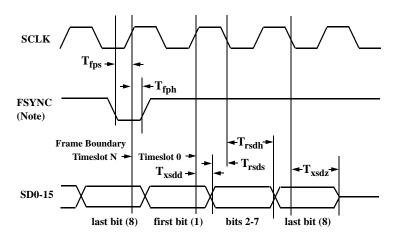

- Figure 58 SCSA Bus Timing 155

- Figure 59 SCSA Bus Timing 156

- Figure 60 MVIP BUS Timing (2/4 MHz) 157

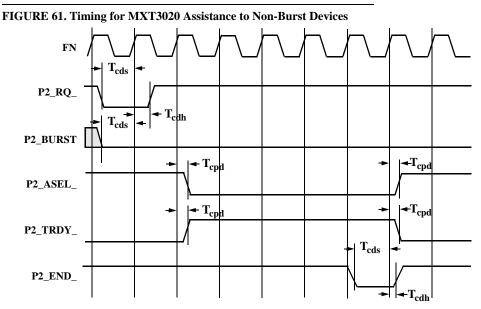

- Figure 61 Timing for MXT3020 Assistance to Non-Burst Devices 158

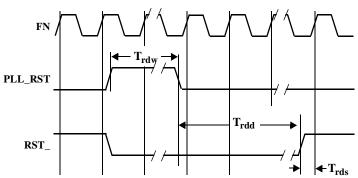

- Figure 62 MXT3020 Reset Timing 159

- Figure 63MXT3020 package/pin diagram162

- Figure 64 Generating a quiet VDD\_PLLVCC 181

- Figure 65MXT3020 decoupling capacitor location182

- Figure 66 MXT3020 package/pin diagram top view 186

- Figure 67 MXT3020 package/pin diagram side view 187

## **List of Tables**

Table 1 Circuit Interface registers (for each link) 11 Table 2 Circuit Interface registers (global) 11 Table 3 Configurations for ACLK and BCLK 16 Table 4 MXT3020 link interface pins and signals 20 Table 5 Buffer size allocation 25 Table 6 Frame Counter / DS0 Counter 26 Table 7 Relation of buffer size to variable y 26 Table 8 Circuit Interface pins, per link 47 Table 9 Circuit Interface pins, common to all links 47 Table 10 Data Mover Unit Instructions 54 Table 11 Data Mover Unit Registers 61 Table 12 Relation of ISEG register to address ranges 64 Table 13 Data Mover Unit and Task Buffer RAM interface pins 71 Table 14 Scatter and Gather Memory Interface Pins 79 Table 15 Port2 Interface pins 86 Table 16 Scatter/Gather Memory control connections 125 Port2 burst DMA instruction bit mapping 129 Table 17 Table 18 Port2 non-burst DMA instruction bit mapping 129 Table 19 Scatter and Gather Task Buffer Busy flag wiring 134 Table 20 Synopsis of MXT3020 and MXT3010 timing requirements 136 Table 21 Simulated interconnect delay 136 Table 22 Input clock timing parameters (in nanoseconds) 140 Table 23 Circuit Interface timing 142 Table 24 Port2 Interface timing 144 Table 25 Scatter/Gather Memory Interface Timing Table 149 Table 26 Status interface timing table 153 Table 27 MXT3020 SCSA Bus Timing (2/4 MHz) 155 Table 28 MXT3020 SCSA Bus Timing (8 MHz) 156 Table 29 MXT3020 MVIP Bus Timing (2/4 MHz) 157 Table 30 MXT3020 Reset Timing 159 Table 31 Port 2 Interface Signal Description 164 Table 32 Scatter/Gather Memory Interface signal description 165 Table 33 Circuit Interface signal description 166 Table 34 Miscellaneous clock, control, and test signal descriptions 167 Table 35 Power and Ground pin descriptions 168 Table 36 Unused pin termination - specific pins 170 Table 37 Unused pin termination - general pins 170 Table 38 Pin Listing 171 Table 39 Pin Type Descriptions 175 Absolute maximum ratings (VSS = 0V) 178 Table 40

- Table 41Recommended operating conditions 178

- Table 42DC Electrical characteristics 179

- Table 43 MXT3020 package summary 187

## Preface

Maker Communications designs, develops, and markets a complete line of programmable, High-Intensity Communications Processors<sup>TM</sup>, software solutions, and development tools. These products are designed to be adapted quickly and effectively to an extensive range of networking applications.

## Maker Products

Maker Communications's product line includes:

- Traffic Stream Processing Solutions

- ATM Cell Processing Solutions

## Traffic Stream Processing Solutions

#### Integrated Circuit

The **MXT4400 Traffic Stream Processor** is Maker Communications's very highperformance communications processing engine. Equally adept at supporting packets and ATM cells, this device resides in the data path of networking systems and provides wire-speed, programmable internetworking and traffic management. It is the first of a product family that supports OC-12 and OC-48 traffic loads. This programmable chip is adapted for a number of different applications using either Maker's firmware packages or customer developed applications.

#### Software Solutions

Executing on the MXT4400, **PortMaker**<sup>TM</sup> employs a modular architecture built on a common kernel to deliver standard inter-domain services. These services include ATM Adaptation Layer 5 (AAL5) Segmentation and Reassembly (SAR) at 622 Mb/ s and support for Packet over SONET.

#### **Development Tools**

Maker Communications offers a full suite of development tools for the MXT4400 Traffic Stream Processor. These include a Verilog model of the chip, the **TSP Assembler**, the MXT4400 simulated test bench (**ESIM**), and the graphical version thereof (**GESIM**). The TSP Assembler assembles, links, and creates a program image that is downloaded to the MXT4400 during device initialization. ESIM is a Verilog-based simulator that provides a tightly controlled and fully observable environment to test and debug both processor applications and external host programs before running them on the target hardware. ESIM is complemented with a graphical post processor, GESIM.

### ATM Cell Processing Solutions

#### **Integrated Circuits**

Maker Communications delivers a wide range of ATM solutions based on the **MXT3010** cell processing engine and the **MXT3020** circuit interface coprocessor. The MXT3010 is a high-performance programmable cell processor engine specifically designed to handle ATM cell manipulation and transmission at data rates up to 622 Mb/s. The MXT3020 is an ATM circuit interface coprocessor for the MXT3010 cell processor. It provides flexible interworking between Time Division Multiplexed (TDM) links and the ATM network.

#### **Software Solutions**

The MXT3010 and MXT3020 are complemented with a series of software applications that provide standard cell processing functionality. **CellMaker®-155** and **Cell-Maker®-622** execute on an MXT3010 and provide ATM Adaptation Layer 5 (AAL5) Segmentation and Reassembly (SAR) at data rates of 155 Mb/s and 622 Mb/ s, respectively. **AccessMaker**<sup>TM</sup> executes on an MXT3010 with up to four attached MXT3020 coprocessors. It provides cell processing functions for both packet and circuit interworking to support multiple services concurrently including AAL1, AAL5, IMA, and cell relay.

#### **Development Tools**

Maker Communications offers a full suite of development tools for the MXT3010 Cell Processor including Verilog models of the chips, the **AS3010** assembler, Cell-Maker Simulator (**CSIM**), and Graphical CellMaker Simulator (**GCSIM**). The AS3010 assembles, links, and creates a program image that is downloaded to the MXT3010 during device initialization. CSIM is a Verilog-based simulator that provides a tightly controlled and fully observable environment to execute and debug both processor applications and external host programs before running them on the target hardware. Maker also provides two development boards. CSIM is complemented with a graphical post processor, GCSIM. The **MXT3016** is a 32-bit, PCI busbased development board used to test 622Mb/s applications. The **MXT3025** is a 32bit, PCI bus-based evaluation board used to test OC-3 ATM (MXT3010) and T1 (MXT3020) applications.

## Using this Manual

This manual is a reference document intended to assist in the design of communications systems. This manual is product specific and should be used in conjunction with other Maker product documentation to develop systems. For a complete listing of Maker documentation refer to the web site at http://www.maker.com/support.

### Additional Document References

The information provided in Maker documentation assumes some reader familiarity with the following documents:

- ATM Forum's UTOPIA Specification, Level 2, Version 1.0, af-phy-0039.000, dated June 1995

- PCI Specification

#### Terminology

The glossary contained in this manual defines Maker terminology as well as networking/ communications terminology applicable to Maker products.

#### **Notes and Cautions**

The manual uses these conventions:

Notes contain information that is incidental to the current subject matter.

Cautions warn of the risk of unfortunate system damage or loss of data.

#### **Typographical Conventions**

This document uses the following typographical conventions:

- API commands appear in mixed case, for example Open\_Channel.

- Simulator commands appear in lower case, for example cdl\_dump.

- Instruction mnemonics and registers appear in uppercase, for example the R\_TSSCFG register.

- User input appears in **bold monospace font**.

- System output and code examples appear in monospace font.

- Variables that accompany commands or configuration switches appear in *<ital-ics and in brackets>*, for example sim *<14000>*

- Text references to locations off of the current page appear in italics. For example, see *Maker Products on page xi*.

- For on-line viewers using ADOBE Acrobat PDF readers, all hypertext links appear in blue.

#### **Change bars**

Change bars are provided to indicate revisions made since the publication of the manual.

## **Contacting Support Services**

Maker Communications has the following forums for getting information, communicating ideas, and reporting problems:

- Sales and customer support: 508-628-0622

- Customer support: support@maker.com

- Product inquiries: info@maker.com

- Facsimile: 508-628-0256

- Web: www.maker.com

## Organization of this manual

This reference manual includes three sections: *Subsystems, Register Reference*, and *Signal Descriptions and Electrical Characteristics*. Also included are Appendix A, *Acronyms*, and Appendix B, *Registered Decoder PAL Source Code*.

The *Subsystems* section is a general tutorial on the organization and features of the MXT3020. Intended for readers unfamiliar with the chip, this section includes information on the:

- Circuit Interface

- Data Mover (Scatter/Gather) Units with List RAMs and Task Buffer RAMs

- Scatter and Gather Memory Interfaces

- Port 2 Interface

Section 2, *Register Reference*, is intended for experienced users of the MXT3020. This section condenses the material provided in the *Subsystems* section into tabular form, and provides the bit assignments and functions for all MXT3020 registers, which are listed in alphabetical order.

Section 3, *Signal Descriptions and Electrical Characteristics*, section includes information on:

- Timing information

- Pin out and pin listing

- Signal descriptions

- Electrical parameters

- Thermal characteristics

- Mechanical information

Preface

## Section 1 Subsystems

This section is composed of five chapters. It provides an overview of the MXT3020 ATM circuit interface coprocessor and its major functional subsystems.

## CHAPTER 1 Device Overview

The MXT3020 is a TDM circuit interface coprocessor for building systems that integrate ATM, packets, and TDM – including voice-over-ATM products. Together with the MXT3010, the MXT3020 delivers the performance and features to support multiple services concurrently, including structured and unstructured AAL1 circuit emulation, ATM User-Network Interface (UNI), Inverse Multiplexing for ATM (IMA), AAL2, and TM4.0 compliant AAL5. With up to four MXT3020s connected to a single MXT3010, systems can be developed that support any combination of up to 32 T1, E1, or J2 links through standard framers, or up to 64 bidirectional links (up to 8 Mb/s each) supporting SCSA and MVIP computer telephony buses.

MXT3020 applications include:

- Circuit emulation service for converting TDM data into AAL1 cells in both Structured Data Transfer (SDT) and Unstructured Data Transfer (UDT) modes.

- ATM User-Network Interface support and inverse multiplexing over TDM circuits including T1, E1, and J2.

Key features of the MXT3020 include:

- A glueless connection to the MXT3010. The MXT3010's SWAN processor programs and controls the MXT3020.

- Support for structured and unstructured data transfer modes on 16 bidirectional TDM wires that directly support SCSA and MVIP telephony busses, or 8 unidirectional TDM wire pairs that connect to T1, E1, or J2 framers.

- Data Mover Units that support fully arbitrary mapping of DS0s to cell payloads including cross link mapping for use in trunking applications. The Data Mover Units contain cell delineation, Header Error Control (HEC) generation and checking, plus cell payload scrambling and descrambling hardware to support T1 and E1 User-Network Interfaces.

- Support for Nx64 mode with up to 2048 DS0's of traffic with up to 1024 virtual circuits.

- Internal clock recovery using Synchronous Residual Time Stamp (SRTS) or Adaptive techniques.

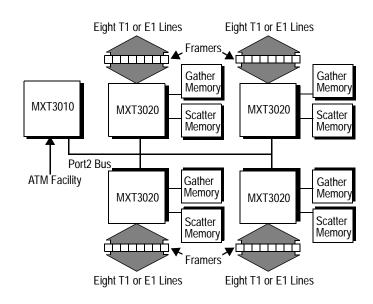

Figure 1 shows a block diagram of a possible application using the MXT3020 as a coprocessor for the MXT3010 to provide an interface between ATM and T1/E1 facilities.

#### FIGURE 1. T1/E1/ATM Interface Using the MXT3010 and MXT3020

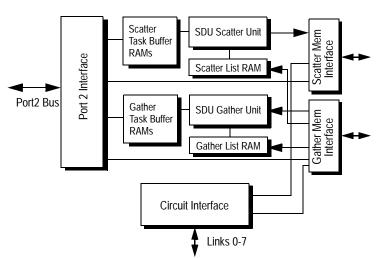

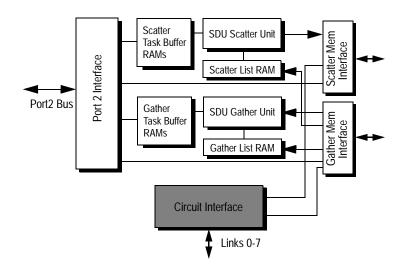

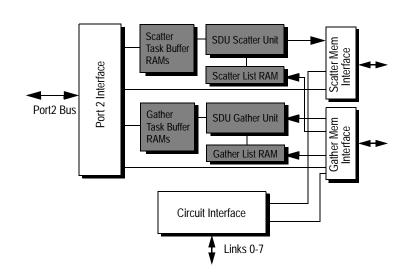

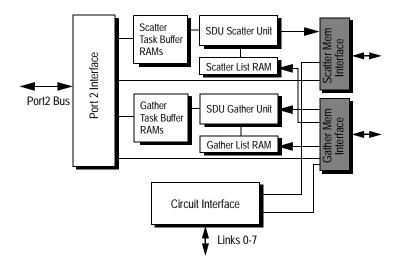

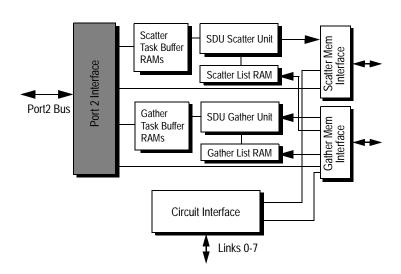

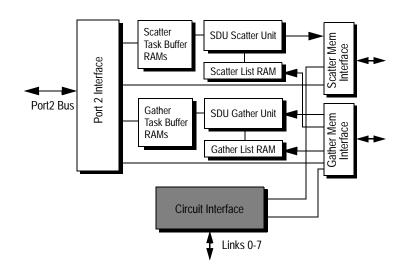

Figure 2 shows a block diagram of the MXT3020.

#### FIGURE 2. Block diagram of the MXT3020

The major sections of the MXT3020 are the:

- Circuit Interface

- Data Mover (Scatter/Gather) Units with List RAMs and Task Buffer RAMs

- Scatter and Gather Memory Interfaces

- Port 2 Interface

## **CIRCUIT INTERFACE**

The Circuit Interface receives and transmits TDM serial data over eight serial link pairs.

- Each link pair supports structured and unstructured data transfer (SDT and UDT) modes, and is independent with its own clocks and unidirectional mode frame synchronization.

- Each link pair can be configured in a unidirectional mode suitable for use with framers or in a bidirectional mode compatible with telephony busses. When configured in unidirectional mode, each link pair implements one receive line and one transmit line. When configured in bidirectional mode, each link of the pair implements an independent bidirectional line.

- For each link, a tri-state control map is provided. The MXT3020 steps through the tri-state control map as each DS0 occurs, enabling or disabling the tri-state output enable on the link as directed by the control bits in the map.

- Received TDM frames are written into buffers in Gather Memory. Transmit TDM frames are read from buffers in Scatter memory.

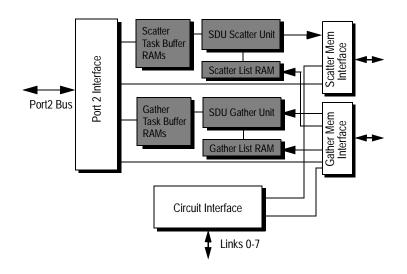

## THE DATA MOVER (SCATTER/GATHER) UNITS

The Data Mover Units (DMUs) are specialized scatter/gather machines. One DMU disassembles SAR Service Data Units (SDUs) from ATM cells and prepares data for transmission over TDM links. Simultaneously, the other DMU receives data from TDM links and assembles it into ATM SAR SDUs. The Data Mover Units are programmed by the MXT3010, which loads lists of instructions for controlling the data transfer process into a designated area of Gather Memory. The MXT3010 then loads control information and data into the Task Buffer RAM of the scatter machine or control information into the Task Buffer RAM of the gather machine.

The Scatter and Gather Memory interfaces are each 16-bits wide and support up to 512 Kbytes of pipelined synchronous SRAM. Each port can accept accesses from any of the on-chip masters (Circuit Interface, Data Mover Units, or Port2 Interface). Because the Scatter and Gather Memory ports are independent, operations to these ports can occur simultaneously.

## PORT2 INTERFACE

The Port2 Interface is the MXT3020's connection to the MXT3010 device. Through the Port2 Interface, the MXT3010 can read and write Scatter and Gather memory, the Task Buffer RAMs, List RAMs, and all internal registers. See "MXT3020 address space" on page 83. Once a Port2 transfer begins, the MXT3020's Port2 Interface demultiplexes the Port2 bus and decodes the address. If the address maps to this chip, the MXT3020 performs the read or write operation to the register or RAM selected by the address. The MXT3020 address space is accessible only in burst transfer mode.

An MXT3020 occupies 1 Mbyte of Port2 address space. Two MXT3020s can reside on a Port2 bus without the need for additional device selection logic. The P2A20 pin of one MXT3020 is strapped low to decode Port2 bus address space 0x000000 to 0x0FFFFF while the P2A20 pin of the other MXT3020 is strapped high to decode Port2 address space 0x100000 to 0x1FFFFF. Alternatively, multiple MXT3020's can be supported with the addition of a device selection PAL. See "Multiple MXT3020 implementation" on page 130.

## CHAPTER 2 Circuit Interface

The Circuit Interface logic receives and transmits TDM serial data. The Circuit Interface supports eight serial link pairs.

- Each link pair supports structured and unstructured data transfer (SDT and UDT) modes.

- Each link pair is completely independent with its own clocks and unidirectional mode frame synchronization.

- TDM serial data rates supported are 1.544, 2.048, 4.096, 6.144, or 8.192 Mhz.

- Each link pair can be configured in a unidirectional or a bidirectional mode. In unidirectional mode, each link pair is configured as one 2-wire port with a dedicated receive and transmit line, and can connect to T1, E1, and J2 framers. In bidirectional mode, each link pair is configured as two single-wire bidirectional links, and can directly support SCSA and MVIP telephony busses.

- A tri-state control map for each link can be stored in a section of the Gather Memory reserved for control purposes. The size of the tri-state control map for a link is determined by the number of DS0s occurring in each frame, as a tri-state control bit is provided for each DS0 on the link. Synchronized by Frame Sync on the link, the MXT3020 steps through the tri-state control map as each DS0 occurs, enabling or disabling the tri-state output enable on the link as directed by the tri-state control bits in the map. In bidirectional mode, each wire is individually tri-statable on a DS0 by DS0 basis. In unidirectional mode, each transmit wire is individually tri-statable on a DS0 by DS0 basis.

- Serial data received by the links is packed into halfwords and written to buffers in Gather Memory. Data to be transmitted is read from Scatter Memory and shifted out onto the transmit links. The Circuit Interface maintains all necessary pointers to Scatter/Gather Memory to support constant-bit-rate data with minimal intervention from the SWAN processor in the MXT3010.

## **CIRCUIT INTERFACE REGISTERS**

## Per-Link registers

Each of the eight link pairs has a configuration register, three address counters, and five link service clock and Synchronous Residual Time Stamp (SRTS) control registers:

| Register                                                                                                                | Function                                                  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--|--|--|--|

| Link Configuration register                                                                                             | See "Link Configuration register" on page 12.             |  |  |  |  |

| Link Tx Buffer Address counter                                                                                          | See "Link Duffer Address counters" on more 22             |  |  |  |  |

| Link Rx Buffer Address counter                                                                                          | See "Link Buffer Address counters" on page 23.            |  |  |  |  |

| Link Tri-state Control Address counter                                                                                  | See "Link Tri-state Control Address counter" on page 27.  |  |  |  |  |

| Link service clock control registers:<br>N register, K register,<br>L counter, FTC counter,<br>Link SRTS Value register | See "Link service clock generation registers" on page 33. |  |  |  |  |

### **Global registers**

In addition to the eight registers provided for each link, the Circuit Interface has six global configuration/status registers:

TABLE 2.

Circuit Interface registers (global)

| Register                                      | Function                                                     |  |  |  |  |

|-----------------------------------------------|--------------------------------------------------------------|--|--|--|--|

| CI Tri-state Control Base Address<br>register | See "CI Tri-state Control Base Address register" on page 37. |  |  |  |  |

| CI Configuration register                     | See "CI Configuration register" on page 37.                  |  |  |  |  |

| CI Quiet Frame Base Address reg-<br>ister     | See "CI Quiet Frame Base Address register" on page 42.       |  |  |  |  |

| CI SRTS FTC register                          | See "CI SRTS FTC register" on page 45.                       |  |  |  |  |

| CI SRTS Valid Status register                 | See "CI SRTS Valid Status register" on page 45.              |  |  |  |  |

| CI Status register                            | See "CI Status register" on page 46.                         |  |  |  |  |

## LINK CONFIGURATION REGISTER

The Link Configuration register controls the operating mode of each link. There is one of these read/write registers for each link. The bit map is shown in Figure 3 and the bit functions are described in the paragraphs which follow.

#### FIGURE 3 Link Configuration register bit assignments

| 15 | 14 | 13     | 12  | 11  | 10      | 9 | 8     | 7 | 6  | 5   | 4    | 3    | 2       | 1       | 0      |

|----|----|--------|-----|-----|---------|---|-------|---|----|-----|------|------|---------|---------|--------|

| 0  | 0  | D_FCNT | TxC | LKS | ACLK_MD |   | ACTDS | ) | BI | DTM | D_Dł | ELAY | LSB_1ST | SRTS_MD | LkRSET |

#### D\_FCNT (bit 13)

The Link Buffer Address counters (page 23) are 15 bits long and consist of a DS0 portion and a frame count portion. The number of bits used in the DS0 portion depends upon the number of DS0's in the frame (MAXDS0 in the "CI Configuration register" on page 37). The bits not used for the DS0 portion are the frame count portion. The D\_FCNT bit enables/disables incrementing the frame count portion. Setting this bit to one (1) disables incrementing the frame count portion, causing programs used in special applications to repeatedly use a single portion of frame buffer storage. Clearing this bit to zero (0) enables incrementing the frame count portion. This latter choice is used by most programs.

#### TxCLKS (bits 12 and 11)

These bits select the link transmitter clock source (SRTS, BCLK, ACLK). See "Added detail: Bits 12-10 – clock source control" on page 15..

| Bit 12 | Bit 11 | Clock Source        |

|--------|--------|---------------------|

| 0      | 0      | Internal SRTS Clock |

| 0      | 1      | External BCLK input |

| 1      | 0      | External ACLK input |

| 1      | 1      | Reserved            |

#### ACLK\_MD (bit 10)

This bit selects the ACLK pin I/O direction. When this bit is one (1), the ACLK pin is an output. When this bit is zero (0), the ACLK pin is an input. See "Added detail: Bits 12-10 – clock source control" on page 15.

#### ACTDS0 (bits 9, 8, and 7)

These bits indicate the actual number of DS0's per frame. This information is used by the tri-state enable control map (see "The tri-state enable control map" on page 28).

| Bit 9 | Bit 8   | Bit 7 | Actual number of DS0's per frame |

|-------|---------|-------|----------------------------------|

| 0     | 0       | 0     | 24                               |

| 0     | 0       | 1     | 32                               |

| 0     | 1       | 0     | 64                               |

| 0     | 1       | 1     | 96                               |

| 1     | 0       | 0     | 128                              |

| 101   | through | 111   | Reserved                         |

#### BI (bit 6)

This bit controls the mode of a link pair. When this bit is one (1), the link operates in bidirectional mode. When this bit is zero (0), the link operates in unidirectional mode. These modes are described in greater detail in "Added detail: Bit 6 - link pair mode" on page 19.

#### DTM (bit 5)

This bit selects the Data Transfer Mode of the link pair. When this bit is one (1), the link operates in Structured Data Transfer (SDT) mode. When this bit is zero (0), the link operates in Unstructured Data Transfer (UDT) mode.

#### D\_DELAY (bits 4 and 3)

| Bit 4 | Bit 3 | Frame Sync to first data delay |

|-------|-------|--------------------------------|

| 0     | 0     | 1 cycle                        |

| 0     | 1     | 2 cycles                       |

| 1     | 0     | 3 cycles                       |

| 1     | 1     | Reserved                       |

These bits control the position of Frame Sync relative to the first bit of a frame.

#### LSB\_1ST (bit 2)

This bit controls the direction of the link shift registers. When this bit is one (1), the link shift registers operate in LSB mode, shifting the least significant bit of each byte onto the serial line first. When this bit is zero (0), the link shift registers operate in MSB mode, shifting the most significant bit of each byte onto the serial line first.

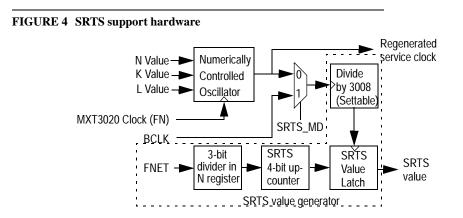

#### SRTS\_MD (bit 1)

This bit controls the mode of the SRTS value generator. Figure 4 shows a simplified diagram of the SRTS support hardware.

When this bit is one (1), the SRTS value generator operates in master mode. In this mode, the value generator uses the externally supplied TDM service clock (BCLK pin) to generate SRTS values for transmission over the ATM link with the data.

When the SRTS\_MD bit is zero (0), the SRTS value generator operates in slave mode. In slave mode, the SRTS value generator measures the service clock generated by the numerically controlled oscillator within the MXT3020. When SRTS is used for clock recovery, the SRTS values thus generated are used by software to adjust the values of N and K and lock the regenerated TDM service clock to the remote TDM service clock.

### LkRESET (bit 0)

This bit controls the reset state of a link pair. Setting this bit to one (1) places the link in the reset state. Clearing this bit to zero (0) removes the link from the reset state.

### Added detail: Bits 12-10 – clock source control

### ACLK pin

In addition to the ASER and BSER pins, an ACLK pin is provided. The state of bit 10 (ACLK\_MD) in the Link Configuration register determines whether this pin is used as an input or as an output:

- If ACLK\_MD is clear (0), the ACLK pin functions as an input and functions as the Transmit Input Clock in both the bidirectional (bus) and unidirectional (framer) modes.

- If ACLK\_MD is set (1), the ACLK pin functions as an output and functions as the Transmit Link (Output) Clock in the unidirectional (framer) mode. In bidirectional (bus) mode, the tri-state control that is being used to control the ASER line is presented on the ACLK pin and can be used to control external output-enabled devices.

### BCLK pin

The BCLK pin provides the Receive Clock signals for both ASER and BSER in both the unidirectional and bidirectional modes.

Table 3 shows four configurations using ACLK and BCLK to provide clocking in unidirectional mode. Table 3 also shows three configurations using ACLK and BCLK to provide clocking in bidirectional mode. The figures cited in the table provide additional information about the clocking configurations.

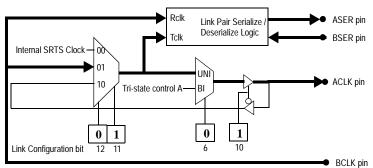

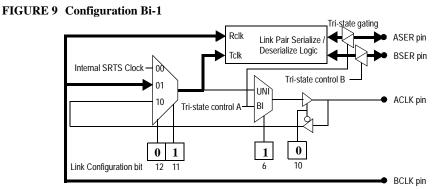

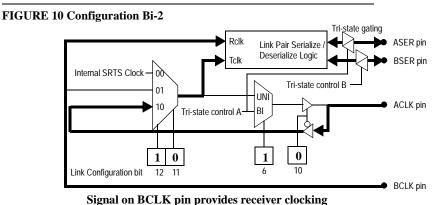

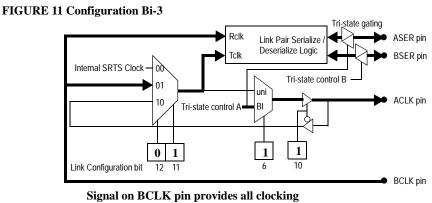

| Bits<br>12,11,10,6 | Description                                                                                                                                                                                                                                                                                             | Figure                                             |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

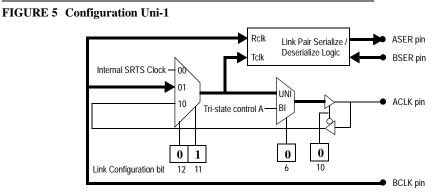

| 0100               | (Unidirectional mode) An external clock on the BCLK pin pro-<br>vides the clocking for both the link logic transmitter and receiver.<br>The ACLK pin is unused.                                                                                                                                         | Figure 5,<br>"Configuration Uni-<br>1," on page 17 |

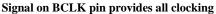

| 1000               | (Unidirectional mode) An external clock on the ACLK pin pro-<br>vides clocking for the link logic transmitter. An external clock on<br>the BCLK pin provides clocking for the link logic receiver.                                                                                                      | Figure 6,<br>"Configuration Uni-<br>2," on page 17 |

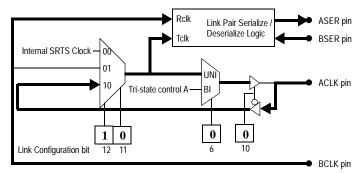

| 0010               | (Unidirectional mode) The internal SRTS clock provides clock-<br>ing for the link logic transmitter and outputs this clock on the<br>ACLK pin. An external clock on the BCLK pin provides clock-<br>ing for the link logic receiver.                                                                    | Figure 7,<br>"Configuration Uni-<br>3," on page 18 |

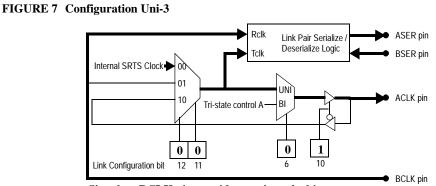

| 0110               | (Unidirectional mode) An external clock on the BCLK pin pro-<br>vides the clocking for both the link logic transmitter and receiver<br>and provides the same clock signal as an output on the ACLK<br>pin.                                                                                              | Figure 8,<br>"Configuration Uni-<br>4," on page 18 |

| 0101               | (Bidirectional mode) An external clock on the BCLK pin pro-<br>vides the clocking for both the link logic transmitter and receiver.<br>The ACLK pin is unused.                                                                                                                                          | Figure 9,<br>"Configuration Bi-<br>1," on page 18  |

| 1001               | (Bidirectional mode) An external clock on the ACLK pin pro-<br>vides clocking for the link logic transmitter. An external clock on<br>the BCLK pin provides clocking for the link logic receiver.                                                                                                       | Figure 10,<br>"Configuration Bi-<br>2," on page 19 |

| 0111               | (Bidirectional mode) An external clock on the BCLK pin pro-<br>vides the clocking for both the link logic transmitter and receiver.<br>The tri-state control that is being used to control the ASER line is<br>presented on the ACLK pin and can be used to control external<br>output-enabled devices. | Figure 11,<br>"Configuration Bi-<br>3," on page 19 |

| TABLE 3.         Configurations for ACLK and BCLK | TABLE 3. | Configurations | for | ACLK | and BCLK |

|---------------------------------------------------|----------|----------------|-----|------|----------|

|---------------------------------------------------|----------|----------------|-----|------|----------|

Note:While sixteen configurations are theoretically possible (four bits are used), only the seven shown in the figures are functional. Other configurations are non-functional and must not be used.

FIGURE 6 Configuration Uni-2

Signal on BCLK pin provides receiver clocking Signal on ACLK pin provides transmitter clocking

Signal on BCLK pin provides receiver clocking Internal SRTS provides transmit clocking and output on ACLK

Signal on BCLK pin provides all clocking and output on ACLK

Signal on BCLK pin provides all clocking

Signal on ACLK pin provides transmitter clocking

Tri-state control for external gating is provided on ACLK pin

# Added detail: Bit 6 - link pair mode

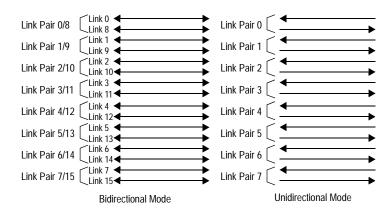

The MXT3020 circuit interface can be operated in either bidirectional or unidirectional mode. The BI bit (bit [6]) in the Link Configuration register selects the mode of operation. Bidirectional mode is typically used with telephony busses, and unidirectional mode is typically used with TDM framers. Figure 12 shows the two modes.

FIGURE 12 MXT3020 operating modes - eight link pairs

As indicated in the figure, the MXT3020 treats the TDM links as eight link pairs, regardless of operating mode. Thus, the two operating modes can be compared by analyzing a single link pair.

#### Pins associated with a link pair

There are five pins associated with each link pair. Depending upon the configuration of the link, these pins may be connected to a variety of different signals within the MXT3020. Table 4 summarizes the connection possibilities, and the paragraphs which follow discuss each pin and its configuration alternatives in greater detail.

| Pin      | Signals carried in unidirectional mode | Signals carried in bidirectional mode |

|----------|----------------------------------------|---------------------------------------|

| ASER     | TxData ("A Serial") for link <i>n</i>  | Tx/RxData for link <i>n</i>           |

| BSER     | RxData ("B Serial") for link <i>n</i>  | Tx/RxData for link $n + 8$            |

| ACLK     |                                        |                                       |

| (output) | Tx Link Clk for ASER                   | Copy of tri-state enable for ASER     |

| (input)  | Tx Input Clk for ASER/BSER             | Tx Input Clk for ASER/BSER            |

| BCLK     | RxCLK for ASER/BSER                    | RxCLK for ASER/BSER                   |

| BSCE     | Frame Sync                             | Copy of tri-state enable for BSER     |

TABLE 4.MXT3020 link interface pins and signals

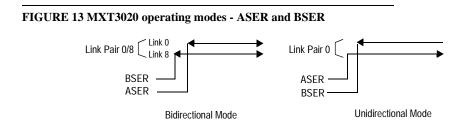

#### **ASER and BSER pins**

Figure 13 shows the ASER (A serial) and BSER (B serial) pins. As indicated in Table 4, in the unidirectional mode, ASER and BSER are TxData and RxData respectively. In bidirectional mode, ASER and BSER carry Tx/RxData. Since ASER and BSER are bidirectional busses in that mode, the transmit functions of ASER and BSER need to be disabled when received data is arriving. Enabling and disabling of the transmit function are accomplished by tri-state enable circuitry described in "Link Tri-state Control Address counter" on page 27.

# Added detail: BSCE pin

As indicated in Table 4 on page 20, the BSCE pin can be used either as a Frame Sync pin, or as a copy of the tri-state enable for the BSER pin. Usage of the BSCE pin depends upon the MXT3020 operating mode and is explained below.

### BSCE usage in unidirectional mode

When the MXT3020 is used in unidirectional mode, it is typically connected to TDM framers that provide Frame Sync signals. Two methods of wiring the Frame Sync signal are available:

• If a single Frame Sync signal is used, it can be connected to the FSYNC pin (pin 160) of the MXT3020. In addition, the FS\_MODE bit (bit [0] of the CI Configuration register) should be cleared to zero (0) to indicate that a Frame Sync signal common to all links is being supplied on the FSYNC pin.

• If the application calls for different link pairs to use different Frame Sync signals, Frame Sync signals can be wired to the BSCE pins of individual link pairs. In addition, the FS\_MODE bit (bit [0] of the CI Configuration register) should be set to one (1) to indicate that Frame Sync signals for each link pair are being provided on their respective BSCE pins.

In addition to the actions listed above, bits [4:3] of the Link Configuration register and bit [10] of the CI Configuration register are used to control the use of Frame Sync in various applications.

#### BSCE usage in bidirectional mode

Bidirectional mode is used with telephony busses, where per-link Frame Sync signals are not required. Therefore, the BSCE pin is not used for Frame Sync in bidirectional mode. In bidirectional mode, the tri-state control that is being used to control the BSER line is presented on the BSCE pin and can be used to control external output-enabled devices.

# LINK BUFFER ADDRESS COUNTERS

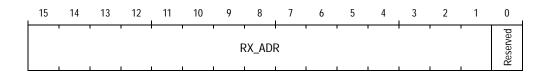

# Link Rx Buffer Address counter

This register indicates where the next data received on this TDM link pair will be stored in the Gather Memory. The contents of this counter combined with the link number provide an 18-bit pointer to a halfword-aligned circular queue in Gather Memory where received data can be written by the Circuit Interface logic. Every link pair has a separate queue for received data, thus each link pair has one of these read/ write registers. The counters are initialized by the SWAN processor in the MXT3010 and are incremented automatically by the link hardware during data transfers.

|    |                                                                                                    |    |    | Restr | riction | on Lir | ık Rx    | Buffer  | Addre | ess cou | nter |     |   |   |   |

|----|----------------------------------------------------------------------------------------------------|----|----|-------|---------|--------|----------|---------|-------|---------|------|-----|---|---|---|

|    | Values in this register can only be modified when the link is in the reset state. This restriction |    |    |       |         |        |          |         |       |         |      |     |   |   |   |

| do | does not affect the automatic incrementing that the MXT3020 performs during data transfers.        |    |    |       |         |        |          |         |       |         |      |     |   |   |   |

| 15 | 14                                                                                                 | 13 | 12 | 11    | 10      | 9      | 8        | 7       | 6     | 5       | 4    | 2   | 2 | 1 | ( |

| 15 |                                                                                                    | 15 | 12 |       |         | ,      | 5        | ,<br>   | 5     | 5       | 4    | - J | 2 |   |   |

|    |                                                                                                    |    |    |       | Rx      | (Gathe | r) Addre | ss coun | ter   |         |      |     |   |   | ( |

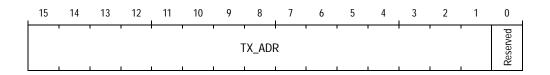

# Link Tx Buffer Address counter

This register indicates the location in Scatter Memory from which the next data to be transmitted on the TDM link will be taken. The contents of this counter combined with the link number provide an 18-bit pointer to a halfword-aligned circular queue in Scatter Memory where transmit link data can be read by the Circuit Interface logic. There is a separate transmit data queue for every link pair; thus, there is one of these read/write registers for each link pair. The counters are initialized by the SWAN processor in the MXT3010 and are incremented automatically by the link hardware during data transfers.

#### Restrictions on Link Tx Buffer Address counter

Values written to this register must be 4 higher than those written to the Link Rx Buffer Address counter. Values in this register can only be modified when the link is in the reset state. These restrictions do not affect the automatic incrementing that the MXT3020 performs during data transfers.

| L | 15 | 14 | 13 | 12 | 11 | 10 | 9       | 8        | 7       | 6    | 5 | 4 | 3 | 2 | 1 | 0 |

|---|----|----|----|----|----|----|---------|----------|---------|------|---|---|---|---|---|---|

|   |    |    | I  | 1  |    | Тх | (Scatte | r) Addre | ss coun | ter] | 1 | I | 1 | 1 | 1 | 0 |

# Details of the Link Tx/Rx Buffer Address counters

Each address counter is composed of a frame counter (FC) and a DS0 counter. The DS0 counter wraps based upon the settings of the ACTDS0 field in the "Link Configuration register" on page 12. The frame counter wraps based on the MAXDS0 and MAXTBS/MAXRBS fields in the "CI Configuration register" on page 37.

The MAXDS0 and MAXTBS/MAXRBS settings determine the buffer size allocated to each link. This is shown in Table 5.

| MAXDS0    | MAXTBS/MAXRBS | Buffer size (Wrap boundary) |

|-----------|---------------|-----------------------------|

| 24 or 32  | 64 frames     | 2K                          |

| 64        | 64 frames     | 4K                          |

| 96 or 128 | 64 frames     | 8K                          |

| 24 or 32  | 128 frames    | 4K                          |

| 64        | 128 frames    | 8K                          |

| 96 or 128 | 128 frames    | 16K                         |

| 24 or 32  | 256 frames    | 8K                          |

| 64        | 256 frames    | 16K                         |

| 96 or 128 | 256 frames    | 32K                         |

| 24 or 32  | 512 frames    | 16K                         |

| 64        | 512 frames    | 32K                         |

| 96 or 128 | 512 frames    | 64K <sup>a</sup>            |

TABLE 5.Buffer size allocation

a. The 64K buffer size is not supported in bidirectional mode.

The positions of the frame counter and DS0 counter portions of the Link TX/RX Buffer Address counters are shown in Table 6.

|           | Unidirectional | mode        | Bidirectional mode |             |  |  |  |  |

|-----------|----------------|-------------|--------------------|-------------|--|--|--|--|

| MAXDS0    | Frame counter  | DS0 counter | Frame counter      | DS0 counter |  |  |  |  |

| 24 or 32  | [ <i>y</i> :5] | [4:0]       | [y:6]              | [5:1]       |  |  |  |  |

| 64        | [y:6]          | [5:0]       | [y:7]              | [6:1]       |  |  |  |  |

| 96 or 128 | [ <i>y</i> :7] | [6:0]       | [ <i>y</i> :8]     | [7:1]       |  |  |  |  |

TABLE 6.

Frame Counter / DS0 Counter

In Table 6, variable *y* represents the highest order bit used by the frame counter. The value of *y* depends upon the buffer size, as shown in Table 7.

| Buffer size | Unidirectional mode, y= | Bidirectional mode, y= |

|-------------|-------------------------|------------------------|

| 2K          | 10                      | 11                     |

| 4K          | 11                      | 12                     |

| 8K          | 12                      | 13                     |

| 16K         | 13                      | 14                     |

| 32K         | 14                      | 15                     |

| 64K         | 15                      | Not supported          |

TABLE 7.

Relation of buffer size to variable y

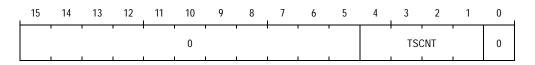

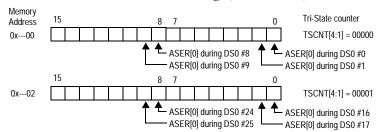

# LINK TRI-STATE CONTROL ADDRESS COUNTER

The contents of the Tri-state Control (TSC) Address counter are combined with the Tri-state Control Base Address register and the Link ID number (LID) to create an 18-bit pointer to a halfword-aligned entry in Gather Memory containing the tri-state control map for the link. The format of the Tri-state Control Address counter is shown below. The format of the complete pointer is shown in "Creation of the tri-state control map pointer" on page 28.

# An example of the tri-state control process

The MXT3020 provides tri-state control of ASER [7:0] and BSER [7:0] when operating in bidirectional mode. The MXT3020 also provides tri-state control of ASER [7:0] when operating in unidirectional mode. Tri-state control is provided by tri-state control maps located in Gather Memory.

Figure 14 shows, in simplified form, the fundamentals of tri-state control. To simplify the figure, only the tri-state control of ASER [0], operating in bidirectional mode, is shown.

#### FIGURE 14 Tri-state enable for the ASER pins

MXT3020 serial data being transmitted on the ASER pin of link pair 0 Data byte Data byte Data byte DS0 #0 DS0 #23 DS0 #1 Data byte for DS0 #0 MXT3020 tri-state map for link pair 0 Enabling 0 1 0 0 Gate Data traversing the bus line connected to ASER [0] pin Time slot Time slot Time slot ASER [0] DS0 #0 DS0 #23 DS0 #1 Time slot for DS0 #0

In the example shown, data is being generated in T1 format. That is, a byte of data is presented for a 64 Kbps channel (DS0); then a byte of data is presented for the next DS0. When data has been presented for 24 DS0's, a new frame begins and a new byte of data for the first DS0 is presented. The data being presented is only enabled onto the ASER[0] pin if the bit in the tri-state map for this link indicates that enabling during the time period of this DS0 is permitted. Specifically, a zero (0) in the tri-state map indicates that the data should be enabled onto the ASER [0] pin. Thus, in the example, data is being applied to DS0 #0 and DS0 #1, but not to DS0 #23.

If one thinks of the registers shown in Figure 14 as shift registers, it is important to note that the tri-state map "shifts" at one-eighth the rate of the data registers, as a bit in the tri-state map controls the enabling or disabling of an entire byte of data. For each byte time (at a DS0 rate) on each link, the MXT3020 provides two tri-state enable bits, one for ASER and one for BSER.

### The tri-state enable control map

#### Creation of the tri-state control map pointer

The contents of the Tri-state Control Address counter (page 27) are combined with the Tri-state Control Base Address register (page 37) and the Link ID number (LID) to create an 18-bit pointer to a halfword-aligned entry in Gather Memory containing the tri-state control map for the link. The pointer has the following format:

| 1        | 8 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8   | 7 | 6 | 5   | 4   | 3 | 2 | 1 |

|----------|---|----|----|----|----|----|----|----|----|---|-----|---|---|-----|-----|---|---|---|

| TSC_BASE |   |    |    |    |    |    |    |    |    |   | LID |   |   | TSC | CNT |   |   |   |

|          | 1 |    | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1 | 1   |   |   |     |     |   | 1 |   |

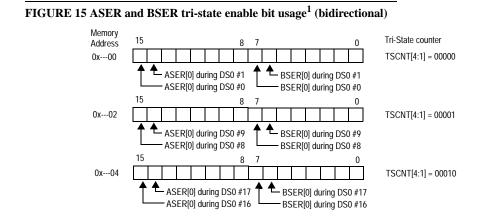

#### **Bidirectional mode**

The tri-state control map pointer identifies eight buffers (LID [7:5]) in memory, one buffer for each link pair. Each buffer consists of 16 halfwords (TSCNT [4:1]) or 256 bits. For each link pair, during each DS0 data byte, the MXT3020 reads two of these tri-state enable bits, one for ASER and one for BSER. Figure 15 shows the sequence in which these enable bits are used.

Figure 15 shows a tri-state map that would be sufficient for 24 DS0's on one link pair. By changing the value of LID and using the same three values for TSCNT, similar maps could be loaded into memory to control 24 DS0's on each of the eight link pairs served by the MXT3020.

The tri-state control map shown in Figure 15 serves 24 DS0's and uses 48 bits. The MXT3020 can accommodate tri-state control maps with as many as 128 DS0's (256 bits) for each link pair.

<sup>1.</sup> In all MXT3020 figures, memory addressing is Big Endian.

If the actual number of DS0s is less than 128, there is no requirement that the tri-state control map be filled with 256 bits, as the Tri-state Control Address counter wraps based upon the actual number of DS0s indicated in the ACTDS0 bits in the Link Configuration register. The wrap boundaries for the Tri-state Address counter are indicated in the following table:

| Mode          | ACTDS0 | Wrap Boundary |

|---------------|--------|---------------|

| Bidirectional | 24     | 6 bytes       |

| Bidirectional | 32     | 8 bytes       |

| Bidirectional | 64     | 16 bytes      |

| Bidirectional | 96     | 24 bytes      |

| Bidirectional | 128    | 32 bytes      |

#### Unidirectional mode

The contents of the Tri-state Control Address counter (page 27) are combined with the Tri-state Control Base Address register (page 37) and the Link ID number (LID) to create an 18-bit pointer to a halfword-aligned entry in Gather Memory containing the tri-state control map for the link.

The tri-state control map pointer (page 28) identifies eight buffers (LID [7:5]) in memory, one buffer for each link pair. Each buffer consists of eight halfwords (TSCNT [3:1])<sup>1</sup> or 128 bits. For each link pair, during each DS0 data byte, the MXT3020 reads one of these tri-state enable bits to control the enabling of data onto the ASER pin. Figure 16 shows the sequence in which these enable bits are used.

<sup>1.</sup> TSCNT[4] is not used in unidirectional mode.

#### FIGURE 16 ASER and BSER tri-state enable bit usage (unidirectional)

Figure 16 shows a tri-state map that would be sufficient for 32 DS0's (E1) on one link pair. By changing the value of LID and using the same two values for TSCNT, similar maps could be loaded into memory to control 32 DS0's on each of the eight link pairs served by the MXT3020.

The tri-state control map shown in Figure 16 serves 32 DS0's and uses 32 bits. The MXT3020 can accommodate tri-state control maps with as many as 128 DS0's (128 bits) for each link pair.

If the actual number of DS0s is less than 128, there is no requirement that the tri-state control map be filled with 128 bits, as the Tri-state Control Address counter wraps based upon the actual number of DS0s. The actual number of DS0s is determined by the ACTDS0 bits in the Link Configuration register, and the wrap boundaries for the Tri-state Address counter are indicated in the following table:

| Mode           | ACTDS0 | Wrap Boundary |

|----------------|--------|---------------|

| Unidirectional | 24     | 4 bytes       |

| Unidirectional | 32     | 4 bytes       |

| Unidirectional | 64     | 8 bytes       |

| Unidirectional | 96     | 12 bytes      |

| Unidirectional | 128    | 16 bytes      |

# Summary of tri-state control operation

The MXT3020 provides tri-state control of ASER [7:0] and BSER [7:0] when operating in bidirectional mode. The MXT3020 also provides tri-state control of ASER when operating in unidirectional mode. To set up a tri-state map, software selects a TSC Base Address, and for each link pair (LID) provides up to 16 (bidirectional mode) or 8 (Unidirectional mode) halfwords specifying the tri-state enable map.

During operation, the MXT3020 services each link pair sequentially. For each link, the MXT3020 maintains a Tri-state Control Address counter (TSCNT) based on the receipt of Frame Sync by the link. Thus, for each link (LID), the MXT3020 has an indication (TSCNT) of which DS0 is being handled by that link. The MXT3020 uses this information (LID and TSCNT), in conjunction with the TSC Base Address, to obtain the tri-state control map appropriate to the DS0 being serviced by that link at that time. In bidirectional mode, two tri-state enable bits from the map are used to control the gating of bytes of DS0 data onto the ASER and BSER pins respectively (see Figure 14 and Figure 15). In unidirectional mode, a tri-state enable bit from the map is used to control the gating of a byte of DS0 data onto the ASER pin (see Figure 14 and Figure 16).

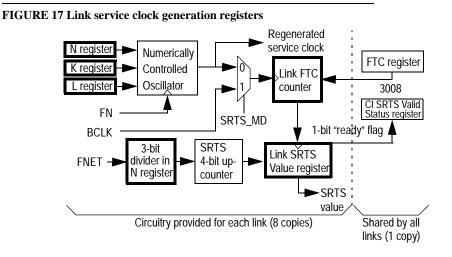

# LINK SERVICE CLOCK GENERATION REGISTERS

For each link, there are five registers used for link service clock generation:

- Link Service Clock N register

- Link Service Clock K register

- Link Service Clock L register

- Link FTC counter

- Link SRTS Value register

Figure 17 shows the relationship of these registers and counters to the link service clock circuitry.

Three of the registers (N, K, L) control a numerically controlled oscillator which has an integer portion N and a fractional portion, K/L. The equation for the output clock is shown below:

Link Service Clock period =

$$\left(N + \frac{K}{L}\right) \times$$

System clock period

# Link Service Clock N register

The LSC\_N value in the Link Service Clock N register represents the integer multiple of system clock periods used to generate the link service clock. This is the coarse setting of the numerically controlled oscillator used to generate the service clock. Setting bit 7 of this register to one (1) enables the SRTS counters. There is one of these registers for each link.

| 15 | 14     | 13 | 12 | 11         | 10       | 9 | 8 | 7      | 6 | 5 | 4 | 3     | 2 | 1 | 0 |

|----|--------|----|----|------------|----------|---|---|--------|---|---|---|-------|---|---|---|

| FI | NET_DI | V  |    | ,<br> <br> | Reserved | ł | 1 | EN_CNT |   |   |   | LSC_N | 1 | 1 |   |

Bits 15-13 of this register provide a programmable divider for the network clock (FNET) (see Figure 17 on page 33). The table below shows the division provided for various settings of bits 15-13. In addition, the table shows the settings that should be used to support common TDM service clock frequencies when an FNET clock of 19.44 MHz is used.

| Bits 15-13 | Divide by | Divider output frequencies for<br>FNET = 19.44 MHz | TDM service clock frequencies<br>for FNET= 19.44 MHz |

|------------|-----------|----------------------------------------------------|------------------------------------------------------|

| 0          | 1         | 19.44 MHz                                          |                                                      |

| 1          | 2         | 9.72 MHz                                           | 8.192 MHz                                            |

| 2          | 3         | 6.48 MHz                                           |                                                      |

| 3          | 4         | 4.86 MHz                                           | 4.096 MHz                                            |

| 4          | 5         | 3.888 MHz                                          |                                                      |

| 5          | 6         | 3.24 MHz                                           |                                                      |

| 6          | 7         | 2.777 MHz                                          |                                                      |

| 7          | 8         | 2.43 MHz                                           | 2.048 MHz and 1.544 MHz                              |

#### Restriction on FNET\_DIV bits

Bits [15:8] of this register are write only and read back as all zeroes. All bits in this register are cleared to zeroes by Reset. Thus, the FNET\_DIV bits are write-only and are cleared to zeroes by Reset.

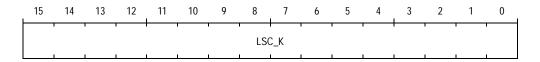

# Link Service Clock K register

The value in the Link Service Clock K register represents the fraction control numerator used to generate the link service clock. This is the fine setting of the numerically controlled oscillator used to generate the service clock. There is one of these read/ write registers for each link.

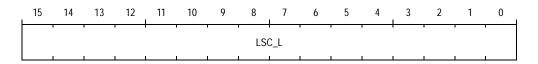

# Link Service Clock L counter

The value in the Link Service Clock L counter represents the fraction control denominator used to generate the link service clock. This is a free running counter that can be read and written for diagnostic purposes and can be seeded with an initial value. However, the value loaded into this counter does not alter the effective denominator value, which is always 65,536 ( $2^{16}$ ). This counter advances once for each service clock cycle generated. There is one of these counters for each link.

### Link FTC counter

The SRTS value generator for each link creates an SRTS value by using an FTC counter to count a designated number (Frequency Terminal Count) of service clock periods. A register common to all links (see "CI SRTS FTC register" on page 45) establishes the number of service clock periods to be counted. This number is generally 3008 (decimal). There is one readable Link FTC counter for each link (see "Link FTC read back" entries in "Circuit Interface per-link registers" on page 85). To change the count used by the Link FTC counter, write the CI SRTS FTC register (page 45).

| ı | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7      | 6       | 5      | 4 | 3 | 2 | 1 | 0 |

|---|----|----|----|----|----|----|---|---|--------|---------|--------|---|---|---|---|---|

|   |    | (  | )  | Ι  |    | I  | I | I | i<br>L | _INK_SF | RTS_FT | C | ł | I | I | 1 |

| L |    |    |    |    |    | 1  | 1 | 1 | 1      |         |        |   |   | 1 |   | 1 |

# Link SRTS Value register

Each link has a single SRTS generator controlled by the SRTS\_MD bit for that link (see "Link Configuration register" on page 12). A 4-bit value is latched into the local SRTS value each time the FTC counter expires (see "Link FTC counter" on page 36). There is one of these read/write registers for each link.

| 1 | 15 | 14 | 13 | 12 | 11 | 10  | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2     | 1        | 0   |

|---|----|----|----|----|----|-----|---|---|---|---|---|---|---|-------|----------|-----|

|   |    |    |    | I  | I  | . ( | ) | T | T | 1 | 1 | I | S | RTS_V | ALUE [3: | :0] |

|   |    |    |    |    |    | 1   |   | 1 | 1 | 1 |   |   |   | 1     | 1        | 1   |

# CI TRI-STATE CONTROL BASE ADDRESS REGISTER

The value in this register defines the base address of the Tri-state Control table in Gather Memory. The contents of this register and the Tri-state Control Address counter are combined with the Link ID number (LID) to create an 18-bit pointer to a halfword-aligned entry in Gather Memory containing the tri-state control map for the link. See "Creation of the tri-state control map pointer" on page 28.. There is only one CI Tri-state Control Base Address register; it is a read/write register.

| L | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5      | 4  | 3 | 2 | 1 | 0 |

|---|----|----|----|----|----|----|---|---|---|---|--------|----|---|---|---|---|

|   |    |    | 0  |    |    |    |   |   |   | T | SC_BAS | SE |   |   |   |   |

# **CI** CONFIGURATION REGISTER

This register controls the operating mode of the Circuit Interface. There is only one CI Configuration register; it is a read/write register.

| I | 15     | 14 | 13     | 12 | 11    | 10    | 9 | 8     | 7 | 6 | 5      | 4 | 3 | 2      | 1 | 0       |

|---|--------|----|--------|----|-------|-------|---|-------|---|---|--------|---|---|--------|---|---------|

|   | FS_POL |    | SS_PER |    | LP_BK | FS_EN |   | MAXRB | 5 |   | MAXTBS | 5 | ſ | MAXDSO | ) | FS_MODE |

### FS\_POL (Bit 15)

This bit controls the interpretation of the polarity of the Frame Sync input. If this bit is set to one (1), FSYNC active level is zero (0). If this bit is cleared to zero (0), FSYNC active level is one (1).

### Snap Shot Period (Bits 14-12)

These bits should be written as 010 and ignored on reads. With this setting, the maximum unidirectional-mode link speed is 8 MHz and the maximum bidirectionalmode link speed is 4, 6, or 8 MHz for System Clock speeds of 33 MHz, 40 MHz, and 50 MHz respectively.

### LP\_BK (Bit 11)

This bit enables link loopback mode. If this bit is set to one (1), the link pair is placed in loopback mode. In unidirectional mode, all links loop their ASER transmit output back to BSER receive input. In bidirectional mode, the ASER transmit output is looped back to the ASER receive input, and the BSER transmit output is looped back to the BSER receive input. If this bit is cleared to zero (0), the link pair is placed in normal operating mode.

When a link pair is in loopback mode, no data is presented to the ASER or BSER pins. Clock signals are not affected by loopback. During loopback mode, clocking and Frame Sync must be supplied in the same fashion as for normal operating mode.

### FS\_EN (Bit 10)

This bit enables/disables Frame Sync detection. When asserted, this global bit permits all SDT mode links to acquire Frame Sync simultaneously. If this bit is set to one (1), Frame Sync detection is enabled, enabling all SDT mode links that have their LkRESET bits<sup>1</sup> clear (0). If this bit is cleared to zero (0), Frame Sync detection is disabled, disabling all SDT mode links. This bit only applies to SDT mode links. UDT mode links ignore this bit.

### MAXRBS (Bits 9-7)

| Bit 6 | Bit 5     | Bit 4 | Maximum TDM to ATM receive frame storage |

|-------|-----------|-------|------------------------------------------|

| 0     | 0         | 0     | 64 frames                                |

| 0     | 0         | 1     | 128 frames                               |

| 0     | 1         | 0     | 256 frames                               |

| 0     | 1         | 1     | 512 frames                               |

| 100   | ) through | 111   | Reserved                                 |

These bits specify the maximum amount of TDM to ATM receive frame storage allocated for any link in the system.

<sup>1.</sup> LkRESET bits are in the Link Configuration registers for each link. See "LkRESET (bit 0)" on page 15.

#### MAXTBS (Bits 6-4)

| Bit 9 | Bit 8     | Bit 7 | Maximum ATM to TDM transmit frame<br>storage |

|-------|-----------|-------|----------------------------------------------|

| 0     | 0         | 0     | 64 frames                                    |

| 0     | 0         | 1     | 128 frames                                   |

| 0     | 1         | 0     | 256 frames                                   |

| 0     | 1         | 1     | 512 frames                                   |

| 100   | ) through | 111   | Reserved                                     |

These bits specify the maximum amount of ATM to TDM transmit frame storage allocated for any link in the system.

### MAXDS0 (Bits 3-1)

These bits specify the maximum number of DS0's per frame for any link in the system.

| Bit 3 | Bit 2      | Bit 1 | Maximum DS0's per frame |  |

|-------|------------|-------|-------------------------|--|

| 0     | 0          | 0     | 24                      |  |

| 0     | 0          | 1     | 32                      |  |

| 0     | 1          | 0     | 64                      |  |

| 0     | 1          | 1     | 96                      |  |

| 1     | 0          | 0     | 128                     |  |

| 1     | 01 through | n 111 | Reserved                |  |

#### FS\_MODE (bit 0)

This bit determines the frame sync source for all of the links. If this bit is set to one (1), each link receives its frame sync (or an equivalent signal) from that link's BSCE pin. If this bit is cleared to zero (0), all links receive frame sync (or an equivalent signal) from the chip Frame Sync pin. This bit must be cleared to zero (0) when any links are in the bidirectional mode.

# MAXDS0, MAXTBS, and MAXRBS and buffer sizing

The MAXDSO, MAXTBS, and MAXRBS bits define a common buffer size in Scatter/Gather memory for all of the TDM links. The common buffer size for all links is the maximum required by any link being served. The following examples are provided:

#### Example #1:

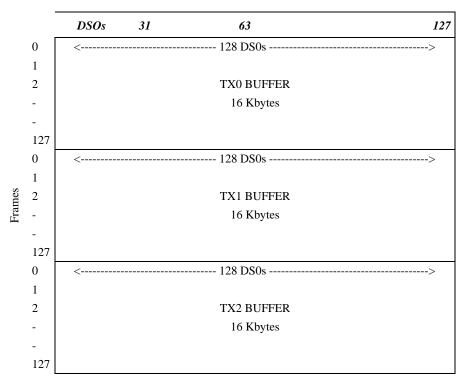

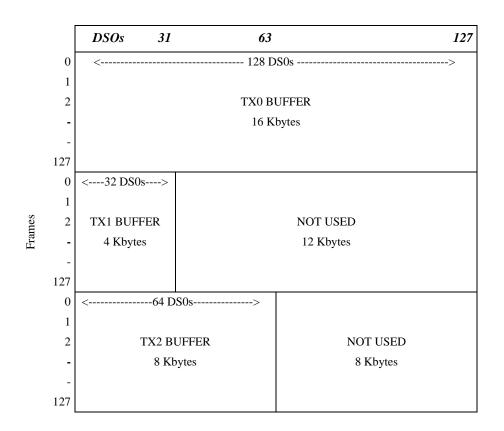

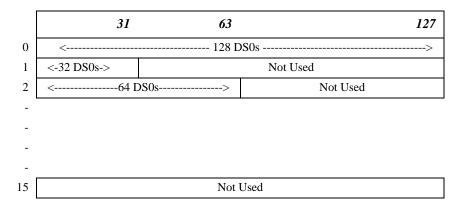

If three active transmit links have a MAXRBS = 128 frames and a MAXDS0 = 128 DS0s, each link buffer is 16 Kbytes ( $128 \times 128$ ).

#### Example #2:

If there are three active transmit links with a MAXRBS = 128 frames and MAXDS0s of 128, 32, and 64 DS0s per frame, all three buffers are the 16 Kbytes ( $128 \times 128$ ) required by the link with the largest buffering requirement. Utilization of the three 16 Kbyte buffers is shown in the figure.

# CI QUIET FRAME BASE ADDRESS REGISTER

An 11-bit value in this register defines the base address of the Quiet Frame in Gather Memory. Additional bits indicate the type of Scatter and Gather SRAM used, control access to the high memory space (FE000 - FFC00), and enable the quiet logic. There is only one CI Quiet Frame Base Address register; it is a read/write register.

| 1 | 5 | 14 | 13 | 12 | 11  | 10     | 9  | 8 | 7 | 6 | 5 | 4 | 3       | 2       | 1       | 0        |

|---|---|----|----|----|-----|--------|----|---|---|---|---|---|---------|---------|---------|----------|

|   |   |    |    |    | QUI | et_fra | ME | 1 |   | 1 | 1 | 0 | GATH_4M | SCAT_4M | EN_HMEM | en_quiet |

#### QUIET\_FRAME (Bits 15-5)

These bits define the base address of the Quiet Frame in Gather Memory.

### **RESERVED (Bit 4)**

This bit is reserved. It should be written as a zero and ignored on reads.

### GATH\_4M (Bit 3)

Set this bit to one (1) if the Gather Memory is implemented with a single 256K x 16 (4 Mb) SRAM. Set this bit to zero (0) if smaller parts are used. This bit controls the Gather Memory address decoding and asserts GATH\_OE\_[0] when any Gather Memory location is read. GATH\_OE\_[0] connects to the SRAM output enable pin.

### SCAT\_4M (Bit 2)

Set this bit to one (1) if the Scatter Memory is implemented with a single 256K x 16 (4 Mb) SRAM. Set this bit to zero (0) if smaller parts are used. This bit controls the Scatter Memory address decoding and asserts SCAT\_OE\_[0] when any Scatter Memory location is read. SCAT\_OE\_[0] connects to the SRAM output enable pin.

### EN\_HMEM (Bit 1)

This bit enables MXT3020 response to Port 2 access in the co-processor high memory space (i.e. FE000 - FFC00). If this bit is set to one (1), the MXT3020 responds to high memory addresses. If this bit is cleared to zero (0), the MXT3020 does not respond to high memory addresses.

When two MXT3020s are present on the same P2 bus, all 2 Mbytes of available address space are assigned. However, the MXT3020 defaults at power-up to not use a small window of space between FE000 and FC000. If a designer wishes, these addresses can be used for a CAM or similar burst mode device. If, however, it is desired to use this space for additional Gather Memory, programs utilizing the MXT3020 should set EN\_HMEM to one (1).

### EN\_QUIET (Bit 0)

This bit enables the quiet logic. If this bit is set to one (1), the quiet logic is enabled. If this bit is cleared to zero (0), the quiet logic is disabled.

# Quiet Logic

The Circuit Interface contains the *quiet logic*. For each transmit link, a dummy *quiet frame* exists in Gather Memory with the proper quiet value for each DS0 in the frame. The quiet logic copies these quiet frames into the Transmit Link buffers as soon as the data in the buffers has been shifted out onto the TDM lines. The quiet frames reside in the Transmit Link buffers until replaced by data arriving from the ATM link. In this way, the MXT3020 ensures that in the event of an ATM link underflow, the correct quiet values (rather than stale data) are transmitted on the TDM links.

The quiet logic reads the quiet values from predefined quiet frames in Gather Memory and writes them into the TDM transmit frame buffers in Scatter Memory. There must be one quiet frame for every active TDM transmitter. The logic reads bursts of eight halfwords from the Gather Memory and then arbitrates for, and writes, the halfwords into Scatter Memory. This process continues until one frame in each TDM transmit buffer is overwritten. To be efficient, and to reduce the overhead required for this operation, the controllers use the Link Reset and Data Transfer Mode bits of the Link Configuration registers to skip links that are unused or are setup for unstructured data transfer mode. The quiet frame area can be a maximum size of 16 frames with 128 bytes per frame, or 2 Kbytes in size. The 2-Kbyte area can be located anywhere in Gather Memory above the TDM Link receive buffers, which always begin at Port2 address 0x80000. The Quiet Frame Base Address register locates the quiet frame area and must be setup at initialization. Bit [0] of this register enables/disables the quiet logic.

Although each quiet frame has storage for 128 quiet DS0 values, only the actual number of quiet DS0's need to be initialized for each frame. For example, if only three links were transmitting, links 0, 1, and 2, and they supported 128, 32 and 64 DS0's respectively, then the allocation map for the quiet frame area would look like the following:

# CI SRTS FTC REGISTER

The value in the CI SRTS FTC register represents the number of service clock<sup>1</sup> periods between updates of the Link SRTS Value register (see "Link FTC counter" on page 36 and "Link SRTS Value register" on page 36). Whenever a Link FTC counter counts down to zero, it is reloaded from the CI SRTS FTC register, which is typically set to 3008. There is only one CI SRTS FTC register; it is a read/write register.

| L | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6     | 5     | 4 | 3 | 2 | 1 | 0 |