## **General Description**

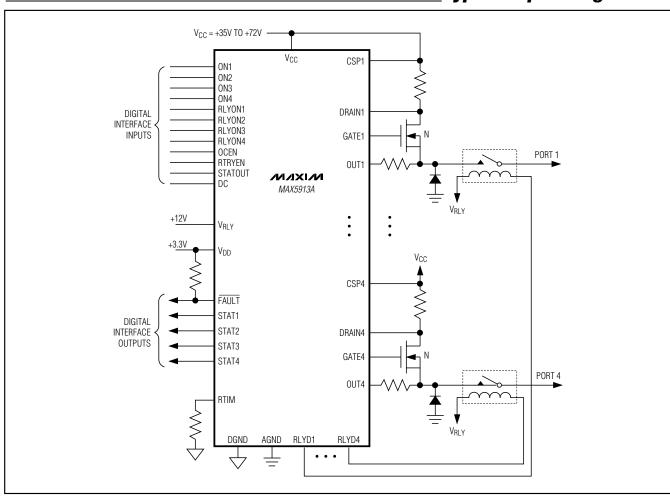

The MAX5913A/MAX5914A are quadruple hot-swap controllers. The MAX5913A/MAX5914A independently control four external n-channel switches to hot-swap system loads from a single VCC supply line. The devices allow the safe insertion and removal of power devices from live network ports. The operating supply voltage range is between +35V and +72V. The devices are intended for applications in Power-Over-Media-Dependent Interface (MDI), but are not limited to such usage.

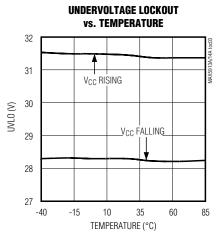

The MAX5913A/MAX5914A feature an internal undervoltage lockout (UVLO) function that prevents the FET from turning on, if VCC does not exceed the default value of +32V. The devices also feature a +12V relay driver with 100mA current drive capable of driving lowvoltage +3.3V relays. The MAX5913A features an active-low relay driver that sinks current when the relay output is enabled. The MAX5914A features an activehigh relay driver output that sources 1mA to drive an external FET relay driver when the relay output is enabled. Control circuitry ensures the relays and the FETs are off until VCC reaches the UVLO threshold. The MAX5913A/MAX5914A use an external sense resistor to enable all the internal current-sense functions.

The MAX5913A/MAX5914A feature a programmable analog current-limit circuit. If the switch remains in current limit for more than a programmable time, the n-channel FET latches off and the supply can be restarted either by autoretry or by an external command after the preset offtime has elapsed.

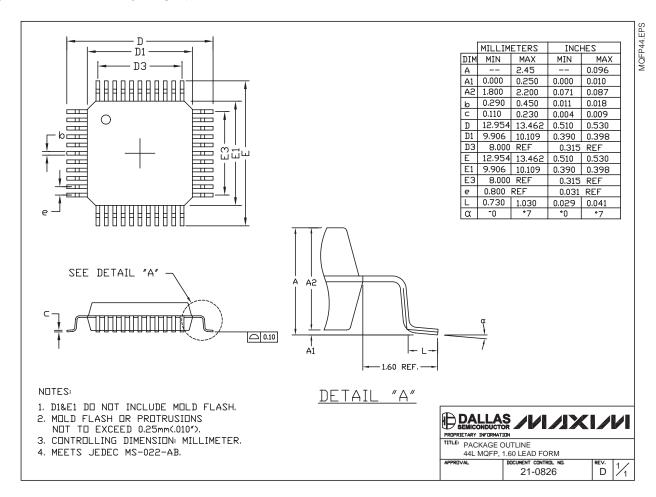

The MAX5913A/MAX5914A are available in a 44-pin MQFP package and are specified for the extended -40°C to +85°C operating temperature range.

## **Applications**

Power-Over-LAN Power-Over-MDI IP Phone Switches/Routers Telecom Line Cards Network Switches/Routers Midspan Power-Over-MDI

Typical Operating Circuit appears at end of data sheet.

#### **Features**

- **♦ Wide Operating Input Voltage Range:** +35V to +72V

- **♦ IEEE 802.3af Compatible**

- **♦** Four Independent Power Switch Controllers

- ♦ Open-Circuit Detector

- ♦ On-Board Charge Pumps to Drive External n-Channel FETs

- Current Sense with External Resistor

- **♦ Foldback Current Limiting**

- ♦ +32V Input Undervoltage Lockout

- ♦ On-Chip +12V, 100mA Voltage Relay Drivers

# **Ordering Information**

| PART         | TEMP RANGE     | PIN-<br>PACKAGE | PKG<br>CODE |

|--------------|----------------|-----------------|-------------|

| MAX5913AEMH  | -40°C to +85°C | 44 MQFP         | M44-3       |

| MAX5914AEMH* | -40°C to +85°C | 44 MQFP         | M44-3       |

<sup>\*</sup>Future product—contact factory for availability.

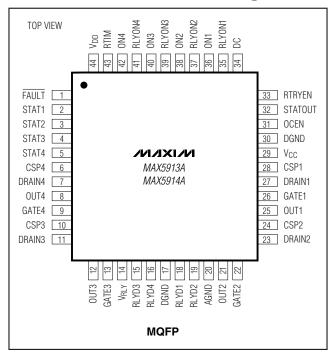

# **Pin Configuration**

MIXIM

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to AGND or DGND | 0.6V to +76V                    |

|---------------------------------|---------------------------------|

| DRAIN_, OUT_ to AGND or DGND    | 0.6V to (V <sub>CC</sub> +0.3V) |

| CSP_ to V <sub>CC</sub>         | 0.3V to +0.3V                   |

| GATE_ to OUT                    | 0.3V to +13V                    |

| V <sub>RLY</sub> to DGND        | 0.3V to +18V                    |

| RLYD_ to DGND                   | 0.3V to $(V_{RLY} + 0.3V)$      |

| ON_, RLYON_, OCEN, RTRYEN, STA  | TOUT,                           |

| DC to DGND                      | 0.3V to +12V                    |

| FAULT to DGND                   | 0.3V to +12V                    |

| STAT_, RTIM to DGND             | 0.3V to $(V_{DD} + 0.3V)$       |

|                                 |                                 |

| V <sub>DD</sub> to DGND                              | 0.3V to +7V    |

|------------------------------------------------------|----------------|

| DGND to AGND                                         | 5V to +5V      |

| Current into RLYD                                    | 50mA to +150mA |

| Current into Any Other Pin                           | ±50mA          |

| Continuous Power Dissipation ( $T_A = +70^{\circ}$ C | C)             |

| 44-Pin MQFP (derate 12.7mW/°C above                  | +70°C) 1.013W  |

| Operating Temperature Range                          | 40°C to +85°C  |

| Storage Temperature Range                            | 65°C to +150°C |

| Lead Temperature (soldering, 10s)                    | +300°C         |

|                                                      |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

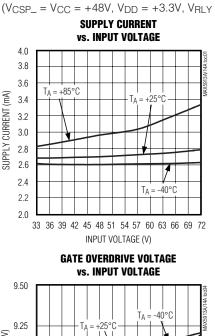

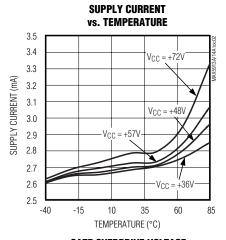

## **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = V_{CSP\_} = +48V, AGND = DGND = 0V, V_{DD} = +3.3V, V_{RLY} = +12V, T_A = -40^{\circ}C \ to \ +85^{\circ}C, unless otherwise noted. Typical values are at V_{CC} = V_{CSP\_} = +48V \ and T_A = +25^{\circ}C.)$

| PARAMETER                             | SYMBOL                | CONDITIONS                                                                                                         |                                      |      | TYP   | MAX  | UNITS |

|---------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------|------|-------|------|-------|

| POWER SUPPLIES                        | •                     |                                                                                                                    | <u> </u>                             |      |       |      |       |

| Analog Supply Voltage                 | Vcc                   | Measured with respect to AGND                                                                                      |                                      | 35   |       | 72   | V     |

| Analog Supply Current                 | lo                    | V <sub>CC</sub> = V <sub>CSP</sub> _ = 72V                                                                         | $T_A = 0$ °C to +85°C                |      | 2.7   | 4    | mA    |

| Analog Supply Current                 | IS                    | IS = ICC + ICSP                                                                                                    | $T_A = -40^{\circ}C$ to $0^{\circ}C$ |      |       | 5    | IIIA  |

| Digital Supply Voltage                | $V_{DD}$              | Measured with respe                                                                                                | ct to DGND                           | 2.5  | 3.3   | 3.7  | V     |

| Digital Supply Current                | I <sub>DD</sub>       | All logic outputs high                                                                                             | , RTIM floating                      |      | 1.1   | 3    | mA    |

| Analog Supply Undervoltage<br>Lockout | Vuvlo                 | V <sub>CC</sub> rising, circuits en                                                                                | nabled                               | 29   | 32    | 35   | V     |

| UVLO Hysteresis                       | V <sub>U</sub> VLO,H  |                                                                                                                    |                                      |      | 3     |      | V     |

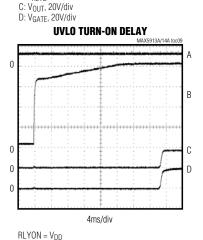

| UVLO Deglitch Delay                   | t <sub>D,UVLO</sub>   | $V_{ON} = 3.3V, V_{RLYON}$                                                                                         | = 3.3V (Figure 1)                    | 12.8 | 25.6  | 38.4 | ms    |

| Relay Driver Supply                   | V <sub>RLY</sub>      | Measured with respe                                                                                                | ct to DGND                           |      |       | 14   | V     |

| Ground Potential Difference           | V <sub>G</sub> G      | Voltage difference between DGND and AGND                                                                           |                                      | -4   |       | 4    | V     |

| FEEDBACK INPUT AND CURREN             | T SENSE               |                                                                                                                    | -                                    |      |       |      |       |

| OUT Sense Bias Current                | IFP                   | V <sub>OUT</sub> _ = V <sub>C</sub> C                                                                              |                                      |      |       | 2    | μΑ    |

| Initial Feedback Voltage              | V <sub>FB</sub> _S    | Voltage under which the foldback circuit starts reducing the current-limit value (Note 1)                          |                                      |      | 18    |      | V     |

| Current-Limit Threshold Voltage       | $V_{SC}$              | Maximum ΔV across R <sub>SENSE</sub> at V <sub>OUT</sub> > V <sub>FB</sub> _S                                      |                                      | 125  | 142.5 | 160  | mV    |

| Foldback Voltage                      | V <sub>FLBK</sub>     | Maximum ΔV across R <sub>SENSE</sub> at V <sub>OUT</sub> = 0V                                                      |                                      | 42   | 48    | 54   | mV    |

| Fast Discharge Threshold              | VFC                   |                                                                                                                    |                                      | 360  | 420   | 480  | mV    |

| Switch-On Threshold                   | Vswon                 | Maximum V <sub>CC</sub> - V <sub>OUT</sub> at which the switch is defined as fully on, V <sub>OUT</sub> increasing |                                      | 1.2  | 1.5   | 1.8  | V     |

| Switch-On Comparator Hysteresis       | Vswon_H               |                                                                                                                    |                                      |      | 160   |      | mV    |

| MOSFET DRIVERS                        |                       |                                                                                                                    | ·                                    |      |       |      | •     |

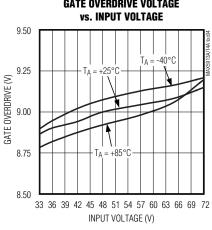

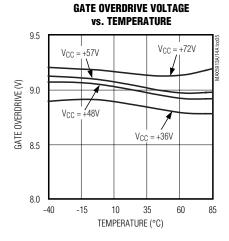

| Gate Overdrive Voltage                | V <sub>GS</sub>       | VGATE - VCC when switch is fully on 0°C to +85°C                                                                   |                                      | 7    | 9     | 11   | V     |

|                                       | $T_A = -40$ °C to 0°C |                                                                                                                    |                                      | 7    | 9     | 12   |       |

| Gate Charge Current                   | IGATE                 | VGATE = 0V                                                                                                         |                                      |      | 10    | 13   | μΑ    |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = V_{CSP\_} = +48V, AGND = DGND = 0V, V_{DD} = +3.3V, V_{RLY} = +12V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted. Typical values are at } V_{CC} = V_{CSP\_} = +48V \text{ and } T_A = +25^{\circ}C.) \text{ (Note 3)}$

| PARAMETER                                | SYMBOL              | CONDITIONS                                                          |                       | MIN                   | TYP  | MAX                 | UNITS |

|------------------------------------------|---------------------|---------------------------------------------------------------------|-----------------------|-----------------------|------|---------------------|-------|

|                                          |                     | During current regulation                                           |                       |                       | 8    |                     | μΑ    |

| Gate Discharge Current                   | IGATE, DIS          | VON = 0V<br>(VCSP VDRAIN_) > VFC                                    |                       |                       | 1    |                     | mA    |

|                                          |                     |                                                                     |                       |                       | 15   |                     | mA    |

| Source-Gate Clamp Voltage                | Vsgz                | VOUT_ = 0V, force 30m<br>measure VGATE - VOUT                       |                       | 14                    | 16.5 | 18                  | V     |

| OPEN-CIRCUIT DETECTOR                    |                     |                                                                     |                       |                       |      |                     |       |

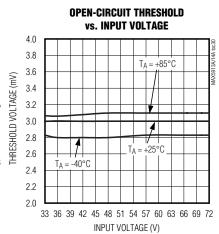

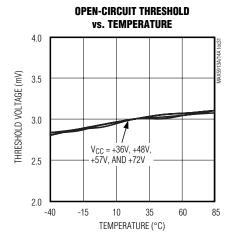

| Open-Circuit Current-Threshold Voltage   | Voc                 | Minimum ΔV across R <sub>SENSE</sub> to detect an open circuit      |                       | 1.5                   | 3    | 4.5                 | mV    |

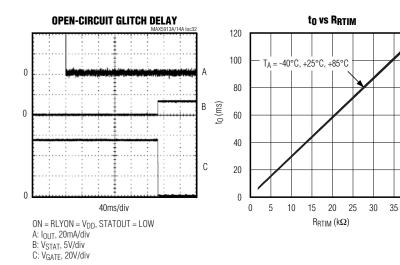

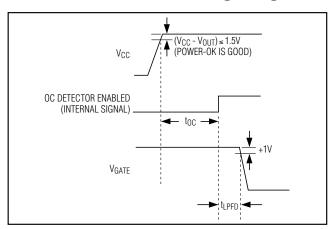

| Delay to Open-Circuit Detect             | toc                 | (Figure 2)                                                          |                       | 450                   | 900  | 1350                | ms    |

| Deglitch Delay                           | tLPFD               | (VCSP VDRAIN_) < V                                                  | OC (Figure 2)         | 106                   | 204  | 302                 | ms    |

| RELAY DRIVERS                            |                     |                                                                     |                       | •                     |      |                     |       |

| Maximum Low Voltage (MAX5913A)           | V <sub>RLOW</sub>   | RLYON = high, I <sub>RLYD</sub> _                                   | = 100mA               |                       |      | 0.5                 | V     |

| Relay Pullup Current (MAX5914A)          | IRPLUP              | RLYON = high, V <sub>RLYD</sub>                                     | _ = 0V                | 0.3                   | 0.8  | 1.3                 | mA    |

| Clamp Diode Voltage                      | V <sub>RCLAMP</sub> | Force 100mA into RLYD, measure V <sub>RLYD</sub> - V <sub>RLY</sub> |                       |                       |      | 2                   | V     |

| Relay Output Leakage                     |                     | RLYON_ = low, V <sub>RLYD</sub> _ = V <sub>RLY</sub>                |                       |                       | 1    |                     | μΑ    |

| TIMING                                   | •                   |                                                                     |                       | •                     |      |                     |       |

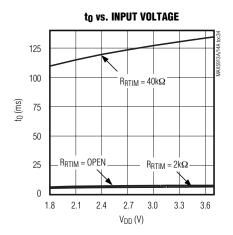

|                                          |                     | On time for continuous overcurrent conditions                       | $R_{RTIM} = 2k\Omega$ | 4.8                   | 6.4  | 8.0                 | ms    |

| Short-Circuit and Startup Timer (Note 2) | to                  |                                                                     | I RDTIM = 40kQ        | 76                    | 128  | 180                 |       |

| (Note 2)                                 |                     |                                                                     | R <sub>RTIM</sub> = ∞ | 3.2                   | 6.4  | 9.6                 |       |

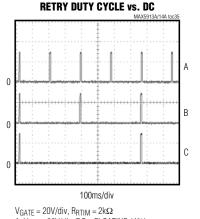

|                                          |                     | DC = logic low                                                      |                       |                       | 1    |                     |       |

| Auto-Retry Duty Cycle                    |                     | DC = logic high                                                     |                       |                       | 2    |                     | %     |

|                                          |                     | DC = floating                                                       |                       |                       | 4    |                     |       |

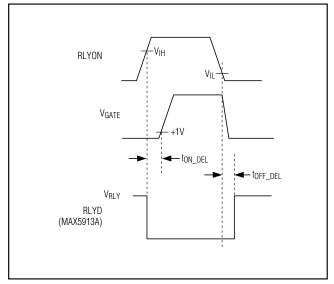

| Port Turn-On Delay                       | ton_del             | V <sub>ON</sub> = 3.3V (Figure 3)                                   |                       | 12.8                  | 25.6 | 38.4                | ms    |

| Relay Turn-Off Delay                     | toff_del            | After RLYON_ goes lov                                               | v (Figure 3)          | 1.6                   | 3.2  | 4.8                 | ms    |

| DIGITAL INTERFACE                        |                     |                                                                     |                       |                       |      |                     |       |

| DC Pin Input-Voltage High                | V <sub>IH</sub> _DC | 2.5V ≤ V <sub>DD</sub> ≤ 3.7V                                       |                       | 0.7 x V <sub>DD</sub> |      |                     | V     |

| DC Pin Input-Voltage Low                 | V <sub>IL_DC</sub>  | 2.5V ≤ V <sub>DD</sub> ≤ 3.7V                                       |                       |                       |      | $0.3 \times V_{DD}$ | V     |

| DC Pin Input Impedance                   | R <sub>IN_DC</sub>  |                                                                     |                       |                       | 1    |                     | kΩ    |

| Logic Input High                         | $V_{IH}$            | $2.5V \le V_{DD} \le 3.7V$                                          |                       | $0.8 \times V_{DD}$   |      |                     | V     |

| Logic Input Low                          | V <sub>I</sub> L    | 2.5V ≤ V <sub>DD</sub> ≤ 3.7V                                       |                       |                       |      | $0.3 \times V_{DD}$ | V     |

| Logic Input Leakage                      |                     |                                                                     |                       |                       |      | 1                   | μΑ    |

| FAULT Output-Voltage Low                 | V <sub>F</sub> L    | I <sub>SINK</sub> = 4mA                                             |                       |                       |      | 0.4                 | V     |

| FAULT High Input Leakage                 |                     |                                                                     |                       |                       |      | 1                   | μΑ    |

| Logic Output-Voltage High                | Voh                 | STAT_ outputs sourcing 0.5mA                                        |                       | V <sub>DD</sub> - 0.4 |      |                     | mV    |

| Logic Output-Voltage Low                 | V <sub>OL</sub>     | STAT_ outputs sinking 0.5mA                                         |                       |                       |      | 0.4                 | ٧     |

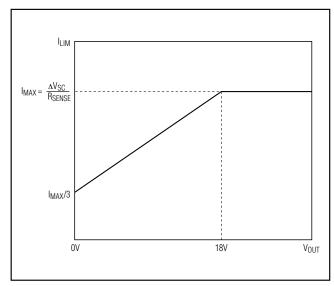

Note 1: See Typical Operating Characteristics for Current-Limit Foldback, and refer to Current Sensing and Regulation section.

**Note 2:** The resistor at RTIM can range from  $2k\Omega$  to  $40k\Omega$ .

Note 3: Limits are 100% tested at T<sub>A</sub> = +25°C and T<sub>A</sub> = +85°C. Limits at -40°C are guaranteed by design and characterization, but are not production tested.

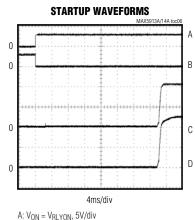

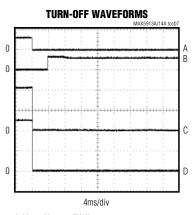

$(V_{CSP\_} = V_{CC} = +48V, V_{DD} = +3.3V, V_{RLY} = +12V, \ AGND = DGND = 0V, \\ RTIM = open, \\ T_{A} = +25^{\circ}C, \\ unless otherwise specified.)$

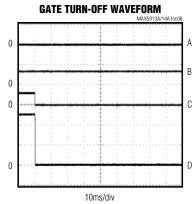

A:  $V_{ON} = V_{RLYON}$ , 5V/div B:  $V_{RLYD}$ , 20V/div C:  $V_{OUT}$ , 20V/div D:  $V_{GATE}$ , 20V/div A: V<sub>RLYD</sub>, 20V/div B: V<sub>RLYON</sub>, 5V/div C: V<sub>ON</sub>, 5V/div D: V<sub>GATE</sub>, 20V/div

A: V<sub>ON</sub>, 5V/div B: V<sub>CC</sub>, 10V/div C: V<sub>OUT</sub>, 50V/div D: V<sub>GATE</sub>, 50V/div

B: V<sub>RLYD</sub>, 20V/div

re, 50V/div

# Typical Operating Characteristics (continued)

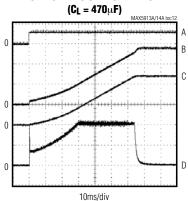

(V<sub>CSP</sub> = V<sub>CC</sub> = +48V, V<sub>DD</sub> = +3.3V, V<sub>RLY</sub> = +12V, AGND = DGND = 0V, RTIM = open, T<sub>A</sub> = +25°C, unless otherwise specified.)

#### **TURN-ON INTO CAPACITIVE LOAD** $(C_L = 0.47 \mu F)$

RLYON = V<sub>DD</sub> A: V<sub>ON</sub>, 5V/div

B: V<sub>GATE</sub>, 20V/div C: V<sub>OUT</sub>, 20V/div D: I<sub>OUT</sub>, 100mA/div

# **TURN-ON INTO CAPACITIVE LOAD**

$\begin{aligned} &RLYON = V_{DD}, \ R_{RTIM} = 2k\Omega \\ &A: \ V_{ON}, \ 5V/div \end{aligned}$

B: V<sub>GATE</sub>, 20V/div C: V<sub>OUT</sub>, 20V/div D: I<sub>OUT</sub>, 200mA/div

# **TURN-ON INTO CAPACITIVE LOAD**

$RLYON = V_{DD}, \, R_{RTIM} = 40 k \Omega$

A: V<sub>ON</sub>, 5V/div

B: V<sub>GATE</sub>, 20V/div C: V<sub>OUT</sub>, 20V/div

D: I<sub>OUT</sub>, 200mA/div

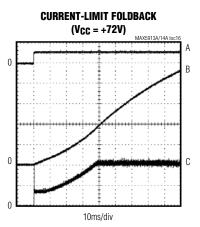

# **CURRENT-LIMIT FOLDBACK**

$RLYON = V_{DD}, \ R_L = 100\Omega, \ R_{RTIM} = 40k\Omega, \ C_{LOAD} = 470\mu F$

A: Von, 5V/div B: Vout, 10V/div C: I<sub>OUT</sub>, 200mA/div

# **CURRENT-LIMIT FOLDBACK**

$RLYON = V_{DD}, \, R_L = 139 \Omega, \, R_{RTIM} = 40 k \Omega, \, C_{LOAD} = 470 \mu F$

A: Von, 5V/div B: Vout, 10V/div

C: I<sub>OUT</sub>, 200mA/div

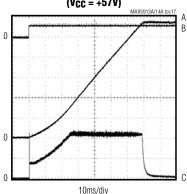

# **CURRENT-LIMIT FOLDBACK**

$RLYON = V_{DD}, \ R_L = 162\Omega, \ R_{RTIM} = 40 k\Omega, \ C_{LOAD} = 470 \mu F$

A: Von, 5V/div B: Vout, 10V/div

C: I<sub>OUT</sub>, 200mA/div

# Typical Operating Characteristics (continued)

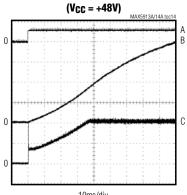

(VCSP\_ = VCC = +48V, VDD = +3.3V, VRLY = +12V, AGND = DGND = 0V, RTIM = open, TA = +25°C, unless otherwise specified.)

- $RLYON = V_{DD}, \; R_L = 200\Omega, \; R_{RTIM} = 40k\Omega$

- A: V<sub>ON</sub>, 5V/div

- B: V<sub>OUT</sub>, 10V/div C: I<sub>OUT</sub>, 200mA/div

#### **CURRENT-LIMIT FOLDBACK** $(V_{CC} = +57V)$

- $RLYON = V_{DD}, \ R_L = OPEN,$  $R_{RTIM}=40k\Omega,\;C_{LOAD}=470\mu F$

- A: V<sub>ON</sub>, 5V/div

- B: V<sub>OUT</sub>, 10V/div C. I<sub>OUT</sub>, 200mA/div

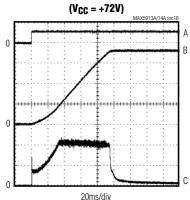

# **CURRENT-LIMIT FOLDBACK**

- $RLYON = V_{DD}, \ R_L = OPEN, \ R_{RTIM} = 40 k\Omega, \ C_{LOAD} = 470 \mu F$

- A: V<sub>ON</sub>, 5V/div

- B: V<sub>OUT</sub>, 20V/div C: I<sub>OUT</sub>, 200mA/div

## **OVERCURRENT DELAY**

- $RTRYEN = V_{DD}, \; RLYON = ON = V_{DD}, \; DC = 4\%, \;$

- $R_{RTIM}=2k\Omega,\,R_L=100\Omega$ A: VGATE, 20V/div

- B: I<sub>OUT</sub>, 200mA/div

#### **OVERCURRENT DELAY** (EXPANDED TIME SCALE)

- RTRYEN =  $V_{DD}$ , RLYON =  $0N = V_{DD}$ , DC = DON'T CARE,  $R_{RTIM} = 2k\Omega$ ,  $R_L = 100\Omega$  A:  $V_{GATE}$ , 20V/div

- B: I<sub>OUT</sub>, 200mA/div

#### **SHORT-CIRCUIT RESPONSE** $(V_{CC} = +48V)$

- $0N = RLYON = V_{DD}, \, R_L = 1\Omega, \, R_{RTIM} = 2k\Omega$

- A: I<sub>OUT</sub>, 200mA/div

- B: V<sub>GATE</sub>, 20V/div

# Typical Operating Characteristics (continued)

(V<sub>CSP</sub><sub>\_</sub> = V<sub>CC</sub> = +48V, V<sub>DD</sub> = +3.3V, V<sub>RLY</sub> = +12V, AGND = DGND = 0V, RTIM = open, T<sub>A</sub> = +25°C, unless otherwise specified.)

#### **SHORT-CIRCUIT RESPONSE** (V<sub>CC</sub> = +48V EXPANDED TIME SCALE)

$0N = RLY0N = V_{DD}, \ R_L = 1\Omega, \ R_{RTIM} = 2k\Omega$ A: I<sub>OUT</sub>, 200mA/div B: V<sub>GATE</sub>, 20V/div

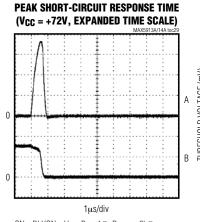

#### **PEAK SHORT-CIRCUIT RESPONSE** (V<sub>CC</sub> = +48V EXPANDED TIME SCALE)

$0N=RLY0N=V_{DD},\,R_{L}=1\Omega,\,R_{RTIM}=2k\Omega$ A: I<sub>OUT</sub>, 5A/div B: V<sub>GATE</sub>, 20V/div

# **SHORT-CIRCUIT RESPONSE**

$\mathsf{ON} = \mathsf{RLYON} = \mathsf{V}_{DD}$ A: I<sub>OUT</sub>, 200mA/div B: V<sub>GATE</sub>, 20V/div

#### **SHORT-CIRCUIT RESPONSE** (VCC = +57V, EXPANDED TIME SCALE)

$0N = RLYON = V_{DD}, \ R_L = 1\Omega, \ R_{RTIM} = 2k\Omega$ A: I<sub>OUT</sub>, 200mA/div B: VGATE, 20V/div

#### **PEAK SHORT-CIRCUIT RESPONSE TIME** $(V_{CC} = +57V, EXPANDED TIME SCALE)$

$ON = RLYON = V_{DD}$ ,  $R_L = 1\Omega$ ,  $R_{RTIM} = 2k\Omega$ A: I<sub>OUT</sub>, 5A/div B: VGATE, 20V/div

# **SHORT-CIRCUIT RESPONSE**

$\mathsf{ON} = \mathsf{RLYON} = \mathsf{V}_{DD}$ A: I<sub>OUT</sub>, 200mA/div B: V<sub>GATE</sub>, 50V/div

# Typical Operating Characteristics (continued)

(VCSP\_ = VCC = +48V, VDD = +3.3V, VRLY = +12V, AGND = DGND = 0V, RTIM = open, TA = +25°C, unless otherwise specified.)

$\begin{array}{l} 0N = RLYON = V_{DD}, \, R_L = 1\Omega, \, R_{RTIM} = 2k\Omega \\ A: \, I_{OUT}, \, 200mA/div \\ B: \, V_{GATE}, \, 50V/div \end{array}$

$ON=RLYON=V_{DD},\,R_L=1\Omega,\,R_{RTIM}=2k\Omega$  A:  $I_{OUT},\,5A/div$  B:  $V_{GATE},\,50V/div$

# Typical Operating Characteristics (continued)

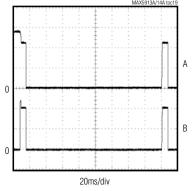

$(V_{CSP} = V_{CC} = +48V, V_{DD} = +3.3V, V_{RLY} = +12V, AGND = DGND = 0V, RTIM = open, T_A = +25°C, unless otherwise specified.)$

$V_{GATE} = 20V/div$ ,  $R_{RTIM} = 2k\Omega$ A:  $V_{GATE}$ , 20V/div, DC = FLOATING (4%) B:  $V_{GATE}$ , 20V/div,  $DC = V_{DD}$  (2%) C:  $V_{GATE}$ , 20V/div, DC = GND (1%)

# **Pin Description**

| PIN           | NAME                                | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | FAULT                               | Active-Low Fault Output. FAULT is an open-drain output that goes low when a fault is detected on any of the four channels. FAULT is low when an OC (open circuit) is detected, or when the MAX5913A/MAX5914A is in auto-retry caused by an overcurrent condition. When RTRYEN is low, and the channel switch is latched off due to an overcurrent condition, FAULT remains low until ON_ is driven low.                                                                                                                                                                 |

| 2, 3, 4, 5    | STAT1,<br>STAT2,<br>STAT3,<br>STAT4 | Status Outputs. STAT_ are push-pull outputs. Depending on the STATOUT pin status, STAT_ flags either the Power-OK_ or Port-OC_ status. Power-OK_ high indicates:  a) ON_ input is high. b) The switch port is fully on and startup is completed (VCSP VOUT_) < VSWON. c) Input voltage is above VUVLO. d) Switch is not in current limit. Power-OK_ low indicates a fault with any of the above conditions. Port-OC_ output high indicates that the switch is latched off because the switch current is less than the open-current threshold, Port-OC is low otherwise. |

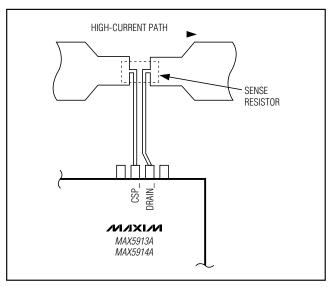

| 6, 10, 24, 28 | CSP4, CSP3, CSP2,<br>CSP1           | Current-Sense Positive Input. Connect to V <sub>CC</sub> and place a current-sense resistor from CSP_ to DRAIN Use a Kelvin sense trace from a current-sense resistor to CSP_ (see Figure 7).                                                                                                                                                                                                                                                                                                                                                                           |

| 7, 11, 23, 27 | DRAIN4, DRAIN3,<br>DRAIN2, DRAIN1   | MOSFET Drain Current-Sense Negative Input. Connect to drain of power MOSFET and connect a current-sense resistor from CSP_ to DRAIN Use Kelvin sense trace from current-sense resistor to DRAIN_ (see Figure 7).                                                                                                                                                                                                                                                                                                                                                        |

# Pin Description (continued)

| PIN               | NAME                              | FUNCTION                                                                                                                                                                                                                                                                                         |

|-------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8, 12, 21, 25     | OUT4, OUT3,<br>OUT2, OUT1         | MOSFET Source Output Voltage Sense. Connect to a power MOSFET source through a $100\Omega$ series resistor.                                                                                                                                                                                      |

| 9, 13, 22, 26     | GATE4, GATE3,<br>GATE2, GATE1     | MOSFET Gate Driver Output. The MAX5913A/MAX5914A regulate the gate-drive voltage to (V <sub>CC</sub> + 9V) to fully turn on the power n-channel MOSFET. GATE_ sources 10µA during startup to slowly turn on the MOSFET switch. GATE_ sinks 1mA to turn off the MOSFET switch.                    |

| 14                | V <sub>RLY</sub>                  | Relay Supply-Voltage Input. Referenced to DGND.                                                                                                                                                                                                                                                  |

| 15, 16, 18,<br>19 | RLYD3, RLYD4,<br>RLYD1, RLYD2     | Relay-Drive Output. For the MAX5913A, RLYD_ sinks 100mA when the relay driver is enabled. For the MAX5914A, RLYD_ sources 1mA when the relay driver is enabled.                                                                                                                                  |

| 17, 30            | DGND                              | Digital Ground. All logic voltages are referred to DGND. The voltage difference between DGND and AGND can be up to ±4V.                                                                                                                                                                          |

| 20                | AGND                              | Analog Ground. All analog voltages are referred to AGND.                                                                                                                                                                                                                                         |

| 29                | Vcc                               | Analog Power Supply. Connect $V_{CC}$ to +35V to +72V power supply. UVLO circuitry turns off the MOSFET switch and relay for $V_{CC}$ < $V_{UVLO}$ . Bypass $V_{CC}$ to AGND with a 1µF capacitor.                                                                                               |

| 31                | OCEN                              | Open-Circuit Detector Enable Input. Drive OCEN high to enable open-circuit detector, or drive low to disable. When enabled, the open-circuit detector waits for a 900ms delay after Power-OK conditions are met before enabling the open-circuit detector function.                              |

| 32                | STATOUT                           | Status Output Multiplexer (MUX) Control Input. Controls the signal MUX into the STAT_ outputs. Drive STATOUT high to route Power-OK_ status to STAT_ outputs, or drive STATOUT low to route Port-OC_ status to STAT_ outputs.                                                                    |

| 33                | RTRYEN                            | Auto-Retry Enable Input. Drive RTRYEN high to enable auto-retry. Drive RTRYEN low to enable switch latch-off mode. When switch is latched off, a high-to-low transition on the ON_ control input clears the latch.                                                                               |

| 34                | DC                                | Duty-Cycle Programming Input. DC sets the minimum off-time after an overcurrent condition latches off the switch. When RTRYEN is high, DC sets the auto-retry duty cycle. Drive DC low for 1% duty cycle, drive DC high for 2%, or leave DC floating for 4% duty cycle.                          |

| 35, 37, 39,<br>41 | RLYON1, RLYON2,<br>RLYON3, RLYON4 | Relay-Driver Control Input. Drive RLYON_ high to enable RLYD_, drive RLYON_ low to turn off the MOSFET switch for the channel and disable RLYD                                                                                                                                                   |

| 36, 38, 40,<br>42 | ON1, ON2, ON3,<br>ON4             | MOSFET Switch Control Input. Drive ON_ high to enable GATE_ to turn on the MOSFET switch. RLYON_ must be high to enable the switch. Drive ON_ low to disable the switch. Pulling ON_ low also resets the latch when RTRYEN is low or if the switch is latched off due to open-circuit detection. |

| 43                | RTIM                              | Timing Oscillator Frequency Set Input. Connect a $2k\Omega$ to $40k\Omega$ resistor from RTIM to DGND to set the maximum continuous overcurrent time, t <sub>O</sub> . Leave RTIM unconnected to set default 6.4ms t <sub>O</sub> .                                                              |

| 44                | $V_{DD}$                          | Digital Power Supply. Bypass VDD to DGND with a 1µF capacitor.                                                                                                                                                                                                                                   |

# **Detailed Description**

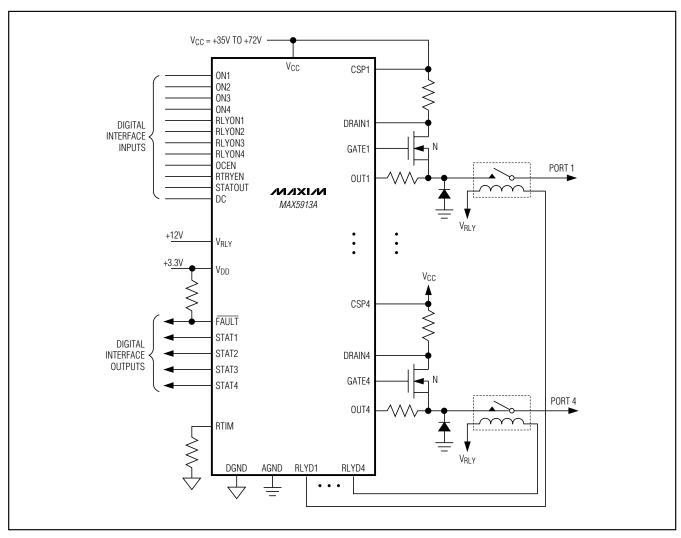

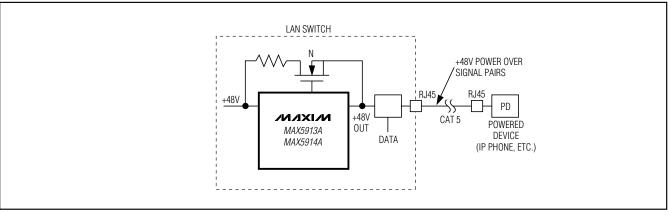

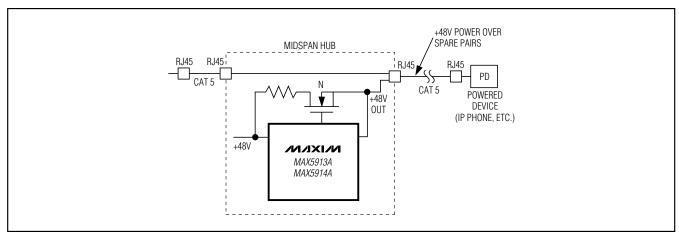

The MAX5913A/MAX5914A quadruple hot-swap controllers provide Power-Over-MDI, also known as Power-Over-LAN systems (Figure 5). The MAX5913A/MAX5914A enable control of four external n-channel MOSFET switches from a single V<sub>CC</sub> ranging from +35V to +72V, with timing control and current-limiting functions built in.

The MAX5913A/MAX5914A features include undervoltage lockout (UVLO), 100mA relay drivers, dual-level current sense, foldback current limit, programmable overcurrent time and auto-retry periods, internal charge pumps to drive external MOSFET and soft-start, port status output indicating power-OK (POK) or open-circuit conditions (Figure 6).

### **Switch and Relay Control Inputs**

The MAX5913A/MAX5914A ON\_ inputs turn on the corresponding MOSFET switch. Driving ON\_ high turns on the switch if the corresponding RLYON is driven high, and VCC > VUVLO for more than 25.6ms. Driving RLYON\_ high immediately turns on the corresponding relay, and activates the 25.6ms delay after which the corresponding ON\_ input is active. Driving RLYON\_ low immediately turns off the switch and activates a 3.2ms delay, after which the relay is turned off. These internal delays safely allow driving ON\_ and RLYON\_ simultaneously. The relay is turned on while the switch is off so that there is no voltage across the relay contacts. The relay is turned off while the switch is off so that there is no current flowing when the relay contacts are opened (see Figure 3).

#### Input Voltage and UVLO

The MAX5913A/MAX5914A operate from a +35V to +72V supply voltage. V<sub>CC</sub> powers the MAX5913A/MAX5914A analog circuitry and is monitored continuously during startup and normal operation. The MAX5913A/MAX5914A keep all MOSFET switches and relay drivers securely off before V<sub>CC</sub> rises above V<sub>UVLO</sub>. The MAX5913A/MAX5914A turn off all MOSFET switches and relay drivers after V<sub>CC</sub> falls below V<sub>UVLO</sub> - V<sub>UVLO</sub>.H.

#### Startup

When the turn-on condition is met (see the *Input Voltage and UVLO* and *Switch and Relay Control Inputs* sections), the MAX5913A/MAX5914A slowly turn on the external MOSFET switch by charging its gate using a constant current source, IGATE (10µA typ). The gate voltage slope is determined by the total gate capacitance CGATE connected to this node. Since the output voltage follows the gate voltage, thus the output rises with a slope determined by:

$$\frac{\Delta V_{OUT}}{\Delta t} = \frac{I_{GATE}}{C_{GATE}}$$

If a capacitor load is connected to the output, the total current through the FET is:

$$I = I_{GATE} \frac{C_L}{C_{GATE}} + I_L$$

where  $C_L$  is the load capacitance and  $I_L$  is the current required by any load connected to the output during the startup phase.

If the current through the FET reaches the programmed current-limit value:

$$I_{MAX} = \frac{V_{SC}}{R_{SENSE}}$$

the internal current-limit circuitry activates and regulates this FET current to be a value, I<sub>LIM</sub>, that depends on V<sub>OUT</sub> (I<sub>FLBK</sub>) (Figure 8). See the *Current Sensing and Regulation* section. In this case, the maximum rate of change of the output is determined by:

$$\frac{\Delta V_{OUT}}{\Delta t} = \frac{I_{LIM} - I_{L}}{C_{L}}$$

The formula shows the necessity for I<sub>LIM</sub> to be larger than I<sub>L</sub> in order to allow the output voltage to rise. The foldback function is active as long as the circuit is in overcurrent condition. Should the overcurrent condition persist for a period longer than the maximum time to, the switch is latched off and GATE\_ is discharged to ground with a 1mA pulldown current.

If auto-retry is enabled, the switch turns on again after a waiting period, tOFF, which is determined by the programmed duty cycle.

After the startup, the internal charge pumps provide  $(V_{CC} + 9V)$  typical gate overdrive to fully turn on the switch. When the switch is fully on (voltage drop across the switch is  $\leq 1.5V$ ), and the switch is not in current limit, the POK signal is asserted.

## **Current Sensing and Regulation**

The MAX5913A/MAX5914A control port current with using two voltage comparators (dual-level detection) that sense the voltage drop across an external current-sense resistor. Connect CSP\_ to VCC and connect a current-sense resistor between CSP\_ and DRAIN\_. Kelvin sensing should be used as shown in Figure 7.

# V<sub>CC</sub> V<sub>GATE</sub> V<sub>UVLO</sub> +1V +1V

Figure 1. UVLO Deglitch Delay

Figure 3. Port Turn-On Delay, Relay Turn-Off Delay

The first comparator compares the sensed voltage against the Vsc threshold (typically 142.5mV). Choose a sense resistor as follows:

RSENSE = VSC / IMAX

where IMAX is the maximum current allowed through the switch.

When  $I_{MAX}$  is reached, foldback current-limit circuitry regulates the current limit as a function of  $V_{OUT}$  (Figure 8). As  $V_{OUT}$  approaches zero, the maximum voltage drop

## **Test Circuits and Timing Diagrams**

Figure 2. Open-Circuit Detector Deglitch Delay

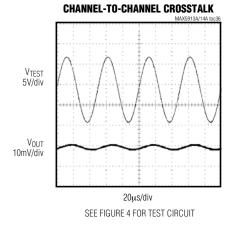

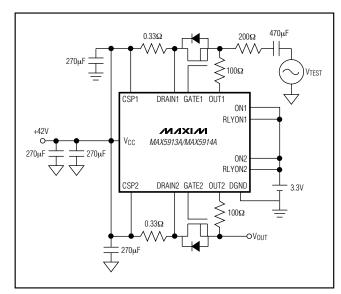

Figure 4. Channel-to-Channel Crosstalk Test Circuit

across the sense resistor is lowered to a minimum value of 48mV (typ). This foldback feature helps reduce the power dissipation in the external power FET during output overload and output short-circuit conditions. If a load with very low activation voltage is permanently connected to the output, make the minimum limit current sufficiently larger than the load current. If the load current indeed exceeds the foldback-limit value, the MAX5913A/MAX5914A are not able to power up the switch.

Figure 5. Typical Application Circuit

A second comparator with a detection threshold of  $3V_{SC}$  activates a fast 15mA pulldown of the gate. The purpose of this comparator is to rapidly discharge the gate when a momentary current peak overstresses the external FET, helping the regulation to act more rapidly.

The sense resistor is also used to detect an open-circuit or low-current condition with a typical threshold of 3mV.

#### **Open-Circuit Detection**

The MAX5913A/MAX5914A detect when a port has low current or is open circuit, and turn off the switch to that port. After the switch is turned on and the POK conditions are met, the open-circuit detector is enabled after

a 900ms delay. The open-circuit voltage threshold is set at 3mV across the current-sense resistor. Drive OCEN high to enable open-circuit detectors for all four ports. Drive OCEN low to disable the detectors. Each port has an open-circuit flag that can be read from STAT\_ outputs when the STATOUT is low. STAT\_ output high indicates that the switch is latched off due to an open-circuit condition on that port. To reset the latch pull ON\_ low and then high to restart (Table 1).

## **Output Voltage Sense and Power-OK**

The MAX5913A/MAX5914A sense the output voltage of the port at the source of the external MOSFET switch.

Figure 6. Functional Diagram

Internally the circuit compares the output voltage with  $V_{\rm CC}$  to determine when the FET is completely on. A POK condition is met when:

$$(VCC - VOUT) \le 1.5V$$

The internal circuit monitors Vout to determine the value of the foldback current when the circuit goes into current-limit conditions. The value of the current limit decreases as the output voltage decreases in order to limit the power dissipation of the FET. The nonlinear relationship between Vout and ILIM is depicted in Figure 8.

The foldback circuit is active whenever the MAX5913A/ MAX5914A are in current-limit mode after an overcurrent condition has been detected.

Connect a catch diode to analog ground and a  $100\Omega$  resistor in series with OUT\_ to limit the current during negative inductive kicks that can bring OUT\_ below the ground potential (Figure 5).

#### **Relay Drivers**

The MAX5913A/MAX5914A include on-chip relay drivers, RYLD\_, capable of sinking 100mA. When RLYON\_ goes high, the MAX5913A/MAX5914A immediately enable the relay driver, and the corresponding ON\_ switch control input is delayed 25.6ms to allow the relay to close under a zero-voltage condition. When RLYON\_ goes low, the MAX5913A/MAX5914A immediately turn off the corresponding switch, and then turn off the relay driver after a 3.2ms delay, ensuring the relay contacts open under a zero-current condition. The polarity of the MAX5913A

RLYD\_ is opposite to that of the MAX5914A. For the MAX5913A, upon the assertion of the RLYON\_ input, RLYD\_ sinks 100mA to DGND. For the MAX5914A, when RLYON\_ is high, an internal 1mA current source pulls up RLYD\_ to VDD. A 100mA catch diode is internally connected between RYLD\_ and VRLY to protect the MAX5913A/MAX5914A from inductive kicks from the relay coil. VRLY must be connected to the high-side relay supply voltage.

## Programmable Timing, RTIM

An external resistor from RTIM to DGND sets the frequency of the internal oscillator upon which to and the auto-retry times are based.

Use  $2k\Omega$  to  $40k\Omega$  resistors for R<sub>RTIM</sub>.

$t_0 = (R_{RTIM} / 2k\Omega) (6.4ms)$

If RTIM is unconnected (floating), an internal resistor sets to to a nominal 6.4ms.

#### **Auto-Retry and Programmable Duty Cycle**

The MAX5913A/MAX5914A feature auto-retry with adjustable duty cycle. Driving RTRYEN high enables the auto-retry function. When the switch encounters an overcurrent for a period greater than to, the switch is turned off, and remains off for a tOFF programmed by DC, a three-level input. After the tOFF period, the switch is automatically turned on again. When the port encounters a continuous overload or short-circuit condition, the switch turns on and off repeatedly with the on duty cycle of 1%, 2%, or 4% depending on the DC input state (Table 2). When RTRYEN is low, the auto-retry is disabled, and a fault condition at the switch turns the switch off and the switch remains latched off. Driving the corresponding ON control input low resets the latch. Pulling ON high to turn on the switch. However, the MAX5913A/MAX5914A always wait a minimum time, tOFF, before restarting the switch.

## **Logic Interface and Status Outputs**

The MAX5913A/MAX5914A logic interface controls the device functionality. All the basic control functions for the four switches are separated. ON\_ enables individual on/off control of each MOSFET (the corresponding relay must be on to turn on the switch). RLYON\_ enables individual on/off control of each relay. STAT\_ indicates POK or Port-OC (open circuit) status of each switch. The other logic pins are common to all four switches. A single FAULT output goes low when any of the four channels is latched off. Driving OCEN high enables the open-circuit detectors. Driving RTRYEN high enables the auto-retry function, RTRYEN low enables the switch latch-off function. DC, a three-level logic input, programs the duty cycle. The STATOUT input selects the signal multiplexed at STAT\_ outputs (Table 1.). Driving STATOUT high routes POK status to the STAT\_ outputs. Driving STATOUT low routes Port-OC status to the STAT\_ outputs.

# Fault Management

**UVLO and Power-OK**

The MAX5913A/MAX5914A monitor the V<sub>CC</sub> input voltage and each switch's current and voltage to determine POK, overcurrent, or Port-OC status. When V<sub>CC</sub> falls below the UVLO threshold, FAULT goes low and all four switches and relays are turned off. When the volage across the switch is less than 1.5V, the switch is fully on, and if the switch is not in current limit or open circuit, POK status is good (high).

#### **Open-Circuit Faults**

With the open-circuit detector enabled, when any switch current falls below the open-circuit detector threshold current, the open-circuit detector turns off the switch after a 25.6ms delay, FAULT goes low, and the Port-OC flag is set for that switch. To clear the switch latched-off condition, FAULT and Port-OC flags drive the corresponding ON input low.

**Table 1. Status Output**

| PORT_ CONDITION                                                           | OCEN | STATOUT | STAT_                                     |

|---------------------------------------------------------------------------|------|---------|-------------------------------------------|

| Enabled. Switch fully on and not in current limit.                        | Х    | Н       | H<br>(Power-OK_ is good)                  |

| Enabled. Switch in current limit, or V <sub>DS</sub> > 1.5V.              | Х    | Н       | L<br>(Power-OK_ is not good)              |

| Enabled. Switch current is less than OC threshold, port is latched off.   | Н    | L       | H (Port-OC_, Port current is low or zero) |

| Enabled. Switch fully on and output current is greater than OC threshold. | Н    | L       | L<br>(Port-OC_, Port current is good)     |

| Disabled.                                                                 | L    | L       | L                                         |

#### Overcurrent Faults

When an on-switch current exceeds the current-limit threshold, foldback circuitry activates and regulates the switch current. When the current limit lasts for longer than to, the switch latches off. The POK status flag is set low, and the FAULT flag is set. If auto-retry is enabled, the switch remains off for a period topper. If auto-retry is disabled, the switch remains latched off, and FAULT is low. Reset the latch and FAULT by driving corresponding ON\_low.

# **Applications Information**

Considerations for circuit design include output capacitor requirements, current-limit requirements, setting the maximum on-time in current limit, and choosing a suitable MOSFET and on-time duty cycle in auto-retry.

## **Output Capacitor Requirements**

The load capacitor requirements should be determined first, as this affects the required startup.

## Current-Limit Requirements (Choosing RSENSE)

The current limit should be set to at least 20% higher than the expected full load current. If current limit is also used to control startup current, then set this limit high enough so that the output voltage can rise and settle before to elapses (see the *Setting to (Choosing RRTIM)* section).

#### Setting to (Choosing RRTIM)

Choose the to time by connecting a  $2k\Omega$  to  $40k\Omega$  resistor from RTIM to DGND. The minimum 6.4ms to is set with  $R_{RTIM} = 2k\Omega$ . The maximum 128ms to is set with  $R_{RTIM} = 40k\Omega$  set according to the following equation:

$$t_0 = (R_{RTIM} / 2k\Omega) (6.4ms)$$

to should be chosen appropriately, depending on the startup condition. There are two cases:

1) For startup without current limit, when:

$$I = I_{GATE} \frac{C_L}{C_{GATE}} + I_L < \frac{V_{SC}}{R_{SENSE}}$$

The startup current does not reach the maximum current-limit threshold and to will not activate during startup condition. In this case, set to to a small

value, but large enough to allow the switch to remain on during large output load-current transients. The smaller the to, the faster the MAX5913A/MAX5914A turn off the external FET in case of output overload or short-circuit condition.

2) For startup with current limit, when:

$$I = I_{GATE} \left( \frac{C_L}{C_{GATE}} + I_L \right) \ge \frac{V_{SC}}{R_{SENSE}}$$

which is expected when:

$$\frac{C_L}{C_{GATE}}$$

is large, to must be set to be long enough to allow the output voltage to rise and settle before to elapses. In this case, to must satisfy the following equation:

$$t_{O} = C_{L} \frac{18}{\frac{2}{3} I_{MAX} - I_{L}} + C_{L} \frac{V_{CC} - 18V}{I_{MAX} - I_{L}}$$

where VCC is the input voltage and given that IL < ILIM.

#### **Choosing Power MOSFET**

The FET must withstand a short-circuit condition where its power dissipation is PDISS = VCC × ILIM. The FET must have sufficient thermal capacitance to prevent thermal heating damage during the to time.

#### **Choose Duty Cycle (Setting DC)**

The duty cycle can be adjusted to allow time for heat to dissipate between to cycles, allowing use of smaller MOSFETs with lower thermal capacitance. For smaller duty cycle, a smaller FET is sufficient. See Table 2 for setting the duty cycle.

The auto-retry off-time should not be too long to keep the system wait time during retry period to a reasonable value. For example, when to is set to 128ms and duty cycle is set to 1%, the retry time is  $99 \times 128ms = 12.7s$ .

#### **Application Circuits**

In a typical LAN system there are two ways to deliver power over the LAN cable. Power can be supplied to the unused cable pairs, or power can be supplied over the signal pairs (Figures 9 and 10).

Figure 7. Recommended Layout for Kelvin-Sensing Current Through Sense Resistor

Figure 8. Foldback Current-Limit Response

# **Table 2. Duty Programming Cycle**

| DC   | toff                | DUTY CYCLE |

|------|---------------------|------------|

| 0    | 99 × t <sub>O</sub> | 1%         |

| 1    | 49 × t <sub>O</sub> | 2%         |

| Open | 24 × t <sub>O</sub> | 4%         |

Figure 9. Power Sent Over Signal Pairs

Figure 10. Power Sent Over Spare Pairs

**Chip Information**

TRANSISTOR COUNT: 14,622

PROCESS: BiCMOS

# **Typical Operating Circuit**

# Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.