## **General Description**

The MAX1807/MAX1808 monitor up to five supply rails for an overvoltage condition and provide a latched output when any one of the five supplies exceeds the trip thresholds. The latched output drives an external Pchannel load switch to remove power when an overvoltage condition is detected. The latch is reset when a logic low is input to ON or the power supply is cycled.

The MAX1807 provides a 28V open-drain fault output that can be used to trigger an alert, trip a resetable fuse, or for other purposes. The MAX1808 includes a low-battery comparator with hysteresis to drive the DP output high, turning off the external P-channel switch when the input voltage is too low.

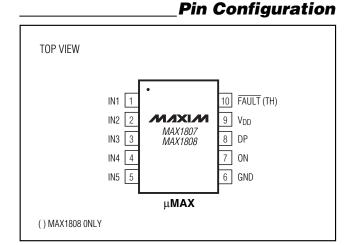

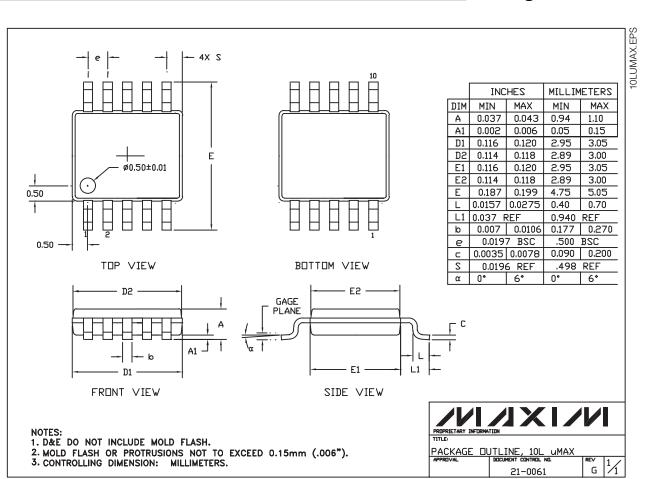

The MAX1807/MAX1808 are available in a miniature 10pin µMAX package.

#### **Applications**

Notebook Computers **Power-Supply Modules**

Multi-Output Power Supplies

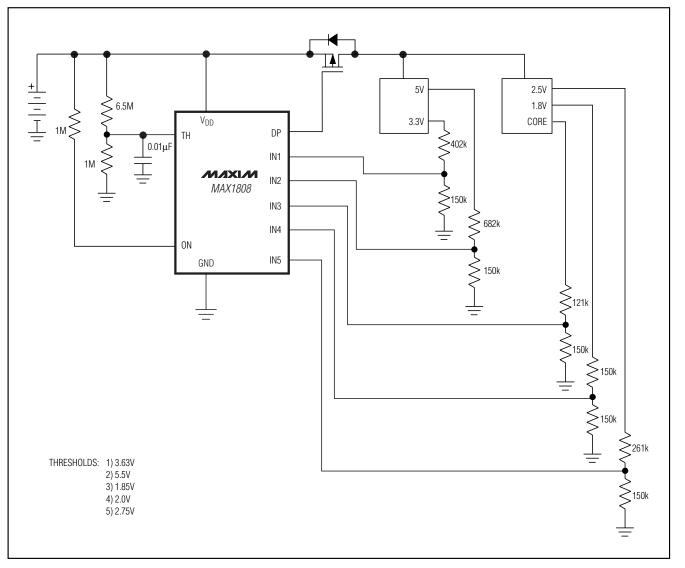

#### Pin Configuration and Typical Operating Circuit appear at end of data sheet.

#### VDD 2 5V 0N INTERNAL POWER-ON 1V REF REF OK SUPPLY PMOS RESET POWER DP (60µs) ΤH DRIVER (MAX1808) IN1 0 IN2 FAULT (MAX1807) IN3 IN4 **MIXIM** GND MAX1807 IN5 MAX1808

#### M/X/M

Maxim Integrated Products 1

♦ 3% Accurate Comparator with 10% Hysteresis for 28V Open-Drain N-Channel Output (MAX1807)

Features

# **Ordering Information**

#### **PIN-PACKAGE** PART TEMP. RANGE MAX1807EUB -40°C to +85°C 10 µMAX MAX1808EUB -40°C to +85°C 10 µMAX

Five 3% Accurate Overvoltage Comparators

Series PFET Gate Driver with VGS Limiter

21µA Quiescent Supply Current

♦ 4.4V to 28V Operating Voltage Range

Low-Battery Detection (MAX1808)

Small 10-Pin µMAX Package

4µA Shutdown Current

For price, delivery, and to place orders, please contact Maxim Distribution at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

# **Functional Diagram**

# MAX1807/MAX1808

## **ABSOLUTE MAXIMUM RATINGS**

| IN1_, TH to GND                 | 0.3V to +6V      |

|---------------------------------|------------------|

| ON, VDD, FAULT to GND           |                  |

| DP to GND                       |                  |

| Continuous Power Dissipation    |                  |

| 10-Pin uMAX (derate 5.6mW/°C at | oove +70°C)448mW |

| Operating Temperature Range       | 40°C to +85°C  |

|-----------------------------------|----------------|

| Junction Temperature              | +150°C         |

| Storage Temperature Range         | 65°C to +150°C |

| Lead Temperature (soldering, 10s) | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = V_{ON} = 15V, V_{IN1} - V_{IN5} = 0.5V, V_{TH} = 2.0V, C_{DP} = 5nF, FAULT = open, T_A = 0°C to +85°C, unless otherwise noted.)$

| PARAMETER SYMBOL                                  |   | CONDITIONS                                                                                            | MIN   | ТҮР  | MAX   | UNITS |

|---------------------------------------------------|---|-------------------------------------------------------------------------------------------------------|-------|------|-------|-------|

| GENERAL                                           | • |                                                                                                       |       |      |       |       |

| V <sub>DD</sub> Input Voltage Range               |   | DP and FAULT in correct state (Table 1)                                                               | 2     |      | 28    | V     |

| V <sub>DD</sub> Operating Voltage Range           |   |                                                                                                       | 4.4   |      | 28    | V     |

| V <sub>DD</sub> Undervoltage Lockout<br>Threshold |   | Rising trip level, typical 2% hysteresis; when $V_{DD}$ is below this level, DP = Hi and FAULT = Hi-Z | 2     | 2.7  | 4.0   | V     |

| Supply Current                                    |   | $V_{TH} = 2V \text{ or } 0.5V$                                                                        |       | 21   | 45    | μΑ    |

| Shutdown Current                                  |   | $V_{DD} = 15V$ , $V_{ON} = GND$ , $V_{IN1} - V_{IN5} = V_{TH} = GND$                                  |       | 4    | 8.5   | μΑ    |

| COMPARATORS (IN1-IN5, TH)                         | • |                                                                                                       |       |      |       |       |

| IN1–IN5 Input Trip Level                          |   | Rising edge, typical 1% hysteresis,<br>V <sub>DD</sub> = 4.4V to 28V                                  | 0.97  | 1    | 1.03  | V     |

| TH Input Trip Level, Falling                      |   | V <sub>DD</sub> = 4.4V to 28V (MAX1808 only)                                                          | 0.97  | 1    | 1.03  | V     |

| TH Input Trip Level, Rising                       |   | V <sub>DD</sub> = 4.4V to 28V (MAX1808 only)                                                          | 1.045 | 1.1  | 1.155 | V     |

| IN1–IN5 Propagation Delay                         |   | IN1–IN5 rising, 10mV overdrive, $V_{DD} = 4.4V$                                                       |       | 40   |       | μs    |

| TH Propagation Delay                              |   | TH rising, 10mV overdrive, V <sub>DD</sub> = 4.4V<br>(MAX1808 only)                                   |       | 11   |       |       |

|                                                   |   | TH falling, 10mV overdrive, V <sub>DD</sub> = 4.4V<br>(MAX1808 only)                                  | 40    |      |       | μs    |

| IN1–IN5 Input Leakage Current                     |   | V <sub>IN</sub> = 1.5V                                                                                |       | 0.5  | 50    | nA    |

| TH Input Leakage Current                          |   | V <sub>TH</sub> = 1.5V (MAX1808 only)                                                                 |       | 0.5  | 50    | nA    |

| ON Input High Logic Level                         |   | $V_{DD} = 4.4 V$ to 28V                                                                               | 1.6   |      |       | V     |

| ON Input Low Logic Level                          |   | $V_{DD} = 4.4 V$ to 28V                                                                               |       |      | 0.5   | V     |

| ON Input Leakage Current                          |   | $V_{ON} = 5V$                                                                                         |       | 0.03 | 1.2   | ۵     |

|                                                   |   | $V_{ON} = 28V$                                                                                        |       |      | 10    | μA    |

| FAULT Output High Leakage<br>Current              |   | VFAULT = 28V (MAX1807 only) 0.01 2                                                                    |       | 2    | μΑ    |       |

| FAULT Output Low Voltage                          |   | I <sub>SINK</sub> = 4mA (MAX1807 only)                                                                |       |      | 0.4   | V     |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = V_{ON} = 15V, V_{IN1} - V_{IN5} = 0.5V, V_{TH} = 2.0V, C_{DP} = 5nF, FAULT = open, T_A = 0°C to +85°C, unless otherwise noted.)$

| PARAMETER                            | SYMBOL | CONDITIONS                                      |                               |     | ТҮР | МАХ  | UNITS |

|--------------------------------------|--------|-------------------------------------------------|-------------------------------|-----|-----|------|-------|

| DP Source Current                    |        | $V_{ON} = V_{DD}$ ,                             | $V_{DP} = V_{DD} - 0.4V$      | 1   | 50  |      | μA    |

| (PMOS Turn-Off)                      |        | $V_{IN1} = 1.5V$                                | $V_{DP} = V_{DD} - 2V$        | 5   | 20  |      | mA    |

| DP Sink Current (PMOS Turn-On)       |        | $V_{DP} = V_{DD} - 5V$                          | 4                             | 50  |     | mA   |       |

| DP Pullup Current (PMOS Off)         |        | $V_{DP} = V_{DD} - 2V, V_{O}$ in shutdown state |                               | 25  |     | μΑ   |       |

| DP Turn-On Clamp Voltage             |        | $V_{ON} = V_{DD}$ ,                             | V <sub>DD</sub> = 8.5V to 28V | 7.5 | 9.5 | 11.5 | V     |

| (V <sub>DD</sub> - V <sub>DP</sub> ) |        | $I_{DPSINK} = 10 \mu A$                         | $V_{DD} = 4.4 V$              | 3.4 | 4.1 | 4.4  | V     |

## **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = V_{ON} = 15V, V_{IN1} - V_{IN5} = 0.5V, V_{TH} = 2.0V, C_{DP} = 5nF, FAULT = open, T_A = -40^{\circ}C to +85^{\circ}C$ , unless otherwise noted.) (Note 1)

| PARAMETER                                         | SYMBOL | CONDITIONS                                                                                                         |                                       |       | ТҮР | МАХ   | UNITS |

|---------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------|-----|-------|-------|

| GENERAL                                           |        |                                                                                                                    |                                       |       |     |       |       |

| V <sub>DD</sub> Input Voltage Range               |        | DP and FAULT in correct state (Table 1)                                                                            |                                       |       |     | 28    | V     |

| V <sub>DD</sub> Operating Voltage Range           |        |                                                                                                                    |                                       | 4.4   |     | 28    | V     |

| V <sub>DD</sub> Undervoltage Lockout<br>Threshold |        | Rising trip level, typical 2% hysteresis; when<br>V <sub>DD</sub> is below this level, DP = Hi and FAULT =<br>Hi-Z |                                       |       |     | 4.0   | V     |

| Supply Current                                    |        | $V_{TH} = 2V \text{ or } 0.5V$                                                                                     |                                       |       |     | 45    | μΑ    |

| Shutdown Current                                  |        | $V_{DD} = 15V, V_{ON} = 6$                                                                                         | $3ND, V_{IN1}-V_{IN5} = V_{TH} = GND$ |       |     | 8.5   | μΑ    |

| COMPARATORS (IN1-IN5, TH)                         |        |                                                                                                                    |                                       |       |     |       |       |

| IN1–IN5 Input Trip Level                          |        | Rising edge, typica                                                                                                | al 1% hysteresis                      | 0.95  |     | 1.05  | V     |

| TH Input Trip Level, Falling                      |        | $V_{DD} = 4.4 V \text{ to } 28 V$                                                                                  | (MAX1808 only)                        | 0.95  |     | 1.05  | V     |

| TH Input Trip Level, Rising                       |        | $V_{DD} = 4.4V$ to 28V                                                                                             | (MAX1808 only)                        | 1.045 |     | 1.155 | V     |

| IN1–IN5 Input Leakage Current                     |        | $V_{IN} = 1.5V$                                                                                                    |                                       |       |     | 50    | nA    |

| TH Input Leakage Current                          |        | V <sub>TH</sub> = 1.5V (MAX1808 only)                                                                              |                                       |       |     | 50    | nA    |

| ON Input High Logic Level                         |        | $V_{DD} = 4.4 V$ to 28V                                                                                            |                                       | 1.8   |     |       | V     |

| ON Input Low Logic Level                          |        | V <sub>DD</sub> = 4.4V to 28V                                                                                      |                                       |       |     | 0.4   | V     |

|                                                   |        | $V_{ON} = 5V$                                                                                                      |                                       |       |     | 1.2   | ۵     |

| ON Input Leakage Current                          |        | $V_{ON} = 28V$                                                                                                     |                                       |       | 10  | μA    |       |

| FAULT Output High Leakage<br>Current              |        | VFAULT = 28V (MAX1807 only)                                                                                        |                                       |       |     | 2     | μΑ    |

| FAULT Output Low Voltage                          |        | I <sub>SINK</sub> = 4mA (MAX1807 only)                                                                             |                                       |       |     | 0.4   | V     |

| DP Source Current                                 |        | $V_{ON} = V_{DD},$ $V_{DP} = V_{DD} - 0.4V$                                                                        |                                       | 1     |     |       | μΑ    |

| (PMOS Turn-Off)                                   |        | $V_{IN1} = 1.5V$                                                                                                   | $V_{DP} = V_{DD} - 2V$                | 4     |     |       | mA    |

| DP Sink Current (PMOS Turn-On)                    |        | V <sub>DP</sub> = V <sub>DD</sub> - 5V                                                                             |                                       | 2     |     |       | mA    |

| DP Turn-On Clamp Voltage                          |        | $V_{ON} = V_{DD}$ , $V_{DD} = 8.5V$ to 28V                                                                         |                                       | 7.5   |     | 11.5  | V     |

|                                                   |        | $I_{\text{DPSINK}} = 10 \mu A$                                                                                     | $V_{DD} = 4.4V$                       | 3.4   |     | 4.4   | v     |

**Note 1:** Specifications to -40°C are guaranteed by design, not production tested.

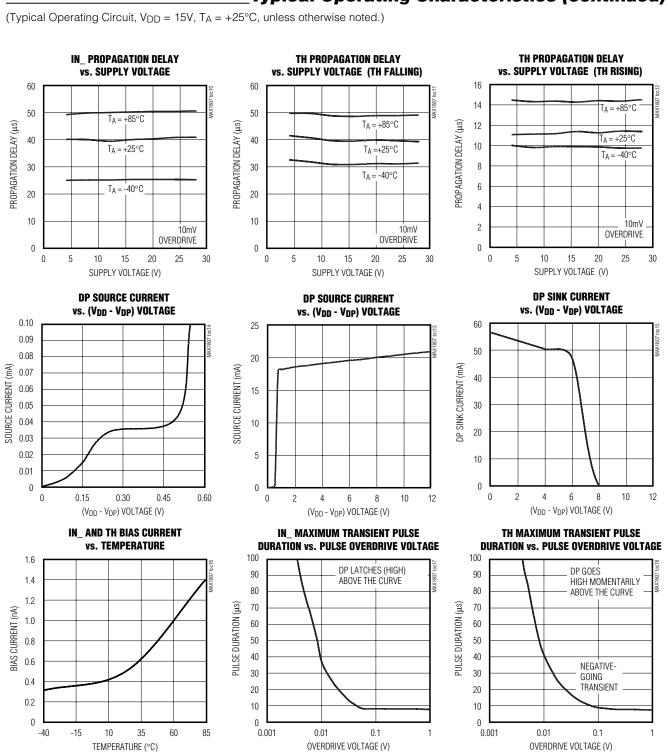

(Typical Operating Circuit, V<sub>DD</sub> = 15V, T<sub>A</sub> = +25°C, unless otherwise noted.)

#### SHUTDOWN SUPPLY CURRENT FAULT OUTPUT VOLTAGE LOW vs. SUPPLY VOLTAGE **SUPPLY CURRENT vs. SUPPLY VOLTAGE** vs. FAULT OUTPUT SINK CURRENT 5.0 25 700 $T_A=+85^\circ C$ $T_A = +85^{\circ}C$ Γ<sub>Δ</sub> = +85°Ċ 4.5 SHUTDOWN SUPPLY CURRENT (µA) 600 4.0 20 $T_A = +25^{\circ}C$ ŧ SUPPLY CURRENT (JuA) 3.5 OUTPUT VOLTAGE (mV) 500 $T_A = +25^{\circ}C$ $T_{A} = +25$ -40°C TA 3.0 15 400 $T_A = -40^{\circ}C$ 2.5 300 2.0 10 1.5 200 -40°C T<sub>A</sub> = 1.0 5 100 0.5 0 0 0 0 10 30 0 5 10 15 25 30 5 15 20 25 20 0 8 12 4 16 SUPPLY VOLTAGE (V) SUPPLY VOLTAGE (V) FAULT OUTPUT SINK CURRENT (mA) NORMALIZED IN TRIP THRESHOLD NORMALIZED IN TRIP THRESHOLD NORMALIZED TH TRIP THRESHOLD **ERROR vs. TEMPERATURE** ERROR vs. SUPPLY VOLTAGE (TH FALLING) **ERROR vs. SUPPLY VOLTAGE** 0.25 0.3 0.02 0.20 0.2 0.15 0.01 0.01 10.0-10.0-TRIP THRESHOLD ERROR (%) **FRIP THRESHOLD ERROR (%)** 0.1 0.10 28V 0.05 0 $T_A = +25^{\circ}C$ $T_A = +25^{\circ}C$ $T_A = +85^{\circ}C$ 0 0 15V -0.1 -0.05 4.4V -0.10 - -40°C -0.2 -0.15 $T_A = -40^{\circ}C$ -0.3 -0.20 T₄ = +85°C -0.25 -0.4 -0.02 30 100 0 10 20 0 5 10 15 20 25 -50 0 50 SUPPLY VOLTAGE (V) TEMPERATURE (°C) SUPPLY VOLTAGE (V) **NORMALIZED TH TRIP THRESHOLD** NORMALIZED TH TRIP THRESHOLD NORMALIZED TH TRIP THRESHOLD **ERROR vs. TEMPERATURE (TH FALLING) ERROR vs. SUPPLY VOLTAGE (TH RISING) ERROR vs. TEMPERATURE (TH RISING)** 0.15 0.3 0.20 0.15 0.10 0.2 28V RIP THRESHOLD ERROR (%) **TRIP THRESHOLD ERROR (%)** THRESHOLD ERROR (%) 0.10 0.05 0.1 0.05 28V $T_A = +25^{\circ}C$ 0 0 0 $T_A = -40^\circ C$ -0.05 -0.05 -0.1 ≝ -0.10 $T_A = +85^{\circ}C$ 4.4V -0.10 -0.2 -0 15 -0.15 -0.3 -0.20 -50 0 50 100 0 15 20 25 30 -50 0 50 5 10

SUPPLY VOLTAGE (V)

**Typical Operating Characteristics**

20

30

100

TEMPERATURE (°C)

M/IXI/N

MAX1807/MAX1808

4

TEMPERATURE (°C)

\_\_\_\_\_Typical Operating Characteristics (continued)

MAX1807/MAX1808

# **Pin Description**

| PIN | NAME            | FUNCTION                                                                                                                                                                                                                                                                                       |

|-----|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1–5 | IN1–IN5         | Overvoltage Detect Comparator Input. When any input exceeds 1V, the fault latch is set. Connect unused inputs to GND.                                                                                                                                                                          |

| 6   | GND             | Ground                                                                                                                                                                                                                                                                                         |

| 7   | ON              | Logic Input. ON turns on internal reference when high. Logic trip level is approximately 1.2V with 15% hysteresis. When ON is low, the fault latch is reset. ON can be connected directly to V <sub>DD</sub> at the expense of supply current.                                                 |

| 8   | DP              | External P-Channel MOSFET Gate Driver Output. The output high level is V <sub>DD</sub> . The output low level is V <sub>DD</sub> - 9.5V or GND, whichever is higher. This output is latched high when an overvoltage condition is detected.                                                    |

| 9   | V <sub>DD</sub> | Analog Supply Input. Use an external RC filter to eliminate excessive switching noise on $V_{DD}$ . When $V_{DD}$ is less than 2.7V, the fault latch is reset.                                                                                                                                 |

|     | FAULT           | Signal Overvoltage Condition Output. This open-drain N-channel output is latched low when an over-<br>voltage condition is detected. <b>(MAX1807 only)</b>                                                                                                                                     |

| 10  | ТН              | Input Monitor Comparator. When TH is below 1V, DP goes high to turn off the external P-channel switch. When TH exceeds 1.1V, DP goes low if there is no fault. Between 1V and 1.1V is the hysteresis band where the output state of the TH comparator remains unchanged. <b>(MAX1808 only)</b> |

# **Detailed Description**

The MAX1807/MAX1808 provide overvoltage protection for systems with multiple supply rails. Very low output voltage supplies can have an overvoltage before the power-supply controller has sufficient supply voltage to activate protection circuitry. The MAX1807/MAX1808 offer a system-wide approach to effectively protect the loads and prevent catastrophic events.

The MAX1807/MAX1808 are powered directly by the main system input supply. A low output voltage from DP activates a P-channel switch to supply power to the rest of the system. As the rest of the system supplies come up, the MAX1807/MAX1808 monitor each of them for overvoltage conditions and safely disconnect the input from the rest of the system if any supply malfunctions occur due to a shorted MOSFET, shorted copper trace, or malfunctioning supply. Built-in overvoltage detectors in individual power supplies provide redundancy.

The MAX1807/MAX1808 drive the main P-channel load switch that powers the system. The driver includes active clamping to safely drive a 12V P-channel MOS-FET gate. If overvoltage is detected, the P-channel load switch is turned off and the state is latched. The internal fault latch resets when V<sub>DD</sub> is less than 2.7V (power cycled) or ON is pulled low (manual reset). When ON is logic low, the P-channel switch is turned off (Table 1).

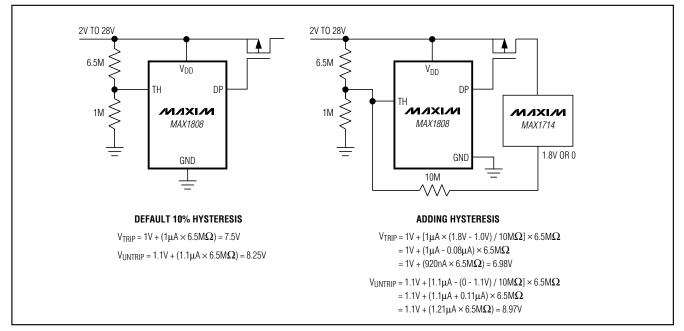

The MAX1808 has a TH input that turns off the P-channel switch if TH goes below 1V without affecting the fault latch. TH output is designed for low-battery detection. The comparator has 10% hysteresis, allowing the battery voltage to rise when the load is removed without reenabling the external P-channel switch.

The MAX1807 has a fault alert output (FAULT) instead of the TH input. FAULT is an open-drain output, rated for up to 28V, that directly reflects the state of the internal fault latch.

#### **IN1-IN5 Overvoltage Comparators**

The overvoltage comparators have a 1V trip level. The fault latch is set if any one of the five overvoltage comparators goes above the trip level. A limited input bandwidth ensures that small glitches will not trigger an overvoltage event (see IN\_ Maximum Transient Pulse Duration vs. Pulse Overdrive Voltage in the *Typical Operating Characteristics*).

#### **DP PFET Driver Output**

The MAX1807/MAX1808 have a totem driver (DP) with an active clamp that simplifies driving the external P-channel load switch. The -9.5V V<sub>gs</sub> clamp eliminates complexity in circuits where V<sub>DD</sub> exceeds the P-channel FET's maximum gate voltage. DP goes high and turns off the P-channel switch during undervoltage lockout, when ON is low, when TH is less than 1V, or if an overvoltage fault occurs.

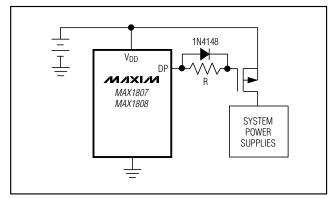

The DP driver can sink and source significant current and achieves fast turn-on and turn-off times even with large P-channel switches. Adding a resistor in series with DP can increase turn-on and turn-off times. To slow the turn-on time without affecting the turn-off time, add a diode in parallel with the resistor (Figure 1). The turnon time will be the product of the series resistor and the gate-to-source capacitance of the P-channel FET:

$$t_{ON} = C_{gs} \times R$$

The turn-off time will be the product of the gate-tosource capacitance of the P-channel FET and the DP source current of the MAX1807/MAX1808 (see DP Source Current vs. (V<sub>DD</sub> - V<sub>DP</sub>) Voltage in the *Typical Operating Characteristics*).

For very slow turn-off times, adding an external capacitor between the gate and the source of the P-channel FET eliminates the need for resistors with extremely high values.

**TH Input Comparator (MAX1808 Only)** TH input comparator can disconnect the load from the battery when the battery voltage is too low. The falling trip level is 1V, and the rising trip level is 1.1V. The 100mV hysteresis can prevent the load switch from turning on when the battery voltage rises as the load is disconnected from the battery. The comparator has a limited bandwidth to ensure that small transients will not shut down the system supplies.

Increase TH hysteresis by adding a resistor from TH to one of the voltage rails disconnected by the P-channel load switch, such as the 1.8V supply (Figure 2). Use one of the lower voltage supplies to eliminate the necessity of extremely large resistors to obtain reasonable hysteresis. When the MAX1714 is on, the trip threshold is lower than when the MAX1714 is off, pro-

Figure 1. External FET Gate Control

Figure 2. Adding Hysteresis

| V <sub>DD</sub>     | ON | тн    | IN1–IN5 | DP        | FAULT     | COMMENT                                         |

|---------------------|----|-------|---------|-----------|-----------|-------------------------------------------------|

| <2V                 | Х  | Х     | Х       | Undefined | Undefined |                                                 |

| $2 < V_{DD} < 4.0V$ | Х  | Х     | Х       | HI        | Hi-Z      |                                                 |

| >4.0V               | 0  | Х     | Х       | HI        | Hi-Z      |                                                 |

| >4.0V               | 1  | <1V   | Х       | HI        |           | Note that TH has 0.1V hysteresis (MAX1808 only) |

| >4.0V               | 1  | >1.1V | All <1V | LO        | Hi-Z      | Only condition for PFET to be turned on         |

| >4.0V               | 1  | >1.1V | Any >1V | HI        | LO        |                                                 |

### Table 1. MAX1807/MAX1808 State Table

viding additional hysteresis. Turning off the chosen supply will change the undervoltage trip levels.

#### FAULT Open-Drain N-Channel Flag Output (MAX1807<u>Only</u>)

The MAX1807 has an open-drain N-channel FAULT output. The FAULT output directly reflects the state of the internal fault latch, going low when an overvoltage event occurs. The FAULT output can be used to signal the system power-management microcontroller, trip a resetable fuse, drive an external high-side driver, or for other purposes.

#### Undervoltage Lockout and Power-On Reset (P<u>OR)</u> Period

Undervoltage lockout holds DP high and FAULT in high impedance until V<sub>DD</sub> exceeds the V<sub>DD</sub> undervoltage lockout threshold. When V<sub>DD</sub> exceeds the undervoltage threshold, the DP and FAULT outputs remain unchanged during the power-on reset period ( $60\mu$ s), allowing the reference and comparators to settle. Normal operation resumes after the POR period.

# **Chip Information**

TRANSISTOR COUNT: 955 PROCESS: BICMOS

# **Typical Operating Circuit**

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

© 2000 Maxim Integrated Products Printed USA

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 **MAXIM** is a registered trademark of Maxim Integrated Products.

**Package Information**