## L64777 DVB QAM Modulator

## **Technical Manual**

**June 2000**

Order Number I14031.A

This document contains proprietary information of LSI Logic Corporation. The information contained herein is not to be used by or disclosed to third parties without the express written permission of an officer of LSI Logic Corporation.

Document DB14-000121-01, First Edition, June 2000.

This document describes revision A of the LSI Logic Corporation L64777 DVB QAM Modulator and will remain the official reference source for all revisions of this product until rescinded by an update.

To receive product literature, visit us at http://www.lsilogic.com.

LSI Logic Corporation reserves the right to make changes to any products herein at any time without notice. LSI Logic does not assume any responsibility or liability arising out of the application or use of any product described herein, except as expressly agreed to in writing by LSI Logic; nor does the purchase or use of a product from LSI Logic convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property rights of LSI Logic or third parties.

Copyright © 2000 by LSI Logic Corporation. All rights reserved.

#### TRADEMARK ACKNOWLEDGMENT

The LSI Logic logo design, G10, and the G10 logo design, are trademarks or registered trademarks of LSI Logic Corporation. All other brand and product names may be trademarks of their respective companies.

## **Preface**

This book is the primary reference and technical manual for the L64777 DVB QAM Modulator. It contains a complete functional description for the L64777 and includes complete physical and electrical specifications for the L64777.

#### **Audience**

This document assumes that you have some familiarity with digital video broadcasting, QAM modulators, and related support devices. The people who benefit from this book are:

- Engineers and managers who are evaluating the modulator for possible use in a system

- Engineers who are designing the modulator into a system

#### Organization

This document has the following chapters and appendixes:

- Chapter 1, Introduction, introduces the L64777 DVB QAM Modulator.

- Chapter 2, Modulator Architecture, describes the functional components of the L64777.

- Chapter 3, Interfaces, describes the L64777 interfaces.

- Chapter 4, Register Descriptions, describes the registers used to configure and monitor the L64777.

- Chapter 5, Signals, presents the signal definitions for the L64777.

Preface iii

- Chapter 6, Specifications, presents the electrical and timing specifications for the L64777. It also presents the pinout and packaging information.

- Appendix A, Programming the L64777 in Serial Host Interface

Mode, discusses how to program the L64777 internal registers and

data tables in serial host interface mode.

- Appendix B, PLL Divider Settings and L64724/34 Connection, lists the PLL divider settings for typical applications. It also describes the L64777 connection to the L64724.

- Appendix C, Monitoring Device Internal Signals, describes how to program test register (14) for monitoring of device internal signals.

#### **Related Publications**

Digital Broadcasting Systems for Television Sound and Data Services: Framing Structure, Channel Coding and Modulation Cable Systems ETS 300 429, September 1996.

Generic Coding of Moving Pictures and Associated Audio, ISO/IEC 13818-1, MPEG2 Systems, November 1994.

G10<sup>®</sup>-p CW900100 10-Bit Direct Digital Synthesis Digital-to-Analog Converter, Preliminary Datasheet, LSI Logic, September 1998.

L64724 Satellite Receiver Technical Manual, LSI Logic, April 2000, order number 114030.

#### Conventions Used in This Manual

The word *assert* means to drive a signal true or active. The word *deassert* means to drive a signal false or inactive.

Hexadecimal numbers are indicated by the prefix "0x" —for example, 0x32CF. Binary numbers are indicated by the prefix "0b" —for example, 0b0011.0010.1100.1111.

## **Contents**

| Chapter 1 | Introduction |          |                                   |      |  |  |  |

|-----------|--------------|----------|-----------------------------------|------|--|--|--|

| •         | 1.1          | Overvi   | ew                                | 1-1  |  |  |  |

|           | 1.2          | Opera    | ting Environment                  | 1-2  |  |  |  |

| Chapter 2 | Modu         | ulator A | rchitecture                       |      |  |  |  |

| -         | 2.1          | Introdu  | uction                            | 2-2  |  |  |  |

|           | 2.2          | PLL M    | odes                              | 2-4  |  |  |  |

|           |              | 2.2.1    | PLL Mode 1                        | 2-4  |  |  |  |

|           |              | 2.2.2    | PLL Mode 2                        | 2-5  |  |  |  |

|           | 2.3          | I/O      |                                   | 2-6  |  |  |  |

|           |              | 2.3.1    | Input                             | 2-6  |  |  |  |

|           |              | 2.3.2    | Output Signals                    | 2-6  |  |  |  |

|           |              | 2.3.3    | Control Interface                 | 2-8  |  |  |  |

|           |              | 2.3.4    | Serial Microprocessor Interface   | 2-10 |  |  |  |

|           | 2.4          | Input S  | Synchronization                   | 2-10 |  |  |  |

|           |              | 2.4.1    | Sync Acquisition Phase            | 2-13 |  |  |  |

|           |              | 2.4.2    | Sync Tracking Phase               | 2-14 |  |  |  |

|           | 2.5          | FIFO (   | Clock Conversion                  | 2-16 |  |  |  |

|           | 2.6          | Sync/E   | F Reinsertion Unit                | 2-17 |  |  |  |

|           |              | 2.6.1    | Sync Insertion Mode               | 2-18 |  |  |  |

|           |              | 2.6.2    | Error Flag Insertion              | 2-18 |  |  |  |

|           |              | 2.6.3    | Energy Dispersal (Scrambler) Unit | 2-18 |  |  |  |

|           | 2.7          | Reed-    | Solomon Encoder                   | 2-20 |  |  |  |

|           |              | 2.7.1    | Forward Error Correction (FEC)    | 2-21 |  |  |  |

|           |              | 2.7.2    | Error Handling and Correction     | 2-22 |  |  |  |

|           | 2.8          | Convo    | lutional Interleaver              | 2-23 |  |  |  |

|           | 2.9          | Bytes    | to M-tuples Converter             | 2-24 |  |  |  |

|           | 2.10         | Differe  | ntial Encoder and QAM Mapping     | 2-26 |  |  |  |

|           | 2.11         | Square   | e Root Nyquist Filter             | 2-27 |  |  |  |

Contents

|           |        | 2.11.1    | Filter Setup Procedure                  | 2-29 |

|-----------|--------|-----------|-----------------------------------------|------|

|           |        | 2.11.2    | Example                                 | 2-30 |

|           |        | 2.11.3    | Default Filter Characteristics          | 2-34 |

|           | 2.12   | Global    | Control and PLL Module                  | 2-34 |

|           |        | 2.12.1    | Numerically Controlled Oscillator (NCO) | 2-35 |

|           |        | 2.12.2    | Acquisition Phase Using the Frequency   |      |

|           |        |           | Measurement Unit                        | 2-36 |

|           |        | 2.12.3    | Autoacquisition Mode                    | 2-38 |

|           |        | 2.12.4    | Regulation Phase                        | 2-39 |

|           | 2.13   | Interpol  | ator                                    | 2-39 |

|           | 2.14   | Serial N  | Aicroprocessor Interface                | 2-40 |

|           | 2.15   | Test Un   | it                                      | 2-41 |

| Chapter 3 | Interf | aces      |                                         |      |

|           | 3.1    | Transpo   | ort Interface                           | 3-1  |

|           |        | 3.1.1     | Synchronization                         | 3-1  |

|           |        | 3.1.2     | Synchronization Methods                 | 3-2  |

|           |        | 3.1.3     | Transport Error Indicator Handling      | 3-2  |

|           | 3.2    | Serial C  | Control Interface                       | 3-2  |

|           | 3.3    | Analog    | Output Interface                        | 3-3  |

|           | 3.4    | Digital ( | Output Interface                        | 3-6  |

| Chapter 4 | Regis  | ster Desc | criptions                               |      |

|           | 4.1    | Group 2   | 2 General-Purpose Registers             | 4-1  |

|           |        | 4.1.1     | Register 0                              | 4-4  |

|           |        | 4.1.2     | Register 1                              | 4-4  |

|           |        | 4.1.3     | Register 2                              | 4-5  |

|           |        | 4.1.4     | Register 3                              | 4-5  |

|           |        | 4.1.5     | Register 4                              | 4-6  |

|           |        | 4.1.6     | Register 5                              | 4-6  |

|           |        | 4.1.7     | Register 6                              | 4-7  |

|           |        | 4.1.8     | Registers 7 and 8                       | 4-8  |

|           |        | 4.1.9     | Registers 9 and 10                      | 4-8  |

|           |        | 4.1.10    | Register 11                             | 4-9  |

|           | 4.2    | NCO-R     | elated Registers                        | 4-10 |

|           |        | 4.2.1     | Register 12                             | 4-10 |

|           |        | 422       | Register 13                             | 4-11 |

vi Contents

|           |      | 4.2.3      | Register 14                          | 4-12 |

|-----------|------|------------|--------------------------------------|------|

|           |      | 4.2.4      | Register 15                          | 4-13 |

|           |      | 4.2.5      | Registers 16, 17, and 18             | 4-13 |

|           |      | 4.2.6      | Registers 19 and 20                  | 4-13 |

|           |      | 4.2.7      | Registers 21 and 22                  | 4-14 |

|           |      | 4.2.8      | Registers 23 and 24                  | 4-14 |

|           |      | 4.2.9      | Register 25                          | 4-14 |

|           |      | 4.2.10     | Registers 26, 27, and 28             | 4-14 |

|           |      | 4.2.11     | Registers 29, 30, and 31             | 4-15 |

|           |      | 4.2.12     | Registers 32, 33, and 34             | 4-15 |

|           |      | 4.2.13     | Registers 35, 36, and 37             | 4-15 |

|           |      | 4.2.14     | Registers 38 and 39                  | 4-16 |

|           |      | 4.2.15     | Register 40                          | 4-16 |

|           |      | 4.2.16     | Register 41                          | 4-16 |

|           |      | 4.2.17     | Register 42                          | 4-17 |

|           |      | 4.2.18     | Register 43                          | 4-17 |

| Chapter 5 | Sign | als        |                                      |      |

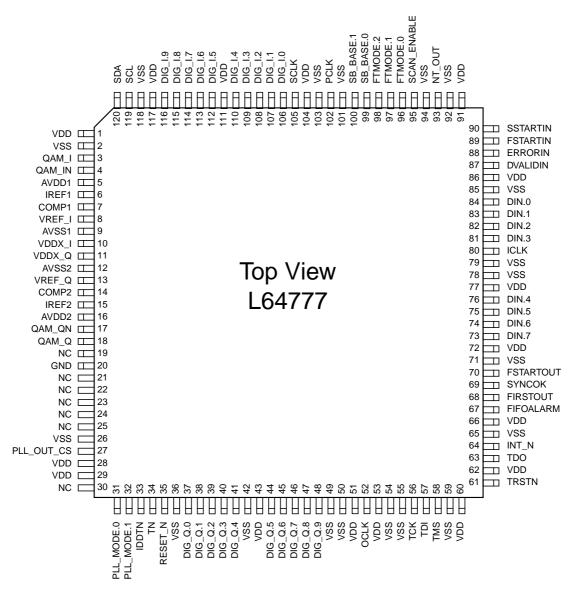

|           | 5.1  | Overvie    | ew                                   | 5-1  |

|           | 5.2  | MPEG       | Transport Stream Multiplexer Signals | 5-3  |

|           | 5.3  | Status     | Information Signals                  | 5-4  |

|           | 5.4  | Test Sig   | gnals                                | 5-5  |

|           | 5.5  | Control    | Signals                              | 5-6  |

|           | 5.6  | Externa    | al PLL Signals                       | 5-6  |

|           | 5.7  | Analog     | QAM Signals                          | 5-7  |

|           | 5.8  | Serial N   | Microprocessor Interface Signals     | 5-8  |

| Chapter 6 | Spec | cification | <br>S                                |      |

| •         | 6.1  |            | Specifications                       | 6-1  |

|           |      | 6.1.1      | Electrical Ratings                   | 6-1  |

|           |      | 6.1.2      | AC Timing Diagrams for L64777        | 6-3  |

|           | 6.2  | Pin Des    | scriptions and Lists                 | 6-5  |

|           |      | 6.2.1      | L64777 Electrical Pin Descriptions   | 6-5  |

|           |      | 6.2.2      | Numerical Pin List for the L64777    | 6-8  |

|           |      | 6.2.3      | Alphabetic Pin List for the L64777   | 6-9  |

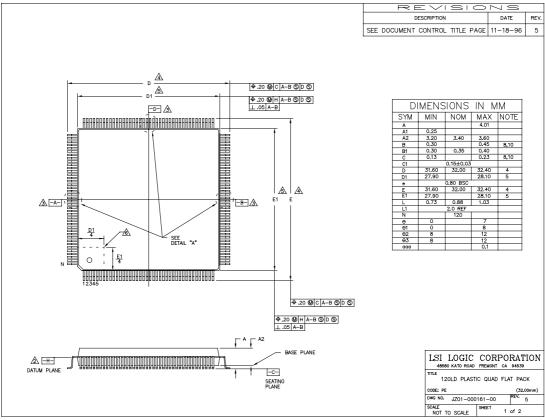

|           | 6.3  | Packag     | e Pinout                             | 6-10 |

Contents vii

| Appendix A | Progr | ramming the L64777 in Serial Host Interface Mode   |      |

|------------|-------|----------------------------------------------------|------|

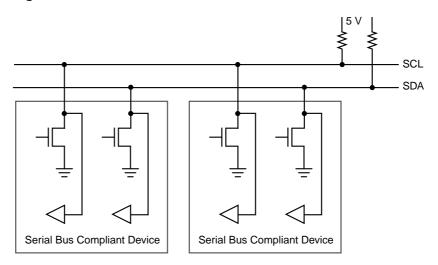

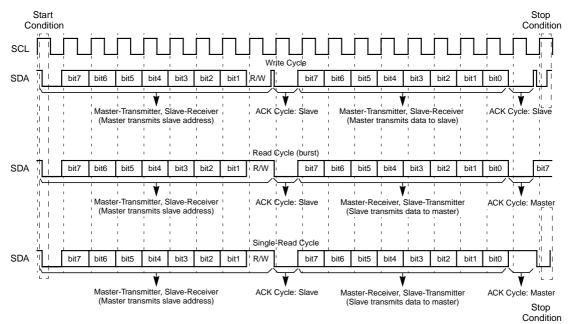

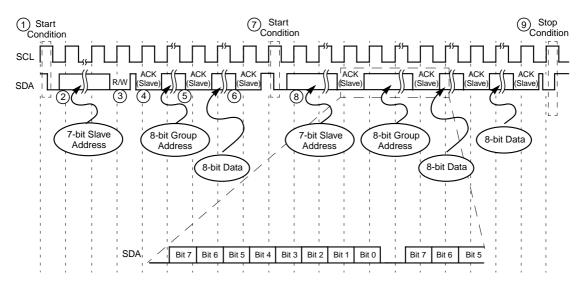

|            | A.1   | Serial Bus Protocol Overview                       | A-1  |

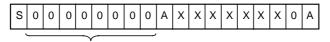

|            | A.2   | Programming the Slave Address Using the Serial     |      |

|            |       | Bus Interface                                      | A-4  |

|            | A.3   | Write Cycle Using the Serial Bus Interface         | A-4  |

|            | A.4   | Read Cycle Using the Serial Bus Interface          | A-5  |

|            | A.5   | Limitations                                        | A-7  |

| Appendix B | PLL I | Divider Settings and L64724/34 Connection          |      |

|            | B.1   | Overview                                           | B-1  |

|            | B.2   | PLL Driver Settings for Typical Applications       | B-2  |

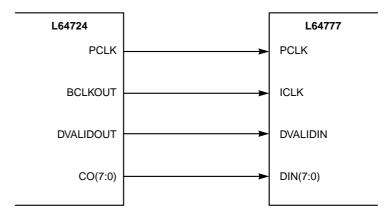

|            | B.3   | Connecting the L64777 to the LSI Logic L64724      | B-3  |

| Appendix C | Monit | toring Device Internal Signals                     |      |

|            | Custo | omer Feedback                                      |      |

| Figures    |       |                                                    |      |

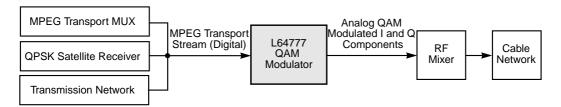

|            | 1.1   | L64777 Operating Environment                       | 1-2  |

|            | 2.1   | ETS 300 429-Compliant Modulation Operation         | 2-2  |

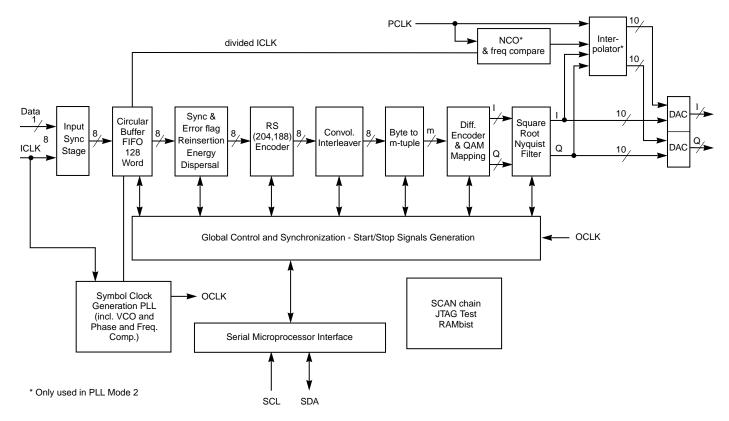

|            | 2.2   | Data Path                                          | 2-3  |

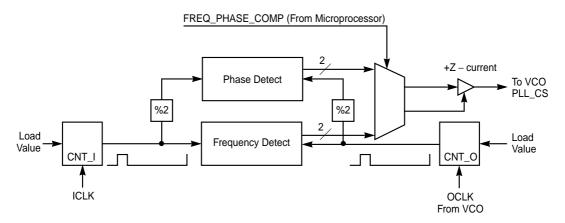

|            | 2.3   | Phase and Frequency Detection with an External VCO | 2-5  |

|            | 2.4   | Analog I/Q Output Interface Diagram                | 2-7  |

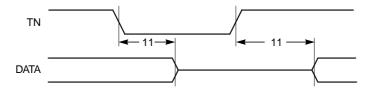

|            | 2.5   | Required Relation of ICLK and DIN/DVALIDIN         | 2-9  |

|            | 2.6   | FIFO Clock Conversion                              | 2-12 |

|            | 2.7   | Sync Acquisition Phase                             | 2-13 |

|            | 2.8   | Sync Tracking Phase                                | 2-14 |

|            | 2.9   | FIFO Pointer Concept                               | 2-16 |

|            | 2.10  | Transport Error Flag Insertion                     | 2-18 |

|            | 2.11  | Scrambler Basic Serial Architecture                | 2-19 |

|            | 2.12  | Shift Register Initialization Sequence             | 2-19 |

|            | 2.13  | Code Word Structure                                | 2-21 |

|            | 2.14  | Forward Error Correction Data Path                 | 2-22 |

|            | 2.15  | Interleaver Block Diagram                          | 2-23 |

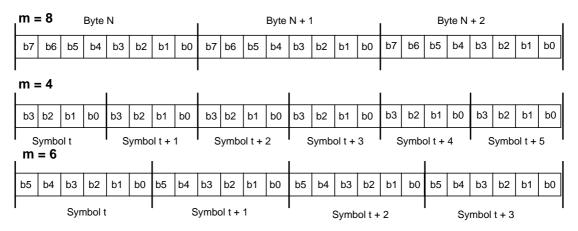

|            | 2.16  | Symbol Cutting From Bytes                          | 2-25 |

viii Contents

|        | 2.17 | Byte to Symbol Conversion                                 | 2-25 |

|--------|------|-----------------------------------------------------------|------|

|        | 2.18 | Differential Encoder and QAM Mapping                      | 2-26 |

|        | 2.19 | Pulse Shaper Structure                                    | 2-27 |

|        | 2.20 | Output Scaling by Arithmetic Shift Right                  | 2-29 |

|        | 2.21 | Square-Root Raised Cosine Filter                          | 2-34 |

|        | 2.22 | NCO Loop Diagram                                          | 2-36 |

|        | 2.23 | Frequency Acquisition Loop Overview                       | 2-38 |

|        | 2.24 | Serial Bus Base Address                                   | 2-40 |

|        | 3.1  | Analog I/Q Output Interface Diagram                       | 3-4  |

|        | 3.2  | I And Q DAC Filter Diagrams                               | 3-5  |

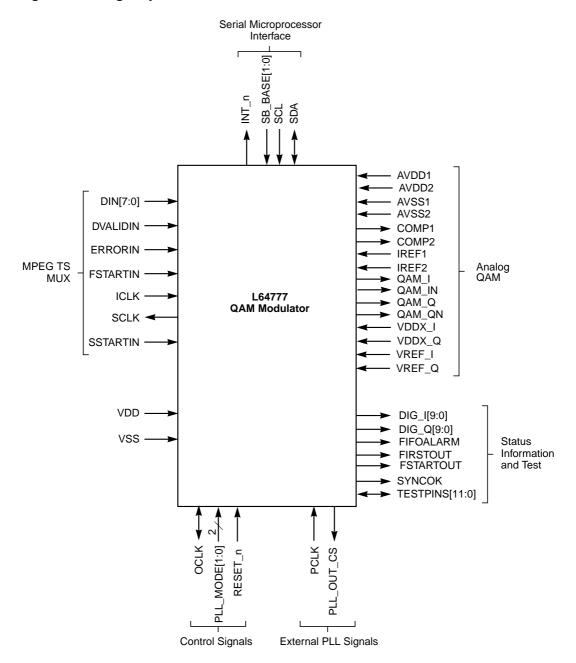

|        | 5.1  | Logic Symbol for the L64777                               | 5-2  |

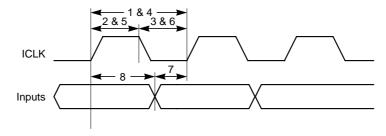

|        | 6.1  | TS Input Timing                                           | 6-3  |

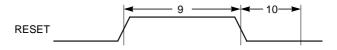

|        | 6.2  | L64777 RESET Timing Diagram                               | 6-3  |

|        | 6.3  | L64777 Bus 3-state Delay Timing                           | 6-4  |

|        | 6.4  | Package 120-Pin PQFP Pinout                               | 6-10 |

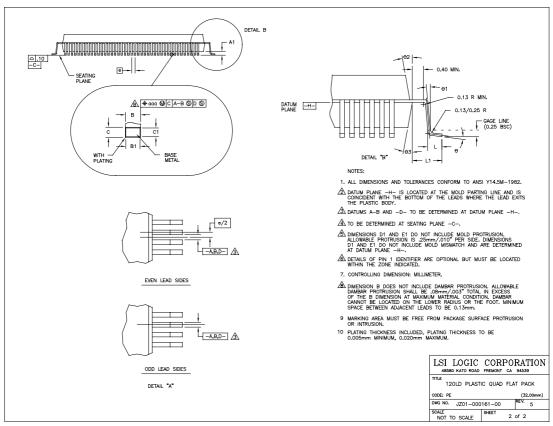

|        | 6.5  | 120-Pin PQFP (PE) Mechanical Drawing                      | 6-11 |

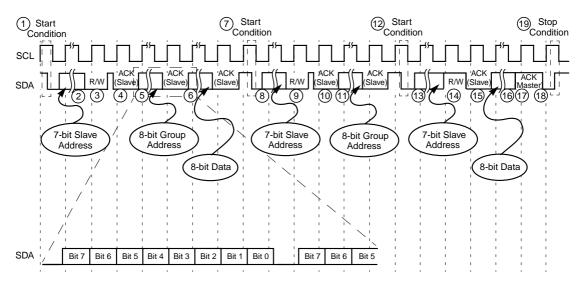

|        | A.1  | Quick Overview of the Serial Bus                          | A-2  |

|        | A.2  | Serial Bus Write/Read Cycle                               | A-3  |

|        | A.3  | General Call Structure                                    | A-4  |

|        | A.4  | Burst Write to Slave (Master-Transmitter, Slave-Receiver) | A-5  |

|        | A.5  | Single Read from Slave                                    | A-7  |

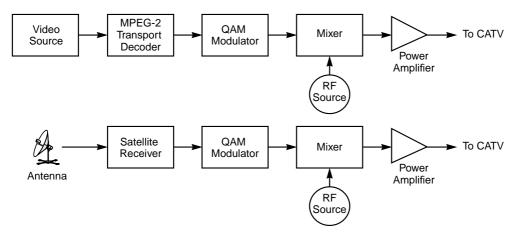

|        | B.1  | CATV Block Diagram                                        | B-1  |

|        | B.2  | Signals between the L64724 and L64777                     | B-3  |

| Tables |      |                                                           |      |

|        | 2.1  | Allocation of Coefficient-Bits for Phase 0                | 2-30 |

|        | 2.2  | Default Nyquist Filter Coefficients                       | 2-32 |

|        | 4.1  | Group 2 Bit Allocation                                    | 4-2  |

|        | 4.2  | Reset Values for Register Fields                          | 4-17 |

|        | 6.1  | L64777 Absolute Maximum Ratings                           | 6-2  |

|        | 6.2  | L64777 Recommended Operating Conditions                   | 6-2  |

|        | 6.3  | L64777 DC Characteristics                                 | 6-2  |

|        | 6.4  | L64777 Preliminary Timing Parameters                      | 6-4  |

|        | 6.5  | L64777 Pin Description Summary                            | 6-5  |

|        | 6.6  | L64777 Numerical Pin List                                 | 6-8  |

|        | 6.7  | L64777 Alphabetical Pin List                              | 6-9  |

|        | B.1  | Typical Settings of CNT_I and CNT_O                       | B-2  |

|        |      |                                                           |      |

Contents ix

# Chapter 1 Introduction

This chapter provides an introduction to the L64777. It consists of the following sections:

- Section 1.1, "Overview," page 1-1

- Section 1.2, "Operating Environment," page 1-2

#### 1.1 Overview

The L64777 chip implements a QAM modulator that is digital video broadcasting (DVB)-compliant, as described in document ETS 300 429. The input is an MPEG-2 system layer-compliant transport stream either in parallel byte-wide or serial format. The chip contains digital signal processing functions, digital-to-analog converters, and sampling clock circuitry that generates a quadrature amplitude modulation (QAM)-modulated output signal in baseband. Users can configure the device by means of its serial interface.

The L64777 chip design is based on the existing LSI Logic L64767 device and includes the following major enhancements:

- Two internal digital-to-analog converters generate in-phase and quadrature (I and Q) baseband signals.

- An on-chip voltage-controlled oscillator improves the symbol rate PLL to support most frequently used application ranges.

- A serial interface replaces the eight-bit microprocessor interface.

- A digital numerically controlled oscillator (NCO) and interpolation mode support operation with the L64724 device.

## 1.2 Operating Environment

The modulator is intended to follow either an MPEG transport stream source (for example, a transport multiplexer) or a satellite receiver, such as the LSI Logic L64724 (see Figure 1.1). It processes MPEG-2 system-compliant frames at the input.

You can program the sync word and block length, and the chip can reinsert the sync information. The device handles the MPEG-specific transport-packet error indication (TEI) bit internally.

Figure 1.1 L64777 Operating Environment

The features of the L64777 include:

- DVB standard ETS 300 429-compliant modulation operation

- Highly integrated global synchronization and clock control

- On-chip VCO to support symbol rates up to 10 Msymbols/s

- Digital NCO and interpolation mode to support operation with the L64724

- Four-fold Nyquist filter oversampling

- Maskable interrupts for all error conditions

- Individual module bypass configuration modes

- I and Q baseband outputs both in digital and analog formats

- I<sup>2</sup>C-compatible serial interface for control, setup, and monitoring of various chip parameters

- User-controllable input synchronization schemes

- 16, 32, 64, 128, and 256 QAM modes

- Reed-Solomon encoder

- Frame sync byte reinsertion

- Input jitter handling and Reed-Solomon gap insertion by a 128-word circular FIFO buffer

- IEEE 1149.1 JTAG interface for testing

- Up to 10 Mbytes/s parallel data input

- Up to 60 Mbits/s serial data input

- Up to 11.25 Mbaud operation in NCO mode of operation

- Easy interface to most input sources

- 85 °C ambient operation without special cooling devices

- Unconstrained serial mode to allow modulation of non-MPEG data stream

# Chapter 2 Modulator Architecture

This chapter briefly introduces the standard modulator chain and the architecture the device uses to implement the chain. This chapter consists of the following sections:

- Section 2.1, "Introduction," page 2-2

- Section 2.2, "PLL Modes," page 2-4

- Section 2.3, "I/O," page 2-6

- Section 2.4, "Input Synchronization," page 2-10

- Section 2.5, "FIFO Clock Conversion," page 2-16

- Section 2.6, "Sync/EF Reinsertion Unit," page 2-17

- Section 2.7, "Reed-Solomon Encoder," page 2-20

- Section 2.8, "Convolutional Interleaver," page 2-23

- Section 2.9, "Bytes to M-tuples Converter," page 2-24

- Section 2.10, "Differential Encoder and QAM Mapping," page 2-26

- Section 2.11, "Square Root Nyquist Filter," page 2-27

- Section 2.12, "Global Control and PLL Module," page 2-34

- Section 2.13, "Interpolator," page 2-39

- Section 2.14, "Serial Microprocessor Interface," page 2-40

- Section 2.15, "Test Unit," page 2-41

#### 2.1 Introduction

The L64777 implements the modulator processing chain defined in ETS 300 429. This processing chain is illustrated in Figure 2.1.

Figure 2.1 ETS 300 429-Compliant Modulation Operation

Figure 2.2 is a block diagram of the L64777 architecture. The input clock drives only the input synchronizing stage. The OCLK, which is four times the QAM symbol rate, is the base of all residual processing.

A numerically controlled oscillator (NCO) module allows the L64777 to interface with LSI Logic L64724. In this case, the chip must receive the L64724 PCLK clock; thus, the byte\_clock output from L64724 must be applied to ICLK. This assumes the PCLK has generated the byte clock.

Figure 2.2 Data Path

The QAM mapping supports 16, 32, 64, 128, and 256 QAM. The input to the device is an MPEG-2 compliant transport stream; its output consists of baseband QAM signals in I and Q.

#### 2.2 PLL Modes

Connecting the L64777 to a satellite receiver and the LSI Logic satellite decoder chip set requires the PLL circuits to lock the input and output clocks. Two modes can achieve this:

- Mode 1 uses the phase/frequency detector and the dividers of L64777 to accept an external VCO.

- Mode 2 connects the PCLK output of L64724 or L64734 to the L64777 PCLK clock input, and connects the byte clock output to the ICLK input of the L64777. This is also called the Numerically Controlled Oscillator (NCO) mode of operation. This mode is dedicated to the connection of the L64724 (see Appendix B, PLL Divider Settings and L64724/34 Connection).

Set the PLL\_MODE[1:0] pins to the values shown on page 5-6. Do not change it during operation.

#### 2.2.1 PLL Mode 1

Figure 2.3 shows the phase and frequency detection for an external voltage-controlled oscillator (VCO) loop. Choose between frequency and phase detection through the microprocessor interface.

Figure 2.3 Phase and Frequency Detection with an External VCO

Prescalers (CNT\_I) and a divider (CNT\_O) in the feedback loop of the PLL generate the internal operating clock (OCLK). Program the 15-bit prescalers through the microprocessor interface, selecting values for CNT\_I and CNT\_O that minimize CNT\_O and reach the required ratio.

#### 2.2.2 PLL Mode 2

In Mode 2, the PCLK input provides an external clock. The L64777 uses the internal NCO to lock to the transport byte clock, provided at ICLK. The chip generates an OCLK internally. Select PCLK to be at least twice the frequency of the internal OCLK. Appendix B, PLL Divider Settings and L64724/34 Connection, describes the connection between the L64777 and the L64724 in Mode 2 operation.

Consecutive sync blocks can have any gap length between them. Thus, the L64777 can convert an input block to a block with a gap for RS insertion, as long as the size of the 128-byte circular input buffer is sufficient to insert RS gaps and to cope with possible PLL jitter. For an encoder with 16-parity RS insertion, the L64777 selects the size of the circular input buffer with sufficient margin.

When operating on public synchronous networks (such as the synchronous digital hierarchy, SDH, or plesiochronous digital hierarchy, PDH), the system designer must consider possible jitter on the input network. The design of the L64777 permits short-term deviations of input-to-output frequency of  $\pm$  56 bytes before a FIFO overrun condition occurs. This is sufficient for operations on SDH or PDH networks.

PLL Modes 2-5

On ATM networks, you must prebuffer input data to get a continuous frame rate at the chip input. If high input jitter occurs over an ATM without a prebuffer, the whole PLL regulation of the input-to-output frame rate fails. You must design the size of the prebuffer according to the maximum jitter expected over the asynchronous transfer mode (ATM) network.

#### 2.3 I/O

The following subsections describe the input and output of the L64777.

## 2.3.1 Input

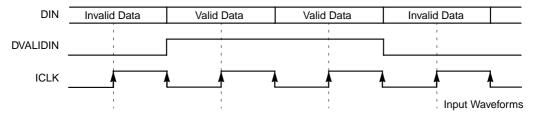

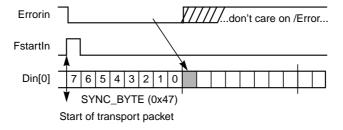

The QAM Modulator accepts serial input data at a maximum 54 MHz clock frequency on the ICLK pin. In Byte-Parallel Input mode (Parallel mode), the maximum frequency on ICLK is 10 MHz. DVALIDIN distinguishes between valid and invalid input data on DIN[7:0]. ERRORIN marks incorrect packets in the transport header, in case a preceding device passes erroneous information. The input error flag is transferred into the TRANSPORT\_ERROR\_INDICATOR bit of MPEG transport packets. Either the FSTARTIN pulse or the SYNC\_BYTE detection (0x47 for MPEG transport packets) establishes input synchronization.

The FSTARTIN pulse marks the first bit, the most significant bit of an MPEG SYNC\_BYTE in Serial Input mode (Serial mode), or the SYNC\_BYTE in Parallel mode. The FSTARTIN pulse synchronizes the process of forming bytes from bits in Serial mode. If no such synchronization signal is applied, the input synchronizer searches for the programmed SYNC\_BYTE occurring in the programmed sync length. In Parallel mode, the L64777 assumes the byte boundaries are correct and compares the SYNC\_BYTE in parallel to the incoming bytes. A flywheel circuit stabilizes the synchronization to a SYNC\_BYTE, while synchronization by external pulses feeds directly into the internal control circuits (see Section 2.4, "Input Synchronization," page 2-10).

## 2.3.2 Output Signals

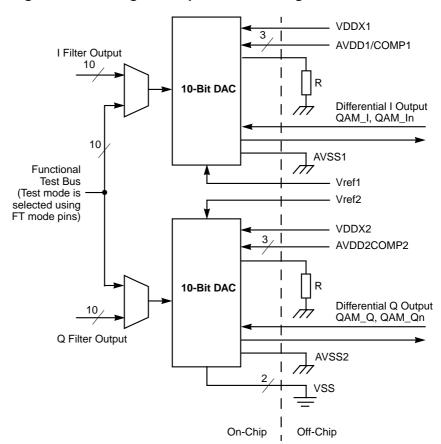

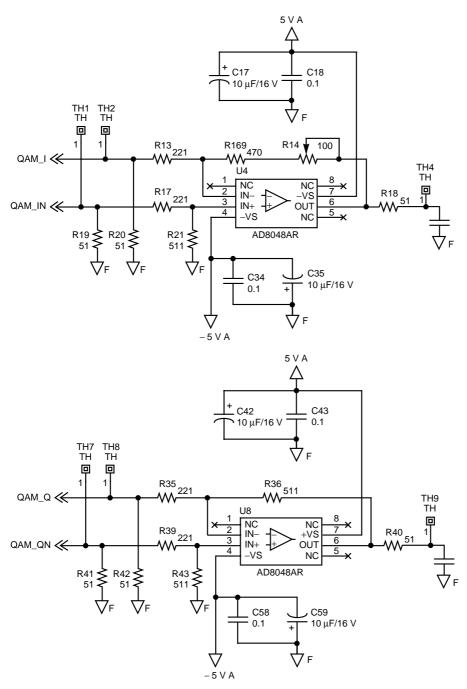

The L64777 outputs the I and Q components of its signal on two separate analog output interfaces (see Figure 2.4). The output interface contains two internal 10-bit digital-to-analog converters.

VDDX1 3 AVDD1/COMP1 I Filter Output 10-Bit DAC Differential I Output QAM\_I, QAM\_In 10 AVSS1 Functional Test Bus VREF1 (Test mode is VREF2 selected using FT mode pins) VDDX2 3/ AVDD2/COMP2 10-Bit DAC Differential Q Output 10 QAM\_Q, QAM\_Qn Q Filter Output AVSS2 VSS On-Chip Off-Chip

Figure 2.4 Analog I/Q Output Interface Diagram

The differential outputs terminate externally (the external components must provide termination to both differential lines, and the DAC achieves maximum linearity in differential mode).

The L64777 I and Q component outputs are available in 10-bit digital format. The related clock depends on the PLL mode: OCLK is used in Mode 1; PCLK is used in Mode 2. The output format can be programmed either as a two's complement, or as a sign magnitude representation.

The analog I- and Q-modulated output signals are at a sampling rate of OCLK, which is four times the QAM symbol rate. The input to the digital-to-analog conversion is available also in a digital format at the DIG\_I and DIG\_Q bus pins.

I/O 2-7

The internal VCO of the L64777 can generate OCLK, or it can use the OCLK input. The L64777 selects OCLK based on the selected PLL mode.

OCLK drives the Nyquist filter and generates the symbol-processing clock inside the chip after the input circular buffer. The beginning of a sync frame at the I and Q output is indicated by the FSTARTOUT signal. FSTARTOUT lets the L64777 watch for gap insertion in the RS code at the FIFO read side. As long as the read pointers are halted to generate gaps, FSTARTOUT remains HIGH for the number of RS check words plus one cycle. For example, FSTARTOUT is one symbol clock cycle long if no gap is inserted; it is 17 symbol clock cycles long if a gap for 16 RS check words is inserted.

The signal FIRSTOUT indicates the head of a sequence after reset with the SSTARTIN signal. The negative slope of the SSTARTIN input pin controls sequence reset.

**Note:** DVALIDIN must be active for at least one ICLK cycle when SSTARTIN is HIGH and when SSTARTIN is LOW.

#### 2.3.3 Control Interface

An external CPU uses the L64777 serial control interface to control and setup the programmable parameters of the chip. This interface is a slave-type only, connected to the same serial bus as LSI Logic L64724.

The chip has five hardwired MSBs and takes two LSBs directly from the input pins SB\_BASE[1:0].

| Bit 6, MSB | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1     | Bit 0, LSB |

|------------|-------|-------|-------|-------|-----------|------------|

| 1          | 1     | 0     | 1     | 0     | SB_BASE.1 | SB_BASE.0  |

The addressing scheme in the L64777 complies with that of the LSI Logic L64724, but due to its small, seven-bit internal address space, the L64777 supports only group 0 and group 2 registers. It ignores all others. Bits [2:0] within the first data byte transmitted to the device specify the group.

Group 0 is the address pointer register (APR); the I<sup>2</sup>C-Compatible Serial Control Interface loads the address byte into APR0 (see Appendix A, "Programming the L64777 in Serial Host Interface Mode"), for programming details. Reading or writing from Group 2 causes a data transfer with the device address specified by APR0:

- If APR0 is set to zero, the Serial Control Interface expects a write access with 196 data bytes to load the filter coefficients; it does not apply an autoincrement to APR0.

- If APR0 is not at zero, the Serial Control Interface expects only a single data byte and applies an autoincrement to the APR0.

The detailed timing of the serial bus is given in Appendix A. The serial bus runs at a maximum 400 kHz clock rate. The serial control interface can transfer reads and writes in single-byte or burst mode. It must access the status registers 12 and 13 with single-byte reads.

The division factor for converting OCLK down to the symbol clock is always four. Input synchronization works at the ICLK rate, either on a bit or byte clock. Energy dispersal (scrambling), Reed-Solomon encoding, convolutional interleaving, byte to m-tuple conversion, differential encoding, and QAM mapping operate at the symbol clock rate (OCLK/4). The final Nyquist filter works on the OCLK rate.

Incoming bits are provided with an input clock (ICLK) and a validation signal (DVALIDIN), which indicates the rising edges of ICLK that are carrying valid data. These inputs feed into a 128-word circular FIFO buffer. The output carries a continuous data stream if the PLL is properly locked.

I/O 2-9

## 2.3.4 Serial Microprocessor Interface

A bidirectional microprocessor interface allows write and confidence read-back of internal registers. No interaction during operation is required with the microprocessor, but all registers must be configured after a RESET to guarantee proper operation of the device. A default setup that requires no microprocessor download is built in for 64 QAM.

In the L64777, the Group 2 register 0 acts as a sequential download register that feeds the 196 bytes of filter coefficients. After every write, the user can read back the last written coefficient to verify the tail entry of the coefficients shift register. The L64777 uses all other registers nonsequentially; these can be read back directly.

## 2.4 Input Synchronization

The L64777 transport interface reads the data stream from the transport source, identifies the position of the synchronization bytes, and strips off invalid data. The transport interface can operate in either Parallel or Serial mode.

The L64777 can synchronize the transport interface in two ways. In both modes, it works synchronously with ICLK and reads all signals, including input data, on the raising edge of ICLK.

- In external synchronization mode, the transport interface specifies

the position of the external sync byte by asserting FSTARTIN HIGH

during sync byte input. In serial mode, the interface must assert the

signal HIGH during the first bit (MSB) of the input stream.

- In internal synchronization mode, the L64777 does not require a block start indication and finds the position of the programmed sync byte automatically.

The transport interface also can apply the signal DVALIDIN, indicating valid input data, to allow gaps between input bytes. To avoid cyclic buffer overrun or underrun, the average data input rate, measured over the programmed block length, must not differ from the nominal payload rate of the generated QAM signal. The circular buffer inside the L64777 allows a maximum 64-byte compensation of the input stream.

Synchronizing the QAM modulator with an input pulse at SSTARTIN sets the byte and block boundaries with this external pulse. The transport interface can reinsert the programmed sync byte at the location defined by the external pulse.

In both the internal and external modes, the transport interface can program the block length and the value of the sync byte. The block length must be less than 256 bytes.

After the L64777 achieves synchronization, it either takes the sync byte from the FIFO, or it inserts the sync byte into the modulated stream according to the programmed sync byte. Only the latter action eliminates any error in the input sync byte, as long as the modulator remains synchronized (see Section 2.6.3, "Energy Dispersal (Scrambler) Unit" for more information).

Given a bit stream consisting of a sequence of TS packets, the sync stage searches for the preprogrammed sync byte (0x47). Upon meeting the sync acquisition criteria, the sync stage issues the control strobes for the downstream modules. In addition to synchronizing the L64777 to SYNC\_BYTEs contained in the input stream, the L64777 can be forced into synchronization by external sync pulses; the modulator can be made to reinsert the programmed SYNC\_BYTE at the sync pulse position.

The transport interface can either pass on a transport error indicator (TEI) unchanged from the input transport stream, or it can force the TEI to indicate an error with the ERRORIN signal. The L64777 observes the forced signal during the sync byte input and ignores it for the rest of the input packet.

The L64777 input stage can operate either in Parallel or Serial mode. The device receives parallel input for connection to transport layer multiplexers at low frequency but with 11 input lines (CLK, 8 lines data, FSTARTIN, and DVALIDIN, if required). The L64777 can mark the MPEG frame SYNC\_BYTE with a pulse on FSTARTIN to identify the beginning of a frame. Together with FSTARTIN, the L64777 can insert sync bytes and error-correction information into the 204 byte frames.

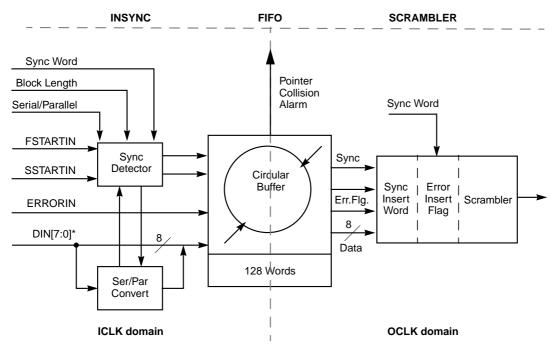

Figure 2.6 shows the FIFO clock conversion from the ICLK domain to the OCLK domain.

Figure 2.6 FIFO Clock Conversion

<sup>\*</sup> Note that DIN[7:0] is valid data, which is the result of D[7:0] and DVALIDIN HIGH

The L64777 synchronizes the input in the ICLK domain and transfers it to the OCLK domain with a reserved bit in the circular buffer. It uses a second bit to transfer the incoming error flag for further insertion into the most significant bit (MSB) of the second byte of a sync frame, according to the MPEG-2 standard.

The L64777 also synchronizes the SSTARTIN pin through the circular buffer, allowing it to lock the beginning of any long-term sequence to the SYNC\_BYTE location of the next sync block. If this pin is not activated after a reset, all generated sequences run free.

When using the L64777 with the L64724, select Parallel mode, which is supported with external synchronization pulses. Use the SPI of L64724 in Mode 2 (204 cycle frames with DVALIDIN LOW during the check bytes). A TEI bit set in the transport stream indicates frames with errors.

A single-line transmission connection to the serial input of the L64777 device generally requires synchronizing on the SYNC\_BYTE within the

bitstream. If the microprocessor interface selects internal synchronization, the L64777 looks for an 8-bit sync pattern S, repeated in the DIN[0] input data stream with a given period of P bytes. For an MPEG-2 DVB transmission, S = 0x47 and P = 204. The values S and P are programmable in the chip to accommodate all applications based on MPEG and MPEG-derived standards.

Parallel operation requires byte-aligning the SYNC\_BYTE to achieve data-dependant synchronization. For serial input, the L64777 searches the SYNC\_BYTE in all possible bit positions and automatically detects the byte-alignment.

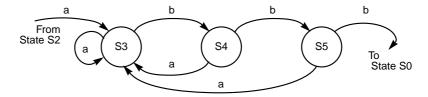

In the L64777, the sync algorithm is fixed to a procedure with programmable values of S and P. In order to achieve the required functionality at the lowest possible gate count, you can select from three values of track steps, which are the number of flywheel repetitions required to declare the states SYNCOK and loss-of-sync. There are two phases to the sync algorithm procedure: the sync acquisition phase, and the sync tracking phase.

## 2.4.1 Sync Acquisition Phase

In the sync acquisition phase, the number of sync detections required for sync and loss is programmable from 3 to 5. TS is the designation for the number of track steps. After TS error-free consecutive detections of the sync byte S at the correct locations, the L64777 declares synchronization; if a mismatch occurs, it goes back to the search state.

Validating the detection of the sync word three times ensures a probability of false alarm equal to  $P_{fa} = (2^{-8})^3 = 6*10^{-8}$ . Validating the detection of the sync word five times insures a probability of false alarm equal to  $P_{fa} = (2^{-8})^5 = 9*10^{-13}$ .

Figure 2.7 shows the states occurring in the sync acquisition phase.

a0 a a To State S3

Figure 2.7 Sync Acquisition Phase

The abbreviations in the illustration indicate the following states:

- S0 is the sync pattern research state. When S is detected, transition a0 leads to state S1. If S is not detected, transition b0 maintains state S0.

- S1 is a retest state. Period (P) bytes after S detection in state S0, the detection of S is retested. If S is detected again, transition "a" leads to state S2. If S is not detected, transition "b" leads back to state S0.

- S2 again tests detection of S after period P. If correct detection occurs, transition "a" leads to the sync tracking phase. If not, transition "b" leads back to S0.

## 2.4.2 Sync Tracking Phase

The sync tracking phase checks the detection of S at the correct location (i.e., every P bytes). TS -1 mismatches are tolerated, but at the last mismatch the L64777 declares a loss-of-sync and goes back to state S0 to look for new synchronization.

Figure 2.8 shows the states occurring in the sync tracking phase.

Figure 2.8 Sync Tracking Phase

The abbreviations in the illustration indicate the following states:

- S3 is a synchronized state. If no mismatches occur, transition "a" maintains this state. If a wrong word is detected at the location where S is expected, transition "b" leads to state S4.

- S4 tests the detection of S after an interval of P bytes since the last detection test. If S is detected, transition "a" leads back to synchronized state S3. If not, transition "b" leads to S5.

• S5 again test the detection of S after period P. If S is detected, transition "a" leads back to synchronized state S3. If not, transition "b" leads back to S0 to look for another sync location.

To review the transitions in the sync acquisition and sync tracking phases:

- Transition a0 occurs when word S is detected.

- Transition b0 occurs when word S is not detected.

- Transition "a" occurs when word S is detected exactly P bytes after the last detection test.

- Transition "b" occurs when word S has not been detected P bytes after the last detection test. This transition activates a declaration of loss-of-sync.

The L64777 activates output SYNCOK in state S3, S4, or S5. This allows easy measurement of synchronization conditions from outside and monitoring during normal operation. The microprocessor interface also provides SYNCOK information. At this interface, the L64777 can read the actual status and a glitch trap (which detects any sync losses between two sync status reads). SYNCOK can also generate interrupts, if the SYNCOK interrupt is not masked (see Section 4.2.1, "Register 12," page 4-10).

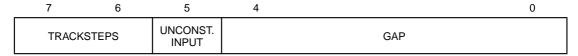

In order to use a subset of the device with random data (without frame structure), bypass the synchronization mechanism by setting the unconstrained bit in the register map (see Section 4.1.10, "Register 11," page 4-9).

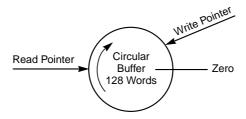

#### 2.5 FIFO Clock Conversion

The L64777 uses a dual-ported RAM to implement the circular buffer FIFO function. The circular buffer has a write pointer driven by ICLK and a read pointer driven by the Symbol clock, OCLK/4. The device does not prevent collisions of the pointers; rather, the PLL-VCO follow-up time and proper initial setup of the pointer distance must guarantee this.

For FIFO initialization, the L64777 loads a user-programmable pointer distance of 0 to 127 cycles (the FIFO delay value of Register 2 in Group 2) into the read address pointer (after each microprocessor delay register access) and sets the write address pointer to zero (see Figure 2.9). After this initialization, both pointers run free, and the OCLK to ICLK frequency relationship determines how the read and write pointers advance.

To allow outside watching of the asynchronous pointers, an alarm comparator indicates when both pointers are equal. Because both counters are Gray Code counters (in which changes occur only in one bit) the spikes and glitches of the asynchronous signals are minimized.

When specifying the microprocessor download value for the read pointer initialization, you must use Gray Code. The write pointer also is Gray Code counter-driven; it initializes to zero when the read counter is loaded.

Figure 2.9 FIFO Pointer Concept

Properly programmed delay values in Gray Code guarantee that the read pointer is directly opposite the write pointer most of the time; this increases system immunity against PLL frequency swings, which might occur during the phases of an unstable input signal. Smaller distances also can reduce system delay.

The hexidecimal address sequence of the read (underlined) and write pointers is:

00, 01, 03, 02, 06, 07, 05, 04, 0C, 0D, 0F, 0E, 0A, 0B, 09, 08,

18, 19, 1B, 1A, 1E, 1F, 1D, 1C, 14, 15, 17, 16, 12, 13, 11, 10,

30, 31, 33, 32, 36, 37, 35, 34, 3C, 3D, 3F, 3E, 3A, 3B, 39, 38,

<u>28</u>, 29, <u>2B</u>, 2A, <u>2E</u>, 2F, <u>2D</u>, 2C, <u>24</u>, 25, <u>27</u>, 26, <u>22</u>, 23, <u>21</u>, 20,

60, 61, 63, 62, 66, 67, 65, 64, 6C, 6D, 6F, 6E, 6A, 6B, 69, 68,

<u>78</u>, 79, <u>7B</u>, 7A, <u>7E</u>, 7F, <u>7D</u>, 7C, <u>74</u>, 75, <u>77</u>, 76, <u>72</u>, 73, <u>71</u>, 70,

<u>50</u>, 51, <u>53</u>, 52, <u>56</u>, 57, <u>55</u>, 54, <u>5C</u>, 5D, <u>5F</u>, 5E, <u>5A</u>, 5B, <u>59</u>, 58,

<u>48</u>, 49, <u>4B</u>, 4A, <u>4E</u>, 4F, <u>4D</u>, 4C, <u>44</u>, 45, <u>47</u>, 46, <u>42</u>, 43, <u>41</u>, 40.

The L64777 download through the microprocessor interface starts with the beginning read pointer value. The write pointer start value is always fixed to zero. Every time the L64777 accesses the FIFO delay value in the microprocessor interface (FDEL, see Section 4.1.3, "Register 2," page 4-5), the pointers are reset to the these values. If the L64777 is programmed to the FIFO Autoreset mode (see Section 4.1.7, "Register 6," page 4-7), it forces the pointers to the value in the FDEL register on the read side and to zero on the write side after every FIFO collision.

#### Attention:

The only legal load values for the read pointer are Gray Code numbers with even parity, which means an even number of 1s (underlined in the above table). Therefore, the FIFO delay increment can only be in steps of two. The device achieves maximum delay with a value of 0x41; the optimum (center) distance to overrun and underruns is 0x60.

## 2.6 Sync/EF Reinsertion Unit

The following subsections describe the Sync/EF modes, error flag insertion, and scrambler.

#### 2.6.1 Sync Insertion Mode

The Sync/EF unit inserts new sync words if that mode is programmed (see Section 4.1.2, "Register 1," page 4-4). Sync insertion can be useful to work against bit errors in sync bytes, even if sync is already inserted in the stream. If the bitstream contains sync bytes that the device uses for synchronization, the regenerated sync bytes conceal single errors in the synchronization pattern.

In unsynchronized states S0, S1, and S2, the L64777 bypasses data bits without any modification of the sync byte. After it establishes synchronization (in states S3, S4 and S5), the device inserts the regenerated sync pattern based on the programming of Register 1.

## 2.6.2 Error Flag Insertion

The next processing task is the error flag handling for MPEG-2 transport packets. If ERRORIN indicates a decoder error at the first byte of a frame, the L64777 sets the TRANSPORT\_ERROR\_INDICATOR bit of the MPEG-2 packet. This is the MSB of the second byte in a packet (see Figure 2.10). If there is no error indication, the L64777 passes the TRANSPORT\_ERROR\_INDICATOR bit transparently.

Figure 2.10 Transport Error Flag Insertion

## 2.6.3 Energy Dispersal (Scrambler) Unit

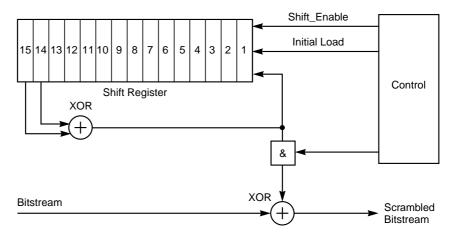

The function of the Scrambler is specified for the serial domain by the Digital Broadcasting Systems for Television Sound and Data Services: Framing Structure, Channel Coding and Modulation Cable Systems. The energy dispersal module (scrambler) operates in Parallel mode based on the algorithm of the serial domain. Figure 2.11 illustrates the basic serial architecture of the Scrambler.

Figure 2.11 Scrambler Basic Serial Architecture

The scrambler block consists of two major modules: one to generate a pseudo-random binary sequence (PRBS) that modifies the incoming data stream, and the other a control module that properly aligns data with the PRBS.

The PRBS the descrambler module produces is characterized by the following generator polynomial:

$$1 + x^{14} + x^{15}$$

For initialization, choose a specific value for the 15-tap shift register (see Figure 2.12).

Figure 2.12 Shift Register Initialization Sequence

| 0  |    |    |    |    |    |   |   |   |   |   |   |   |   |   |

|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 |

The L64777 uses a special sync word (0xB8), generated by inverting every eighth transport sync word (0x47), to align the descrambler with the incoming data stream. The L64777 applies the first bit of the PRBS to the first data bit following the inverted sync byte and freezes the scrambler register contents during gaps for RS check words. During the following noninverted sync words, the descrambler sequence generator is kept in operation but does not modify the data stream. The L64777 resets the descrambler sequence after every inverted sync word. The

SSTARTIN input signal can preset the phase of the inverted SYNC\_BYTE and the whole scrambler sequence.

The microprocessor can switch off the scrambler module through Register 3 (see Section 4.1.4, "Register 3," page 4-5). The selected microprocessor control applies the sequence of Start, Run, and Disable modes, depending on the programmed sync block length values in Register 4 (see page 4-6).

### 2.7 Reed-Solomon Encoder

Reed-Solomon (RS) error correction codes are systematic and operate on bytes rather than single-bit data streams. The codes are expressed by convention as two numbers, the first indicating the total code word length (N), and the second indicating the number of message bytes (K). The difference between these two numbers (N-K) is the number of check bytes.

DVB uses this generator polynomial for RS codes:

$$\prod_{i=0}^{R-1} (x + \alpha^i)$$

where R = 16 (checkbytes), and  $\alpha$  is a root of the binary primitive polynomial:

$$x^8 + x^4 + x^3 + x^2 + 1$$

A data byte (d<sub>7</sub>, d<sub>6</sub>,...d<sub>1</sub>, d<sub>0</sub>) is identified with the element  $d_7\alpha^7 + d_6\alpha^6 + ... + d_1\alpha + d_0$  in GF (256), the finite field with 256 elements.

The error-correcting power of an RS code is related to the number of redundant check symbols in its code words. In general, an RS code with 2t check symbols per code word can correct up to "t" byte errors per code word. Higher redundancy allows more errors to be corrected.

ECC devices have a specific lexicon associated with their ability to correct transmission messages; the terms used for variables in the Reed-Solomon Core are as follows:

#### R Check Bytes

The encoder generates and appends check bytes to the incoming message according to the Reed-Solomon error-correction encoding. The decoder uses check bytes to locate and correct errors due to transmission.

#### d Detection Power

Detection power has a minimum value of  $\lfloor \frac{R}{2} \rfloor$  and a maximum value of R.

#### K Message Length

The message is comprised of multiple bytes. The size of the message varies depending on the code word length and the check bytes used, where K = N - R.

#### m Symbol Size

The symbol size m is 8 bits fixed.

#### N Code Word Length

This is the sum of the number of message bytes and the number of check bytes (K + R).

#### t Number of Error Corrections

This variable is the maximum number of error corrections performed by the decoder. Its maximum value is:

$\frac{R}{2}$

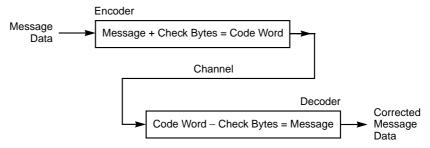

## 2.7.1 Forward Error Correction (FEC)

FEC requires an encoder that appends redundant check information to the message before transmission. The bytes with an indeterminate number of bits are referred to as symbols. The message symbols and following redundant check symbols make up code words. The check symbols are redundant because they are derived from the message and are appended to the message. Check symbols are also referred to as "redundant check bytes," and sometimes as "correction bytes." Figure 2.13 illustrates a code word.

Figure 2.13 Code Word Structure

N Code Word Bytes

| K Message Bytes R Redundant Check Bytes |

|-----------------------------------------|

|-----------------------------------------|

A code word is a block of N bytes that includes K message symbols and N-K check bytes (R). The check bytes, or symbols, are some fraction of the message symbols. A large number of check symbols allows the decoder to correct a large number of transmission errors. The redundant check symbols in a message allow a decoder at the receiving end of a transmission line to detect transmission errors and reconstruct the original message content. Figure 2.14 shows a block diagram of the basic encoder and decoder functions in a transmission system.

Figure 2.14 Forward Error Correction Data Path

After generating a code word, the encoder transmits it to a decoder. The decoder compares the bitstream in the message data to the encoding in the check bytes to detect transmission errors. The L64777 can reconstruct the original message precisely from the check symbols, as long as the code word has no more than  $\lfloor (R)/2 \rfloor$  byte errors, where R = the number of redundant check bytes.

## 2.7.2 Error Handling and Correction

A bit error occurs when a transmitted 0 is received as a 1, or vice versa. A byte error occurs when one or more bits in the byte have errors. For example, a byte with only one bit error is counted as one byte error, and a byte with m bit errors (all bits are inverted) is also counted as 1 byte error. As long as a code word has no more than  $t = \lfloor (R)/2 \rfloor$  byte errors, the RS decoder corrects all errors.

To achieve RS encoding at the lowest possible gate count and power consumption, the check byte parameters of the RS encoder in the L64777 are fixed to R = 16, according to the DVB standard. When the RS encoder is switched off, data feeds through without check-word insertion at an internal delay of two clock cycles.

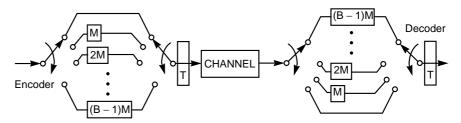

### 2.8 Convolutional Interleaver

Figure 2.15 is a block diagram of a convolutional interleaver system, which rearranges the ordering of a sequence of symbols in a deterministic manner. A (B, N) periodic interleaver has the following characteristics:

- The minimum separation at the interleaver output is B symbols for any two symbols that are separated by less than N symbols at the interleaver input.

- Any burst of b < B errors inserted by the channel results in single errors at the deinterleaver output.

The scheme is also referred to as a convolutional interleaver/deinterleaver (based on the Forney approach).

Figure 2.15 Interleaver Block Diagram

The L64777 interleaver performs periodic interleaving with two fixed parameters: B, the desired interleaving depth, and M, defined as:

$$M = \left\lceil \frac{N}{B} \right\rceil$$

The values of the interleaver in the L64777 are: N = 204, B = 12, and M = 17. You can switch off the interleaver. It is fully transparent with an intrinsic delay of three clock cycles.

The main modules are a set of configured RAM-based delay lines to implement the proper delay for individual data bytes, and a controller to handle and generate the strobes needed by subsequent modules in the data path.

The interleaver must recover the block boundaries, and the SSTARTIN pin indicates them by internal strobes; it also resets the interleaver sequence. You can program the interleaver so that all data fed into the interleaver RAM before the very first arrival of a SSTARTIN negative slope is set to zero. This eases operation verification and debugging during development when the interleaver RAM is completely initialized with zero values. You must apply a fresh reset to feed zeros after an active SSTARTIN slope.

The interleaver and the deinterleaver, in sequence, output the original byte stream after a delay of

$$Delay = (B-1) \times B \times M$$

In the L64777, the Delay =  $(11 \times 12 \times 17) = 2244$  clock cycles. Thus, the delay from the time of the first input byte to the first valid output byte in the maximum delay path of the interleaver is half of this value, which is 1122 valid clock cycles.

If the QAM is not in 256 mode, the interleaver inserts invalid cycles in an eight-byte sequence, which proportionally increases the delay time. The zero delay path in the interleaver delivers data with a propagation delay of three clock cycles. This is equal to the delay of the interleaver when it is off.

## 2.9 Bytes to M-tuples Converter

This unit cuts down bytes to slices of m = 1, 2, 3, 4, 5, 6, 7, and 8 bits. The programming parameter, mSize (see Section 4.1.2, "Register 1," page 4-4), must be set to m - 1. The order is the MSB of the oldest byte first. See the *Digital Broadcasting Systems for Television Sound and Data Services: Framing Structure, Channel Coding and Modulation Cable Systems* for a detailed specification. When cutting six-bit symbols, it cuts three bytes into four symbols. The case of four-bit symbols is trivial (eight bits are split into two sets of four bits each).

Figure 2.16 outlines the basic principle for symbol cutting out of bytes. Modes for m = 5 and m = 7 are similar.

Figure 2.16 Symbol Cutting From Bytes

The general control unit feeds packets of eight bytes and a valid indicator to the convertor. Thus, the conversion is as shown in Figure 2.17.

Figure 2.17 Byte to Symbol Conversion

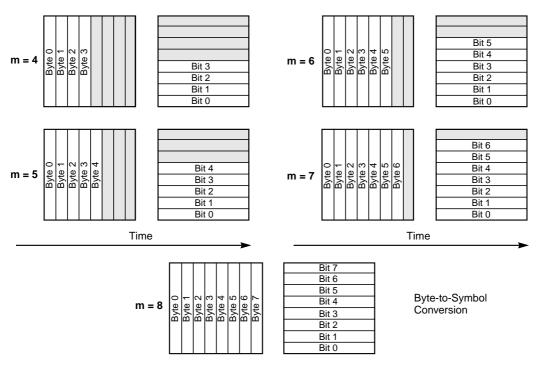

## 2.10 Differential Encoder and QAM Mapping

This block performs differential encoding and mapping for 16 and 64 QAM, as specified in the *Digital Broadcasting Systems for Television Sound and Data Services: Framing Structure, Channel Coding and Modulation Cable Systems*, the baseline document, and its extensions. The QAM 256 mapping is taken from the DVB document 1190.

The encoder performs differential encoding on the two most significant bits of each symbol, as shown in the block diagram in Figure 2.18 and specified in equations 2.1 and 2.2.

Figure 2.18 Differential Encoder and QAM Mapping

To clarify the underlying concepts in Figure 2.18, here are two examples:

- 1. If m = 4,  $A_k$  is bit 3,  $B_k$  is bit 2, and the LSB = (m 2) bits = bits [1:0].

- 2. If m = 6,  $A_k$  is bit 5,  $B_k$  is bit 4, and the LSB = (m 2) bits = bits [3:0].

Equation 2.1

$$I_k = (\neg (A_k \oplus B_k))(A_k \oplus I_{k-1}) + (A_k \oplus B_k)(A_k \oplus Q_{k-1})$$

Equation 2.2

$$Q_k = (\neg (A_k \oplus B_k))(B_k \oplus Q_{k-1}) + (A_k \oplus B_k)(B_k \oplus I_{k-1})$$

Mapping performs a table look-up for the concatenation of the (m-2) least significant bits of each symbol with the differentially generated bits  $I_k$  and  $Q_k$ .

In 64 QAM mode, the mapping block of the differential encoder maps the 6-tuples to two 3-bit values for I and Q output. In 16 QAM mode, it maps the 4-tuples to two 2-bit values. For lower QAM modes, it aligns the I and Q output values to the MSB and stuffs the least-significant bit (LSB) with ones.

Differential encoding has an infinite error propagation. You can switch it off independently from the mapping function (see bit 3 of Register 6, on page 4-8).

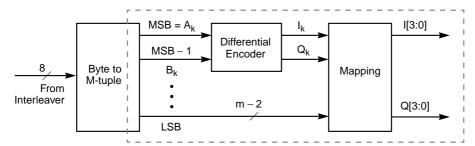

## 2.11 Square Root Nyquist Filter

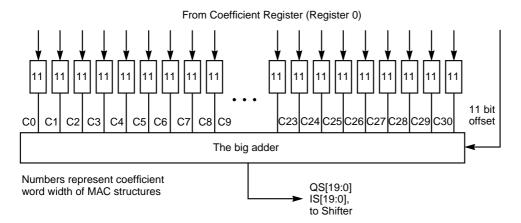

This pulse-shaper module implements a programmable square-root raised cosine filtering function with a default 15% roll-off factor. The precision of the internal Nyquist filter computations, and the width of the output data bus, are sufficient for QAM modulations up to 256. The filter operates at four times the oversampling rate. Figure 2.19 illustrates the structure of the pulse shaper.

Figure 2.19 Pulse Shaper Structure

Note that the 20 bits per channel is a result of the length of each coefficient register ( $2^{11}$ ) plus the length of INQ ( $2^4$ ) plus the number of stages ( $30 = 2^5$ ). The total number of coefficients is 124 (there is one coefficient set for each of the four phases multiplied by the MAC structure, which contains 31 multipliers).

Each of the two I and Q branches has one filter, realized as polyphase structures. Each filter consists of four filter branches, which compute 1-phase filter results at the symbol rate. Thus, the L64777 Nyquist filter module generates the desired pulse shape by combining the outputs of four identical filter branches for I and Q.

For an oversampling factor of four, the filter executes the above sequence at four times the symbol rate (60 MHz in PLL mode).

Each multiply accumulator (MAC)-structure contains 31 multipliers whose outputs add up to the desired result. The pulse shaper module connects one input of each multiplier to a delayed version of the filter input data; the other multiplier input is connected to one of four coefficient registers through a multiplexer. The pulse shaper clocks the delay line for IData and QData with the symbol clock rate. The coefficient and multiplier width are as described below.

The pulse shaper interprets all data as two's complement. Each MACstructure contains an additional input to the adder array to allow for the addition of an 11-bit value to compensate for an offset. The pulse shaper treats these offset coefficients like regular coefficients, except that it adds them directly to the MAC outputs. There is one offset coefficient for each phase.

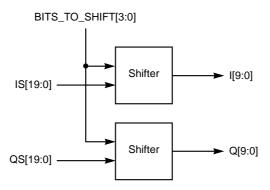

The shifter block adjusts the internally generated filter result to accommodate the limited range of the internal D/A-converter. The standard mapping after reset is a five-bit shift to the right, which means IS[5] to I[0], IS[6] to I[1] and so on. The shifter treats the Q-branch accordingly.

By applying a value different from zero to the BITS\_TO\_SHIFT[3:0] input of the shifter (using Register 0), the shifter connects IS to I, and QS to Q, so that the lowest bits of IS and QS are truncated, while the more significant bits are hooked to the I and Q outputs. The BITS\_TO\_SHIFT input can assume a maximum value of 15, thus mapping IS[15] to I[0], IS[16] to I[1], and so on. The filter output value is not limited to maximum positive or negative values before shifting, so it is the user's responsibility to download coefficients and an appropriate shifting value to avoid output overflow and underflow. Figure 2.20 illustrates the output scaling by an arithmetic shift to the right.

Figure 2.20 Output Scaling by Arithmetic Shift Right

The shifter treats the value of BITS\_TO\_SHIFT[3:0] like a coefficient, and the value is available separately for every phase. This means that the hardware of the filter is multiplexed in such a way that there are the same coefficient registers for the I and Q channel, and each of the two MACs switches between four banks of coefficients cyclically, driven by OCLK. Setting all coefficients to zero (except the center coefficient, which is 1), offers a bypass mode for the filter.

The interpolator following the Nyquist filter receives 12-bit resolution in PLL Mode 2. Program the shifter accordingly to make the increase precision available to the interpolator; for example: to 3 rather than 5.

## 2.11.1 Filter Setup Procedure

The filter module is loaded with 31 filter coefficients sequentially, with four blocks of 49 bytes in the PHASE\_0, PHASE\_1, PHASE\_2, and PHASE\_3 registers (Register 0 of Group 2). The same data controls the I and Q data path in parallel. Also, the filter is loaded with four BITS\_TO\_SHIFT and an 11-bit offset value for each phase. It is specified within 49 bytes in each phase, as shown in Table 2.1. The complete setup sequence consists of 4 \* 49 = 196 bytes for all four phases. The filter organizes the coefficient registers for each register bank as described below, using the coefficient enumeration shown in the block diagram. Note that no meaningful operation can be performed while the filter is being programmed, since the old coefficients are being shifted out while the new ones are programmed in.

As shown in Figure 2.18, the filter shifts four coefficient register banks (Register 0) sequentially, starting with register 48 and proceeding down to 0. In this configuration, it shifts bank 3 first, then 49 bytes of bank 2, bank 1, and, finally, bank 0. Table 2.1 shows the exact allocation of bits within each bank.

## **2.11.2 Example**

Assuming all filter configuration bits are located in a host microprocessor ROM array of bytes addressed with [0 to 195], the filter coefficients place phase 0 coefficients in registers [0 to 48], phase 1 in [49 to 97], phase 2 in [98 to 146], and phase 3 in [147 to 195]. To download this array, the microprocessor must write bytes [195 down to 0] sequentially into address 0 register, highest array address first.

After 196 write cycles, the four coefficient register banks are completely configured. During configuration, the filter is not operational to save gates by avoiding double buffering of the coefficient registers. For different QAM modes, the filter must load the appropriate sets of coefficients and shifter values.

The default set of coefficients is a square-root raised cosine filter. The filter sets the coefficients in Table 2.2 after reset, and it can overwrite them with external programming through the I<sup>2</sup>C-compatible interface.

Table 2.1 Allocation of Coefficient-Bits for Phase 0

| В7   | В6    | B5   | B4   | В3   | B2    | B1   | В0   | Reg # |

|------|-------|------|------|------|-------|------|------|-------|

| c0.7 | c0.6  | c0.5 | c0.4 | c0.3 | c0.2  | c0.1 | c0.0 | 0     |

| c1.7 | c1.6  | c1.5 | c1.4 | c1.3 | c1.2  | c1.1 | c1.0 | 1     |

| _    | c0.10 | c0.9 | c0.8 | _    | c1.10 | c1.9 | c1.8 | 2     |

| c2.7 | c2.6  | c2.5 | c2.4 | c2.3 | c2.2  | c2.1 | c2.0 | 3     |

| c3.7 | c3.6  | c3.5 | c3.4 | c3.3 | c3.2  | c3.1 | c3.0 | 4     |

| _    | c2.10 | c2.9 | c2.8 | _    | c3.10 | c3.9 | c3.8 | 5     |

| c4.7 | c4.6  | c4.5 | c4.4 | c4.3 | c4.2  | c4.1 | c4.0 | 6     |

| c5.7 | c5.6  | c5.5 | c5.4 | c5.3 | c5.2  | c5.1 | c5.0 | 7     |

| _    | c4.10 | c4.9 | c4.8 | _    | c5.10 | c5.9 | c5.8 | 8     |

Table 2.1 Allocation of Coefficient-Bits for Phase 0 (Cont.)

| B7    | В6     | B5    | B4    | В3    | B2     | B1    | В0    | Reg # |

|-------|--------|-------|-------|-------|--------|-------|-------|-------|

| c6.7  | c6.6   | c6.5  | c6.4  | c6.3  | c6.2   | c6.1  | c6.0  | 9     |

| c7.7  | c7.6   | c7.5  | c7.4  | c7.3  | c7.2   | c7.1  | c7.0  | 10    |

| _     | c6.10  | c6.9  | c6.8  | _     | c7.10  | c7.9  | c7.8  | 11    |

| c8.7  | c8.6   | c8.5  | c8.4  | c8.3  | c8.2   | c8.1  | c8.0  | 12    |

| c9.7  | c9.6   | c9.5  | c9.4  | c9.3  | c9.2   | c9.1  | c9.0  | 13    |

| _     | c8.10  | c8.9  | c8.8  | _     | c9.10  | c9.9  | c9.8  | 14    |

| c10.7 | c10.6  | c10.5 | c10.4 | c10.3 | c10.2  | c10.1 | c10.0 | 15    |

| c11.7 | c11.6  | c11.5 | c11.4 | c11.3 | c11.2  | c11.1 | c11.0 | 16    |

| _     | c10.10 | c10.9 | c10.8 | _     | c11.10 | c11.9 | c11.8 | 17    |

| c12.7 | c12.6  | c12.5 | c12.4 | c12.3 | c12.2  | c12.1 | c12.0 | 18    |

| c13.7 | c13.6  | c13.5 | c13.4 | c13.3 | c13.2  | c13.1 | c13.0 | 19    |

| _     | c12.10 | c12.9 | c12.8 | _     | c13.10 | c13.9 | c13.8 | 20    |

| c14.7 | c14.6  | c14.5 | c14.4 | c14.3 | c14.2  | c14.1 | c14.0 | 21    |

| c15.7 | c15.6  | c15.5 | c15.4 | c15.3 | c15.2  | c15.1 | c15.0 | 22    |

| _     | c14.10 | c14.9 | c14.8 | _     | c15.10 | c15.9 | c15.8 | 23    |

| c16.7 | c16.6  | c16.5 | c16.4 | c16.3 | c16.2  | c16.1 | c16.0 | 24    |

| c17.7 | c17.6  | c17.5 | c17.4 | c17.3 | c17.2  | c17.1 | c17.0 | 25    |

| _     | c16.10 | c16.9 | c16.8 | _     | c17.10 | c17.9 | c17.8 | 26    |

| c18.7 | c18.6  | c18.5 | c18.4 | c18.3 | c18.2  | c18.1 | c18.0 | 27    |

| c19.7 | c19.6  | c19.5 | c19.4 | c19.3 | c19.2  | c19.1 | c19.0 | 28    |

| _     | c18.10 | c18.9 | c18.8 | _     | c19.10 | c19.9 | c19.8 | 29    |

| c20.7 | c20.6  | c20.5 | c20.4 | c20.3 | c20.2  | c20.1 | c20.0 | 30    |

| c21.7 | c21.6  | c21.5 | c21.4 | c21.3 | c21.2  | c21.1 | c21.0 | 31    |

| _     | c20.10 | c20.9 | c20.8 | _     | c21.10 | c21.9 | c21.8 | 32    |

| c22.7 | c22.6  | c22.5 | c22.4 | c22.3 | c22.2  | c22.1 | c22.0 | 33    |

Table 2.1 Allocation of Coefficient-Bits for Phase 0 (Cont.)

| B7       | B6       | B5       | B4       | В3       | B2        | B1       | В0       | Reg # |

|----------|----------|----------|----------|----------|-----------|----------|----------|-------|

| c23.7    | c23.6    | c23.5    | c23.4    | c23.3    | c23.2     | c23.1    | c23.0    | 34    |

| _        | c22.10   | c22.9    | c22.8    | _        | c23.10    | c23.9    | c23.8    | 35    |

| c24.7    | c24.6    | c24.5    | c24.4    | c24.3    | c24.2     | c24.1    | c24.0    | 36    |

| c25.7    | c25.6    | c25.5    | c25.4    | c25.3    | c25.2     | c251     | c25.0    | 37    |

| _        | c24.10   | c24.9    | c24.8    | _        | c25.10    | c25.9    | c25.8    | 38    |

| c26.7    | c26.6    | c26.5    | c26.4    | c26.3    | c26.2     | c26.1    | c26.0    | 39    |

| c27.7    | c27.6    | c27.5    | c27.4    | c27.3    | c27.2     | c271     | c27.0    | 40    |

| _        | c26.10   | c26.9    | c26.8    | _        | c27.10    | c27.9    | c27.8    | 41    |

| c28.7    | c28.6    | c28.5    | c28.4    | c28.3    | c28.2     | c28.1    | c28.0    | 42    |

| c29.7    | c29.6    | c29.5    | c29.4    | c29.3    | c29.2     | c29.1    | c29.0    | 43    |

| _        | c28.10   | c28.9    | c28.8    | _        | c29.10    | c29.9    | c29.8    | 44    |

| c30.7    | c30.6    | c30.5    | c30.4    | c30.3    | c30.2     | c30.1    | c30.0    | 45    |

| offset.7 | offset.6 | offset.5 | offset.4 | offset.3 | offset.2  | offset.1 | offset.0 | 46    |

| _        | c30.10   | c30.9    | c30.8    | _        | offset.10 | offset.9 | offset.8 | 47    |

| _        | _        | _        | _        | shift.3  | shift.2   | shift.1  | shift.0  | 48    |

Table 2.2 Default Nyquist Filter Coefficients

| Тар | Phase0 | Phase1    | Phase2    | Phase3 |

|-----|--------|-----------|-----------|--------|

| #0  | 0      | 0         | 0         | 0      |

| #1  | 0      | -1        | -1        | 0      |

| #2  | 0      | 0         | 0         | 0      |

| #3  | 0      | 1         | 1         | 1      |

| #4  | -1     | -3        | -3        | -1     |

| #5  | 3      | 5         | 5         | 1      |

| #6  | -4     | <b>-9</b> | <b>-7</b> | -1     |

Table 2.2 Default Nyquist Filter Coefficients (Cont.)

| Тар | Phase0 | Phase1     | Phase2 | Phase3     |

|-----|--------|------------|--------|------------|

| #7  | 8      | 13         | 10     | -1         |

| #8  | -14    | -19        | -13    | 3          |

| #9  | 20     | 28         | 16     | -8         |

| #10 | -31    | -38        | -20    | 15         |

| #11 | 46     | 51         | 23     | -27        |

| #12 | -69    | <b>-71</b> | -26    | 48         |

| #13 | 107    | 105        | 28     | <b>-95</b> |

| #14 | -191   | -184       | -29    | 257        |

| #15 | 593    | 862        | 965    | 862        |

| #16 | 593    | 257        | -29    | -184       |

| #17 | -191   | -95        | 28     | 105        |

| #18 | 107    | 48         | -26    | -71        |

| #19 | -69    | -27        | 23     | 51         |

| #20 | 46     | 15         | -20    | -38        |

| #21 | -31    | -8         | 16     | 28         |

| #22 | 20     | 3          | -13    | -19        |

| #23 | -14    | -1         | 10     | 13         |

| #24 | 8      | -1         | -7     | -9         |

| #25 | -4     | 1          | 5      | 5          |

| #26 | 3      | -1         | -3     | -3         |

| #27 | -1     | 1          | 1      | 1          |

| #28 | 0      | 0          | 0      | 0          |

| #29 | 0      | 0          | -1     | -1         |

| #30 | 0      | 0          | 0      | 0          |

The default offset value for all four phases is 0. To shift the shifter by default, set it to 5 bits.

### 2.11.3 Default Filter Characteristics

Figure 2.20 shows the characteristics of the L64777 default filter.

50 Magnitude Response (dB) 0 -50-100 -1500.1 0.2 0.3 0.4 0.5 0.6 1.0 Normalized Frequency (Nyquist = 1) 0 -2000Phase (degrees) -4000 -6000 -8000 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 0 1.0 Normalized Frequency (Nyquist = 1)

Figure 2.21 Square-Root Raised Cosine Filter

## 2.12 Global Control and PLL Module

The L64777 interface supports serial and parallel input modes at the input interface. The global control generates the clocking for the input and output interfaces; it also controls the data path. It contains all the necessary logic to chain the processing units together.

The global control manages the output data stream so that it is continuous (no gaps between the symbols), assuming that the incoming data rate is constant (on average). To achieve this, a PLL must derive the output clock OCLK from the input transport stream rate.

The PLL module consists of two independent clock dividers for ICLK and OCLK. The dividers are 15-bit binary counters that have a count sequence length that is programmable through Registers 7 through 10.

The default values written by the external microprocessor are: OCLK divider = 32, ICLK divider = 6 for 64 QAM.

## 2.12.1 Numerically Controlled Oscillator (NCO)

In PLL Mode 2, an NCO generates the internal clocking (OCLK, SCLK) and the control information for the interpolator. The NCO is locked to ICLK clock and operates with the processing clock PCLK provided from L64724. PCLK must be at least twice as fast as the necessary OCLK.

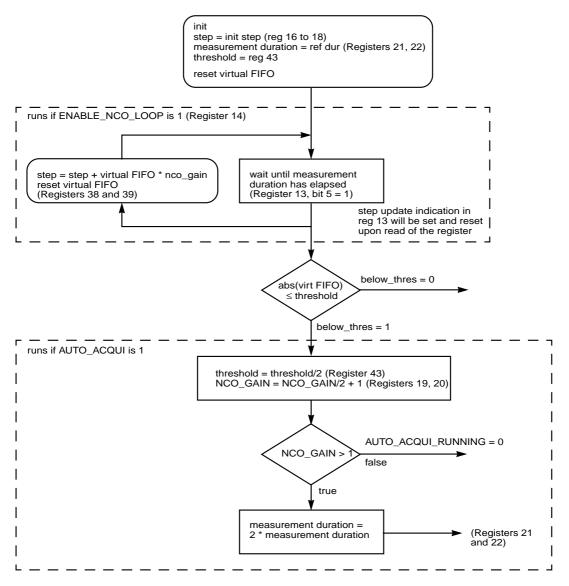

To lock the loop with low jitter, program the NCO with a frequency close to the ideal value obtained from the formulae given for the other PLL modes. A phase loop in a second step does the fine regulation (see Figure 2.22).

To find the required initial frequency, the device supports two modes: a frequency measurement unit, and an automated frequency acquisition. These are described in the following sections.

NPCLK. Frequency N\_COUNT, NP\_COUNT, Measurement Unit NM\_COUNT Step Correction **ICLK** Virtual FIFO for Automatic 58 Threshold If Serial Frequency Acquisition Byte Clock Phase Loop CNT I CNT O **OCLK** Divider Divider Interpolator **EXOR** Ctrl phase\_gain NCO enable\_phase\_loop = Step (for Frequency Selection)

Figure 2.22 NCO Loop Diagram

## 2.12.2 Acquisition Phase Using the Frequency Measurement Unit

During the acquisition phase, the NCO bases the measurement on the assumption that the byte clock on the ICLK input has a duration of either of n-1, n, or n+1 PCLK cycles and that the input stays within these bounds for the duration of the measurement. You can program the duration in multiples of 256-byte clock cycles in the REF\_DUR register (see Section 4.2.7, "Registers 21 and 22," page 4-14). The NCO control register (see Section 4.2.3, "Register 14," page 4-12) can control the start of the measurement, and the Measurement Done bit in register 13 indicates successful completion. If bit 2 of Register 14 enables an interrupt, the measurement generates it.

After completion of the measurement, the host reads the number of byte clock cycles found with the appropriate length of n, n + 1 and n - 1 (from NM\_COUNT, N\_COUNT, NP\_COUNT—see Sections 4.2.10 through 4.2.12), as well as the value of n (from N\_PCLK—see Section 4.2.9).

The host computes the following formulae to get the initial step for phase 2, where ñ indicates the average n value.

Equation 2.3

$$\tilde{n} = \frac{(C1(n-1) + C2(n) + C3(n+1))}{(C1 + C2 + C3)}$$

and from this:

**Equation 2.4** initial step =

$$\frac{2^{24}}{\tilde{n}} \frac{32}{Id(QAMmode)} \frac{\text{Sync length}}{\text{valid bytes}}$$

In the above formulae:

- C1 is the reading from NM\_COUNT register.

- C2 is the reading from N\_COUNT register.

- C3 is the reading from NP\_COUNT register.

- n is the reading from N\_PCLK register.

- Sync length is the number of ICLK cycles between sync bytes (for example, 204).

- Valid bytes are the number of valid bytes during the sync interval (for example, 188).

- Id(QAMmode) is the number of bits per QAM symbol.

If the RS encoder is enabled in DVB mode and the SPI interface of L64724 is programmed to Mode 2, the factor of sync length by valid bytes becomes one.

In order to get an accurate initial step, the measurement must run for a long duration. A recommended duration is 250 ms.

In general the OCLK frequency is calculated as

$$f_{OCLK} = f_{PCLK} \cdot \frac{step}{2^{24}}$$

.

Above,  $0 < step < 2^{23} - 1$ .

Start measurement by toggling the "start measurement" bit (bit 6) in the NCO control register 14. If the NCO control register is enabled for interrupt (through bit 2 of Register 14), an interrupt indicates completion.

## 2.12.3 Autoacquisition Mode

To ease the usage of phase 1, the NCO can use an automatic frequency acquisition. Enable regulation of the NCO\_LOOP\_ENABLE (bit 5) and set the AUTO\_ACQUI bit (bit 3) in the NCO control register. Figure 2.23 outlines the parameter usage during automatic frequency acquisition.