# LS6505

LSI Computer Systems, Inc. 1235 Walt Whitman Road, Melville, NY 11747 (631) 271-0400 FAX (631) 271-0405

November 2002

## PIR SENSOR INTERFACE

## **FEATURES:**

- · Direct Interface with PIR Sensor

- Two-Stage Differential Amplifier

- · Amplifier Gain and Bandwidth externally controlled

- Window Comparator and Digital Filter limit Noise

- · Triac Output Drive

- Programmable Output Duration Timer

- Selectable Dead Time

- Single or Dual Pulse Detection

- Timing derived from 50Hz/60Hz AC

- Motion Detection LED Indicator

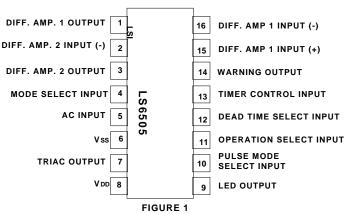

- LS6505 (DIP), LS6505-S (SOIC)- See Figure 1

#### **APPLICATIONS:**

Wall and ceiling mounted occupancy sensors providing energy savings and convenience.

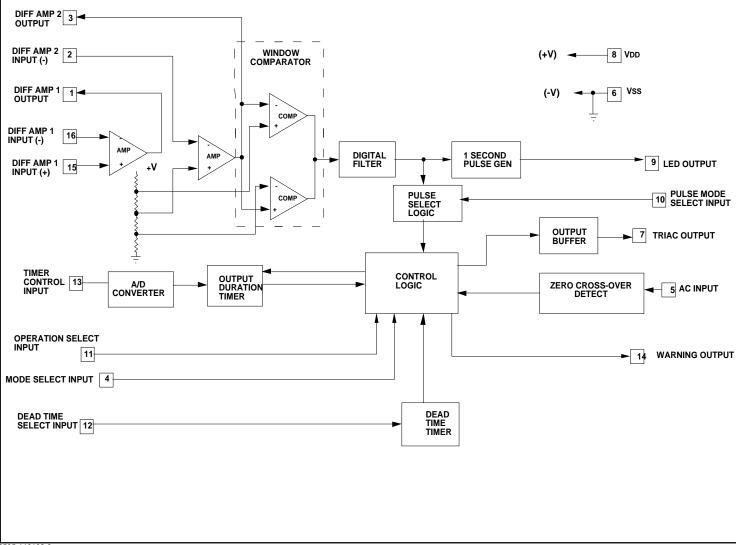

#### **DESCRIPTION** (See Figure 2)

The LS6505 is a CMOS integrated circuit, designed for detecting motion from a PIR Sensor and initiating appropriate responses.

## **DIFFERENTIAL AMPLIFIER**

Each stage of the two stage Differential Amplifier can be set to have its own amplification and bandwidth. The two inputs to the first stage allow for single ended or differential connection to PIR Sensors. This stage can be biased anywhere in its dynamic range. The second stage is internally biased so that the Window Comparator's lower and higher thresholds can be fixed relative to this bias.

## WINDOW COMPARATOR

The Window Comparator provides noise filtering by enabling only those signals equal to or greater than a fixed threshold at the output of the Differential Amplifier to appear at the output of the Window Comparator.

## **COMPARATOR DIGITAL FILTER**

The output of the Window Comparator is filtered so that motion must be present for a certain duration before it can be recognized and appear as pulses at the Digital Filter output.

## SINGLE PULSE / DUAL PULSE MODES

The logic level at the Pulse Mode Select input selects Single Pulse (SP) or Dual Pulse (DP) mode. The trigger for the Output Duration Timer is generated by requiring one (SP Mode) or two (DP Mode) pulses to be present at the Digital Filter output within a specified time period. SP Mode = 0; DP Mode = 1

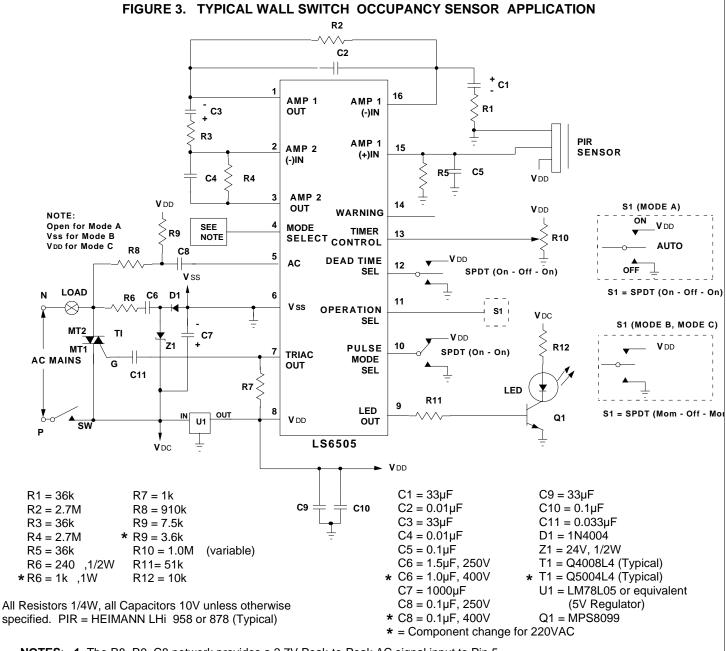

## **OUTPUT DURATION TIMER** (See Table 1 and Figure 3)

The timeout is selected by the voltage level at the Timer Control input. The Timer's trigger is generated from pulses at the Digital filter output. In Auto operation, the Timer controls the On duration of the Triac output and is retriggerable.

## **DEAD TIME** (See Table 2)

False turn-ons are prevented from occurring by establishing a Dead Time between the end of the timeout of the Output Duration Timer and the retriggering of that Timer.

#### **PIN ASSIGNMENT - TOP VIEW**

#### TRIAC OUTPUT

This open drain output turns On when the Output Duration Timer is triggered. The output drives a Triac gate. With the Output Duration Timer On and a 2.7V P-P 60Hz signal applied to the AC input, this output produces a negative going pulse in each half-cycle delayed a nominal 1.2ms from the zero crossing. There is no more than 150us difference between the zerocrossing delay of each pulse.

## **WARNING OUTPUT**

This output goes high for 2 sec beginning 7.5 sec before the Triac output turns off. This signal can be used to trigger an audible or visual alert.

## **LED OUTPUT** (See Figure 3)

Normally, the status of the LED output is opposite to the Triac output, but in Auto operation the LED output flashes on for one second whenever motion is detected.

#### MODE SELECT

Open = Mode A, Vss = Mode B, VDD = Mode C

#### **OPERATION SELECT** (See Figure 3, S1)

The 3-state Operation Select input determines the operation of LS6505 in accordance with the selected Mode as shown below:

| Input | Mode A | Mode B          | Mode C |

|-------|--------|-----------------|--------|

| VDD   | On     | (1)             | (3)    |

| Open  | Auto   | Prior Condition | Auto   |

| Vss   | Off    | (2)             | (4)    |

- (1) Momentary application of VDD turns on the Triac output and starts Auto operation. After the Triac output is off for 15 seconds, Auto operation terminates.

- (2) Momentary application of Vss turns off the Triac output.

- (3) Same as (1) except that Auto operation does not terminate.

- (4) Same as (2) except that after the Triac output is off for 8 seconds, Auto operation begins.

| ABSOL | UTF | MAXI | MHM | RAT | NGS. |

|-------|-----|------|-----|-----|------|

|       |     |      |     |     |      |

| PARAMETER             | SYMBOL    | VALUE                    | UNIT |

|-----------------------|-----------|--------------------------|------|

| DC supply voltage     | VDD - VSS | +5.5                     | V    |

| Any input voltage     | VIN       | Vss - 0.3  to  Vdd + 0.3 | V    |

| Operating temperature | TA        | -40 to +85               | °C   |

| Storage temperature   | Тsтg      | -65 to +150              | °C   |

## **ELECTRICAL CHARACTERISTICS:**

(All voltages referenced to Vss,  $TA = -40^{\circ}C$  to  $+55^{\circ}C$ , 4.5V VDD 5.5V, unless otherwise specified.)

| (g                                                                                                                                      |            |              |            |        |          |                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------|------------|--------------|------------|--------|----------|-----------------------------------------------------------------------------|

| PARAMETER<br>SUPPLY CURRENT:                                                                                                            | SYMBOL     | MIN          | TYP        | MAX    | UNIT     | CONDITIONS                                                                  |

| VDD = 5V                                                                                                                                | IDD        | _            | 150        | 200    | μA       | Triac and LED                                                               |

| VDD = 4.5V - 5.5V                                                                                                                       | IDD        | _            | 180        | 240    | μA       | outputs not loaded                                                          |

| 100 - 4.00                                                                                                                              | 100        |              | 100        | 210    | μπ       | culpute not loaded                                                          |

| DIFFERENTIAL AMPLIFIERS                                                                                                                 |            |              |            |        |          |                                                                             |

| Open Loop Gain, Each Stage                                                                                                              | G          | 70           |            |        | dB       |                                                                             |

|                                                                                                                                         |            |              | -          | -      |          | -                                                                           |

| Common Mode Rejection Ratio                                                                                                             |            | 60           | -          | -      | dB       | -                                                                           |

| Power Supply Rejection Ratio                                                                                                            | PSRR       | 60           | -          | -      | dB       | -                                                                           |

| Output Drive Current                                                                                                                    | lD         | -            | -          | 25     | μΑ       | -                                                                           |

| Input Sensitivity<br>(Minimum Detectable Voltage<br>to first amplifier when both<br>amplifiers are cascaded for<br>a net gain of 5,000) | Vs         | 100          | -          | -      | μV       | TA = 25°C, with Amplifier<br>Bandpass configuration<br>as shown in Figure 3 |

| Input Dynamic Range                                                                                                                     | -          | 0            | -          | 2.5    | V        | -                                                                           |

| Diff. Amp 2 Internal<br>Reference                                                                                                       | VIR        | -            | 0.4VR      | -      | V        | -                                                                           |

| COMPARATOR:                                                                                                                             |            |              |            |        |          |                                                                             |

| Lower Reference                                                                                                                         | VTHL       | _            | VIR - 0.5V | _      | V        | _                                                                           |

|                                                                                                                                         | VTHH       | -            | VIR + 0.5V | -      | V        | -                                                                           |

| Higher Reference                                                                                                                        | VIHH       | -            | VIR + 0.5V | -      | V        | -                                                                           |

| DIGITAL FILTER:<br>Input Pulse Width<br>(for recognition)                                                                               | Tpw<br>Tpw | 66.3<br>79.6 | -<br>-     | -<br>- | ms<br>ms | 60Hz operation<br>50Hz operation                                            |

| OUTPUT DRIVE CURRENT:                                                                                                                   |            |              |            |        |          |                                                                             |

| Triac                                                                                                                                   | lo         | -40          | -          | -      | mA       | With 3V Triac Gate                                                          |

| Warning: Source Current                                                                                                                 | lw +       | 2            | -          | -      | mA       | Vo =VDD - 0.5V                                                              |

| Sink Current                                                                                                                            | lw -       | 1            | -          | -      | mA       | Vo = 0.3V Max                                                               |

| TRIAC OUTPUT TIMING:                                                                                                                    |            |              |            |        |          |                                                                             |

| Pulse Width                                                                                                                             | TTPW       | 20           | 30         | 45     | μs       | VDD = 5V, $f = 60Hz$ and                                                    |

| Delay from zero crossover                                                                                                               | Tod        | 1.00         | 1.2        | 1.32   | ms       | 2.7V P-P AC input                                                           |

| Delay difference between zero crossovers                                                                                                | Todd       | -            | -          | 150    | μs       | f = 60Hz                                                                    |

| Zeio (10330vei3                                                                                                                         |            |              |            |        |          |                                                                             |

| AC INPUT IMPEDANCE                                                                                                                      | ZAC        | 270          | -          | -      | k        | -                                                                           |

| LED OUTPUT:                                                                                                                             |            |              |            |        |          |                                                                             |

| Source Current                                                                                                                          | ls+        | 2            | -          | -      | mA       | Vo = VDD - 0.5V                                                             |

| Sink Current                                                                                                                            | Is-        | _<br>1       | _          | _      | mA       | Vo = 0.3V                                                                   |

| Sink Guiten                                                                                                                             | 10-        | •            |            |        | 1117 (   | vo = 0.5 v                                                                  |

| Pulse Width                                                                                                                             | TLPW       | 0.75         | 1          | 1.25   | sec      | f = 60Hz                                                                    |

| DUAL PULSE MODE:                                                                                                                        |            |              |            |        |          |                                                                             |

| Time between pulse-pairs for motion recognition                                                                                         | TR         | -            | -          | 5.125  | sec      | f = 60Hz                                                                    |

| 101 motion recognition                                                                                                                  |            |              |            |        |          |                                                                             |

## TABLE 1 **OUTPUT DURATION TIMER AS A FUNCTION OF TIMER CONTROL INPUT VOLTAGE**

(f = Frequency at AC input)

| INPUT VOLTAGE | f = 50Hz | f = 60Hz | UNIT |

|---------------|----------|----------|------|

| 0             | 18       | 15       | sec  |

| 1/16 VDD      | 36       | 30       | sec  |

| 2/16 VDD      | 54       | 45       | sec  |

| 3/16VDD       | 72       | 60       | sec  |

| 4/16 VDD      | 2.4      | 2        | min  |

| 5/16 VDD      | 3.6      | 3        | min  |

| 6/16 VDD      | 4.8      | 4        | min  |

| 7/16 VDD      | 6        | 5        | min  |

| 8/16 VDD      | 7.2      | 6        | min  |

| 9/16 VDD      | 8.4      | 7        | min  |

| 10/16 VDD     | 9.6      | 8        | min  |

| 11/16VDD      | 10.8     | 9        | min  |

| 12/16 VDD     | 12       | 10       | min  |

| 13/16 VDD     | 14.4     | 12       | min  |

| 14/16 VDD     | 16.8     | 14       | min  |

| 15/16 VDD     | 18       | 15       | min  |

## **TABLE 2 DEAD TIME DURATION AS A FUNCTION OF THE** STATE OF DEAD TIME SELECT INPUT

(f = Frequency at AC input)

| INPUT STATE | f = 50Hz | f = 60Hz | UNIT |

|-------------|----------|----------|------|

| 0           | 0        | 0        | sec  |

| OPEN        | 1.2      | 1        | sec  |

| 1           | 2.4      | 2        | sec  |

The information included herein is believed to be accurate and reliable. However, LSI Computer Systems, Inc. assumes no responsibilities for inaccuracies, nor for any infringements of patent rights of others which may result from its use.

## FIGURE 2. LS6505 BLOCK DIAGRAM

6505-110102-3

NOTES: 1. The R8, R9, C8 network provides a 2.7V Peak-to-Peak AC signal input to Pin 5.

- 2. The C7, D1, Z1, C6, R6 components generate the DC Supply Voltage for the LS6505.

- **3.** The R1, C1, R2, C2, R3, C3, R4, C4, R5, C5 components and the two on-chip Differential Amplifiers set a nominal gain of 5,500 with bandpass filtering of 0.13Hz to 6Hz.

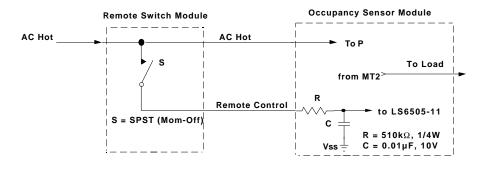

FIGURE 4. ADAPTING WALL SWITCH FOR 3-WAY OPERATION

When operated in Mode B or Mode C, the wall switch occupancy sensor shown in Figure 3 can easily be adapted to operate with a remote switch by adding an R-C network to the occupancy sensor module. R limits the current from the remote module into Pin 11 of the LS6505 and C suppresses noise.