## Data Sheet

## 2.0GHz - 2.7GHz 250mW Power Amplifier

The Intersil HFA3926 is an integrated power amplifier in a low cost SSOP 28 plastic package. The power amplifier delivers +27dB of gain with high efficiency and can be operated with

voltages as low as 2.7V.

intersil

The HFA3926 is ideally suited for QPSK, BPSK or other linearly modulated systems in the 2.4GHz Industrial, Scientific, and Medical (ISM) frequency band. It can also be used in GFSK systems where levels of +25dBm are required. Typical applications include Wireless Local Area Network (WLAN) and Wireless Local Loop systems.

REMEMBER: Always apply Negative power to the VG pins before applying the Positive  $V_{DD}$  bias. Failure to do so may result in the destruction of the HFA3926 Power Amplifier.

## **Ordering Information**

| PART NUMBER | TEMP.<br>RANGE ( <sup>o</sup> C) | PACKAGE       | PKG.<br>NO. |

|-------------|----------------------------------|---------------|-------------|

| HFA3926IA   | -40 to 85                        | 28 Ld SSOP    | M28.15      |

| HFA3926IA96 | -40 to 85                        | Tape and Reel |             |

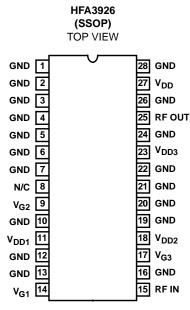

## Pinout

### Features

- · Highly Integrated Power Amplifier

- Operates Over 2.7V to 6V Supply Voltage

- High Linear Output Power (P<sub>1dB</sub>: +24.5dBm)

- Low Cost SSOP-28 Plastic Package

## Applications

- Wireless Local Loop Systems

- Systems Targeting IEEE 802.11 Standard

- TDD Quadrature-Modulated Communication Systems

- Wireless Local Area Networks

- PCMCIA Wireless Transceivers

- · ISM Systems

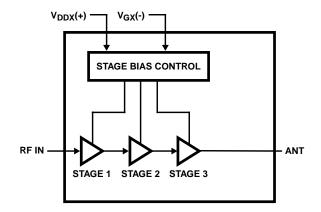

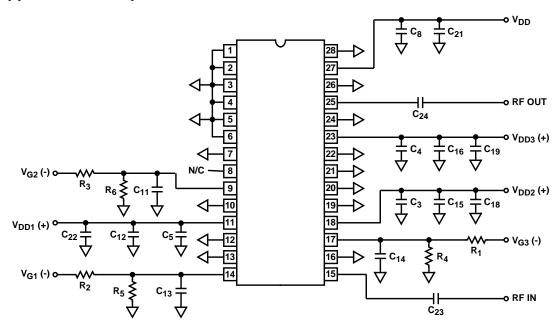

# Functional Block Diagram

# Pin Description

| PINS  | SYMBOL           | DESCRIPTION                                                                                                                                                                                 |

|-------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | GND              | DC and RF Ground.                                                                                                                                                                           |

| 2     | GND              | DC and RF Ground.                                                                                                                                                                           |

| 3     | GND              | DC and RF Ground.                                                                                                                                                                           |

| 4     | GND              | DC and RF Ground.                                                                                                                                                                           |

| 5     | GND              | DC and RF Ground.                                                                                                                                                                           |

| 6     | GND              | DC and RF Ground.                                                                                                                                                                           |

| 7     | GND              | DC and RF Ground.                                                                                                                                                                           |

| 8     |                  | No connect.                                                                                                                                                                                 |

| 9     | V <sub>G2</sub>  | Negative bias control for the second PA stage, adjusted to set $V_{DD2}$ quiescent bias current, which is typically 53mA. Typical voltage at pin = -0.75V. Input impedance: > 1M $\Omega$ . |

| 10    | GND              | DC and RF Ground.                                                                                                                                                                           |

| 11    | V <sub>DD1</sub> | Positive bias for the first stage of the PA, 2.7V to 6V.                                                                                                                                    |

| 12    | GND              | DC and RF Ground.                                                                                                                                                                           |

| 13    | GND              | DC and RF Ground.                                                                                                                                                                           |

| 14    | V <sub>G1</sub>  | Negative bias control for the first PA stage, adjusted to set $V_{DD1}$ quiescent bias current, which is typically 20mA. Typical voltage at pin = -0.75V. Input impedance: > 1M $\Omega$ .  |

| 15    | RF IN            | RF Input of the Power Amplifier.                                                                                                                                                            |

| 16S   | GND              | DC and RF Ground.                                                                                                                                                                           |

| 17    | V <sub>G3</sub>  | Negative bias control for the third PA stage, adjusted to set $V_{DD3}$ quiescent bias current, which is typically 90mA. Typical voltage at pin = -0.95V. Input impedance: > 1M $\Omega$ .  |

| 18    | V <sub>DD2</sub> | Positive bias for the second stage of the PA. 2.7V to 6V.                                                                                                                                   |

| 19-22 | GND              | DC and RF Ground.                                                                                                                                                                           |

| 23    | V <sub>DD3</sub> | Positive bias for the third stage of the PA. 2.7V to 6V.                                                                                                                                    |

| 24    | GND              | DC and RF Ground.                                                                                                                                                                           |

| 25    | RF OUT           | RF output of power amplifier.                                                                                                                                                               |

| 26    | GND              | DC and RF Ground.                                                                                                                                                                           |

| 27    | V <sub>DD</sub>  | V <sub>DD</sub> .                                                                                                                                                                           |

| 28    | GND              | DC and RF Ground.                                                                                                                                                                           |

NOTE: Process variation will effect  $V_{G3}$  voltage requirement to develop 90mA stage 3 quiescent current, maximum range = -0.69V to -1.04V.

### **Absolute Maximum Ratings**

#### **Operating Conditions**

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTES:

- 1. Ambient temperature  $(T_A) = 25^{\circ}C$ .

- 2.  $|V_{DD}| + |V_{GG}|$  not to exceed 12V.

3.  $\theta_{\text{JA}}$  is measured with the component mounted on an evaluation PC board in free air.

#### **Electrical Specifications** T<sub>A</sub> = 25<sup>o</sup>C, Z<sub>0</sub> = 50Ω, V<sub>DD</sub> = +5V, P<sub>IN</sub> = -30dBm, f = 2.45GHz, Unless Otherwise Specified

| PARAMETER                                                                         | MIN  | TYP    | MAX | UNITS |

|-----------------------------------------------------------------------------------|------|--------|-----|-------|

| Power Amplifier Input Frequency Range                                             | 2.0  | -      | 2.7 | GHz   |

| Linear Gain                                                                       |      |        |     |       |

| 2.0GHz - 2.5GHz                                                                   | 27   | 28     | 32  | dB    |

| 2.5GHz - 2.7GHz                                                                   | 23.5 | 27     | -   | dB    |

| VSWR In/Out                                                                       | -    | 1.75:1 | -   |       |

| Input Return Loss                                                                 | -    | -11.3  | -   | dB    |

| Output Return Loss                                                                | -    | -11.3  | -   | dB    |

| Output Power at P <sub>1dB</sub><br>2.0GHz - 2.7GHz                               | 23   | 24.5   | -   | dBm   |

| Second Harmonic at P <sub>1dB</sub>                                               | -    | -20    | 0   | dBc   |

| Third Harmonic at P <sub>1dB</sub>                                                | -    | -30    | -10 | dBc   |

| I <sub>DD</sub> at P1dB (V <sub>DD1</sub> + V <sub>DD2</sub> + V <sub>DD3</sub> ) | -    | 270    | 375 | mA    |

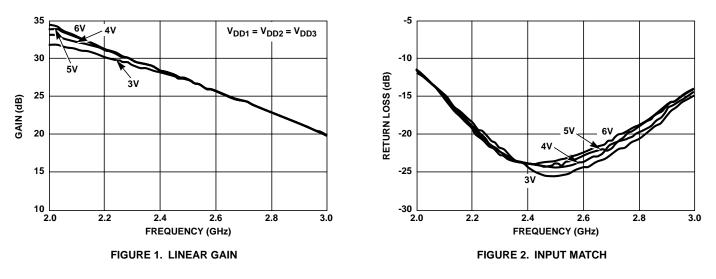

# **Typical Performance Curves**

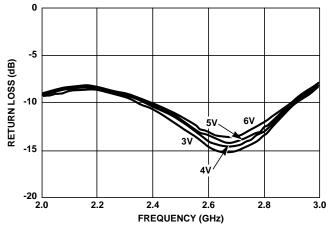

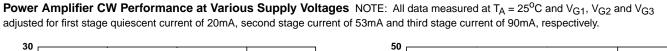

**Power Amplifier Small Signal Performance** NOTE: All data measured at  $T_A = 25^{\circ}C$  and  $V_{G1}$ ,  $V_{G2}$  and  $V_{G3}$  adjusted for first stage quiescent current of 20mA, second stage current of 53mA and third stage current of 90mA, respectively.

### **Thermal Information**

| Thermal Resistance (Typical, Note 3) | $\theta_{JA}$ ( <sup>o</sup> C/W)       |

|--------------------------------------|-----------------------------------------|

| SSOP Package                         | . 88                                    |

| Maximum Storage Temperature Range    | 65 <sup>0</sup> C to 150 <sup>0</sup> C |

## Typical Performance Curves (Continued)

FIGURE 3. OUTPUT MATCH

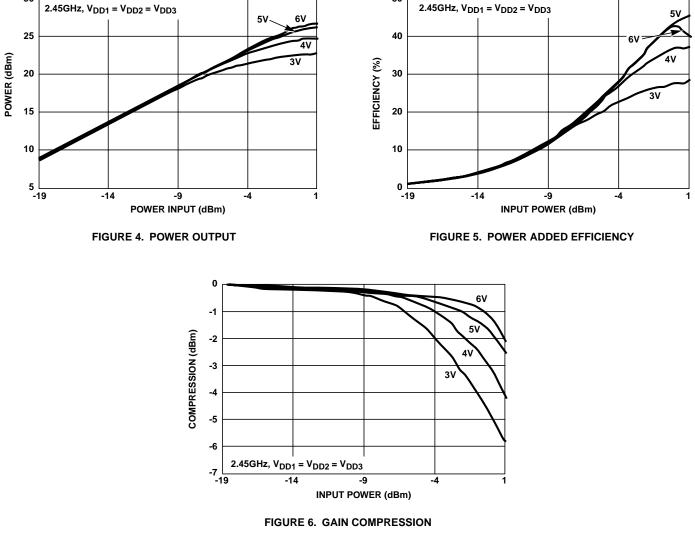

## Typical Performance Curves (Continued)

**Power Amplifier Temperature Performance** NOTE: All data measured at  $T_A = 25^{\circ}C$  and  $V_{G1}$ ,  $V_{G2}$  and  $V_{G3}$  adjusted for first stage quiescent current of 20mA, second stage current of 53mA and third stage current of 90mA, respectively.

FIGURE 9. GAIN COMPRESSION

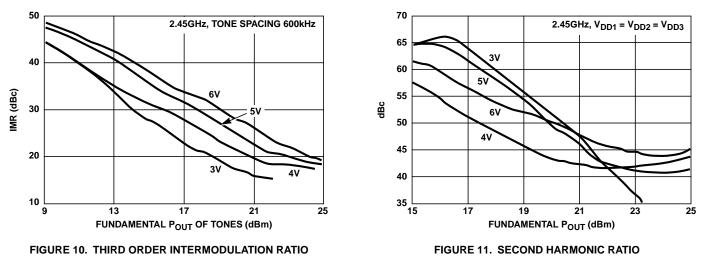

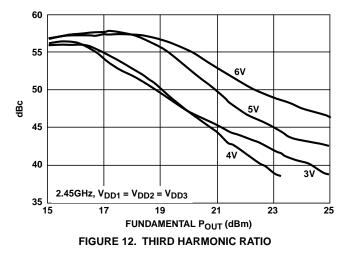

**Power Amplifier Spurious Response at Various Supply Voltages** NOTE: All data measured at  $T_A = 25^{\circ}C$  and  $V_{G1}$ ,  $V_{G2}$  and  $V_{G3}$  adjusted for first stage quiescent current of 20mA, second stage current of 53mA and third stage current of 90mA, respectively.

Typical Performance Curves (Continued)

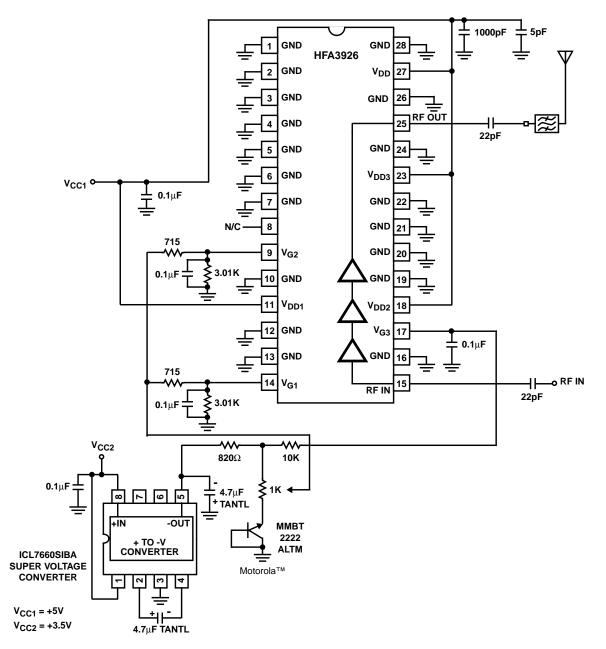

## Typical Application Example

#### EXTERNAL CIRCUITRY PARTS LIST

| LABEL                                                            | VALUE  | PURPOSE                  |

|------------------------------------------------------------------|--------|--------------------------|

| C <sub>3</sub> - C <sub>5,</sub> C <sub>7</sub> , C <sub>8</sub> | 22pF   | Bypass (GHz)             |

| C <sub>23</sub> - C <sub>24</sub>                                | 22pF   | DC Block                 |

| C <sub>11</sub> - C <sub>16</sub>                                | 1000pF | Bypass (MHz)             |

| C <sub>18</sub> - C <sub>22</sub>                                | 0.01µF | Bypass (kHz)             |

| R <sub>1</sub> , R <sub>6</sub>                                  | 1.5kΩ  | FET Gate Divider Network |

| R <sub>3</sub> , R <sub>5</sub>                                  | 5kΩ    |                          |

| R <sub>2</sub>                                                   | 12kΩ   |                          |

| R <sub>4</sub>                                                   | 1kΩ    |                          |

NOTE: All off-chip components are low cost surface mount components obtainable from multiple sources. (0.020in x 0.040in or 0.030in x 0.050in.)

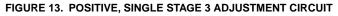

Typical Application Example: Positive Supply, Single Stage 3 Adjustment Circuit

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil semiconductor products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com