# intel

# MCS® 251 Architecture Overview

- Binary Code Compatible with MCS 51<sup>®</sup> Architecture

- 5 to 15 Times Increase in Performance Compared to MCS 251 Microcontroller at the Same Clock Speed

- 3-Stage Pipeline CPU Architecture

- 2 Clocks (1 State) per Instruction

- 16-Bit Internal Code Bus

2 Bytes/State Code Fetch

- 8-Bit ALU

High Speed 8-Bit Source and 16-Bit Destination Bus

- 40 Bytes General Purpose Register File

Accessible as 16 8-Bit, 16 16-Bit or 10 32-Bit Registers

- With Accumulator Functionality and Data Indexing Capability

- 24-Bit Linear Code and Data Addressing

- 64KB Stack Space

- New Instructions and Addressing Modes

- 8, 16 and Limited 32-Bit Data Transfer, Arithmetic and Logical Instructions

- Supports Register, Immediate, Direct, Indirect, Displacement, Relative and Bit Addressing

- Support 64 Interrupt Sources

1 TRAP Instruction Interrupt (Highest Priority)

- 1 Non-Maskable Interrupt (2nd Highest Priority)

- 62 Maskable Interrupt Sources - 4 Interrupt Priority Levels

- Complete Tools Support

- Assemblers and C Compilers

- In-Circuit Emulator

- OTP/EPROM Programmer

- Debuggers

MCS 251 architecture is the next generation of Intel MCS 51 architecture that increases system performance by a factor of five using existing MCS 51 microcontroller code. By rewriting code using the MCS 251 architecture instructions, designers can increase performance up to 15 times.

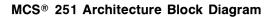

The new MCS 251 architecture brings high performance, an increased memory mix and addressing, low power, low noise, efficient high level language support, enhanced instruction set, integrated features and functionality to the 8-bit embedded control market segment. All products in the family will be built around the new MCS 251 architecture core. They will have various peripherals, memories, input/ouput (I/O) ports, and a BIU (Bus Interface Unit). Most importantly, new proliferations will be binary code-compatible with existing 8051 components. Software investment is protected while providing an easy performance upgrade path. (See table 1 for features and benefits listing.)

Development tools for the MCS® 251 architecture are available from a number of leading tools vendors. For more information, please refer to http://developer.intel.com/design/mcs5; click on Electronic Tools Catalog.

Order Number: 272620-002

| Tabla | 1  | Features | and | <b>Bonofite</b> |

|-------|----|----------|-----|-----------------|

| rable | ι. | reatures | and | Denents         |

| Features                                                                                                                                                                                                                                                                                                   | Benefits                                                                                                                                                                                                                                     |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <ul> <li>3-stage pipeline CPU architecture</li> <li>1 state (2 clocks) per machine cycle (vs 6 states (12 clocks) per machine cycle for MCS<sup>®</sup> 51 microcontroller)</li> <li>16-bit internal code bus</li> </ul>                                                                                   | <ul> <li>High performance. 5 to 15 times increase in<br/>performance compared to MCS 51<br/>microcontroller at the same clock speed</li> <li>High instruction throughput at low clock speed<br/>reduces power consumption and RFI</li> </ul> |  |

| <ul> <li>Enhanced MCS 51 instruction set with:</li> <li>16-bit and limited 32-bit data transfer,<br/>arithmetic and logic instructions</li> <li>Register-to-register operations</li> <li>Extended addressing modes</li> <li>Improved control instructions</li> <li>Bigger bit addressable space</li> </ul> | <ul> <li>Increased performance and programming flexibility.</li> <li>Reduced code size.</li> </ul>                                                                                                                                           |  |

| Binary code-compatible with MCS 51 microcontroller                                                                                                                                                                                                                                                         | <ul> <li>Protects software investment</li> <li>Easy performance upgrade from MCS 51<br/>microcontroller applications</li> </ul>                                                                                                              |  |

| Register-based machine with 40 register bytes<br>accessible as 16 8-bit registers, 16 16-bit<br>registers, 10 32-bit registers or a combination<br>of all. All registers are general-purpose with<br>accumulator functionality and data indexing capability.                                               | <ul> <li>Increased performance and programming<br/>flexibility</li> <li>Increased efficiency for C code</li> </ul>                                                                                                                           |  |

| 24-bit linear addressing for up to 16 MB memory space                                                                                                                                                                                                                                                      | <ul> <li>Support bigger code and data memory<br/>requirement.</li> </ul>                                                                                                                                                                     |  |

| 64 KB extended stack space and additional<br>stack instructions                                                                                                                                                                                                                                            | Increased efficiency for C code                                                                                                                                                                                                              |  |

## **CPU Overview**

The central processing unit (CPU) represents the heart of the MCS 251 architecture and consists of the ALU, instruction sequencer, program counter and the register file, connected by high-speed source and destination buses. The CPU performs all instructions as a series of 8-bit microcontroller operations. The CPU is implemented using typical pipelining techniques, and is built around a three-stage pipeline. The pipe stages are instruction fetch or decode, address generation or data fetch, and execution or write back. The three-stage pipeline implementation offers the best trade-off between performance and design complexity.

### **Memory Interface**

The CPU interfaces with the peripherals, memories and other chip units via internal instruction and data buses. The MCS 251 architecture has an internal 16-bit wide instruction bus capable of sustained 2 bytes/state code fetches. It also has an 8-bit data bus capable of one byte/state data transfer rate.

The MCS 251 architecture has one contiguous 16MB address space that is used for both code and data. The 16MB address space will be partitioned for internal and external access, depending on the amount of on-chip memory.

# intel

Code memory can reside anywhere in the address space except for reserved areas. Further restrictions may prevent code execution from certain locations that may vary from product to product. The code memory resides outside the CPU and will be partitioned as internal and external memory, depending on the amount of on-chip code memory.

Data memory can reside anywhere in the address space except for reserved areas. The lower 32 bytes of the data memory space can be accessed as both data memory and as four banks of general-purpose registers. All MCS 251 controllers will have this memory as part of the CPU; the amount of additional on-chip data memory may vary from product to product.

To provide flexibility to designers during development and production, the MCS 251 microcontroller will have one-time programmable (OTP), ROM and CPU-only versions available. Flash memory versions will be available in the future.

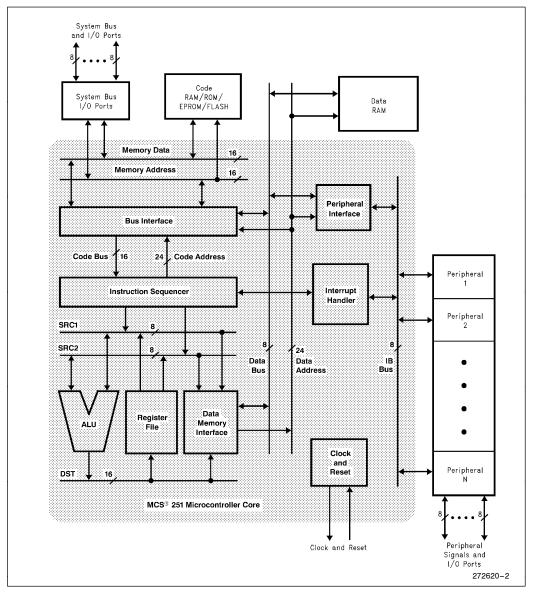

The MCS 251 architecture also supports an extra 32 bytes of general-purpose registers which reside in the CPU as register file. This is in addition to the 4 banks of 8 registers found on the MCS 51 microcontroller architecture. The register file can be addressed in the following ways, depending upon the registers to be accessed: registers 0–15 can be addressed as either byte, word or double word (Dword) registers; registers 16-31 can be addressed as either word or Dword registers; and registers 56-63 can be addressed only as Dword registers. There are 16 possible byte registers, 16 possible word registers and 10 possible Dword registers for register file diagram.)

Figure 1. Register File Diagram

#### MCS 251

#### **New Instruction Set**

The MCS 251 architecture instruction set provides the user with newly-defined instructions that take advantage of the new architecture while maintaining all existing MCS 51 microcontroller instructions. Many of the MCS 251 microcontroller instructions can operate on either 8-, 16-, or limited 32-bit operands. This capability allows the MCS 251 architecture proliferations to be used more easily and efficiently with high-level programming languages such as "C."

The instruction set consists of data instructions, bit instructions and control instructions. Data instructions process 8-, 16-, and limited 32-bit data; bit instructions manipulate bits; and control instructions manage program flow. Each instruction type has a unique set of addressing modes; for example, not all data addressing modes apply to control instructions and vice-versa. The MCS 251 architecture supports the following addressing modes:

| • Register addressing:     | The instruction specifies<br>the register which con-<br>tains the operand.                                  |

|----------------------------|-------------------------------------------------------------------------------------------------------------|

| •Immediate addressing:     | The instruction contains the operand.                                                                       |

| • Direct addressing:       | The instruction contains the operand address.                                                               |

| • Indirect addressing:     | The instruction specifies<br>the register containing<br>operand address.                                    |

| • Displacement addressing: | The sum of the register<br>and a signed offset speci-<br>fied by the instruction is<br>the operand address. |

| • Relative addressing:     | The instruction contains<br>the relative offset from<br>the next instruction to<br>target address.          |

| • Bit addressing:          | The instruction contains the bit address.                                                                   |

#### Interrupt Overview

The MCS 251 architecture supports one non-maskable interrupt, one TRAP (technical return analysis program) instruction interrupt and up to 62 maskable interrupt sources. The user can select each interrupt individually as well as control its priority level. The nonmaskable interrupt is fixed in hardware to always have the second highest priority (after TRAP) and is always enabled. The exact number of interrupt sources, both internal and external, depends on the specific MCS 251 architecture proliferations.

INTA

### Compatibility

The MCS 251 architecture is code-compatible with the MCS 51 architecture. And, all 51 microcontroller instructions are available on the 251. The 51 controllers have four separate address spaces: program memory, special function registers, and internal and external data memory. The 251 incorporates the program memory and the data memory address spaces into a 16MB unified address space. The mapping is completely transparent to the user and is taken care of by the assembler.

### **Future Outlook**

General samples for first product based on the MCS 251 architecture core are anticipated in the first quarter of 1995. This product will be 80C51 pin-compatible and a direct plug-in replacement. Additional products based on the core will include additional peripherals targeted to specific market segments to meet customer needs.

# intel