Data Sheet, DS1, April 2001

NTC-T AM Network Termination Controller (4B3T All Modes) PEB 80900 Version 1.1

Wired Communications

Never stop thinking.

Edition 2001-04-02

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München, Germany © Infineon Technologies AG 2001. All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# NTC-T AM Network Termination Controller (4B3T All Modes) PEB 80900 Version 1.1

Wired Communications

Never stop thinking.

| Revision History:<br>Previous Version: |          | <b>2001-04-02</b> D                 |  |  |

|----------------------------------------|----------|-------------------------------------|--|--|

|                                        |          | Preliminary Data Sheet DS1          |  |  |

| Page                                   | Subjects | (major changes since last revision) |  |  |

|                                        |          |                                     |  |  |

|                                        |          |                                     |  |  |

|                                        |          |                                     |  |  |

|                                        |          |                                     |  |  |

|                                        |          |                                     |  |  |

|                                        |          |                                     |  |  |

|                                        |          |                                     |  |  |

|                                        |          |                                     |  |  |

|                                        |          |                                     |  |  |

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com

| Table of | Contents Pa                                                                                                 | ge |

|----------|-------------------------------------------------------------------------------------------------------------|----|

| 1        | Overview                                                                                                    | 1  |

| 1.1      | Selection between NTC-T and IEC-T Functionality                                                             | 2  |

| 1.2      | Organization of the Document                                                                                |    |

| 1.3      | Pin Configuration of the NTC-T AM with NTC-T and IEC-T Functionality                                        | 4  |

| 1.4      | Pin Definitions and Functions                                                                               | 5  |

| 1.4.1    | Special Pin IFDISC: Interface Disconnect (Available only with TP02 = '011') 9                               |    |

| 1.5      | Functional Differences between PEB 80900 with IEC-T Functionality and PE 20901/2 10                         | B  |

| 1.5.1    | Data Output on IOM                                                                                          | 10 |

| 1.5.2    | Power-On Reset and Undervoltage Detection                                                                   | 10 |

| 1.5.3    | External Circuitry for Connection to the U-Interface                                                        | 10 |

| 1.6      | Editorial Changes between the IEC-T Target Specification [2] and Part II 'IE T' of the NTC-AM Data Sheet 11 | C- |

| 2        | Part I 'NTC-T': Overview                                                                                    | 13 |

| 2.1      | Features                                                                                                    | 14 |

| 2.2      | Logic Symbol                                                                                                | 15 |

| 2.3      | Pin Configuration of the NTC-T AM with NTC-T Functionality                                                  | 16 |

| 2.4      | Pin Definitions and Functions                                                                               | 17 |

| 2.5      | System Integration                                                                                          | 21 |

| 3        | Part I 'NTC-T': Functional Description                                                                      | 23 |

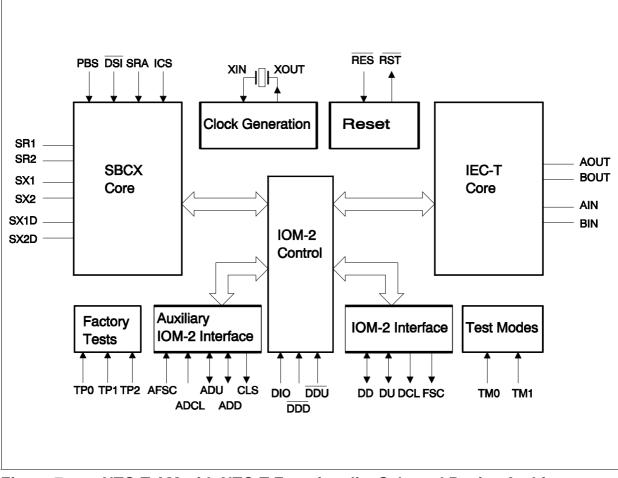

| 3.1      | Device Architecture                                                                                         | 23 |

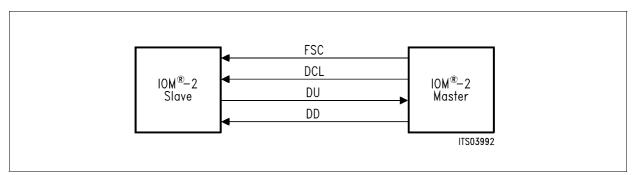

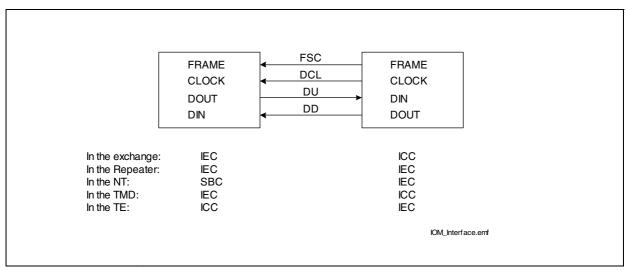

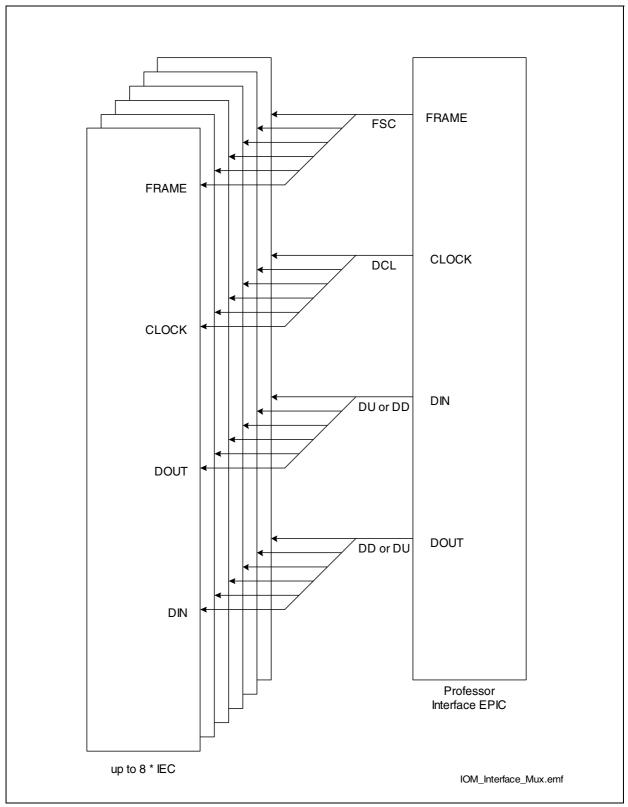

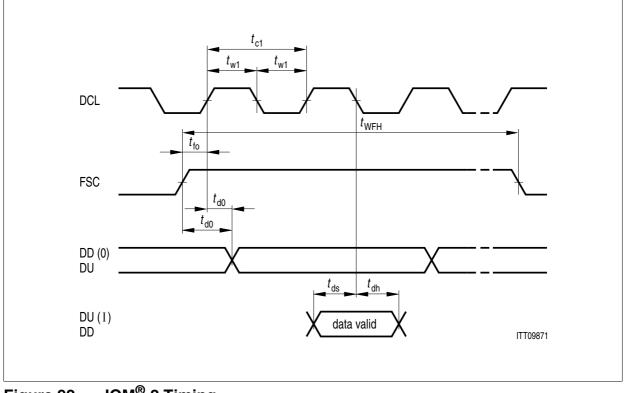

| 3.2      | IOM®-2 Interface                                                                                            |    |

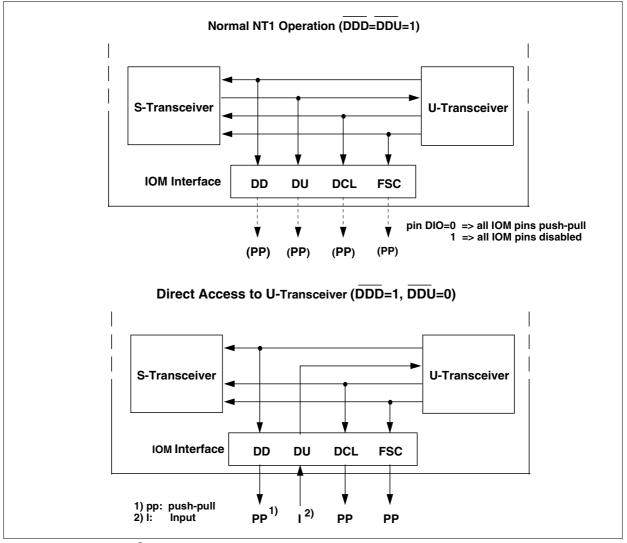

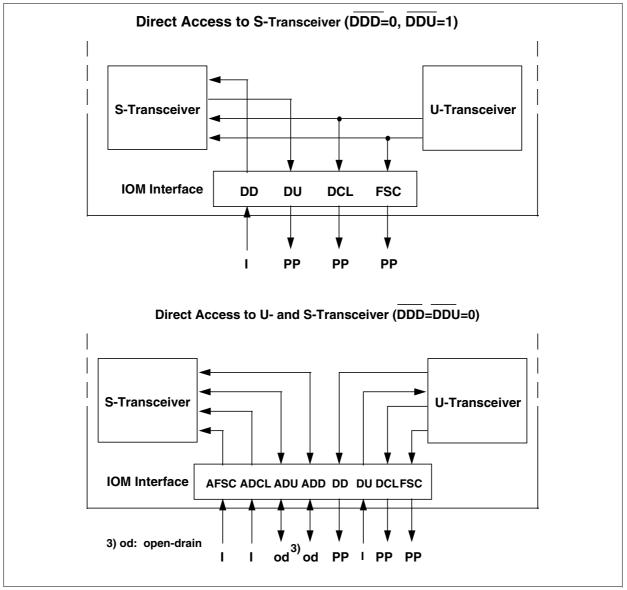

| 3.2.1    | IOM®-2 Configurations                                                                                       | 24 |

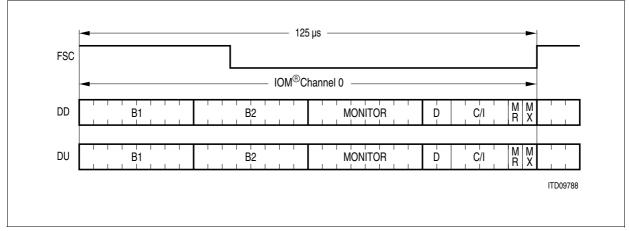

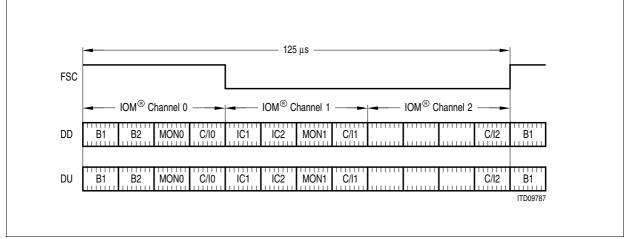

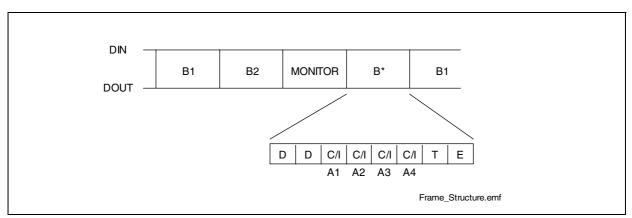

| 3.2.2    | IOM®-2 Frame Structure                                                                                      |    |

| 3.2.2.1  | NT1 Frame Structure (DCL = 512 kHz)                                                                         |    |

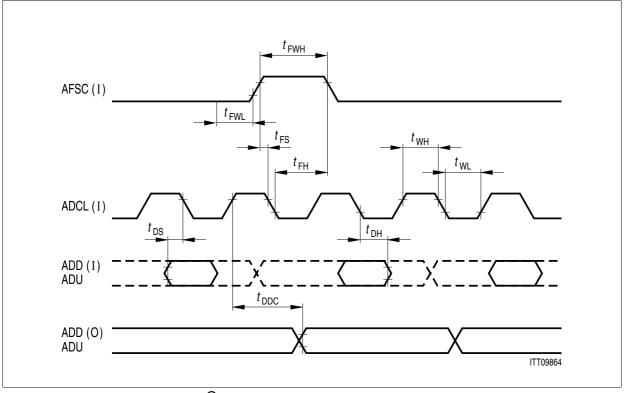

| 3.2.2.2  | TE Frame Structure (ADCL = 1.536 MHz)                                                                       | 28 |

| 3.2.3    | IOM®-2 Command / Indication Channel                                                                         |    |

| 3.2.4    | IOM®-2 Monitor Channel                                                                                      |    |

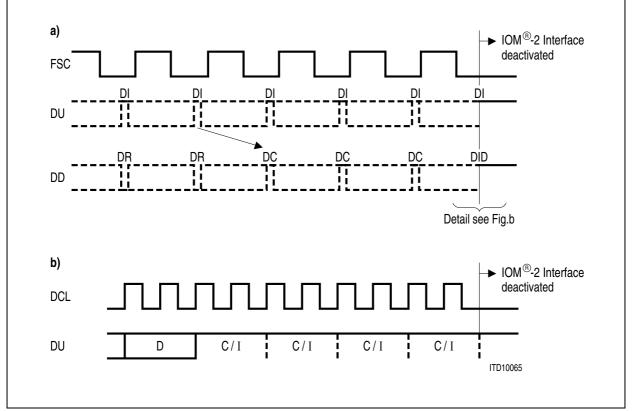

| 3.2.5    | Activation/Deactivation of IOM®-2 Clocks                                                                    |    |

| 3.3      |                                                                                                             | 31 |

| 3.3.1    | General                                                                                                     |    |

| 3.3.2    | Frame Structure of the U-Interface                                                                          |    |

| 3.3.3    | Coding from Binary to Ternary Data                                                                          |    |

| 3.3.4    | Decoding from Ternary to Binary Data                                                                        |    |

| 3.3.5    | Monitoring of Code Violations                                                                               |    |

| 3.3.6    | Scrambler / Descrambler                                                                                     |    |

| 3.3.7    |                                                                                                             | 36 |

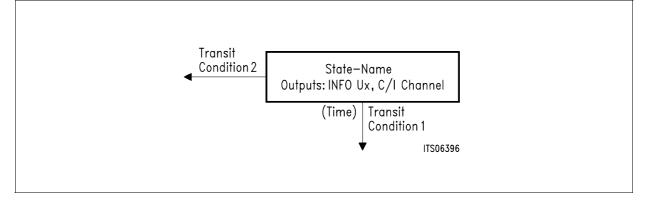

| 3.3.8    | State Machine Notation                                                                                      |    |

| 3.3.9    |                                                                                                             | 38 |

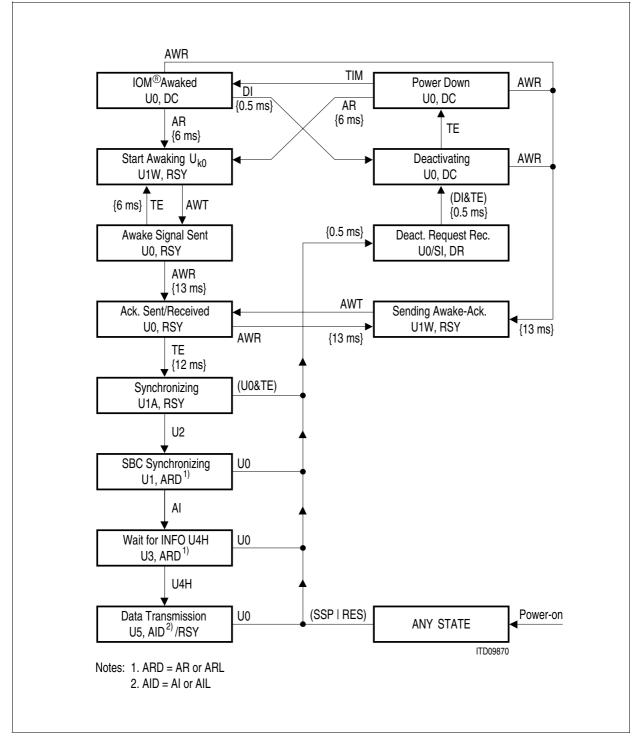

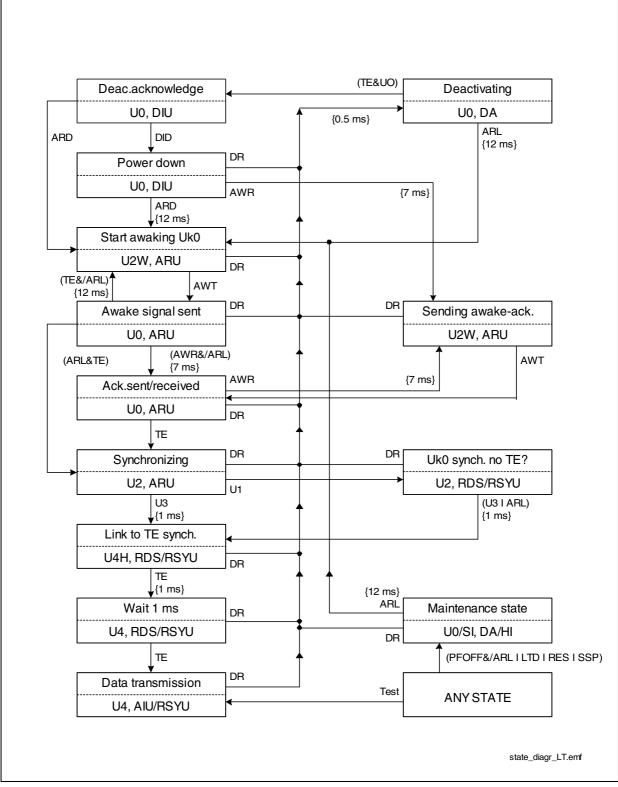

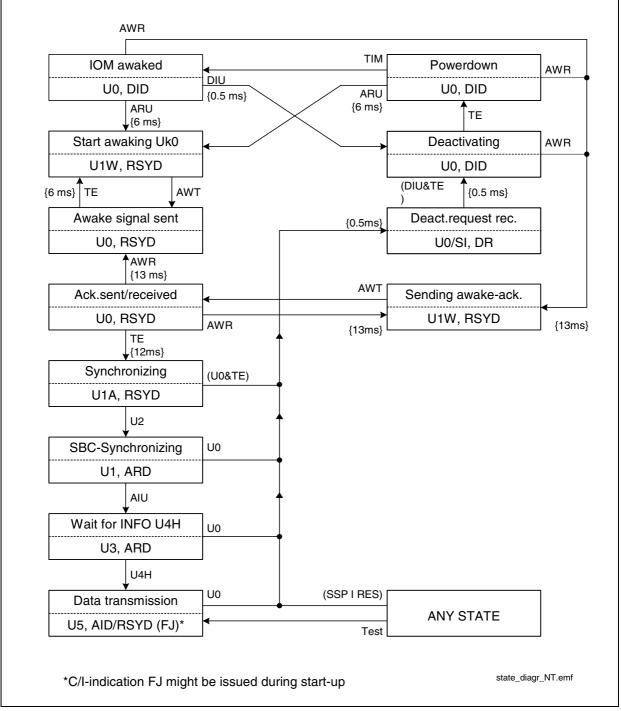

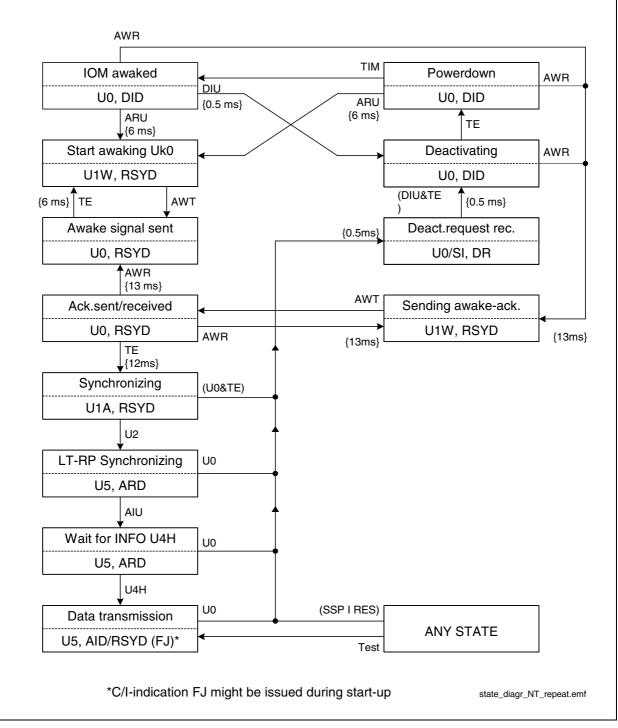

| 3.3.9.1  | NT Mode State Diagram                                                                                       | 38 |

### **Table of Contents**

|                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | U                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

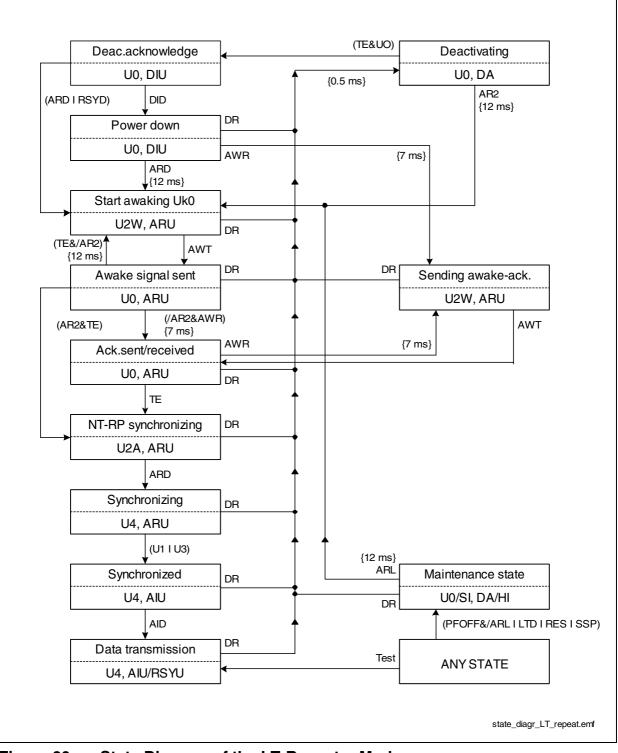

| 3.3.9.2<br>3.3.9.3<br>3.3.9.4<br>3.3.10<br>3.3.11<br>3.3.12<br>3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.4.1<br>3.4.4.2<br>3.4.4.3<br>3.4.4.3<br>3.4.4.3<br>3.4.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.5<br>3.6 | Inputs to the U-Transceiver<br>Outputs of the U-Transceiver<br>NT-States<br>C/I Codes<br>Loop-Back 2<br>Analog Line Port<br>S-Transceiver<br>Modes<br>S/T-Interface Coding<br>State Machine Notation<br>State Machine<br>NT Mode State Diagram<br>Inputs to the S-Transceiver<br>Outputs of the S-Transceiver<br>States<br>C/I Codes<br>Analog Line Port<br>Timing Recovery<br>Reset<br>Test Modes                                                                                                                                                                                                                                                                                                                                                  | $\begin{array}{c} 40\\ 41\\ 43\\ 45\\ 45\\ 48\\ 48\\ 50\\ 51\\ 53\\ 53\\ 55\\ 56\\ 57\\ 58\\ 60\\ 61\\ \end{array}$ |

| <b>4</b><br>4.1<br>4.2<br>4.3                                                                                                                                                                                     | Part I 'NTC-T': Operational DescriptionLayer 1 Activation/DeactivationExternal CircuitryOscillator Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 62<br>67                                                                                                            |

| <b>5</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.4.1<br>5.4.2<br>5.4.3<br>5.4.3<br>5.4.4<br>5.4.5<br>5.4.6<br>5.4.7<br>5.5<br>5.6<br>5.6.1                                                                               | Part II 'IEC-T': General Description<br>Basic System Functions<br>Pin Configuration of the NTC-T AM with IEC-T Functionality<br>Related Documents<br>Operation Modes and Functions<br>The ISDN Telecom IC Family from Siemens<br>PEB 2070 ISDN Communications Controller (ICC)<br>PEB 2080 S-Bus Interface Circuit (SBC)<br>PEB 2085 ISDN Subscriber Access Controller (ISAC-S)<br>PEB 2095 ISDN Burst Transceiver Circuit (IBC)<br>PEB 20950 ISDN Subscriber Access Controller (ISAC-P)<br>PEB 2050 Peripheral Board Controller (PBC)<br>SAB 82520 High Level Serial Communications Controller (HSCC)<br>IOM, Concept and Applications of the IEC<br>Interfaces in the Different Applications of the NTC-T AM with IEC-T Functionality Selected 79 | 70<br>72<br>73<br>74<br>74<br>74<br>74<br>74<br>74<br>74<br>75<br>75<br>75<br>75                                    |

### Table of Contents

| Table of | Contents                                                                                    | Page    |

|----------|---------------------------------------------------------------------------------------------|---------|

| 5.6.2    | Pin Definitions and Functions                                                               | 83      |

| 5.6.3    | Mode Dependent Functions                                                                    | 88      |

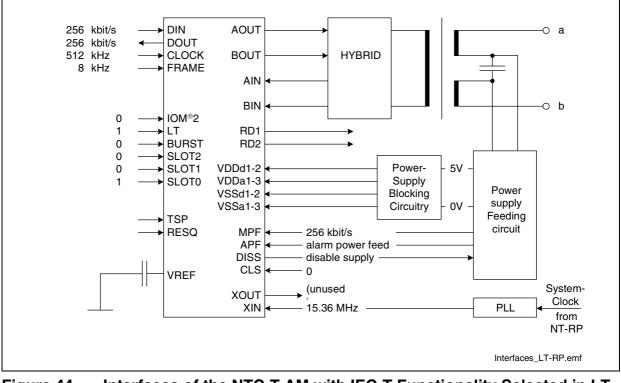

| 5.6.4    | Data and Clocks in LT, LT-RP Mode                                                           | 88      |

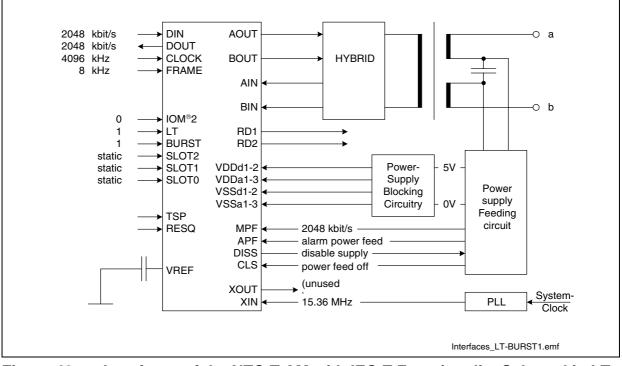

| 5.6.5    | Data and Clocks in LT-BURST1 Mode                                                           | 89      |

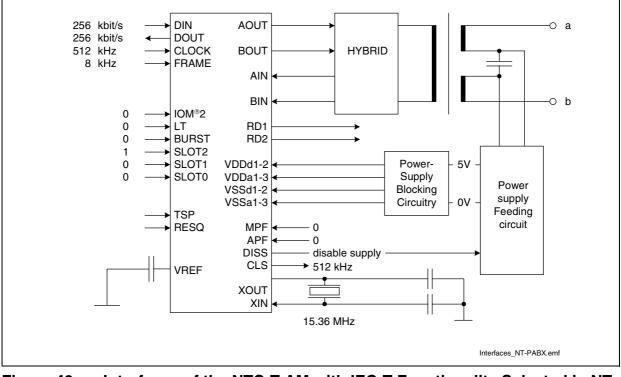

| 5.6.6    | Data and Clocks in NT-PABX Mode                                                             | 89      |

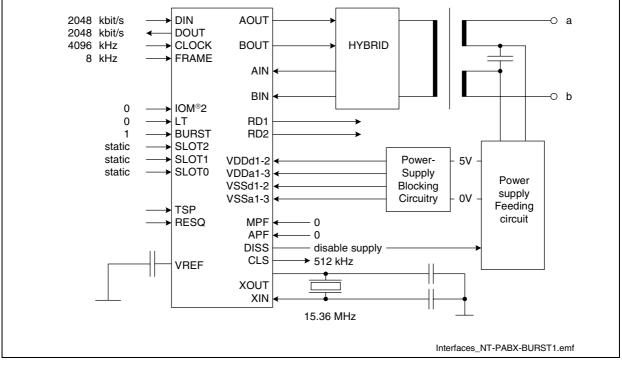

| 5.6.7    | Data and Clocks in NT-PABX BURST1 Mode                                                      | 90      |

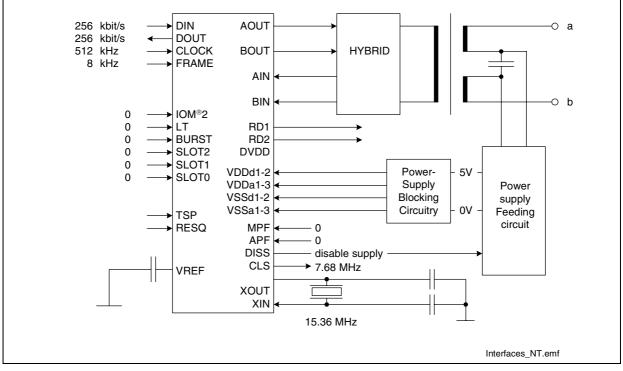

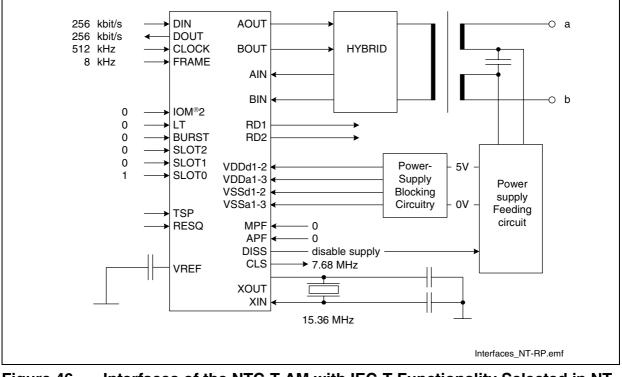

| 5.6.8    | Data and Clocks in NT, NT-RP, NT-TE1 Mode                                                   | 90      |

| 6        | Part II 'IEC-T': Functional Description                                                     |         |

| 6.1      | Description of the Digital Module Interface                                                 |         |

| 6.2      | Frame Structure of the Module Interface                                                     |         |

| 6.3      | Serial I/O Data Format and Timing                                                           |         |

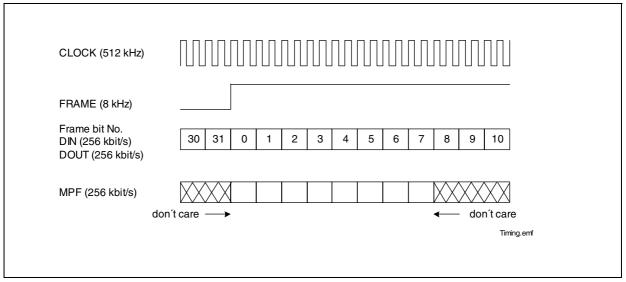

| 6.3.1    | Continuous Modes (256 kbit/s)                                                               |         |

| 6.3.2    | IOM, Multiplexed Modes                                                                      |         |

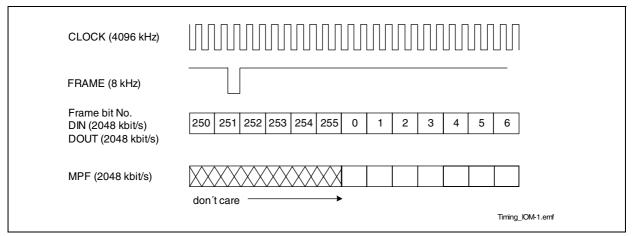

| 6.3.2.1  | IOM,-1 Burst Modes (2048 kbit/s)                                                            |         |

| 6.4      | Synchronous and Deactivated States of the Module Interface                                  |         |

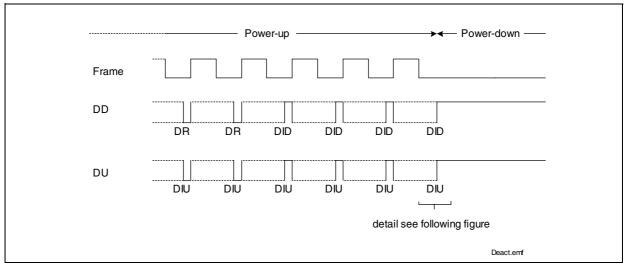

| 6.4.1    | Transition from Synchronous to Power-Down State                                             |         |

| 6.4.2    | Wake-Up of the IOM, Interface Originated by the Downstream Unit .                           |         |

| 6.4.3    | Wake-Up of IOM, Interface Originated by the Upstream Unit                                   |         |

| 6.5      | Clock Generation                                                                            |         |

| 6.5.1    | Master Clock                                                                                |         |

| 6.5.2    | Suggestion for the Generation of the Master Clock in the Repeater .                         |         |

| 6.5.3    | Synchronous Half Master Clock                                                               |         |

| 6.6      | Description of the Line Port                                                                |         |

| 6.6.1    |                                                                                             |         |

| 6.6.2    | Frame Structure of the Uk0-Interface                                                        |         |

| 6.6.3    | Coding from Binary to Ternary Data                                                          |         |

| 6.6.4    | Decoding from Ternary to Binary Data                                                        |         |

| 6.6.5    | Monitoring of Code Violations                                                               |         |

| 6.6.6    | Scrambler / Descrambler                                                                     |         |

| 6.6.7    | Signal Elements used for Activation and Deactivation                                        |         |

| 6.6.8    | Analog Functions of the Line Port                                                           |         |

| 6.7      | Maintenance Functions                                                                       |         |

| 6.7.1    | Loops                                                                                       |         |

| 6.7.1.1  | Switching an Analog Loop in the NTC-T AM with IEC-T Functional<br>lected 106                | ity Se- |

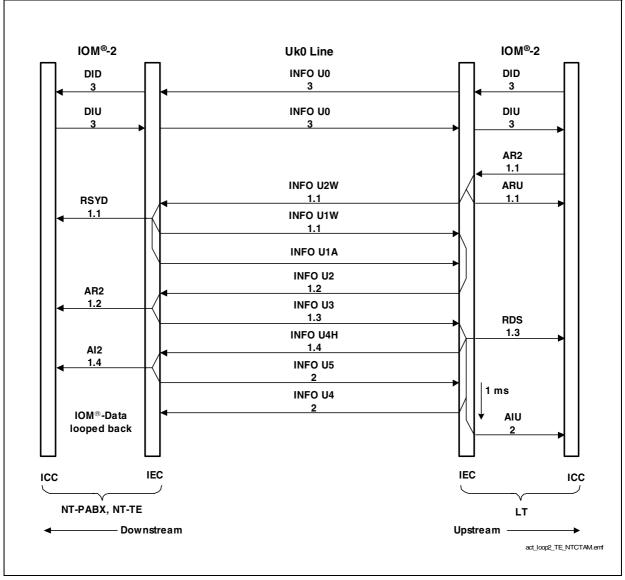

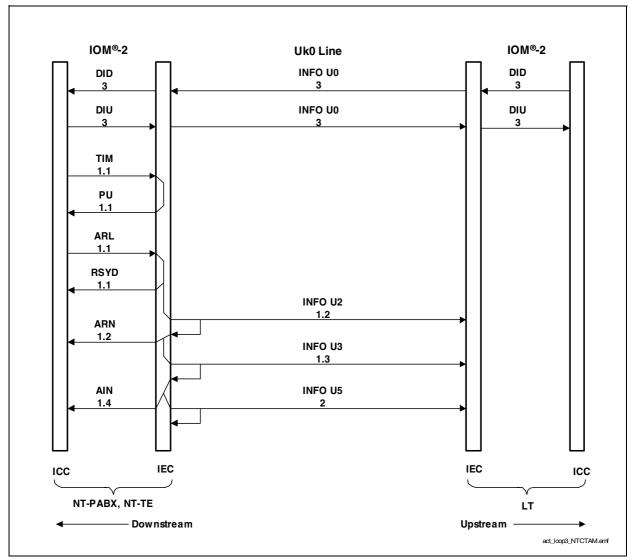

| 6.7.1.2  | Switching Loop 2 in the NTC-T AM with IEC-T Functionality Selec<br>NT-PABX and TE Modes 107 | ted in  |

| 6.7.1.3  | Remote Control of Loop 4 and Loop 2 by the NTC-T AM with IEC-T tionality Selected 107       | Func-   |

| 6.7.2    | Monitoring of Code Violations                                                               | . 108   |

| 6.7.3    | Transparent Maintenance Channel                                                             |         |

| 6.7.4    | Interfaces to the Power Supply Circuit                                                      |         |

|          |                                                                                             |         |

| Table of                                                                                                                                       | Contents Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.7.4.1<br>6.7.4.2<br>6.7.4.3<br>6.7.5                                                                                                         | Scanning of Measured Values (MPF)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

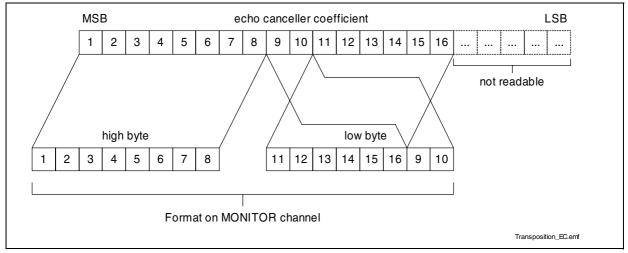

| 6.7.5.1<br>6.7.6                                                                                                                               | Access to MONITOR Channel in the IOM,-1 Mode 111<br>Readout Format of Echocanceller Coefficients 111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

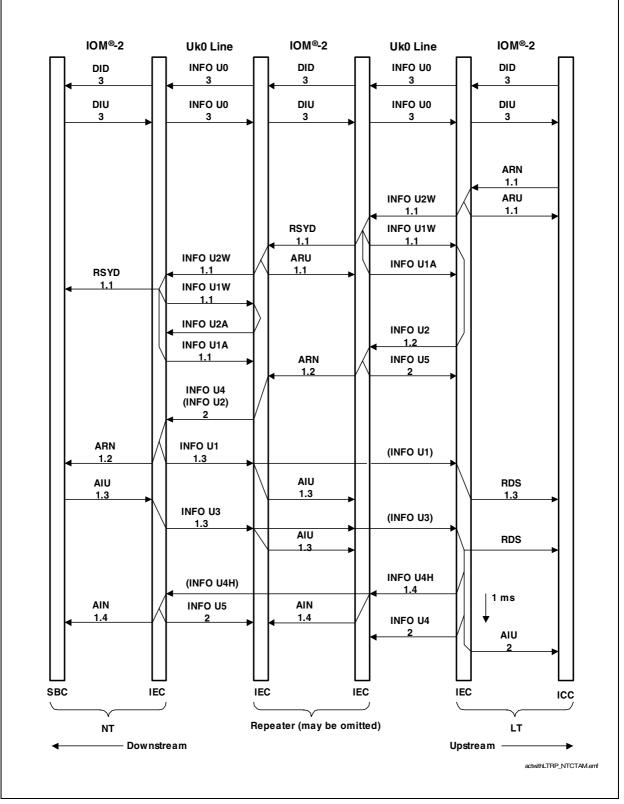

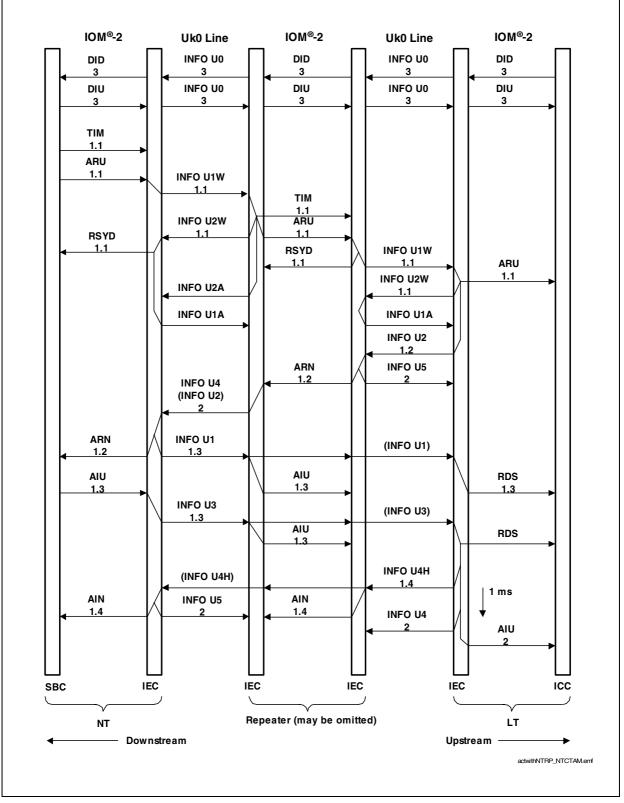

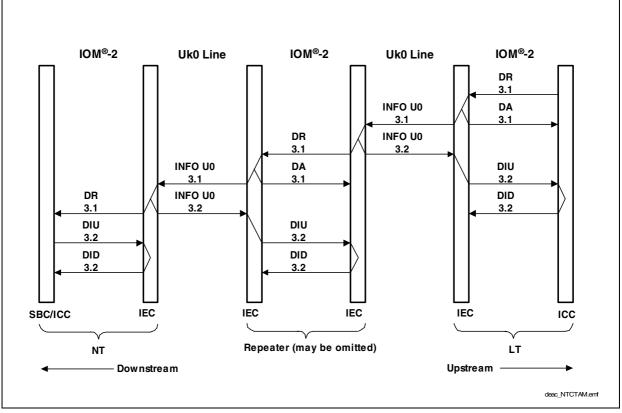

| <b>7</b><br>7.1<br>7.2<br>7.2.1<br>7.3<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.4<br>7.3.5<br>7.4<br>7.5<br>7.5.1<br>7.5.2<br>7.5.1<br>7.5.2<br>7.5.3 | Part II 'IEC-T': Operational Description112Control Procedures112Activation and Deactivation of Uk0 Transmission Lines113Awake Protocol113IOM, Control Information in the C/I Channel124IOM, Control Information for (De-)Activation Downstream125IOM, Control Information for (De-) Activation Upstream126IOM, Control Information for (De-) Activation Upstream126IOM, Control Information for the NTC-T AM with IEC-T Functionality Select-128IOM Control Information from the NTC-T AM with IEC-T Functionality Selected for Power Control 128129Summary of IOM, Control Informations in Different Applications129Meaning of Uk0 INFOs132Transit Conditions and their Abbreviations137Control of the Analog Loop and Loop Commands on Uk0138Description of the Activation/Deactivation States of NTC-T AM with IEC-TFunctionality Selected139 |

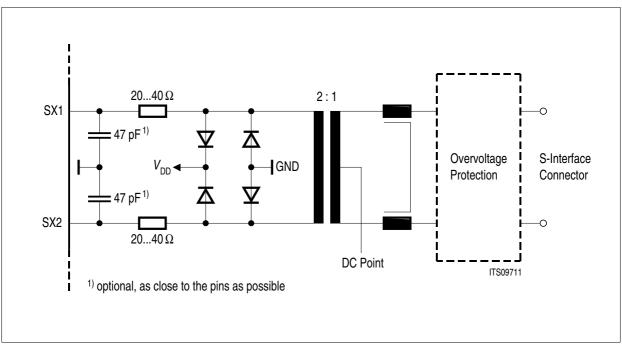

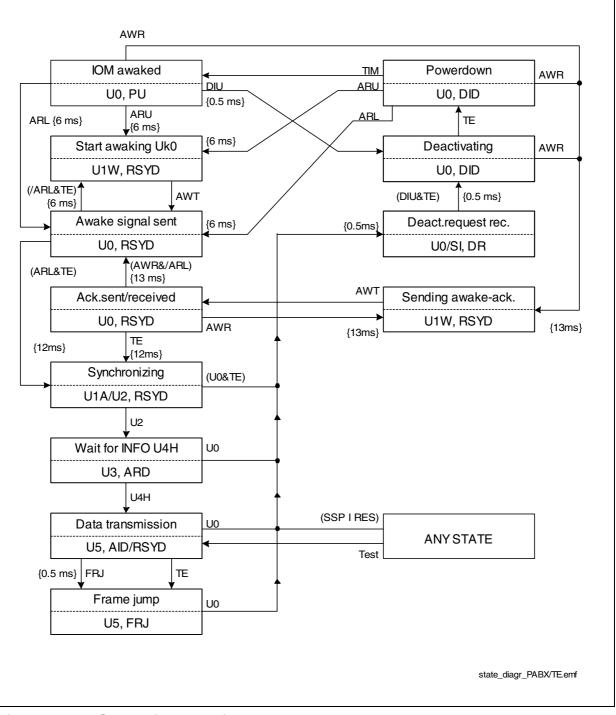

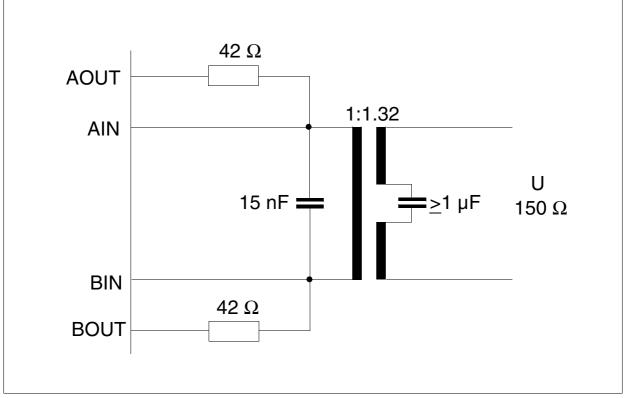

| <b>8</b><br>8.1<br>8.2<br>8.2.1<br>8.2.2                                                                                                       | Part III 'Common': Functional Description144Reset144External Circuitry145Power Supply Blocking Recommendation145U-Interface145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <b>9</b><br>9.1<br>9.2<br>9.3<br>9.4                                                                                                           | Part III 'Common': Electrical Characteristics147Absolute Maximum Ratings147Power Consumption149DC Characteristics150AC Characteristics152                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

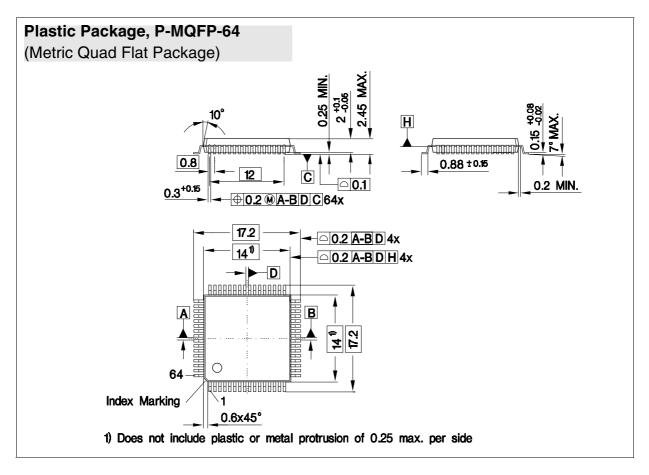

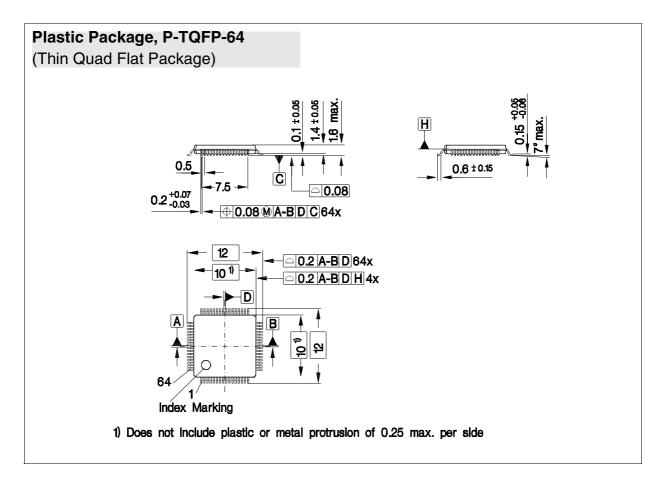

| 10                                                                                                                                             | Part III 'Common': Package Outlines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 11                                                                                                                                             | Part III 'Common': Power Consumption in the Application 161                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 12                                                                                                                                             | Part III 'Common': External Component Sourcing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 13                                                                                                                                             | Part III 'Common': Glossary 166                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

### List of Figures

# **PEB 80900**

| List of F | igures Pa                                                            | age |

|-----------|----------------------------------------------------------------------|-----|

| Figure 1  | Pin Configuration of the NTC-T AM with NTC-T and IEC-T Functionality | . 4 |

| Figure 2  | Logic Symbol                                                         |     |

| Figure 3  | Pin Configuration of the NTC-T AM with NTC-T Functionality           |     |

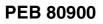

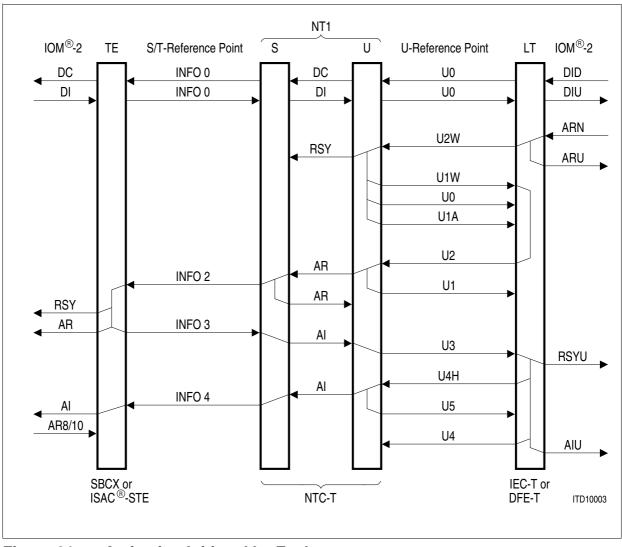

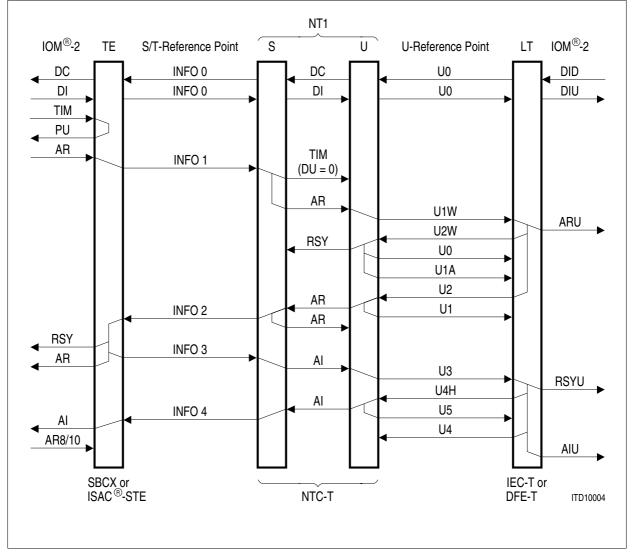

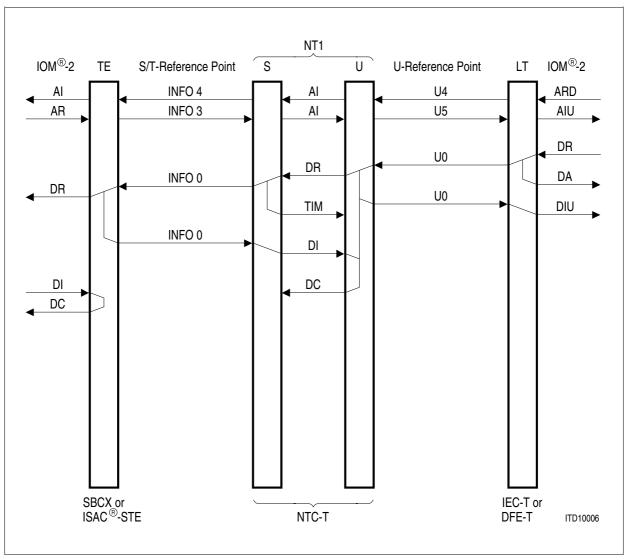

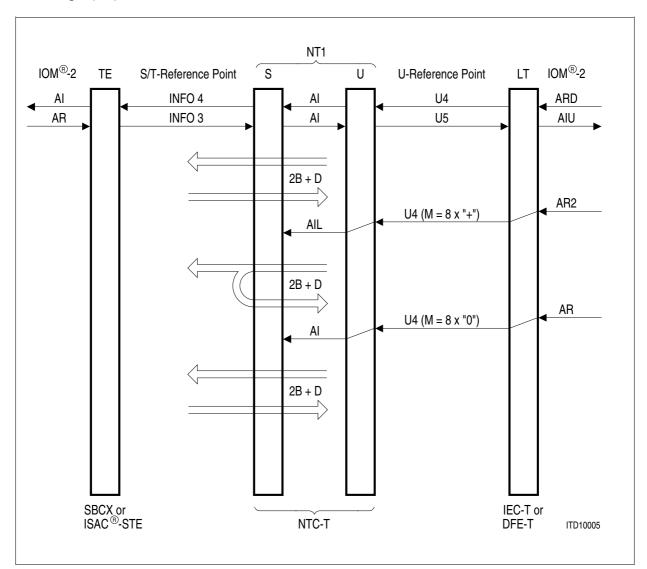

| Figure 4  | ITU Reference Model with NTC-T AM as NT1                             |     |

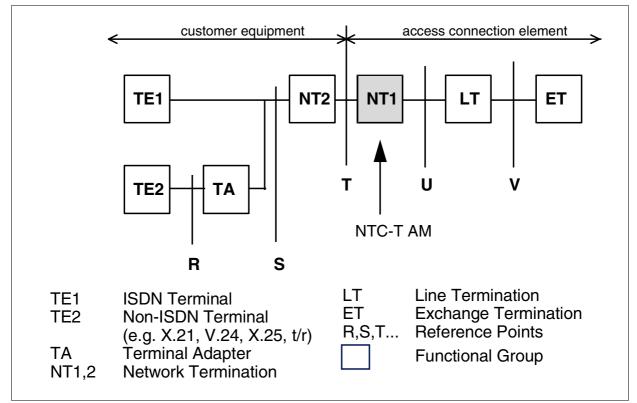

| Figure 5  | NTC-T AM with NTC-T Functionality Selected in NT1 Application        |     |

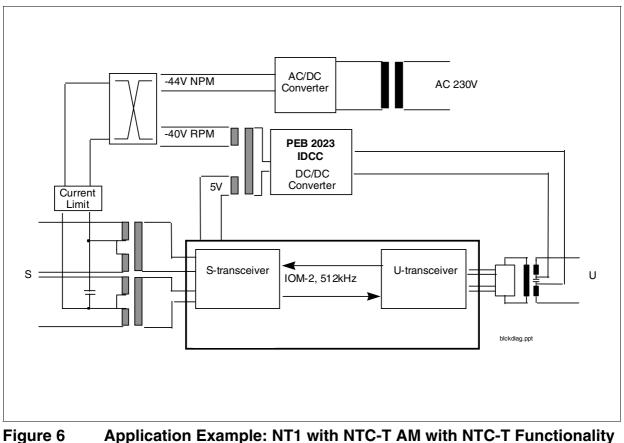

| Figure 6  | Application Example: NT1 with NTC-T AM with NTC-T Functionality      |     |

| Figure 7  | Selected and IDCC                                                    |     |

| Figure 8  | IOM®-2 Configurations (a)                                            |     |

| Figure 9  | IOM®-2 Configurations (b)                                            |     |

| Figure 1  |                                                                      |     |

| Figure 14 |                                                                      |     |

| Figure 1  |                                                                      |     |

| Figure 1  |                                                                      |     |

| Figure 1  | •                                                                    |     |

| Figure 1  |                                                                      |     |

| Figure 19 | •                                                                    |     |

| Figure 2  |                                                                      |     |

| Figure 2  |                                                                      |     |

| Figure 2  |                                                                      |     |

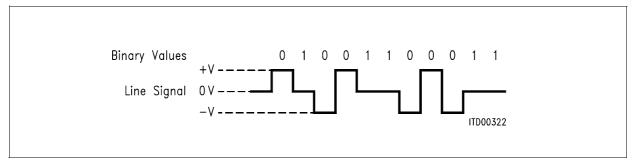

| Figure 2  | 3 S/T -Interface Line Code (without code violation)                  | 50  |

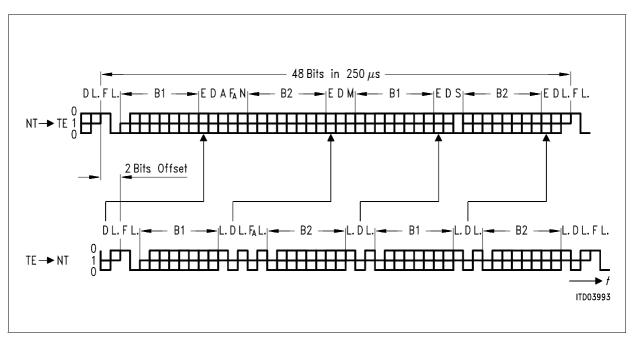

| Figure 24 | Frame Structure at Reference Points S and T (ITU I.430)              | 50  |

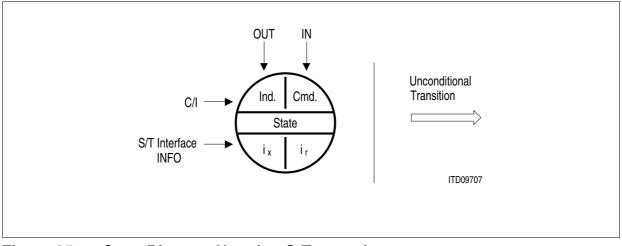

| Figure 2  | 5 State Diagram Notation S-Transceiver                               | 51  |

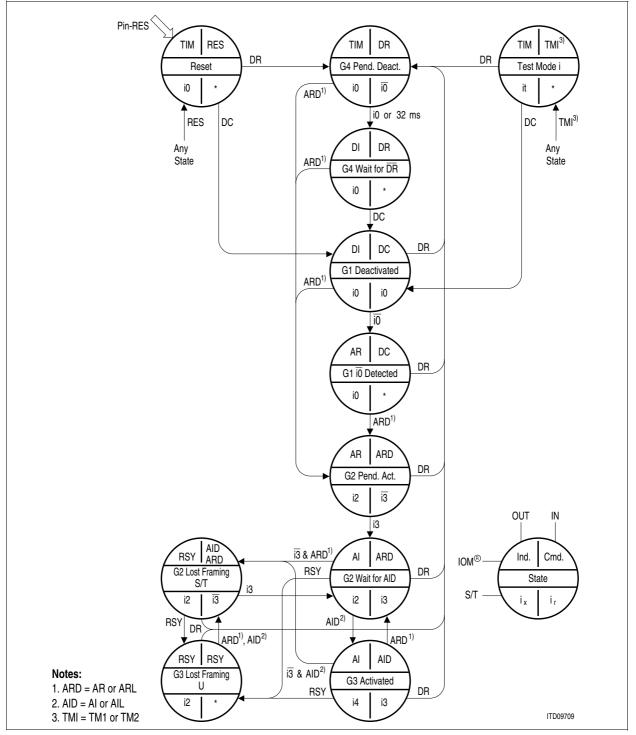

| Figure 2  | 6 State Diagram                                                      | 53  |

| Figure 2  | 7 Receiver and Transmitter Stages                                    | 58  |

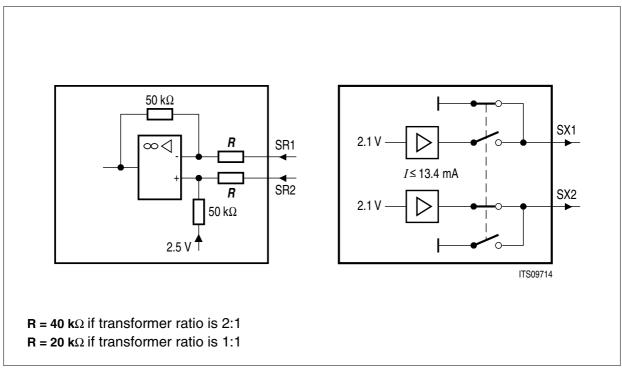

| Figure 2  | 8 S-Interface Transmitter External Circuitry                         | 59  |

| Figure 2  | 9 S-Interface Receiver External Circuitry                            | 60  |

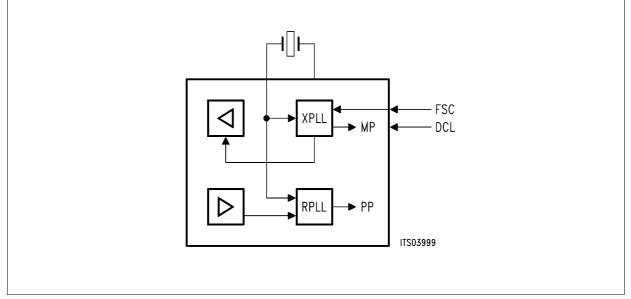

| Figure 3  | 0 Clock System of the S-Transceiver                                  | 61  |

| Figure 3  | 1 Activation Initiated by Exchange                                   | 64  |

| Figure 3  |                                                                      | 65  |

| Figure 3  |                                                                      |     |

| Figure 34 | •                                                                    | 67  |

| Figure 3  | •                                                                    | 68  |

| Figure 3  |                                                                      | 72  |

| Figure 3  |                                                                      |     |

| Figure 3  |                                                                      | 76  |

| Figure 3  |                                                                      |     |

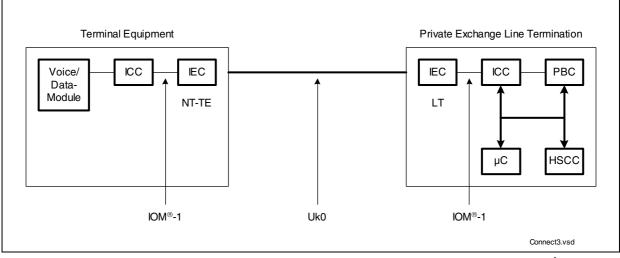

|           | (1st Generation)                                                     | 76  |

# List of Figures

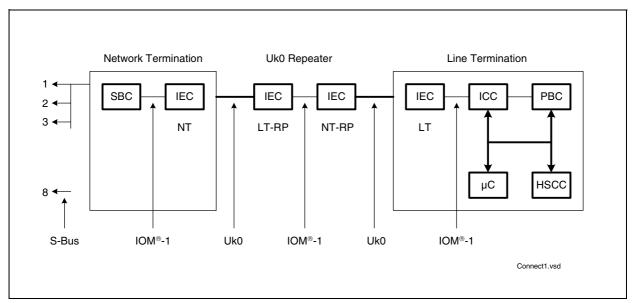

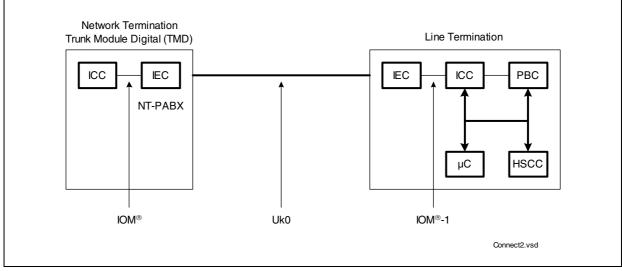

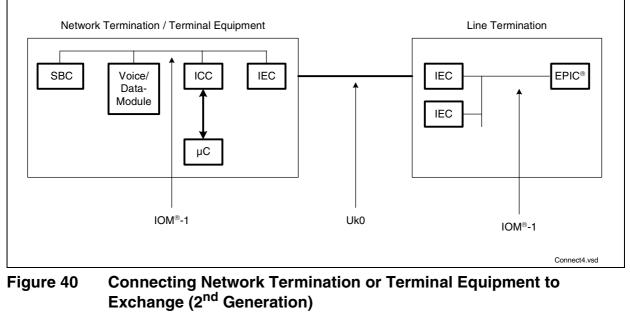

| Figure 40              | Connecting Network Termination or Terminal Equipment to Exchange (2nd Generation)                                                  |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------|

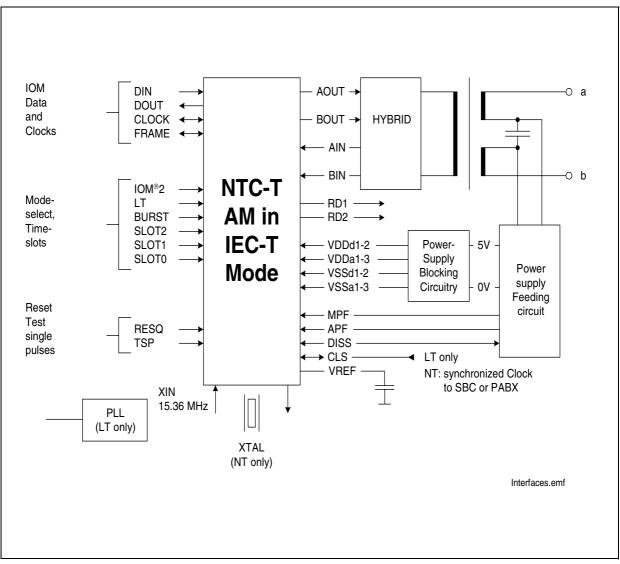

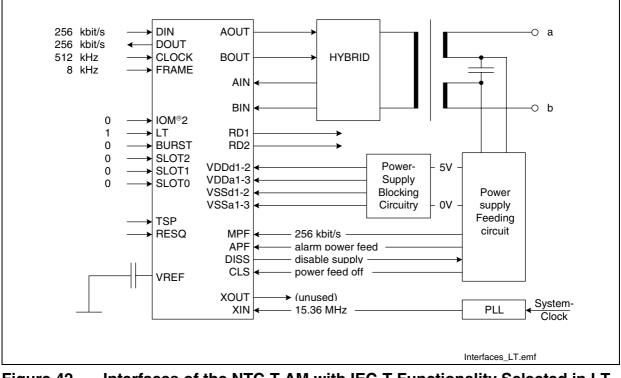

| Figure 41<br>Figure 42 | Interfaces of the NTC-T AM with IEC-T Functionality Selected 78<br>Interfaces of the NTC-T AM with IEC-T Functionality Selected in |

| i iguio iz             | LT-Mode                                                                                                                            |

| Figure 43              | Interfaces of the NTC-T AM with IEC-T Functionality Selected in LT-BURST1 Mode                                                     |

| Figure 44              | Interfaces of the NTC-T AM with IEC-T Functionality Selected in<br>LT-RP Mode                                                      |

| Figure 45              | Interfaces of the NTC-T AM with IEC-T Functionality Selected in<br>NT Mode                                                         |

| Figure 46              | Interfaces of the NTC-T AM with IEC-T Functionality Selected in<br>NT-RP Mode                                                      |

| Figure 47              | Interfaces of the NTC-T AM with IEC-T Functionality Selected in<br>NT-PABX-BURST1 Mode                                             |

| Figure 48              | Interfaces of the NTC-T AM with IEC-T Functionality Selected in                                                                    |

| Figure 49              | NT-PABX Mode                                                                                                                       |

| Figure 50              | NT-TE1 Mode                                                                                                                        |

| Figure 51              | Functionality Selected    91      IOM, Interface Mux Mode    92                                                                    |

| Figure 52              | Frame Structure of the Digital Interface of the NTC-T AM with IEC-T                                                                |

| ge. e e_               | Functionality Selected                                                                                                             |

| Figure 53              | Timing of Data and Clocks at the 256 kbit/s Interface                                                                              |

| Figure 54              | Timing of Data and Clocks at the IOM,-1 2048 kbit/s Interface 95                                                                   |

| Figure 55              | Timing of Frames at the IOM,-1 2048 kbit/s Interface                                                                               |

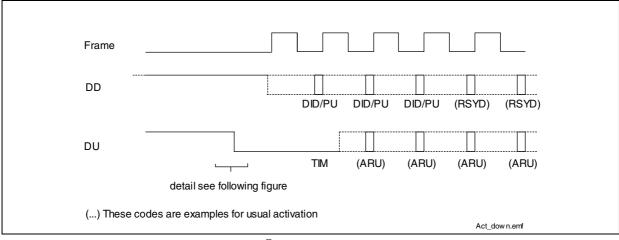

| Figure 56              | Deactivation of the IOM, Interface                                                                                                 |

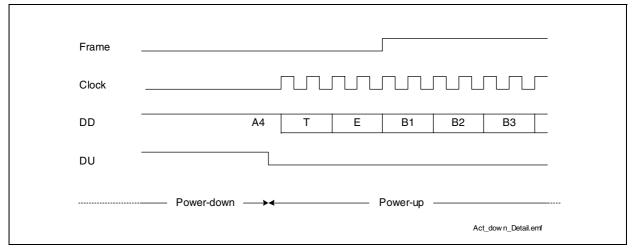

| Figure 57              | Deactivation of the IOM, Interface (Detail)                                                                                        |

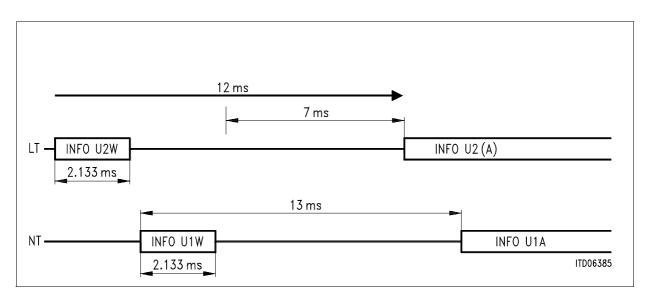

| Figure 58              | Activation of the IOM, Interface by the Downstream Unit                                                                            |

| Figure 59              | Activation of the IOM, Interface by the Downstream Unit (Detail) 99                                                                |

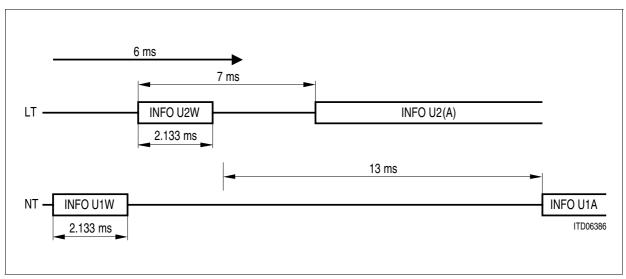

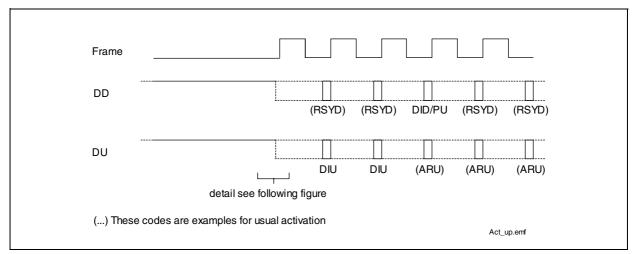

| Figure 60              | Activation of the IOM, Interface by the Upstream Unit                                                                              |

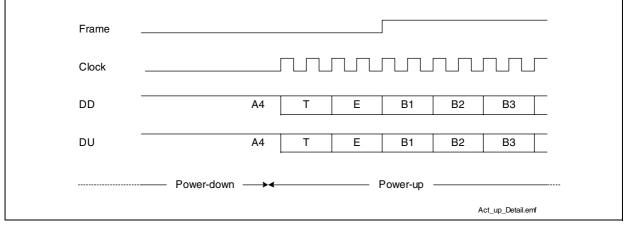

| Figure 61              | Activation of the IOM, Interface by the Upstream Unit (Detail) 100                                                                 |

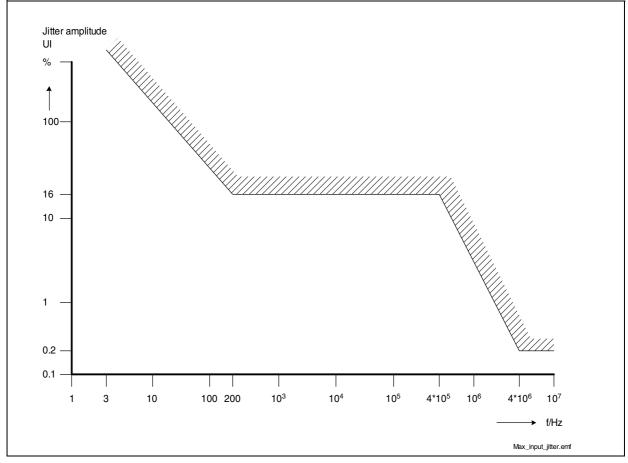

| Figure 62              | Maximum Sinusoidal Input Jitter of Master Clock 15.36 MHz 102                                                                      |

| Figure 63              | Interfaces of the NTC-T AM with IEC-T Functionality Selected in RP<br>Mode                                                         |

| Figure 64              | Generation of CLS from the Master Clock                                                                                            |

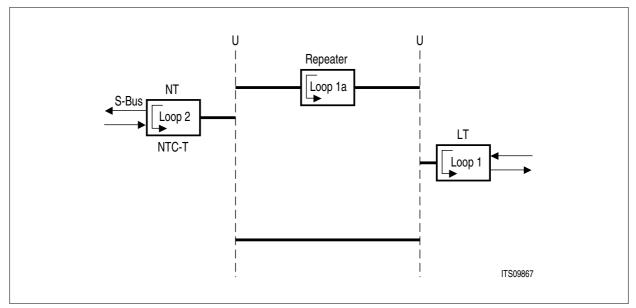

| Figure 65              | Test Loops Closed by the NTC-T AM with IEC-T Functionality Selected<br>or under its Remote Control                                 |

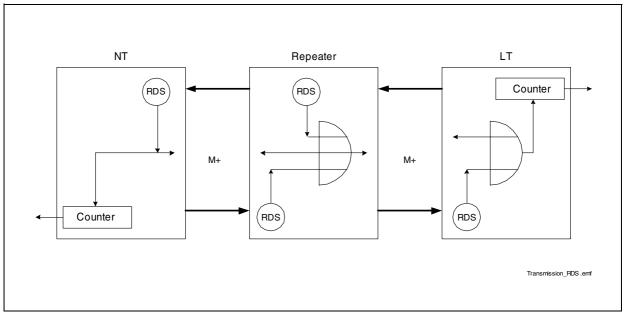

| Figure 66              | Transmission of Detected Frames with RSD Errors                                                                                    |

| Figure 67              | Transposition of EC Coefficient to MONITOR Channel                                                                                 |

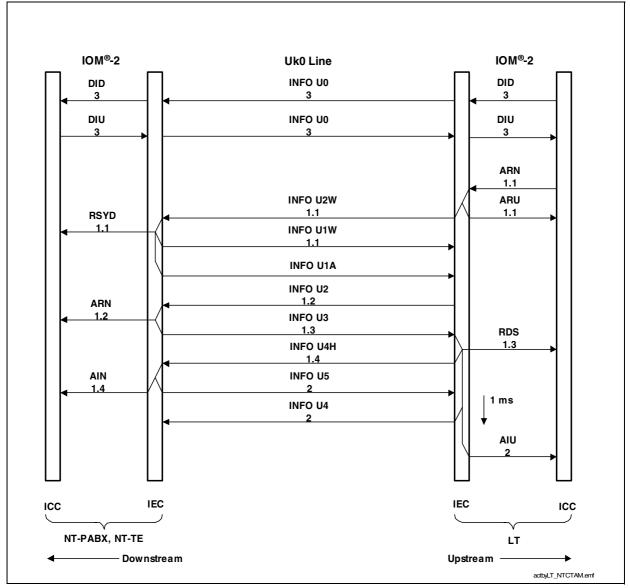

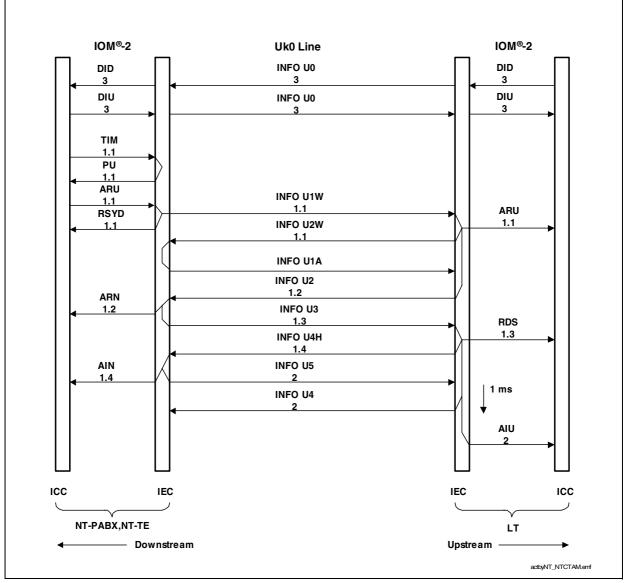

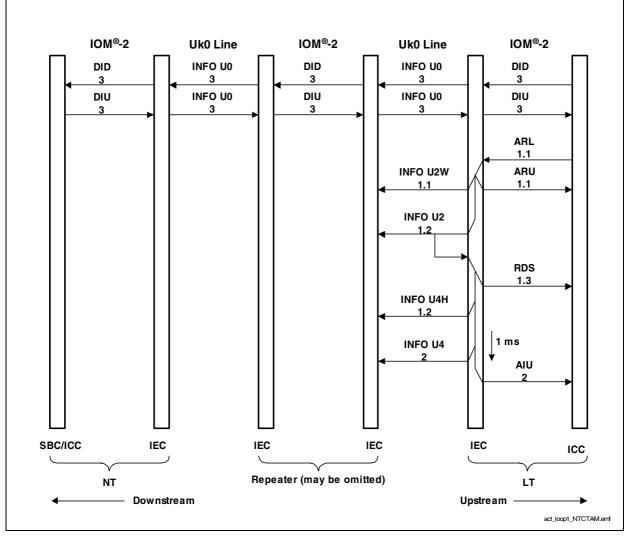

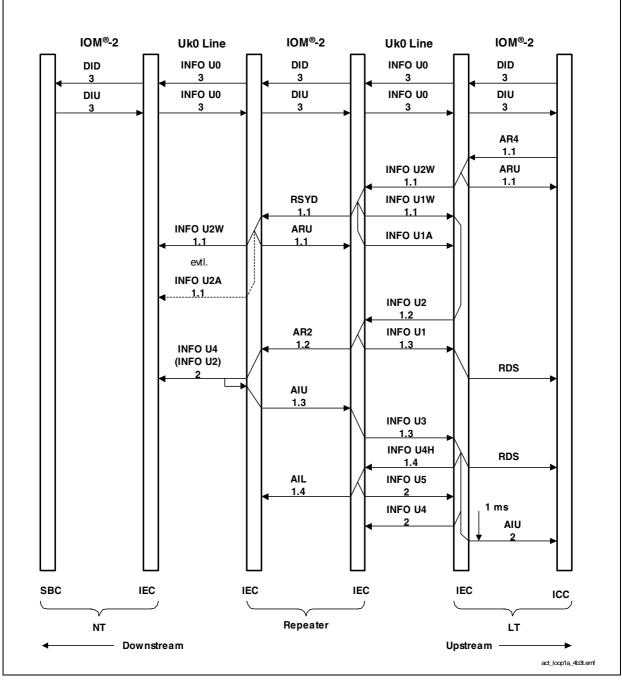

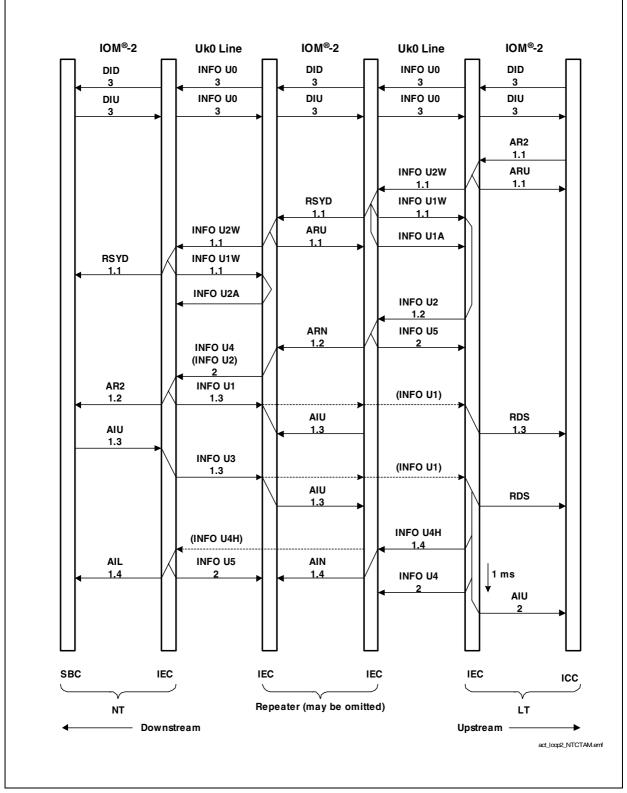

| Figure 68              | Activation of Uk0 Link Initiated by LT                                                                                             |

# List of Figures

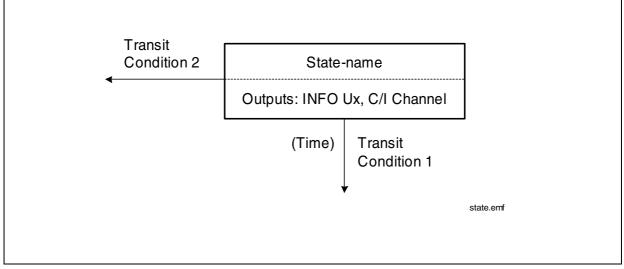

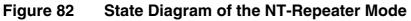

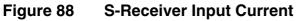

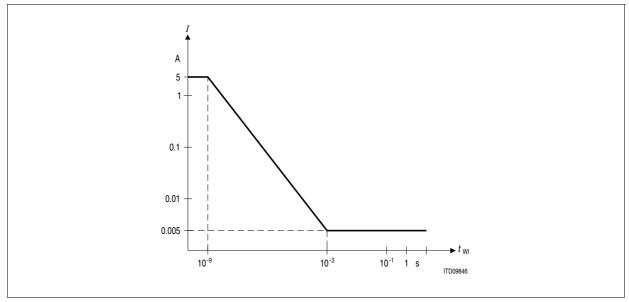

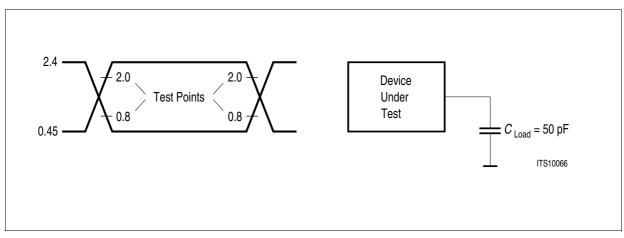

| Figure 69<br>Figure 70<br>Figure 71<br>Figure 72<br>Figure 73<br>Figure 74<br>Figure 75<br>Figure 76<br>Figure 77<br>Figure 78<br>Figure 79<br>Figure 80<br>Figure 81<br>Figure 82<br>Figure 83<br>Figure 83<br>Figure 84<br>Figure 85<br>Figure 85<br>Figure 85<br>Figure 87<br>Figure 88<br>Figure 89<br>Figure 90<br>Figure 91 | Activation of Loop 2 within NT-PABX or TE.<br>Activation of Loop 3 Within NT-PABX or TE<br>Deactivation of Uk0 Link Always Initiated by LT<br>Example of a State with Outputs and Inputs<br>State Diagram of the LT Mode.<br>State Diagram of the LT-Repeater Mode.<br>State Diagram of the NT-Repeater Mode<br>State Diagram of the NT-Repeater Mode<br>State Diagram of the NT-PABX and NT-TE Mode.<br>Power Supply Blocking<br>U-Interface Hybrid Circuit.<br>Test Condition for Maximum Input Current<br>S-Transmitter Input Current.<br>S-Receiver Input Current<br>U-Transceiver Input Current<br>Input/Output Waveform for AC Tests. | <ol> <li>117</li> <li>118</li> <li>119</li> <li>120</li> <li>121</li> <li>122</li> <li>123</li> <li>124</li> <li>132</li> <li>134</li> <li>135</li> <li>136</li> <li>137</li> <li>145</li> <li>146</li> <li>147</li> <li>148</li> <li>148</li> <li>149</li> </ol> |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 90                                                                                                                                                                                                                                                                                                                         | Input/Output Waveform for AC Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 152                                                                                                                                                                                                                                                               |

| Figure 91<br>Figure 92<br>Figure 93<br>Figure 94<br>Figure 95                                                                                                                                                                                                                                                                     | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 155<br>156<br>157                                                                                                                                                                                                                                                 |

### List of Tables

| Overview of 'NTC-T' and 'IEC-T' Functionality                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

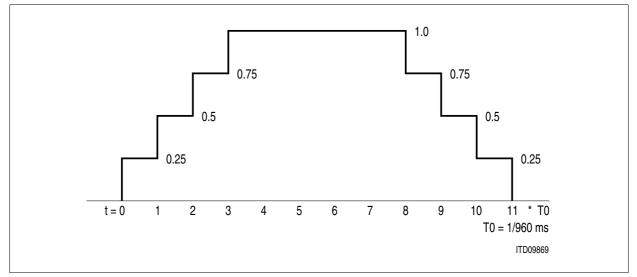

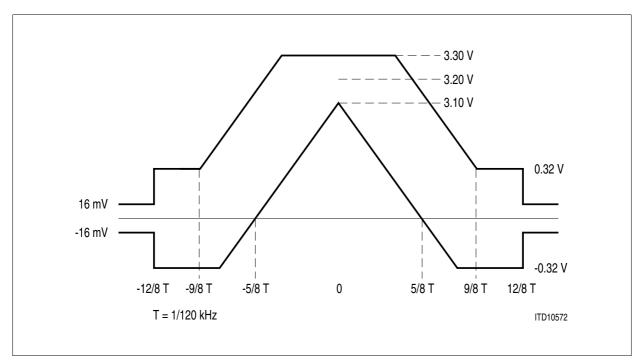

| IOM®-2 Configurations24Frame Structure for Downstream Transmission LT to NT32Frame Structure for Upstream Transmission NT to LT33MMS 43 Coding Table344B3T Decoding Table34U-Transceiver C/I Codes43S-Transceiver C/I Codes57Transceiver Test Modes61S/T-Interface Signals62U-Interface Signals63Programming the NTC-T AM with IEC-T Functionality Operation Modes |

| 77<br>Pin Definitions and Functions of the NTC-T AM with IEC-T Functionality                                                                                                                                                                                                                                                                                       |

| Selected 83                                                                                                                                                                                                                                                                                                                                                        |

| Mode Dependent Functions                                                                                                                                                                                                                                                                                                                                           |

| Allocation of Time Slots in IOM,-1 Modes                                                                                                                                                                                                                                                                                                                           |

| Coding of MONITOR Commands 110                                                                                                                                                                                                                                                                                                                                     |

| Summary of Codes in C/I Channel 129                                                                                                                                                                                                                                                                                                                                |

| IOM®-1: Dynamic Input Characteristics                                                                                                                                                                                                                                                                                                                              |

| IOM®-1: Dynamic Output Characteristics                                                                                                                                                                                                                                                                                                                             |

| IOM®-2                                                                                                                                                                                                                                                                                                                                                             |

| Auxiliary IOM®-2 156                                                                                                                                                                                                                                                                                                                                               |

| External Reset Timing                                                                                                                                                                                                                                                                                                                                              |

| Undervoltage Detection                                                                                                                                                                                                                                                                                                                                             |

| Power Consumption in a Typical Application                                                                                                                                                                                                                                                                                                                         |

| U-Transformer Information                                                                                                                                                                                                                                                                                                                                          |

| Crystal Information                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                    |

# Network Termination Controller (4B3T All Modes) NTC-T AM

**PEB 80900**

### Version 1.1

# 1 Overview

The Network Termination Controller (4B3T All Modes) NTC-T AM PEB 80900 features two fundamental modes:

• NTC-T Functionality

When 'NTC-T functionality' is selected, the NTC-T AM PEB 80900 provides all features known from the Network Termination Controller NTC-T PEB8090 V1.1 [1].

• IEC-T Functionality

When 'IEC-T functionality' is selected, the NTC-T AM PEB 80900 offers the full functionality of the IEC-T 4B3T two chip set PEB 20901 (IEC -TD) and PEB 20902 (IEC - TA) [2] and can hence replace the latter in all applications.

The NTC-T AM is a CMOS device which is available in a P-MQFP-64 and P-TQFP-64 package and operates from a single + 5 V supply with very low power consumption.

### References

- [1] NTC-T, Network Termination Controller (4B3T), PEB 8090 V1.1, Data Sheet 6.98, Siemens AG, 1998

- [2] IEC-T, ISDN Echocancellation Circuit IEC-T 4B3T Two Chip Set, PEB 2090-1/2, Target Specification 11.88, Siemens AG, 1988

| Туре      | Package   |  |  |

|-----------|-----------|--|--|

| PEB 80900 | P-MQFP-64 |  |  |

|           | P-TQFP-64 |  |  |

# 1.1 Selection between NTC-T and IEC-T Functionality

The selection between NTC-T and IEC-T functionality is possible by clamping the factory test pins TP0..2:

- TP0...2 = '000': NTC-T functionality according to [1]

- TP0...2 = '011': IEC-T functionality according to [2]

- TP0...2 = '1xx', '010', '001': reserved

**Table 1** gives an overview of functions, which are available with 'NTC-T' and 'IEC-T-Functionality' selected, respectively.

### Table 1 Overview of 'NTC-T' and 'IEC-T' Functionality

| '011' |

|-------|

|       |

|       |

| +     |

| +     |

| +     |

| +     |

| +     |

|       |

| -     |

|       |

| +     |

| +     |

|       |

| -     |

| 1     |

| -     |

| -     |

|       |

# 1.2 Organization of the Document

The document consists of three major parts:

- Part I 'NTC-T' specifies all features provided with NTC-T functionality selected

- Part II 'IEC-T' specifies all features provided with IEC-T functionality selected

- Part III 'Common' lists information, which is common to both modes

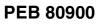

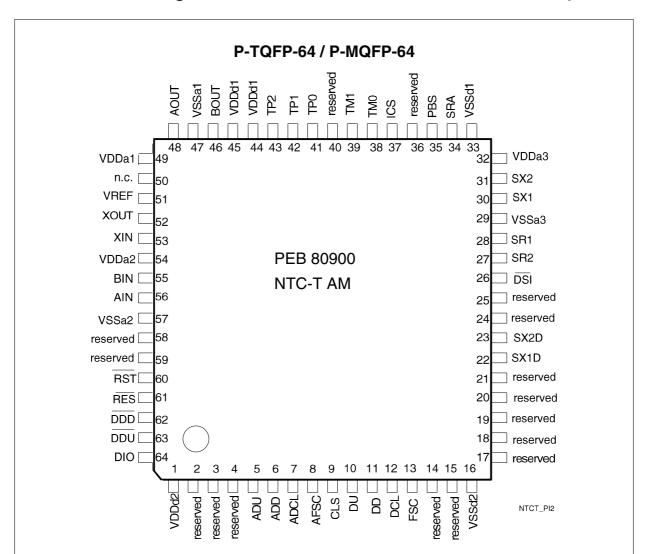

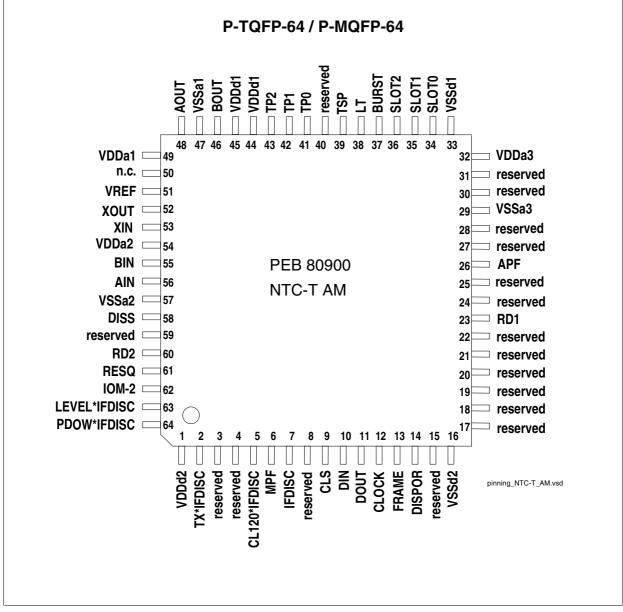

# 1.3 Pin Configuration of the NTC-T AM with NTC-T and IEC-T Functionality

P-TQFP-64 / P-MQFP-64

### Figure 1 Pin Configuration of the NTC-T AM with NTC-T and IEC-T Functionality

Pins with different functions in NTC-T and IEC-T mode are denoted in the order: 'function<sub>NTC-T</sub> - function<sub>IEC-T</sub>'.

# 1.4 Pin Definitions and Functions

The setting of the Factory Testpins TP0...2 influences the pin definitions and functions according to Table 2.

# Table 2Pin Definitions and Functions of the NTC-T AM for NTC-T and IEC-TFunctionality

| Pin | PEB 80900 with NTC-T Functionality |          |                                          | y PEB 80900 with IEC-T Functionality |                       |                                                                              |  |

|-----|------------------------------------|----------|------------------------------------------|--------------------------------------|-----------------------|------------------------------------------------------------------------------|--|

|     | I/O                                | Symbol   | Function                                 | I/O                                  | Symbol                | Function                                                                     |  |

|     | according to [1]                   |          |                                          | acco                                 | according to [2]      |                                                                              |  |

| 1   |                                    | VDDD2    | + 5 V +/- 5% supply voltage, digital     |                                      | VDDD2                 | + 5 V +/- 5% supply voltage, digital                                         |  |

| 2   | 0                                  | reserved | Leave open                               | 0                                    | IFDISC=0:<br>reserved | Leave open                                                                   |  |

|     |                                    |          |                                          |                                      | IFDISC=1:<br>TX       | 120 kHz Clock Output<br>(from IEC-TD)                                        |  |

| 3   | 0                                  | reserved | Leave open                               | 0                                    | reserved              | Leave open                                                                   |  |

| 4   | 0                                  | reserved | Leave open                               | 0                                    | reserved              | Leave open                                                                   |  |

| 5   | I/O                                | ADU      | Auxiliary Data<br>Upstream               | I                                    | IFDISC=0:<br>reserved | Tie to $VSS_{D}$                                                             |  |

|     |                                    |          |                                          |                                      | IFDISC=1:<br>CL 120   | 120 kHz Clock Input<br>(to IEC-TA)                                           |  |

| 6   | I/O                                | ADD      | Auxiliary Data<br>Downstream             | I                                    | MPF                   | Monitor Power Feed                                                           |  |

| 7   | I                                  | ADCL     | Auxiliary Data Clock                     | I                                    | IFDISC                | Interface Disconnect                                                         |  |

| 8   | 1                                  | AFSC     | Auxiliary Frame<br>Synchronization Clock | I                                    | reserved              | Tie to $VSS_{D}$                                                             |  |

| 9   | 0                                  | CLS      | Clock Signal                             | I/O                                  | CLS                   | LT: Power Feed Off<br>Signal from Power<br>Controller<br>NT/TE: Clock Output |  |

| 10  | I/O                                | DU       | Data Upstream                            | I                                    | DIN                   | IOM Data Input                                                               |  |

| 11  | I/O                                | DD       | Data Downstream                          | 0                                    | DOUT                  | IOM Data Output                                                              |  |

| 12  | 0                                  | DCL      | Data Clock                               | I/O                                  | CLOCK                 | Double IOM Clock                                                             |  |

| 13  | 0                                  | FSC      | Frame Synchronization<br>Clock           | I/O                                  | FRAME                 | IOM Frame Signal                                                             |  |

| Table 2 | Pin Definitions and Functions of the NTC-T AM for NTC-T and IEC-T |

|---------|-------------------------------------------------------------------|

|         | Functionality (cont'd)                                            |

| Pin | PEE |             | h NTC-T Functionality                           | PEE | 8 80900 wit      | h IEC-T Functionality               |  |  |  |

|-----|-----|-------------|-------------------------------------------------|-----|------------------|-------------------------------------|--|--|--|

|     | I/O | Symbol      | Function                                        | I/O | Symbol           | Function                            |  |  |  |

|     | acc | ording to [ | 1]                                              | acc | according to [2] |                                     |  |  |  |

| 14  | I   | reserved    | Tie to VSS <sub>D</sub>                         | I   | DISPOR           | Disable Power-On<br>Reset           |  |  |  |

| 15  | Ι   | reserved    | Tie to VSS <sub>D</sub>                         | I   | reserved         | Tie to VSS <sub>D</sub>             |  |  |  |

| 16  |     | VSSD2       | Digital GND                                     |     | VSSD2            | Digital GND                         |  |  |  |

| 17  | I   | reserved    | Tie to VSS <sub>D</sub>                         | I   | reserved         | Tie to VSS <sub>D</sub>             |  |  |  |

| 18  | I   | reserved    | Tie to VSS <sub>D</sub>                         | I   | reserved         | Tie to VSS <sub>D</sub>             |  |  |  |

| 19  | I   | reserved    | Tie to VSS <sub>D</sub>                         | I   | reserved         | Tie to VSS <sub>D</sub>             |  |  |  |

| 20  | Ι   | reserved    | Tie to VSS <sub>D</sub> .                       | I   | reserved         | Tie to VSS <sub>D</sub> .           |  |  |  |

| 21  | I   | reserved    | Tie to VSS <sub>D</sub> .                       | I   | reserved         | Tie to VSS <sub>D</sub> .           |  |  |  |

| 22  | 0   | SX1D        | S/T-interface positive transmit output, digital | 0   | reserved         | Leave open                          |  |  |  |

| 23  | 0   | SX2D        | S/T-interface negative transmit output, digital | 0   | RD1              | Relay Driver Pin 1                  |  |  |  |

| 24  | 0   | reserved    | Leave open.                                     | 0   | reserved         | Leave open                          |  |  |  |

| 25  | 0   | reserved    | Leave open.                                     | 0   | reserved         | Leave open                          |  |  |  |

| 26  | I   | DSI         | Digital S-Interface<br>Transmitter              | -   |                  | Alarm Power Feed                    |  |  |  |

| 27  | I   | SR2         | Differential S/T-<br>interface receive input    | I   |                  | Tie to VSS <sub>A</sub>             |  |  |  |

| 28  | I   | SR1         | Differential S/T-<br>interface receive input    | I   |                  | Tie to VSS <sub>A</sub>             |  |  |  |

| 29  |     | VSSA3       | Analog GND                                      |     | VSSA3            | Analog GND                          |  |  |  |

| 30  | 0   | SX1         | S/T-interface positive transmit output          | 0   |                  | Leave open                          |  |  |  |

| 31  | 0   | SX2         | S/T-interface negative transmit output          | 0   |                  | Leave open                          |  |  |  |

| 32  |     | VDDa3       | + 5 V +/- 5% supply voltage, analog             |     | VDDa3            | + 5 V +/- 5% supply voltage, analog |  |  |  |

| 33  |     | VSSD1       | Digital GND                                     |     | VSSD1            | Digital GND                         |  |  |  |

# Table 2Pin Definitions and Functions of the NTC-T AM for NTC-T and IEC-T<br/>Functionality (cont'd)

| Pin | PEB     | 80900 wit   | h NTC-T Functionality                         | PEE | 8 80900 wit | h IEC-T Functionality                                              |

|-----|---------|-------------|-----------------------------------------------|-----|-------------|--------------------------------------------------------------------|

|     | I/O     | Symbol      | Function                                      | I/O | Symbol      | Function                                                           |

|     | acco    | ording to [ | 1]                                            | acc | ording to [ | 2]                                                                 |

| 34  | I       | SRA         | S-Receiver Amplifier                          | I   | SLOT0       | Selection of Different<br>256 kbit/s Modes/ Time<br>Slot Selection |

| 35  | I<br>PU | PBS         | Point-to-point / Bus<br>Selection             | 1   | SLOT1       | Selection of Different<br>256kbit/s Modes/ Time<br>Slot Selection  |

| 36  | I       | reserved    | Tie to VSS <sub>D</sub> .                     | 1   | SLOT2       | Selection of Different<br>256kbit/s Modes/ Time<br>Slot Selection  |

| 37  | I       | ICS         | IOM <sup>®</sup> -2 Channel S-<br>Transceiver | I   | BURST       | Burst Mode                                                         |

| 38  | l<br>PU | TM0         | Test Mode 0                                   | I   | LT          | NT/LT Mode                                                         |

| 39  | l<br>PU | TM1         | Test Mode 1                                   | I   | TSP         | Test Single Pulses                                                 |

| 40  | I       | reserved    | Tie to VSS <sub>D</sub>                       | I   | reserved    | Tie to VSS <sub>D</sub>                                            |

| 41  | I       | TP0         | Factory Testpin. Tie to $VSS_{D}$ .           | I   | TP0         | see Chapter 1.1                                                    |

| 42  | I       | TP1         | Factory Testpin. Tie to $VSS_{D}$ .           | I   | TP1         |                                                                    |

| 43  | I       | TP2         | Factory Testpin. Tie to $VSS_{D}$ .           | I   | TP2         |                                                                    |

| 44  |         | VDDD1       | + 5 V +/- 5% supply voltage, digital          |     | VDDD1       | + 5 V +/- 5% supply voltage, digital                               |

| 45  |         | VDDD1       | + 5 V +/- 5% supply voltage, digital          |     | VDDD1       | + 5 V +/- 5% supply voltage, digital                               |

| 46  | 0       | BOUT        | Differential U-interface output               | 0   | BOUT        | Differential U-interface output                                    |

| 47  |         | VSSA1       | Analog GND                                    |     | VSSA1       | Analog GND                                                         |

| 48  | 0       | AOUT        | Differential U-interface output               | 0   | AOUT        | Differential U-interface output                                    |

# Table 2Pin Definitions and Functions of the NTC-T AM for NTC-T and IEC-T<br/>Functionality (cont'd)

| Pin | PEE | 8 80900 wit | h NTC-T Functionality                                                                                    | PEE | 80900 wit   | h IEC-T Functionality                                                                                    |

|-----|-----|-------------|----------------------------------------------------------------------------------------------------------|-----|-------------|----------------------------------------------------------------------------------------------------------|

|     | I/O | Symbol      | Function                                                                                                 | I/O | Symbol      | Function                                                                                                 |

|     | acc | ording to [ | 1]                                                                                                       | acc | ording to [ | 2]                                                                                                       |

| 49  |     | VDDA1       | + 5 V +/- 5% supply voltage, analog                                                                      |     | VDDA1       | + 5 V +/- 5% supply voltage, analog                                                                      |

| 50  |     | n.c.        | Leave open                                                                                               |     | n.c.        | Leave open                                                                                               |

| 51  | I/O | VREF        | Reference Voltage.<br>Connect 100 nF vs.<br>VSSA to buffer<br>internally generated<br>reference voltage. | I/O | VREF        | Reference Voltage.<br>Connect 100 nF vs.<br>VSSA to buffer<br>internally generated<br>reference voltage. |

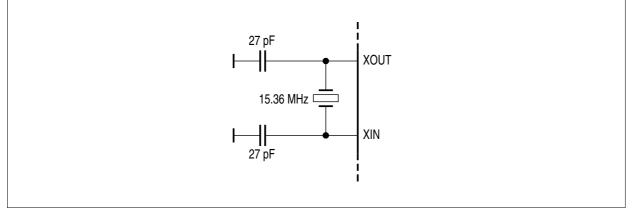

| 52  | 0   | XOUT        | Crystal OUT.<br>Connect a 15.36 MHz<br>crystal                                                           | 0   | XOUT        | Crystal OUT.<br>Connect a 15.36 MHz<br>crystal                                                           |

| 53  | 1   | XIN         | Crystal IN.<br>Connect a 15.36 MHz<br>crystal                                                            | I   | XIN         | Crystal IN.<br>Connect a 15.36 MHz<br>crystal                                                            |

| 54  |     | VDDa2       | + 5 V +/- 5% supply voltage, analog                                                                      |     | VDDa2       | + 5 V +/- 5% supply voltage, analog                                                                      |

| 55  | I   | BIN         | Differential U-interface input                                                                           | I   | BIN         | Differential U-interface input                                                                           |

| 56  | I   | AIN         | Differential U-interface input                                                                           | I   | AIN         | Differential U-interface input                                                                           |

| 57  |     | VSSA2       | Analog GND                                                                                               |     | VSSA2       | Analog GND                                                                                               |

| 58  | 0   | reserved    | Leave open                                                                                               | 0   | DISS        | Disable Supply                                                                                           |

| 59  | 0   | reserved    | Leave open                                                                                               | 0   | reserved    | Leave open                                                                                               |

| 60  | 0   | RST         | Reset Output                                                                                             | 0   | RD2         | Relay Driver Pin 2                                                                                       |

| 61  | Ι   | RES         | Reset Input                                                                                              | Ι   | RESQ        | Power On Reset                                                                                           |

| 62  | Ι   | DDD         | Disconnect Data<br>Downstream                                                                            | I   | IOM2        | Tie to VSSD                                                                                              |

# Table 2Pin Definitions and Functions of the NTC-T AM for NTC-T and IEC-TFunctionality (cont'd)

| Pin | PEE | PEB 80900 with NTC-T Functionality |                             |     | PEB 80900 with IEC-T Functional |                                                |  |  |

|-----|-----|------------------------------------|-----------------------------|-----|---------------------------------|------------------------------------------------|--|--|

|     | I/O | Symbol                             | Function                    | I/O | Symbol                          | Function                                       |  |  |

|     | acc | ording to [                        | 1]                          | acc | ording to [2                    | 2]                                             |  |  |

| 63  | I   | DDU                                | Disconnect Data<br>Upstream | I   | IFDISC=0:<br>reserved           | Tie to VSSD                                    |  |  |

|     |     |                                    |                             |     | IFDISC=1:<br>LEVEL              | Awake Signal<br>Detection<br>(input to IEC-TD) |  |  |

| 64  | I   | DIO                                | Disable IOM <sup>®</sup> -2 | I   | IFDISC=0:<br>reserved           | Tie to VSSA                                    |  |  |

|     |     |                                    |                             |     | IFDISC=1:<br>PDOW               | Power Down<br>(input to IEC-TA)                |  |  |

# 1.4.1 Special Pin IFDISC: Interface Disconnect (Available only with TP0..2 = '011')

The IEC-T is available only in a two-chip set (IEC-TA and IEC-TD). Therefore, signals between the IEC-TA and IEC-TD may be accessed for special applications (e.g. repeater application). In contrast to the IEC-T, the NTC-T AM is delivered in a single package. Access to signals corresponding to those between IEC-TA and IEC-TD may be selected with pin IFDISC:

- With TP0...2 = '011' and IFDISC = '0' selected, all user interfaces of the IEC-T are accessible, but no signals corresponding to those between IEC-TA and IEC-TD.

- By setting TP0...2 = '011' and IFDISC = '1', all user interfaces of the IEC-T are accessible, too. In addition, some important signals of the internal interface between IEC-TD and IEC-TA are disconnected and accessible externally. In this case, the user must take care to apply the corresponding inputs for proper operation.

# 1.5 Functional Differences between PEB 80900 with IEC-T Functionality and PEB 20901/2

### 1.5.1 Data Output on IOM

Pin 23 'DOUT: IOM data output synchronous to CLOCK' of the IEC-TD PEB 20901 operates always in open-drain mode. In contrast to PEB 20901, pin 11 of the NTC-T AM PEB 80900 with IEC-T functionality selected operates always in push-pull mode (see also **Chapter 6.3.2**). Especially in modes with DOUT operating in burst mode, pin 11 drives during inactive timeslots a logical '1'.

This difference must be taken into account, when an NTC-T AM with IEC-T functionality selected shall be connected to an IOM bus configuration. In this case, the different data output lines must be ANDed with external logic.

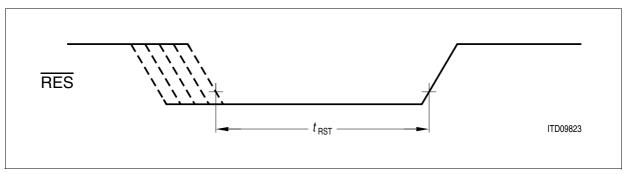

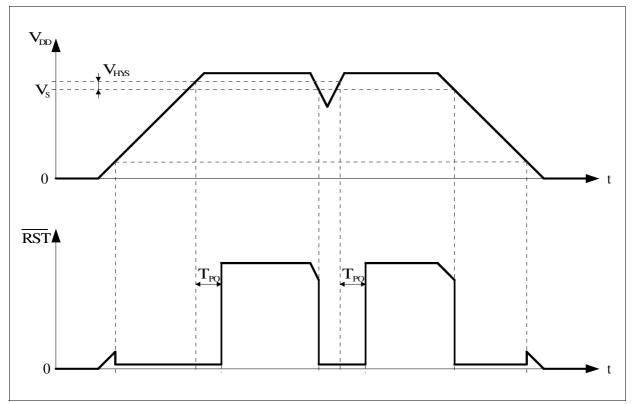

### **1.5.2** Power-On Reset and Undervoltage Detection

In addition to the IEC-T PEB 20901/2, the NTC-T AM PEB 80900 with IEC-T functionality provides the Power-On Reset and Undervoltage detection function as specified in Ref. [1]. It can be disabled by setting DISPOR = '1'.

### **1.5.3** External Circuitry for Connection to the U-Interface

The IEC-TA PEB 20902 is connected to the twisted pair of the U-interface via an external hybrid. In contrast, the NTC-T AM provides an integrated U-interface hybrid for both NTC-T and IEC-T mode. The recommended external circuitry is displayed in **Chapter 8.2.2**.

# 1.6 Editorial Changes between the IEC-T Target Specification [2] and Part II 'IEC-T' of the NTC-AM Data Sheet

### "Part II 'IEC-T': General Description" on Page 69

Removed: 'At present, the IEC is available in a two chip set only.'

### "Basic System Functions" on Page 70

Removed: 'Low power consumption: Standby:max. 20 mW Active:max. 250 mW'

Removed: '40 pin DIL package or 44 pin PLCC package.'

Reworked pin configuration

### "Related Documents" on Page 73

The following documents have been removed from the list 'Related Documents':

- Technische Lieferbedingungen 163 TL 31 f

ür digitale Fernsprechvermittlungstechnik EWSD/0

- Technische Lieferbedingungen 163 TL 311 für die Anpassung EWSD/0 an ISDN

- Technische Lieferbedingungen Basisanschluss-Multiplexgerät (BAMX)

- FTZ-Richtlinie 1 TR 211, Speisekonzept für den Basisanschluss

- FTZ-Richtlinie 1 TR 212, Prüfen und Messen von digitalen Anschlüssen

- IC's for Telecommunications, IOM<sup>®</sup>-ISDN oriented Modular Interface Edition 5.86

The documentation for ICC and SBC is updated.

### "IOM, Concept and Applications of the IEC" on Page 75

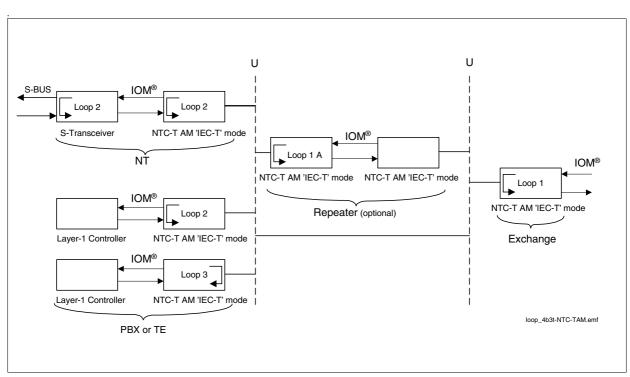

According to the Delta Sheet IEC-T/D PEB 20901 Version 5.1, the IOM-2 mode is not functional in any version of PEB 20901. Therefore, the whole part II of this document refers only to IOM-1 mode.

#### "Interfaces" on Page 78

Updated pinning in all figures and table.

### "Mode Dependent Functions" on Page 88

Removed all IOM-2 modes

### "Data and Clocks in NT, NT-RP, NT-TE1 Mode" on Page 90 CLS output: .

NT, NT-RP: 7.68 MHz clock, synchronized to received data on Uk0. NT-TE1: 1.536 MHz, synchronized to received data on Uk0.

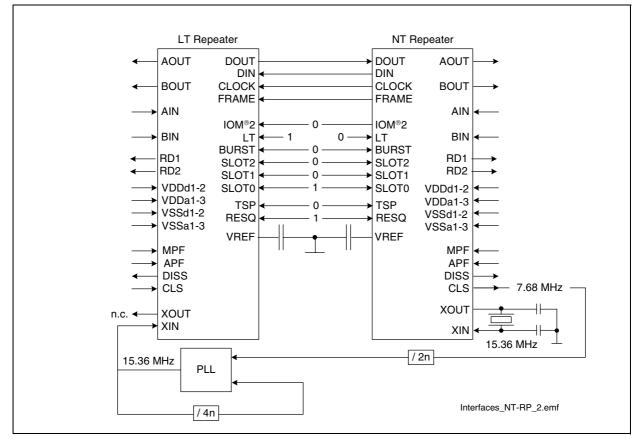

"Suggestion for the Generation of the Master Clock in the Repeater" on Page 103

Reworked figure for NTC-T AM.

"Remote Control of Loop 4 and Loop 2 by the NTC-T AM with IEC-T Functionality Selected" on Page 107

Added Note: 'The IEC in NT mode does not close loop2 itself.

NT-RP: The polarity of the E-bit is <u>high</u> when detecting positive M-symbols and <u>low</u> when detecting negative or zero M symbols.

"Monitoring of Code Violations" on Page 108

LT-RP: The polarity of the E-bit is <u>high</u> when detecting positive M-symbols.

"Access to MONITOR Channel in the IOM,-1 Mode" on Page 111

Detection of a valid command in the MONITOR channel will be acknowledged by setting the E Bit to 0 in the frame containing the <u>response</u>.

"Summary of IOM, Control Informations in Different Applications" on Page 129 Added FJ in NT and NT-RP mode (in table and state diagrams).

"Control of the Analog Loop and Loop Commands on Uk0" on Page 138

ARL: removed: '(in the C/I channel input or RESQ pin low) always causes the chip to be reset.'

# 2 Part I 'NTC-T': Overview

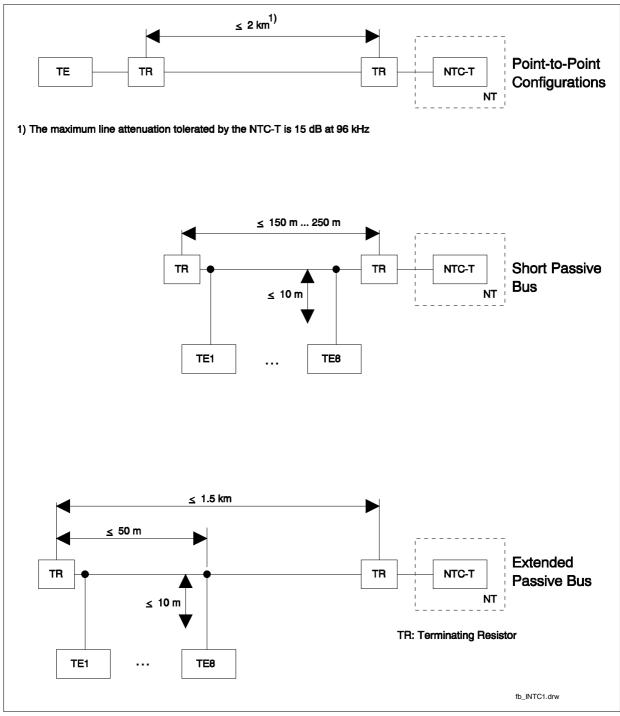

The NTC-T AM with NTC-T functionality selected is a Network Termination (NT) circuit for the basic rate Integrated Services Digital Network (ISDN). It combines a U-transceiver and an S-transceiver on one chip. The NTC-T AM with NTC-T functionality selected provides the 4B3T U-interface as defined by FTZ Guideline 1TR 220, ETSI ETR 080 1995 together with the S/T-interface as specified in ITU Rec. I.430 and ETS 300 012.

The NTC-T AM with NTC-T functionality selected works as a stand-alone NT1 with completely automatic handling of all layer-1 procedures without a microcontroller. It transparently exchanges the 144 kbit/s user data rate between the U- and the S/T-interface (see [1]).

An optional IOM-2 interface and various test modes ease chip evaluation and testing.

# 2.1 Features

- Single chip solution including U- and S-transceiver

- Perfectly suited for the NT1 in the ISDN

- Fully automatic activation and deactivation of U<sub>k0</sub> interface and S/T-interface

- U-interface (4B3T) conform to the FTZ Guideline 1 TR 220 of the Deutsche Telekom AG (DTAG) and ETR 080 of ETSI:

- 4B3T ternary block code

- Meets all transmission requirements on all ETSI and FTZ loops with margin

- Function compatible to IEC-T

- S/T-interface conform to ITU Rec. I.430 and

- ETS 300 012:

- Meets and exceeds all FTZ and ETSI transmission requirements

- Supports point-to-point and bus configurations

- Function compatible to SBCX

- Minimized external component count:

- Integrated U interface hybrid

- Integrated pull-up resistors

- On-chip reset generation at power-on and undervoltage detection; no external components needed.

- IOM-2 interface eases chip testing and design of an Intelligent NT

- Single 5 Volt power supply

- Low power CMOS technology with power-down mode

- 240 mW typical power consumption with random data over typical lines

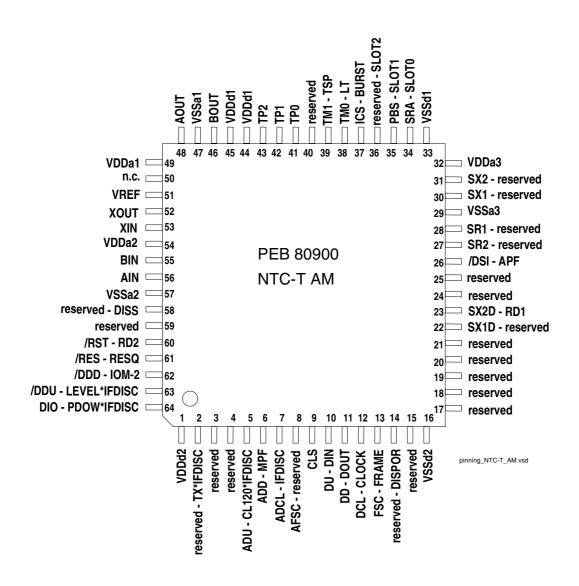

### 2.2 Logic Symbol

Figure 2 Logic Symbol