# HDM8513A Users Manual DVB/DSS Compliant Receiver

Nov. 2000 Revision 1.0

Direct Broadcast Satellite (DBS) has been one of the most successful new product introductions in the history of consumer electronics. This product represents the first application of digital video compression for broadcast television. Originally intended to provide cable quality television services to remote areas, this product is now offering a competitive replacement to cable services in many urban areas.

The first operational systems employ closed proprietary signaling structures. The European Broadcasting Union (EBU) has developed the first open standard (DVB-S) for DBS services. The broadcasting community has embraced this standard which is now being adopted for new systems throughout the world. This widely accepted open standard is essential for DBS to achieve full market potential.

The HDM8513A<sup>TM</sup> is a fully DVB-S&DSS compliant ADC/QPSK demodulator/FEC device which provides an MPEG-2 stream to be processed by the conditional access and video decompression circuits. The demodulator clocked with a fixed frequency is true variable rate over the range of 1 to 55M symbols-per-second. This product achieves the highest performance and flexibility. It minimizes the cost of external circuits, thus reducing overall system cost.

Hyundai Electronics Ind. Co., Ltd reserves the right to make changes to its products or specifications to improve performance, reliability, or manufacturability. Information furnished by Hyundai Electronics Ind. Co., Ltd is believed to be accurate and reliable. However, no responsibility is assumed by Hyundai Electronics Ind. Co., Ltd for its use; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by its implication or otherwise under any patent rights of Hyundai Electronics Ind. Co., Ltd.

For more information contact:

Address: Youngdong Bldg. 891, Daechi-dong, Kangnam-gu, Seoul, 135-738, Korea Tel: 82-2-3459-3188 Fax: 82-2-3459-5843 E-mail: kosb@hei.co.kr

## TABLE OF CONTENTS

| 1. INTRODUCTION TO THE HDM8513A                                                                                             | 6 |

|-----------------------------------------------------------------------------------------------------------------------------|---|

| 1.1 FEATURES AND BENEFITS                                                                                                   | 7 |

| 2. HARDWARE SPECIFICATION                                                                                                   | 8 |

| 3. TECHNICAL OVERVIEW                                                                                                       |   |

| 3.1 DUAL CHANNEL ANALOG TO DIGITAL CONVERTER                                                                                |   |

| <ul> <li>3.3 NOISE MEASUREMENT CIRCUIT</li></ul>                                                                            |   |

| 3.6 REED SOLOMON DECODER                                                                                                    |   |

| 3.8 DBS RECEIVER                                                                                                            |   |

| 4. MECHANICAL SPECIFICATIONS                                                                                                |   |

| 4.1 100 Pin Quad Flat Pack<br>4.2 64 Pin Thin Quad Flat Pack                                                                |   |

| 4.3 RECOMMENDED ANALOG PIN CONNECTION                                                                                       |   |

| 5. SIGNAL DESCRIPTION                                                                                                       |   |

| 5.1 INPUTS<br>5.2 OUTPUTS<br>5.3 M ONITOR AND CONTROL INTERFACE<br>5.4 I2C MODE                                             |   |

| 6. REGISTER DEFINITIONS                                                                                                     |   |

| 6.1 W RITE REGISTERS                                                                                                        |   |

| APPENDIX                                                                                                                    |   |

| A1. LOOP FILTER PROGRAMMING APPLICATION NOTE<br>A2. FALSE LOCK ESCAPE APPLICATION NOTE<br>A3. PERFORMANCE WITH INTERFERENCE |   |

| A4. NYQUIST CRITERIA CONSIDERATIONS                                                                                         |   |

## LIST OF FIGURES

| FIGURE 1: | TOP LEVEL BLOCK DIAGRAM           | 6  |

|-----------|-----------------------------------|----|

| FIGURE 2: | INPUT DATA TIMING DIAGRAM         | 9  |

| FIGURE 3: | INTEL 80C88A READ TIMING DIAGRAM  | 10 |

| FIGURE 4: | INTEL 80C88A WRITE TIMING DIAGRAM | 11 |

| FIGURE 5: | INTEL 8051 READ TIMING DIAGRAM    | 12 |

| FIGURE 6: | INTEL 8051 WRITE TIMING DIAGRAM   | 13 |

|           |                                   |    |

| FIGURE 7: MOTOROLA READ TIMING DIAGRAM                               | 14 |

|----------------------------------------------------------------------|----|

| FIGURE 8: MOTOROLA WRITE TIMING DIAGRAM                              | 15 |

| FIGURE 9: OUTPUT TIMING DIAGRAM FOR NORMAL PARALLEL                  | 16 |

| FIGURE 10: OUTPUT TIMING DIAGRAM FOR NORMAL SERIAL                   | 16 |

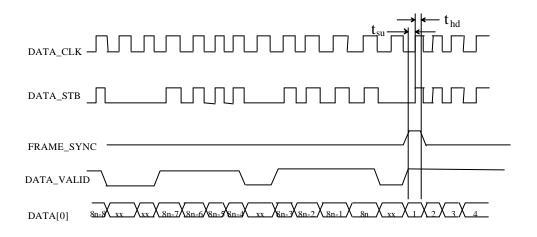

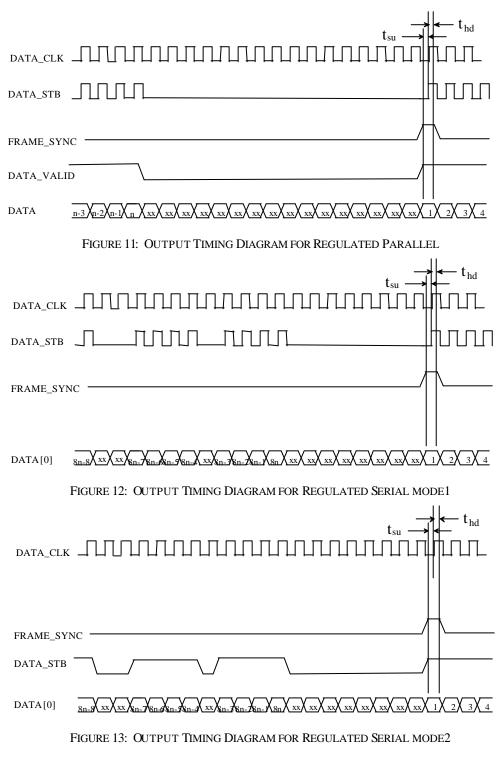

| FIGURE 11: OUTPUT TIMING DIAGRAM FOR REGULATED PARALLEL              | 17 |

| FIGURE 12: OUTPUT TIMING DIAGRAM FOR REGULATED SERIAL MODE1          | 17 |

| FIGURE 13: OUTPUT TIMING DIAGRAM FOR REGULATED SERIAL MODE2          | 17 |

| FIGURE 14: ADC BLOCK DIAGRAM                                         | 19 |

| FIGURE 15: DEMODULATOR BLOCK DIAGRAM                                 | 20 |

| FIGURE 16: NOISE MEASUREMENT CIRCUIT                                 | 22 |

| FIGURE 17: NOISE ACCUMULATOR AS A FUNCTION OF SNR AND TIME           | 23 |

| FIGURE 18: VITERBI DECODER                                           | 24 |

| FIGURE 19: REED SOLOMON DECODER                                      | 28 |

| FIGURE 20: CLOCK SIGNAL GENERATION                                   | 29 |

| FIGURE 21: TYPICAL SET TOP BOX DEMODULATOR                           | 30 |

| FIGURE 22: MECHANICAL CONFIGURATION                                  | 32 |

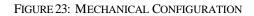

| FIGURE 23: MECHANICAL CONFIGURATION                                  | 34 |

| FIGURE 24: A NALOG PIN CONNECTION                                    | 35 |

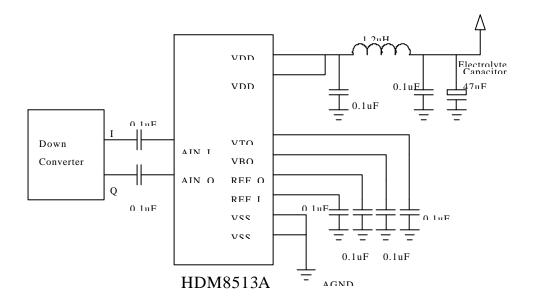

| FIGURE 25: CLOCK GENERATION CIRCUIT                                  |    |

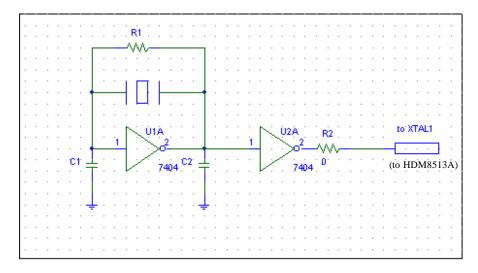

| FIGURE 26: I2C WRITE TO THE HDM8513A                                 |    |

| FIGURE 27: I2C READ FROM THE HDM8513A                                | 41 |

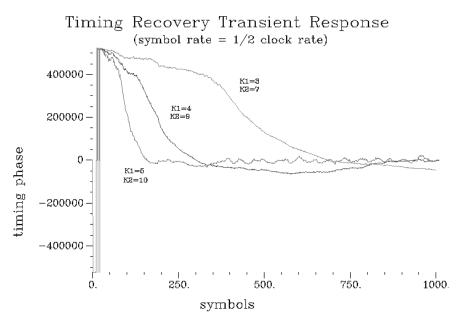

| FIGURE A1: SYMBOL TIMING RECOVERY TRANSIENT RESPONSE                 | 59 |

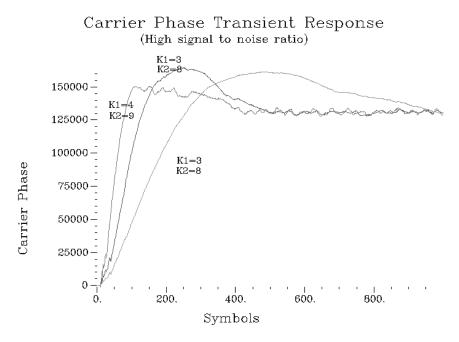

| FIGURE A2: CARRIER PHASE RECOVERY TRANSIENT RESPONSE                 | 60 |

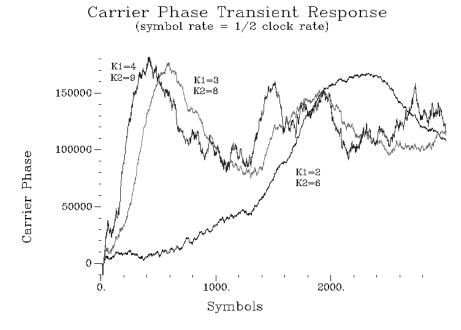

| FIGURE A3: CARRIER PHASE RECOVERY TRANSIENT RESPONSE WITH LOW SNR    |    |

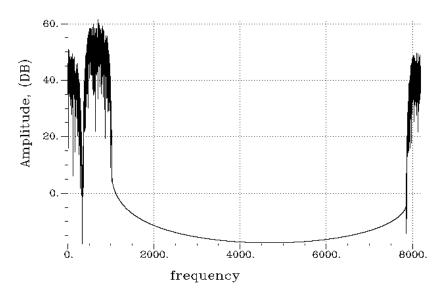

| FIGURE A4: ADJACENT CHANNEL INTERFERENCE OF 10 DB, 1.35 SPACING      | 64 |

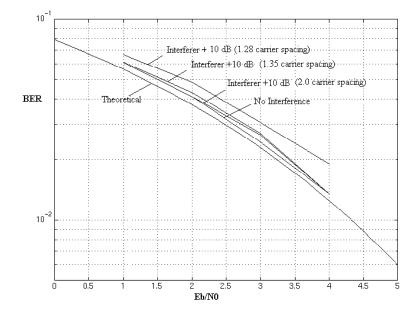

| FIGURE A5: PERFORMANCE WITH INTERFERER AT DIFFERENT CARRIER SPACINGS | 65 |

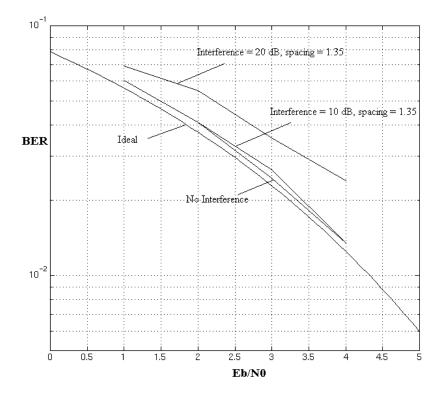

| FIGURE A6: PERFORMANCE WITH +10 DB INTERFERER                        | 66 |

## LIST OF TABLES

| TABLE 1: ABSOLUTE MAXIMUM RATINGS                                 | 8  |

|-------------------------------------------------------------------|----|

| TABLE 2: DC CHARACTERISTICS                                       | 8  |

| TABLE 3: DEMODULATOR SPECIFICATIONS                               | 9  |

| TABLE 4: AC CHARACTERISTICS                                       | 9  |

| TABLE 5: INTEL 80C88A READ CYCLE TIMING PARAMETERS (BUSMODE = 1)  |    |

| TABLE 6: INTEL 80C88A WRITE CYCLE TIMING PARAMETERS (BUSMODE = 1) | 11 |

| TABLE 7: INTEL 8051 READ CYCLE TIMING PARAMETERS (BUSMODE = 1)    |    |

| TABLE 8: INTEL 8051 WRITE CYCLE TIMING PARAMETERS (BUSMODE = 1)   |    |

| TABLE 9:       MOTOROLA READ CYCLE TIMING PARAMETERS (BUSMODE =0) | 14 |

| TABLE 10: MOTOROLA WRITE CYCLE TIMING PARAMETERS (BUSMODE =0)     | 15 |

| TABLE 11: OUTPUT TIMING                                           |    |

| TABLE 12: EXAMPLE OF ACQUISITION TIMING                           |    |

| TABLE 13: I2C SLAVE ADDRESS                                       | 41 |

|                                                                   |    |

## 1. Introduction to the HDM8513A

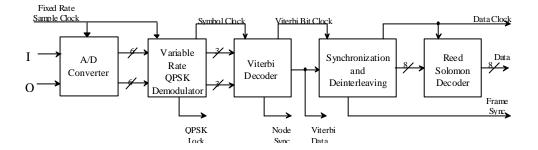

The HDM8513A digital demodulator for direct broadcast satellite receivers is a single chip solution fully compliant with the European Telecommunications Standards Institute (ETSI) specification ETS 300 421. This chip integrates an A/D converter, a variable rate matched filter, a variable rate QPSK demodulator with a Viterbi decoder, a deinterleaver and a Reed Solomon decoder.

The HDM8513A, which is implemented in a 0.35 micron CMOS, Triple Layer Metal Process, provides variable rate capability while operating with a fixed frequency sampling clock. Digital samples of baseband I and Q data are generated by an internal A/D converter, then provided to the demodulator at a fixed sample rate. The root raised cosine filter is implemented internally with fully digital techniques. Similarly, the symbol timing recovery and carrier phase tracking functions are performed entirely in the digital domain. This approach provides minimum constraints on external circuits, thus reducing overall system costs.

The HDM8513A may be configured by an external processor for a specific symbol rate, and carrier frequency along with loop gain parameters. The HDM8513A provides an external AGC signal which is used to control the gain of the analog signal which is applied to the down-converters. And it also provides a digital AGC internally which controls the gain of the signal out of the matched filters. In addition, the HDM8513A provides fully programmable sweep circuitry to aid in initial acquisition when large frequency offsets may be present.

The digital frequency translation capability of the HDM8513A permits this part to be used in frequency multiplexing applications. In this application, an entire transponder bandwidth containing many signals is sampled at a fixed rate. The digital oscillator within the HDM8513A is programmed to the specific desired carrier frequency within that band to permit the selected signal to be passed through the baseband filter and processed by the demodulator circuits.

FIGURE 1: TOP LEVEL BLOCK DIAGRAM

## **1.1 Features and Benefits**

- \* Fully DVB&DSS compliant

- \* Dual 6bit A/D converters

- \* Continuously variable symbol rate from 1Msps to 55Msps (75MHz clock)

- \* Internal digital root raised cosine filter

- \* Less than 0.5 dB implementation loss

- \* Frequency multiplexing capability \* Automated frequency search

- \* Internal bias cancellation

- \* Both wideband and narrowband AGC

- \* Noise calibration for antenna steering

- \* Output data rate as high as 68Mbps

- \* Fixed frequency sampling clock

- \* Simple interface with tuner and analog processing

- \* Microcontroller interface

- \* Eight bit parallel or I2C monitor and control interface

- \* I2C by-pass mode

- \* Two package types

| Part code | Package |

|-----------|---------|

| HDM8513AP | 100PQFP |

| HDM8513AT | 64TQFP  |

# 2. Hardware Specification

| Rating                         | Value                                            | Unit |

|--------------------------------|--------------------------------------------------|------|

| Ambient Temperature under Bias | -10 to 70                                        | С    |

| Storage Temperature            | -65 to 150                                       | С    |

| Ambient Humidity under Bias    | 85(85 c,500hrs)                                  | %    |

| Thermal Resistance(Ja)         | 45                                               | c/W  |

| Junction Temperature           | 150                                              | С    |

| Voltage on Any Pin             | Vss - 0.3V to Vpp + 0.5V                         | V    |

| VDD, IOVDD                     | 5.5                                              | V    |

| Package Material               | - Compound : CEL-4630SX<br>- Lead Frame : Copper |      |

Table 1: Absolute Maximum Ratings

#### Table 2: DC Characteristics

| Symbol | Parameter                                 | Min.    | Max.        | Units | Test Conditions                        |

|--------|-------------------------------------------|---------|-------------|-------|----------------------------------------|

| ססן    | Dynamic Current<br>(Power Supply Current) | -       | 395         | mA    | VDD=3.3, Freq=60Mhz<br>(Typical 367mA) |

| IOVDD  | Interface Power Supply<br>Voltage         | 3       | 3.6         | V     | Normal Operation                       |

| VDD    | Core Power Supply<br>Voltage              | 3       | 3.6         | V     | Normal Operation                       |

| V      | ADC Power Supply<br>Voltage               | 3       | 3.6         | V     | Normal Operation                       |

| VIL    | Input Low Voltage                         | 0       | 0.3V dd     | V     |                                        |

| Viн    | Input High Voltage                        | 0.7V dd | Vdd+<br>0.5 | V     |                                        |

| Vol    | Output Low Voltage                        | -       | 0.4         | V     | IOL = 4 mA                             |

| Vон    | Output High Voltage                       | 2.4     | -           | V     | юн = 4 mA                              |

| Ін     | Input High Current                        | -10     | 10          | uA    | VIL = VDD                              |

| ١L     | Input Low Current                         | -10     | 10          | uA    | VDD = 3.6, VIL =0.5                    |

| Cin    | Input Capacitance<br>(analog pad)         | -       | 10<br>10    | pF    | Typical 8.76pF<br>(8.52pF)             |

| Соит   | Output Capacitance                        | -       | 10          | рF    | Typical 8.83pF                         |

(IOVDD and VDD = 3.3V+ or - 5%, TA = 0 to 70 c, unless otherwise specified)

## Table 3: Demodulator Specifications

| Parameter                     | Min.                     | Max.           |

|-------------------------------|--------------------------|----------------|

| Sampling Clock Frequency      | 1MHz                     | 75MHz          |

| Analog Input Full Scale Range | 0.9 Vpp                  | 1.1 Vpp        |

| Symbol Rate                   | 1Msps                    | 55Msps         |

| Viterbi Data Rate             | -                        | 75Mbps         |

| Reed Solomon Data Rate        | -                        | 69Mbps         |

| Implementation Loss           | -                        | 0.5 dB         |

| Symbol Rate Resolution        | Clock/(2 <sup>20</sup> ) | -              |

| Carrier Frequency Resolution  | Clock/(2 <sup>20</sup> ) | _              |

| Acquisition Sweep Range       | -                        | + or - Clock/2 |

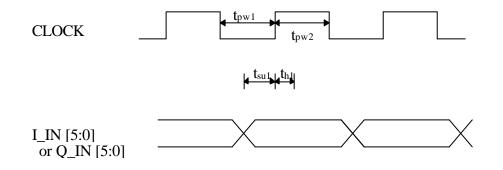

#### Table 4: AC Characteristics

| Symbol           | Parameter                     | Min. | Max. | Unit |

|------------------|-------------------------------|------|------|------|

| t <sub>su1</sub> | Input Data Setup before Clock | 6    | -    | ns   |

| <sup>t</sup> h1  | Input Data Hold after Clock   | 2    | -    | ns   |

| <sup>t</sup> pw1 | Low Pulse Width of Clock      | 8.7  | -    | ns   |

| tpw2             | High Pulse Width of Clock     | 8.1  | -    | ns   |

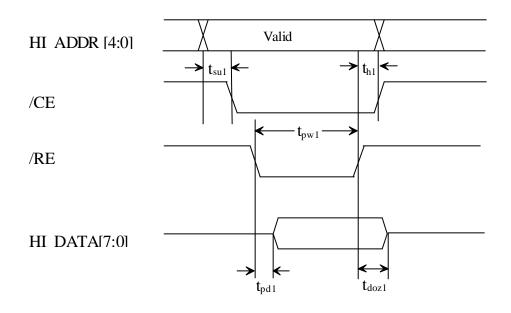

FIGURE 2: INPUT DATA TIMING DIAGRAM

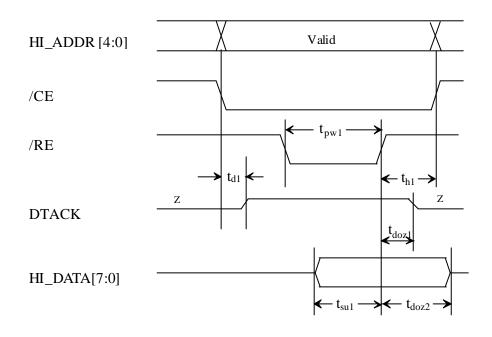

| Symbol            | Parameter                                              | Min. | Max. | Unit |

|-------------------|--------------------------------------------------------|------|------|------|

| <sup>t</sup> su1  | Input Address and /CE Setup before /RE Inactive        | 35   | -    | ns   |

| <sup>t</sup> h1   | Input Address and /CE Hold after /RE Inactive          | 5    | -    | ns   |

| <sup>t</sup> pw1  | /RE Low Duration                                       | 200  | -    | ns   |

| <sup>t</sup> d1   | Delay from /CE to DTACK Active                         | -    | 35   | ns   |

| t <sub>doz1</sub> | Delay from /RE Inactive to DTACK in Tristate Mode      | -    | 10   | ns   |

| t <sub>doz2</sub> | Delay from /RE Inactive to HI_DATA [7:0] Tristate Mode | 10   | -    | ns   |

| Table 5: Intel 80C88A Read Cycle | Timing Parameters (Busmode = 1) |

|----------------------------------|---------------------------------|

|----------------------------------|---------------------------------|

FIGURE 3: INTEL 80C88A READ TIMING DIAGRAM

Note: HI\_ADDR[4:0] is derived from the processor(80C88A) A15-A8 bus and HI\_DATA[7:0] is connected to the AD7 - AD0 bus.

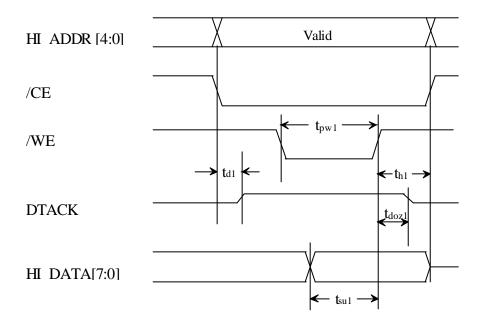

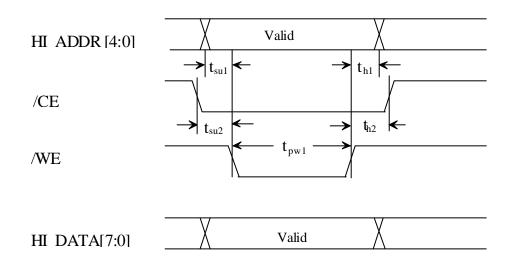

| Symbol            | Parameter                                           | Min. | Max. | Unit |

|-------------------|-----------------------------------------------------|------|------|------|

| t <sub>su1</sub>  | Input Data Setup before /WE Inactive                | 20   | -    | ns   |

| <sup>t</sup> h1   | Input Address, Data and /CE Hold after /WE Inactive | 8    | -    | ns   |

| tpw1              | /WE Low Duration                                    | 200  | -    | ns   |

| <sup>t</sup> d1   | Delay from /CE to DTACK Active                      | -    | 35   | ns   |

| <sup>t</sup> doz1 | Delay from /WE Inactive to DTACK in Tristate Mode   | -    | 15   | ns   |

| Table 6: | Intel | 80C88A | Write ( | Cycle | Timing | Parameters | (Busmode = 1 | ) |

|----------|-------|--------|---------|-------|--------|------------|--------------|---|

|----------|-------|--------|---------|-------|--------|------------|--------------|---|

FIGURE 4: INTEL 80C88A WRITE TIMING DIAGRAM

Note: HI\_ADDR[4:0] is derived from the processor(80C88A) A15-A8 bus and HI\_DATA[7:0] is connected to the AD7 - AD0 bus.

| Symbol            | Parameter                                             | Min. | Max. | Unit |

|-------------------|-------------------------------------------------------|------|------|------|

| <sup>t</sup> su1  | Input Address Setup before /CE Active                 |      | -    | ns   |

| <sup>t</sup> h1   | Input Address and /CE Hold after /RE Inactive         | 5    | -    | ns   |

| <sup>t</sup> pw1  | /RE Active Duration                                   | 400  | -    | ns   |

| <sup>t</sup> pd1  | Delay from /RE Active to HI_DATA [7:0] Valid          | -    | 40   | ns   |

| t <sub>doz1</sub> | Delay from /RE Inactive to HI_DATA[7:0] Tristate Mode | 10   | -    | ns   |

| Table 7: Int | tel 8051 Read Cyc | le Timing Parameters | (Busmode = 1) |

|--------------|-------------------|----------------------|---------------|

|              |                   |                      |               |

FIGURE 5: INTEL 8051 READ TIMING DIAGRAM

| Symbol           | Parameter                                      | Min. | Max. | Unit |

|------------------|------------------------------------------------|------|------|------|

| <sup>t</sup> su1 | Input Address and Data Setup before /WE Active | 5    | -    | ns   |

| <sup>t</sup> h1  | Input Address and Data Hold after /WE Inactive | 5    | -    | ns   |

| <sup>t</sup> pw1 | /WE Active Duration                            | 400  | -    | ns   |

| t <sub>su2</sub> | /CE Setup to /WE Active                        | 5    | -    | ns   |

| <sup>t</sup> h2  | /CE Hold after /WE Inactive                    | 5    | -    | ns   |

| Table 8: Intel 8051 Write Cycle Timir | ng Parameters (Busmode = 1) |

|---------------------------------------|-----------------------------|

|---------------------------------------|-----------------------------|

FIGURE 6: INTEL 8051 WRITE TIMING DIAGRAM

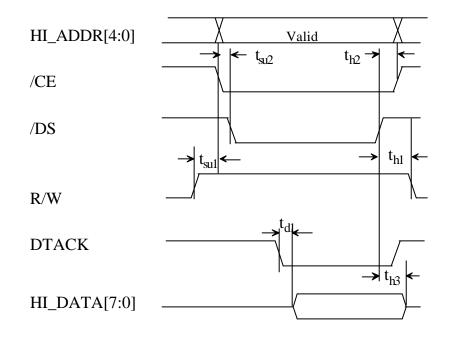

| Symbol           | Parameter                                    | Min. | Max. | Unit |

|------------------|----------------------------------------------|------|------|------|

| <sup>t</sup> su1 | Setup Time of R/W with respect to /CE Active | 5    | -    | ns   |

| <sup>t</sup> su2 | Address Setup with respect to /DS Active     | 5    | -    | ns   |

| <sup>t</sup> d1  | Delay from DTACK Active to Data Valid        | -    | 30   | ns   |

| <sup>t</sup> h1  | R/W Hold with respect to /DS Inactive        | 5    | -    | ns   |

| <sup>t</sup> h2  | Address Hold with respect to /DS Inactive    | 5    | -    | ns   |

| t <sub>h3</sub>  | Data Hold with respect to /DS Inactive       | 10   | -    | ns   |

| Table 9: M | lotorola Read Cy | cle Timing | Parameters | (Busmode =0) |

|------------|------------------|------------|------------|--------------|

|------------|------------------|------------|------------|--------------|

FIGURE 7: MOTOROLA READ TIMING DIAGRAM

Note: External pull-up resistor is required on DTACK.

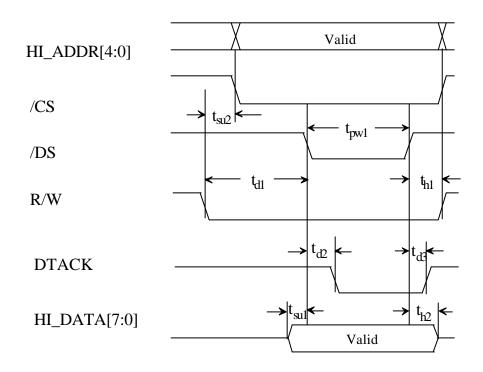

| Symbol           | Parameter                                   | Min. | Max. | Unit |

|------------------|---------------------------------------------|------|------|------|

| <sup>t</sup> su1 | Data Setup to /DS Active                    | 5    | -    | ns   |

| t <sub>su2</sub> | R/W Setup to /CS and Address                | 3    | -    | ns   |

| <sup>t</sup> d1  | /DS Delay from R/W                          | 5    | -    | ns   |

| t <sub>d2</sub>  | DTACK Delay from /DS Active                 | -    | 40   | ns   |

| t <sub>d3</sub>  | DTACK Delay from /DS Inactive               | -    | 10   | ns   |

| <sup>t</sup> pw1 | /DS Active Duration                         | 5    | -    | ns   |

| <sup>t</sup> h1  | Address, /CS and R/W Hold from /DS Inactive | 5    | -    | ns   |

| <sup>t</sup> h2  | Data Hold from /DS Inactive                 | 5    | -    | ns   |

| Table 10: | Motorola Write | <b>Cycle Timing</b> | Parameters | (Busmode =0) |

|-----------|----------------|---------------------|------------|--------------|

|-----------|----------------|---------------------|------------|--------------|

FIGURE 8: MOTOROLA WRITE TIMING DIAGRAM

Note: External pull up resistor is required on DTACK.

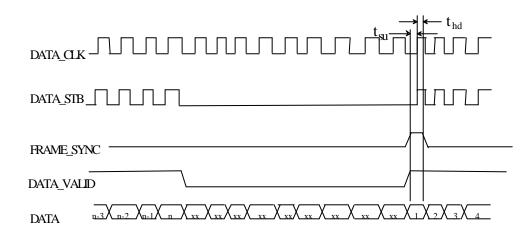

#### Table 11: Output Timing

| Symbol          | Parameter                                      | Min. | Max. | Unit |

|-----------------|------------------------------------------------|------|------|------|

| t <sub>su</sub> | Output Data Setup before DATA_CLK and DATA_STB | 5    | -    | ns   |

| <sup>t</sup> hd | Output Data Hold after DATA_CLK and DATA_STB   | 10   | -    | ns   |

FIGURE 9: OUTPUT TIMING DIAGRAM FOR NORMAL PARALLEL

FIGURE 10: OUTPUT TIMING DIAGRAM FOR NORMAL SERIAL

NOTE : In case of DVB, n is 188 In case of DSS, n is 144

## 3. Technical Overview

## 3.1 Dual Channel Analog to Digital Converter

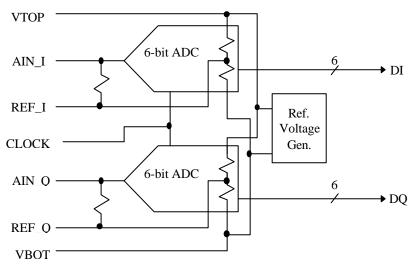

The block diagram shown below illustrates internal configuration of the Dual Channel ADC. Baseband signals, in-phase(I) and quadrature phase(Q), which are generated by down converters, are applied to the dual channel ADC and quantized to 6-bit digital codes respectively. The ADC is optimized to allow AC coupled inputs with full scale input range of 1V + or - 10%. An LSB weight is approximately 15.6 mV.

The full scale input analog conversion range (Vpp) is determined by the voltages of VTOP and VBOT and simply equal to (VTOP - VBOT). The full scale range is defined as the voltage range that accommodates 63 codes of equally spaced LSBs. Also the ADC supplies its own reference voltages for A/D conversions. The voltages can be monitored by external reference pins. The VTOP, VBOT represent top and bottom reference voltages respectively. REF\_I, REF\_Q represent middle reference voltages for each channel. All these 4 reference voltage pins should be by-passed to GND via 0.1uF capacitors. The values of internally generated voltage of VTOP and VBOT are 2.0V and 1.0V respectively. Vpp can be adjusted by externally applying voltages to both VTOP and VBOT pins respectively when different conversion ranges are necessary. VTOP can be adjusted as high as 2.3V and VBOT can be as low as 0.5V. A larger input range can be established by taking VTOP higher and VBOT lower than on-chip generated voltages.

To supply necessary bias voltages for AC coupled applications, REF\_I and REF\_Q, which are middle reference voltages for I and Q channel, are connected to the analog input pins (AIN\_I and AIN\_Q) respectively through 40 kohm resistors, as shown in the block diagram. For DC coupled applications, these voltages can be used to feed back offset compensation signals.

To insure optimum performance, a low impedance analog ground plane is recommended and should be separated from other digital ground planes. The analog power supplies should be by-passed at device to analog ground through 0.1uF ceramic capacitors.

FIGURE 14: ADC BLOCK DIAGRAM

#### 3.2 Variable Rate Demodulator

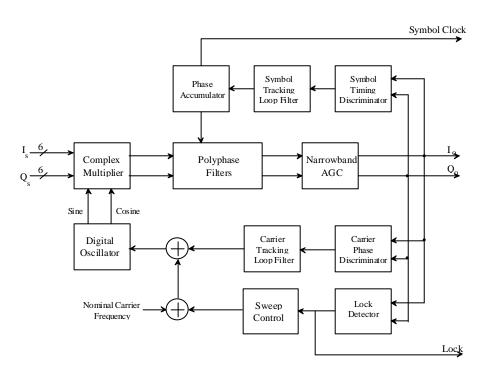

The block diagram illustrates the overall configuration of the variable rate QPSK demodulator. Baseband in-phase (I) and quadrature (Q) inputs are applied to the demodulator at a fixed sampling rate. These digital samples are produced by A/D converters which employ AC coupling to minimize DC offset.

FIGURE 15: DEMODULATOR BLOCK DIAGRAM

The carrier frequency error associated with these samples is removed digitally during tracking operations by a complex multiplier and a digitally controlled oscillator, sometimes called a numerically controlled oscillator (NCO). During initial acquisition, coarse frequency error is removed by a combination of the digital AGC within the HDM8513A and external analog tuning circuits.

A polyphase filter performs the root raised cosine filtering of the frequency corrected baseband samples. This filter, which implements the function of equation (1), is always configured to have an impulse response duration of 4 symbols regardless of the programmed symbol rate. For low symbol rates, a large number of samples are used, while for high symbol rates a relatively low number of samples are processed for each filter output. The outputs of the polyphase filters are applied to a digital narrowband AGC which insures that the signal is optimally scaled to the Viterbi decoder to an accuracy of + or - 0.5 dB to insure optimum FEC performance.

(1)

$y[k] = \Sigma h[n] x[k-n]$

In addition to optimizing performance of the Viterbi decoder, the digital narrowband AGC also insures that the performance of the symbol timing and carrier tracking loops is independent of

signal level variations. An analog wideband AGC is also employed to insure that the analog signal applied to the A/D converters is properly scaled.

Both the symbol timing and carrier tracking loops are implemented digitally, which eliminates the need for external connections to analog tuning components during steady state operation. This causes the requirements on the analog presampling filter to be relaxed, permitting a lower cost analog front end. For systems which require a narrowband presampling filter, and have the potential for significant frequency error in the LNB (several MHz) the HDM8513A provides a high resolution measure of carrier frequency to permit periodic readjustment of the front end tuner frequency to compensate for drift. The host processor periodically reads the frequency register, then computes appropriate correction to the tuner frequency.

The nominal symbol rate and the nominal carrier frequency are programmed into the demodulator to an accuracy provided by 20 bits of resolution, and the system accuracy is equivalent to that of the fixed frequency sampling clock.

During initial acquisition, the HDM8513A provides an automated sweep program to facilitate carrier acquisition. The host processor loads a 20 bit register which determines the initial carrier frequency. A 16 bit register is programmed with the number of symbol times the receiver will dwell at each frequency. If the receiver remains at the initial frequency for the programmed number of symbol times without achieving lock, the carrier frequency is incremented by the step frequency value programmed into another 16 bit register. If no lock is achieved, the receiver will continue to increment the frequency until the maximum number of search frequencies, as determined by the value in an eight bit register, is achieved. When the maximum number of search frequencies is reached, the carrier frequency returns to the initial value and the entire process is repeated. Once the host processor determines that lock is achieved by observing the lock flag, it then inhibits the sweep function and programs loop bandwidth parameters which are optimized for steady state performance.

#### 3.3 Noise Measurement Circuit

When the DBS system is being installed in any place, the most difficult part of the installation is accurate pointing of the antenna toward the satellite. Inaccurate pointing results in loss of margin and greater potential for outages in adverse weather conditions. Existing systems use information from the demodulator forward error correction circuits to provide a measure of antenna pointing. Unfortunately, this method is useful over a range of only several dB above system threshold.

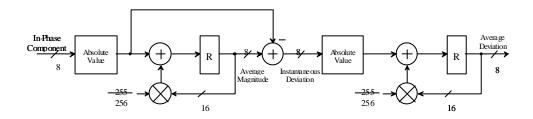

The HDM8513A employs a unique circuit for accurate measure of signal strength over a 20 dB range of signal to noise ratio. This method, illustrated in the block diagram, makes use of the fact that the demodulator provides 8 bits of resolution for each of the quadrature output components. This high resolution provides a means of measuring the noise component with great accuracy.

The eight bit in-phase demodulator filter output is detected by an absolute value circuit, then passed through an IIR to provide a measure of average signal amplitude. Each sample is then subtracted from this average amplitude to provide an instantaneous noise sample. The absolute value of these noise samples are then averaged by a second IIR to provide a measure of the noise which is roughly proportional to the noise power and inversely proportional to signal to noise ratio.

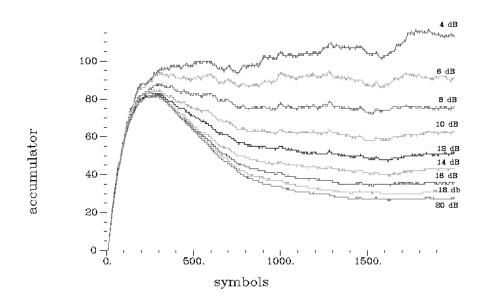

Finally, the Figure 17 illustrates the results of simulations under different noise conditions. This figure illustrates that for signal-to-noise ratio as high as 19 dB, the noise measurement circuit provides a meaningful measure of signal power with worst case resolution of 1 dB.

FIGURE 16: NOISE MEASUREMENT CIRCUIT

FIGURE 17: NOISE ACCUMULATOR AS A FUNCTION OF SNR AND TIME

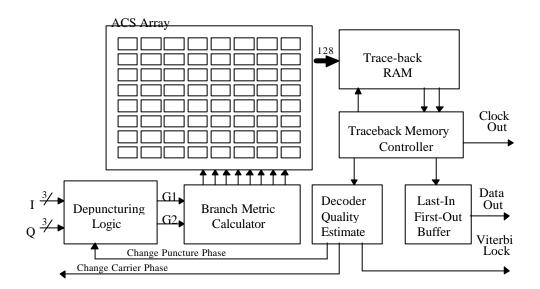

### 3.4 Viterbi Decoder

The Viterbi decoder accepts 3 bit soft decision samples of the in-phase (I) and quadrature (Q) components of the received signal. Once QPSK lock has been achieved, the decoder searches for the correct code rate, starting with rate 3/4, then proceeding to rate 2/3, 5/6, 7/8 and finally rate 1/2. Each of the possible synchronization phases at each rate is tested as well as the two possible carrier phase ambiguity conditions. Polarity reversal is corrected in the word synchronization logic. Viterbi lock is achieved when the trellis traceback algorithm converges, on the average, within a prescribed number of symbols.

Although the algorithm automatically tests for carrier phase ambiguity, there is no provision to automatically correct for phase reversal. Phase reversal can occur if the receiver chain, consisting of an LNB and the tuner, provides an odd number of high side frequency translation operations. A system may be required to operate with different LNBs, some of which provide phase reversal. This condition may be corrected by the host processor, which can set a bit in the down converter to correct for phase reversal.

The Viterbi decoder employs the radix two algorithm. The output buffer reserializes the data which is made available, along with the Viterbi data clock as external signals. These signals permit verification of the DVB specification which is referenced to the Viterbi decoder output.

FIGURE 18: VITERBI DECODER

## 3.5 Autonomous Acquisition

The HDM8513A provides several features to permit signal acquistion with minimal interaction with the host microcontroller. The host microcontroller must configure the HDM8513A for a specific symbol rate, carrier frequency, carrier sweep conditions, and tracking loop bandwidth. The microcontroller also must monitor lock status to determine when acquisition is achieved. There are many provisions in the HDM8513A to enable the system designer to implement custom algorithms for specific requirements.

The microcontroller first must set the lower edge of the carrier search range in the Carrier Frequency registers (04, 05 and 06). Then the processor configures the Carrier Sweep Step Size register (09, 0A) to a value which is less than two times the carrier pull-in range. The number of symbols per dwell is defined in registers (0B,0C), and is typically set to a value of 500 to 1000. The total search range is set by the Number of Search Frequencies as defined in register 0D. The total sweep frequency range is this number times the Carrier Sweep Step Size. The sweep process stops once QPSK carrier lock is detected. If no lock is detected, the sweep process continuously repeats.

The QPSK demodulator may lock to any one of four different phase reference states, only one of which produces true I and Q data as it was modulated at the transmitter. If the local phase reference is plus 90 degrees or minus 90 degrees with respect to the true phase, the information provided to the Viterbi decoder will be unintelligible. If the Viterbi decoder is unable to achieve valid lock, it will reattempt lock with a 90 degree phase shift, without external intervention.

In the event that the local phase is 180 degrees from the true phase, the data provided to the Viterbi decoder will be inverted, but otherwise valid. The code employed by the Viterbi decoder is transparent, thus the data from the Viterbi decoder will be inverted if the input is inverted. This situation is corrected in the word synchronization circuit. This circuit searches for the unscrambled sync word which occurs once per frame (every 204 bytes at the Viterbi output). Once correlation with the sync word is found, the data is reformatted as a series of bytes with the beginning of each 204 byte frame identified to provide the synchronization information required for the deinterleaver and the Reed Solomon decoder. If the polarity of the sync word is incorrect, the data is inverted before further processing without external interaction.

The HDM8513A supports five different code rates, including 1/2, 2/3, 3/4, 5/6 and 7/8. When rate 1/2 is employed, there is a one-to-one correspondence between incoming I and Q samples and G1 and G2 terms required by the Viterbi decoder. The higher rates employ punctured coding techniques which periodically cause either a G1 or G2 term to be deleted. The puncturing pattern can have 6 possible ambiguity states for rate 2/3, 4 states for rate 3/4, 6 states for rate 5/6 and 8 states for rate 7/8. As part of the Viterbi decoding acquisition process, each puncturing state of each code must be tested. Total acquisition requires search of 26 different conditions. The process starts with rate 3/4 coding and proceeds sequentially to rate 2/3, 5/6, 7/8, and finally rate 1/2.

In some systems, it may be possible to experience spectral inversion. This might occur when different combinations of LNBs and tuners are employed which implement different frequency translation schemes. Correction of spectral inversion must be corrected with host processor interaction. If the host processor detects that QPSK lock is achieved, but Viterbi lock has not occurred within a specified time, then a bit must be set in the demodulator which reverses the spectrum.

The table below illustrates a typical acquisition timing. For this example, the symbol rate is one half of the clock rate. The code rate is set to 5/6, which requires 13 trial and errors before node sync is achieved. The carrier search logic requires 10 dwells at different frequencies (500 symbols per dwell) before demodulator lock is achieved.

|                     | Bit Times | Symbols | Clock Cycles |

|---------------------|-----------|---------|--------------|

| Carrier Search      | 8,333     | 5,000   | 10,000       |

| Viterbi Node Sync   | 2,652     | 1,591   | 3,182        |

| Byte Sync           | 16,000    | 9,600   | 19,200       |

| Deinterleaver Flush | 19,584    | 11,750  | 23,500       |

| Reed Solomon        | 1,632     | 979     | 1,958        |

| Total Timing        | 48,201    | 26,950  | 57,840       |

Table 12: Example of Acquisition Timing

The total time required for acquisition could vary widely, depending upon the carrier search range and the time required for Viterbi node sync. For this example, however, the Byte Sync time and the time required to flush the deinterleaver dominates the total time. If a 60MHz clock were employed, the total acquisition time would be 0.963 milliseconds for this example

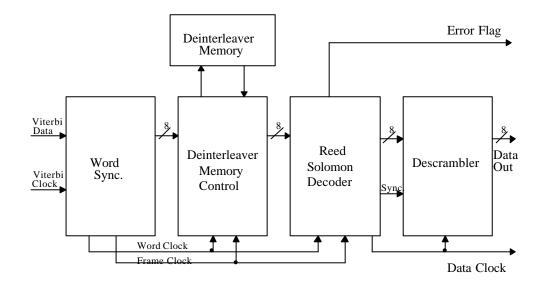

## 3.6 Reed Solomon Decoder

The serial output from the Viterbi is provided to the Word Sync circuits which searches for the eight bit frame sync word which occurs every 204 bytes. By detecting the polarity of the sync word, this module can correct polarity reversals in the data provided by the Viterbi decoder.

Byte serial data is provided to the convolutional deinterleaver, which reorders the received symbols. This process causes errors, which typically occur in bursts from the Viterbi decoder, tobe distributed randomly over many blocks. This deinterleaved data is then provided to the Reed Solomon decoder which can reduce an error rate of 2 x10<sup>-4</sup> from the Viterbi decoder to less than 1 in 10<sup>-10</sup>. The Reed Solomon decoder accepts input data in blocks of 204 bytes and produces error corrected blocks of 188 bytes. Maximum 8 bytes per a RS block can be corrected in RS decoder. Reedsolomon block includes on-chip BER calculator at the output of Viterbi to monitor signal quality or estimate the SNR of incoming signal. The calculated value can be read by accessing two read registers via utility bus such as I2C. It represents the number of errors among 2<sup>20</sup> data bits.

The next process is descrambling, not to be confused with the descrambling which is part of conditional access. The purpose of scrambling the transmitted data and performing the inverse in the receiver is to insure that the spectrum of the transmitted waveform is always evenly distributed without significant discrete spectral lines. Without the scrambling/descrambling process, a transmitted sequence of all ones or all zeroes would result in strong spectral components and could interfere with other signals in the same satellite transponder.

The final process is data regulation. Viterbi Data and Viterbi Clock occur irregularly according to the code rate. Data clock regulation makes it possible to interface with external common interface devices. To make external bus interface more flexible, interface mode such as parallel or serial can be selected by mode selection register.

| Parameter         | Register              |

|-------------------|-----------------------|

| Regulate_data_clk | Bit 5 of 14H register |

| Serial_valid      | Bit 6 of 14H register |

| Mode_serial       | Bit 0 of 18H register |

#### • NORMAL INTERFACE MODE (parallel/serial)

If regulate\_data\_clk is reset, both parallel interface and serial interface work in normal operation which is same as HDM8513 regardless of serial\_valid bit. Parallel interface or serial interface can be alternated by modifying mode\_serial bit (Refer to Figure 9 and Figure 10)

#### • **REGULATED INTERFACE MODE (parallel)**

If regulate\_data\_clk is set,all interfaces are from internal FIFO designed to regulate irregular interface signals. Data clock cycle is a little bit faster than the average of cycle of irregular data clock, so meaningless data can be output in invalid data period. (Refer to Figure 11)

#### • REGULATED INTERFACE MODE (serial)

If mode\_serial bit is set in the regulate interface mode, regulate interface mode is enabled for serial interface. Regular serial interface mode has two modes for more flexibility. The mode selection is controlled by serial\_valid bit. If serial\_valid is reset, DATA\_STB signal alternates when every valid bit is out (mode1). While serial\_valid is set, DATA\_STB signal sustains high when valid bit is out (mode2). (Refer to Figure 12 and Figure 13)

FIGURE 19: REED SOLOMON DECODER

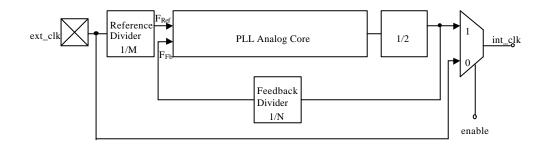

#### 3.7 Clock Generation PLL

An integrated VCO is locked to MxN times a reference frequency provided by a external clock.

FIGURE 20: CLOCK SIGNAL GENERATION

This programmable PLL consists of a PLL analog core, a reference divider with a divider ratio M, a feedback divider with a divider ratio N, and a divider which askes the duty cycle 1/2. Reference divider and feedback divider are used to synthesize various frequencies from a reference frequency,  $f_{ext\_clk}$ .

Since PLL synchronizes the frequency and phase of two signals,  $F_{\text{Ref}}$  and  $F_{\text{Fb}}$ ,

$$\frac{f_{ext\_clk}}{M} = \frac{f_{int\_clk}}{N}$$

Internal clock is calculated as follows

$$f_{int\_clk} = \frac{N}{M} f_{ext\_clk}$$

The following two PLL modes are provided to control PLL.

(1) PLL Enable mode : The internal clock is connected to the generated clock of the PLL.

(2) PLL Disable mode : The PLL is bypassed and the external clock is directly connected to the internal clock.

More information can be found on the part of the write register.

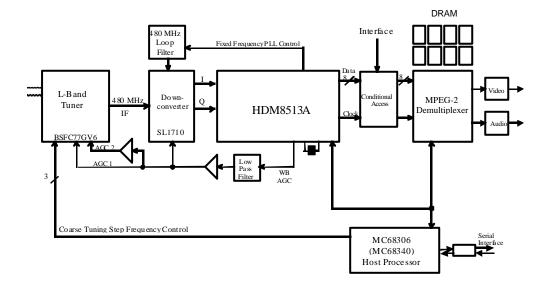

#### 3.8 DBS Receiver

The HDM8513A DVB Demodulator including a dual A/D converter and the MPEG-2 decoder provide the core digital processing technology for a DBS receiver conforming with the DVB standard.

FIGURE 21: TYPICAL SET TOP BOX DEMODULATOR

A tuner accepts an L-band RF input from the antenna/LNB assembly located outside the building. A host processor controls the tuner to the nominal center frequency of the target signal. Baseband I and Q outputs from the downconverter are applied to an A/D converter pair which is sampled at a fixed rate, 60MHz as illustrated in this example. The tuner is required to filter the received baseband signal to a bandwidth less than half the sampling rate, but is not required to perform matched filtering.

Once the HDM8513A has locked to the target signal, the host processor may read the internal registers to determine the steady state frequency error. This error would be used to make period corrections to the programmed frequency of the tuner PLL.

The HDM8513A provides an output which can be used to control the analog AGC in the tuner. This digital signal must be filtered and amplified before applying it to the AGC control element. When the loop is closed, the signal applied to the A/D converters is optimally scaled.

# 4. Mechanical Specifications

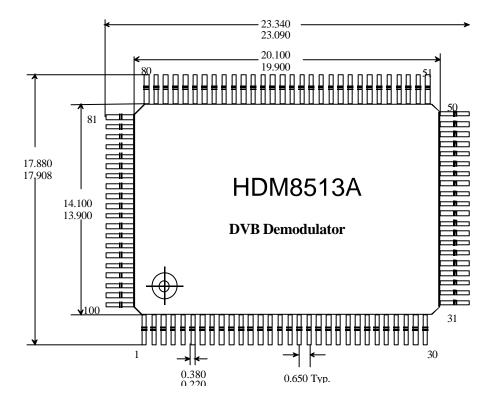

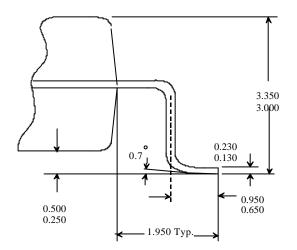

## 4.1 100 Pin Quad Flat Pack

## 4.1.1 Pin Assignment

| 4  |              | 26 | TESTS | 54 |             | 76  | DTACK      |

|----|--------------|----|-------|----|-------------|-----|------------|

| 1  | DATA_CLK     | 26 | TEST6 | 51 | HI_ADDR4    | 76  | DTACK      |

| 2  | FRAME_ERROR  | 27 | VDDA  | 52 | HI_ADDR3    | 77  | SDA_I2CO   |

| 3  | FRAME_SYNC   | 28 | VSSA  | 53 | HI_ADDR2    | 78  | SDA_I2C    |

| 4  | VDD          | 29 | VTOP  | 54 | HI_ADDR1    | 79  | SCL_I2CO   |

| 5  | VSS          | 30 | AIN_I | 55 | HI_ADDR0    | 80  | SCL_I2C    |

| 6  | LNB_TONE     | 31 | VSSA  | 56 | VDD         | 81  | IOVDD      |

| 7  | SIGMADELTA   | 32 | VDDA  | 57 | VSS         | 82  | IOVSS      |

| 8  | SYMBOL_CLOCK | 33 | REF_I | 58 | HI_DATA7    | 83  | R/W(/RE)   |

| 9  | WB_AGC       | 34 | REF_Q | 59 | HI_DATA6    | 84  | /CE        |

| 10 | QPSK_LOCK    | 35 | AIN_Q | 60 | HI_DATA5    | 85  | /DS(/WE)   |

| 11 | IOVDD        | 36 | VBOT  | 61 | HI_DATA4    | 86  | VDD        |

| 12 | IOVSS        | 37 | VSS   | 62 | IOVDD       | 87  | VSS        |

| 13 | TEST15       | 38 | TEST5 | 63 | IOVSS       | 88  | DATA7      |

| 14 | TEST14       | 39 | TEST4 | 64 | HI_DATA3    | 89  | DATA6      |

| 15 | TEST13       | 40 | TEST3 | 65 | HI_DATA2    | 90  | DATA5      |

| 16 | TEST12       | 41 | VDD P | 66 | HI_DATA1    | 91  | LOCK       |

| 17 | VDD          | 42 | VSS P | 67 | HI_DATA0    | 92  | DATA4      |

| 18 | VSS          | 43 | TEST2 | 68 | VDD         | 93  | DATA3      |

| 19 | TEST11       | 44 | TEST1 | 69 | VSS         | 94  | IOVDD      |

| 20 | TEST10       | 45 | TEST0 | 70 | VB_NODESYNC | 95  | IOVSS      |

| 21 | TEST9        | 46 | XTAL1 | 71 | VB_CLOCK    | 96  | DATA2      |

| 22 | TEST8        | 47 | CLOCK | 72 | VB_DATA     | 97  | DATA1      |

| 23 | IOVDD        | 48 | IOVDD | 73 | VDD         | 98  | DATA0      |

| 24 | IOVSS        | 49 | IOVSS | 74 | VSS         | 99  | DATA_VALID |

| 25 | TEST7        | 50 | RESET | 75 | BUSMODE     | 100 | DATA_STB   |

#### 4.1.2 Package Dimensions

#### All Dimensions in mm

FIGURE 22: MECHANICAL CONFIGURATION

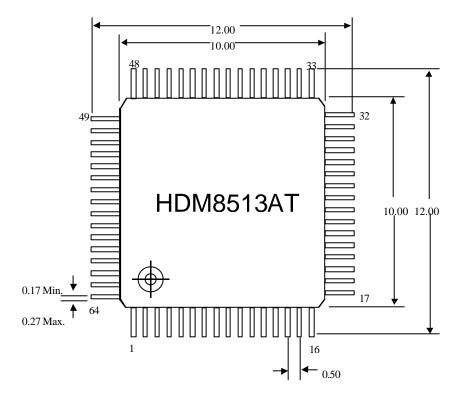

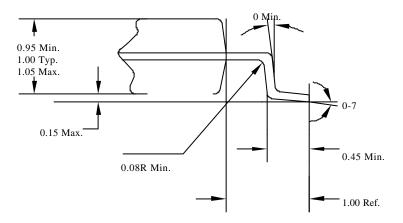

## 4.2 64 Pin Thin Quad Flat Pack

4.2.1 Pin Assignment

| 1  | FRAME_ERROR | 17 | VSSA  | 33 | VDD      | 49 | IOVSS      |

|----|-------------|----|-------|----|----------|----|------------|

| 2  | FRAME_SYNC  | 18 | VDDA  | 34 | VSS      | 50 | VDD        |

| 3  | LNB_SYNC    | 19 | REF_I | 35 | I2C_ADD2 | 51 | VSS        |

| 4  | WB_AGC      | 20 | REF_Q | 36 | IOVDD    | 52 | DATA7      |

| 5  | IOVDD       | 21 | AIN_Q | 37 | IOVSS    | 53 | DATA6      |

| 6  | IOVSS       | 22 | VBOT  | 38 | I2C_ADD1 | 54 | DATA5      |

| 7  | TEST13      | 23 | VSSA  | 39 | I2C_ADD0 | 55 | LOCK       |

| 8  | TEST12      | 24 | VDD   | 40 | VDD      | 56 | DATA4      |

| 9  | VDD         | 25 | VSS   | 41 | VSS      | 57 | DATA3      |

| 10 | VSS         | 26 | N/C   | 42 | VB_CLOCK | 58 | IOVDD      |

| 11 | TEST11      | 27 | N/C   | 43 | VB_DATA  | 59 | DATA2      |

| 12 | TEST10      | 28 | N/C   | 44 | BUSMODE  | 60 | DATA1      |

| 13 | TEST9       | 29 | XTAL1 | 45 | SDA_I2C0 | 61 | DATA0      |

| 14 | TEST8       | 30 | IOVDD | 46 | SDA_I2C  | 62 | DATA_VALID |

| 15 | VTOP        | 31 | IOVSS | 47 | SCL_I2C0 | 63 | DATA_STB   |

| 16 | AIN_I       | 32 | RESET | 48 | SCL_I2C  | 64 | DATA_CLK   |

#### 4.2.2 Package Dimensions

#### All Dimensions in mm

## 4.3 Recommended Analog Pin Connection

FIGURE 25: CLOCK GENERATION CIRCUIT

# 5. Signal Description

# 5.1 Inputs

| XTAL1 | XTAL1 can be configured either for sampling clock input or PLL reference clock input. The sampling clock rate must be a minimum of 1.33 times the symbol rate of the signal to be processed and at least equal to the total bandwidth of the signal to be processed. |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET | A low on this signal causes the chip to be initialized. I/O registers are not cleared by this signal. This signal is asynchronous with respect to the clock.                                                                                                         |

| AIN_I | Analog Input Signal for I channel. This should be AC coupled with Analog Input Source via 0.1uF capacitor.                                                                                                                                                           |

| AIN_Q | Analog Input Signal for I channel. This should be AC coupled with Analog Input Source via a 0.1uF capacitor.                                                                                                                                                         |

# 5.2 Outputs

| VTOP       | Top Reference Voltage Output of about 2.0V. It should be bypassed to GND by 0.1uF capacitor. External bias voltage can be applied if necessary. |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| VBOT       | Bottom Reference Voltage Output of 1.0V. It should be bypassed to GND by a 0.1uF capacitor. External bias voltage can be applied if necessary.  |

| REF_I      | Middle Reference Voltage for I Channel. It should be bypassed to GND by a 0.1uF capacitor.                                                      |

| REF_Q      | Middle Reference Voltage for Q Channel. It should be bypassed to GND by a 0.1uF capacitor.                                                      |

| DATA [7:0] | The eight bit output data is provided in parallel format to be handed to an MPEG decoder for video and audio decompression.                     |

| DATA_CLK     | The DATA_CLK is used to latch data and control signal of transport<br>stream. The data and control signals can be programmed to be<br>latched either at positive or negative edge of DATA_CLK. This signal is<br>used in conjunction with DATA_VALID to transfer data from the<br>HDM8513A. The DATA_CLK will continue to toggle during the 16<br>bytes that the DATA_VALID signal indicates that no data is available<br>(see figure 9 and 10). |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DATA_VALID   | When this signal is true, data is valid. This signal is not true during the time the 16 bytes of redundancy information is transmitted for the Reed Solomon decoder.                                                                                                                                                                                                                                                                             |

| FRAME_SYNC   | This signal is true at the first byte of a block of 188/144 bytes.                                                                                                                                                                                                                                                                                                                                                                               |

| DATA_STB     | This signal is used to transfer data from the HDM8513A to an MPEG decoder. This signal goes from low to high when a new byte of a 188 /144byte MPEG2 data stream block is available. This signal is inactive during the time the 16 redundancy bytes are transferred.                                                                                                                                                                            |

| FRAME_ERROR  | This signal goes true when the Reed Solomon decoder detects that an uncorrectable number of errors have occurred. The error flag in the MPEG2 output stream is also set when this flag goes high.                                                                                                                                                                                                                                                |

| WB_AGC       | This one bit output provides a measure of the external analog gain<br>required for optimizing the signal applied to the analog to digital<br>converters. This signal must be filtered, then applied to the analog<br>gain control.                                                                                                                                                                                                               |

| CLOCK        | This is a buffered clock output signal which may be used to drive other devices with the same clock which drives the HDM8513A.                                                                                                                                                                                                                                                                                                                   |

| QPSK_LOCK    | This signal goes true when the QPSK demodulator has achieved phase lock.                                                                                                                                                                                                                                                                                                                                                                         |

| VB_NODESYNC  | This signal goes true when the Viterbi decoder has achieved node synchronization.                                                                                                                                                                                                                                                                                                                                                                |

| LOCK         | This signal goes true when the output data is valid and all synchronization functions have been performed.                                                                                                                                                                                                                                                                                                                                       |

| SYMBOL_CLOCK | This signal, used for test purposes, goes true for a duration of one clock cycle for each received symbol. For symbol rates equal or greater than half the clock frequency, this signal at times may remain high for two successive clock cycles to indicate that two symbols have occurred.                                                                                                                                                     |

| VB_DATA      | The serial output of the Viterbi Decoder is provided on this pin. The information rate at this point is less than the rate of the input clock (less than 60Mbps if a 60MHz clock is employed). As long as valid convolutional encoding is employed, there is no constraint that the input signal adheres to MPEG2 format. This data is tapped priod to the polarity correction circuitry, so the data at this point may be inverted.             |

| VB_CLOCK   | The positive edge of this signal indicates that VB_DATA is valid.                                                                                                                                               |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SIGMADELTA | This is an one bit Sigma Delta D/A converter which has 8 bits of resolution. This output must be filtered with an analog low pass filter off the chip. This output may be used for any external analog control. |

| LNB_TONE   | This is a 22KHz clock output to control the LNB.                                                                                                                                                                |

| TEST[15:0] | The data provided on the test output signals is defined by data value of register 14H. Refer to register 14H.                                                                                                   |

# **5.3 Monitor and Control Interface**

Three different modes are supported for the monitor and control interface. Two of the modes are 8 bit parallel interfaces, one which supports Intel microcontrollers and the other intended for Motorola microcontrollers. The third mode is a serial interface conforming to the I2C standard.

The I2C mode is activated by placing BUSMODE high at the same time both /RE and /WE are low simultaneously. When this mode is active, the seven bit I2C slave address of the HDM8513A is configured by the seven least significant bits of the HI\_DATA[7:0] bus.

| HI_DATA [7:0] | This bi-directional data bus is used for transferring control parameters to<br>the demodulator and for reading the status registers within the<br>demodulator.                                                                                                                                           |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| /CE           | Chip enable is an active low input to the demodulator which signifies that the other control signals are active.                                                                                                                                                                                         |

| /RE           | Read Enable is an active low input to the device which, when active at the same time chip enable is true, permits the device to drive the HI_DATA [7:0] lines. When BUSMODE is 0 (Motorola), this pin is read / not write (see timing diagrams).                                                         |

| /WE           | Write enable is an active low input to the device which, when true at the same time chip enable is true, causes input data on the HI_DATA [7:0] bus to be transferred to the register defined by the HI_ADDR [4:0] bus. When BUSMODE is 0 (Motorola), this pin is not data strobe (see timing diagrams). |

| HI_ADDR [4:0] | The address bus defines which location within the device is to be accessed during a read or write operation.                                                                                                                                                                                             |

| BUSMODE       | BUSMODE selects the type of microcontroller/processor used to setup the chip. When high, an Intel processor/microcontroller interface is used. When low, a Motorola processor interface is used.                                                                                                         |

| DTACK         | Data Acknowledge/Data Ready is a tristate output signal which informs the controlling processor that a data transfer has been acknowledged by the HDM8513A.                                                                                                                                              |

| SCL_I2C       | This pin provides the clock for the I2C interface when that mode is active.                                                                                                                                                                                                                              |

| SDA_I2C       | This pin is the data for the I2C interface and requires an external pull-up resistor as per the I2C standard.                                                                                                                                                                                            |

| SDA_I2CO      | This pin, which can be by-passed, is the data for the I2C interface.                                                                                                                                                                                                                                     |

| SCL_I2CO      | This pin, which can be by-passed, provides the clock for the I2C interface.                                                                                                                                                                                                                              |

## 5.4 I2C Mode

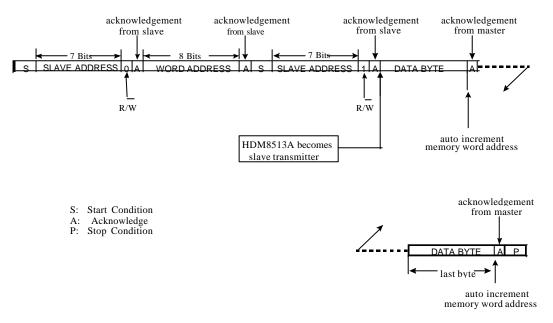

The HDM8513A utilizes the subaddress technique when the I2C mode is employed. In all cases, the HDM8513A behaves as the slave device (transmitter or receiver), whilst the host behaves as the master device. The seven bit slave address of the HDM8513A is user selectable, being defined by the inputs to HI\_DATA[6:0] when the HDM8513A is in I2C mode.

Further information on the I2C bus formats and protocols is contained in the Philips Semiconductors I2C specification.

In a 100pin configuration, SDA\_I2CO and SCL\_I2CO are added to provide a by-passing function. When I2C bypass bit is set to zero, SDA\_I2CO and SCL\_I2CO are disabled.

#### 5.4.1 I2C Write to HDM8513A

The master initiates communication with the HDM8513A by generating a start condition and then sending the HDM8513A the slave address defined by the seven bit hardwired address on HI\_DATA [6:0]. Per I2C convention, the eighth bit in the address byte is a read/not write bit, and should be set to zero. The HDM8513A will acknowledge the correctly sent slave address, following which the master sends an eight bit word address; this is the address of the first HDM8513A register to be written to. Once the word address has been acknowledged by the HDM8513A, the master can then transmit the byte to be written to the word address. Once this byte is acknowledged by the HDM8513A, the word address is automatically incremented and further data bytes may be transmitted by the master as necessary; one transmission may therefore contain a number of bytes of data to be written to a sequential set of addresses (dummy bytes should be written to addresses is atternated by the master generating a stop condition. Figure 25 depicts this protocol.

#### FIGURE 26: I2C WRITE TO THE HDM8513A

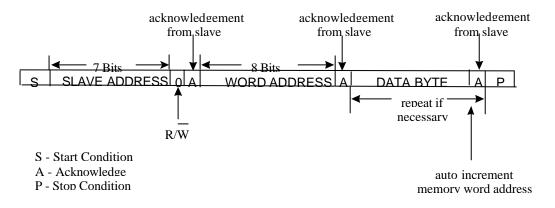

#### 5.4.2 I2C Read from the HDM8513A

To read information from the HDM8513A, the master must first write the desired word address. Hence the master must first generate a start condition and transmit the seven bit HDM8513A slave address defined on HI\_DATA[6:0], with the eighth bit (read/not write) set to zero. Once this has been acknowledged by the HDM8513A, the master transmits the first word address from which it wishes to read information. The master must then generate a second start condition and

retransmit the HDM8513A slave address, this time with the read/not write bit set to one (read). This will be acknowledged by the HDM8513A, which then assumes the role of slave transmitter and transmits the requested byte. This byte should be acknowledged by the master receiver. If no stop condition is generated by the master, the HDM8513A will increment its word address pointer and transmit the next byte of information. This process is detailed in Figure 26.

FIGURE 27: I2C READ FROM THE HDM8513A

| Table | 13: | I2C | Slave | Address |

|-------|-----|-----|-------|---------|

|-------|-----|-----|-------|---------|

| I2C_ADD0 | I2C_ADD1 | I2C_ADD2 | I2C Address |

|----------|----------|----------|-------------|

| 0        | 0        | 0        | 0000000     |

| 1        | 0        | 0        | 0000011     |

| 0        | 1        | 0        | 0001100     |

| 1        | 1        | 0        | 0001111     |

| 0        | 0        | 1        | 0110000     |

| 1        | 0        | 1        | 0110011     |

| 0        | 1        | 1        | 0111100     |

| 1        | 1        | 1        | 0111111     |

# 6. Register Definitions

### 6.1 Write Registers

#### ADDRESS (Hex)

#### 00, 01, 02 Symbol Timing Frequency

The 20 bit straight binary number in this field establishes the symbol timing frequency utilized within the demodulator. Bit 7 of address 00 is the MSB and bit 4 of address 02 is the LSB. If Rs is the symbol rate and f<sub>c</sub> is the clock frequency, the value to be stored in this 20 bit field is the integer portion of  $R_S(2^{20})/f_C$ .

#### 03 Symbol Timing Loop Gain Control

This field establishes the K1 and K2 gain values for the second order loop filter of the symbol tracking loop. Bits 0,1 and 2 determine the straight-through gain, and bits 4,5,6 and 7 determine the integration path gain. The nominal value of this parameter in Hex, is expressed below for different ranges of symbol rate to clock rate ratios:

| Symbol Rate/Clock | <u>Value</u> |

|-------------------|--------------|

| 0.75 - 0.40       | B6           |

| 0.40 - 0.20       | A5           |

| 0.20 - 0.10       | 94           |

| 0.10 - 0.05       | 83           |

| 0.05 - 0.025      | 72           |

| 0.025 - 0.016     | 61           |

04, 05, 06 Ca

# Carrier Frequency

The 20 bit, two's complement number in this field establishes the nominal carrier frequency of the demodulator. Bit 7 of address 04 is the MSB and bit 4 of address 06 is the LSB. The number in this 20 bit field multiplied by the clock frequency divided by  $2^{20}$  is the carrier frequency in Hertz. When the carrier sweep function is active, this value defines the starting frequency.

#### Carrier Loop Filter Control

07, 08

This field establishes the K1 and K2 gain values for the second order loop filter of the carrier tracking loop. Bits 0,1,2 and 3 determine the straight-through gain, and bits 4,5,6 and 7 determine the integration path gain. The nominal value of this parameter in Hex, is expressed below for different ranges of symbol rate to clock rate ratios. Two loop filter configurations are provided at each symbol rate, one for steady state operation(08) and one which is used only for acquisition(07) to permit greater frequency pull-in. Initially the gains are set to acquisition values. When QPSK\_LOCK is achieved, they are automatically switched to steady state values.

Symbol Rate/Clock Steady State Acqu.

| 0.75 - 0.40   | 47 | 77 |

|---------------|----|----|

| 0.40 - 0.20   | 47 | 77 |

| 0.20 - 0.10   | 47 | 77 |

| 0.10 - 0.05   | 46 | 77 |

| 0.05 - 0.025  | 45 | 77 |

| 0.025 - 0.016 | 45 | 77 |

09, 0A Carrier Sweep Step Size

This 16 bit value defines the size of the step of each carrier frequency dwell. Bit 7 of address 09 is the MSB and bit 0 of address 0A is the LSB. The number in this register is divided by 2<sup>16</sup>, and multiplied by the clock frequency to determine the frequency step increment.

#### 0B, 0C Symbols Per Dwell

This 16 bit value defines the time, in symbol periods, for which the demodulator will dwell before making the next frequency step in a sweep. Bit 7 of address 0B is the MSB and bit 0 of address 0C is the LSB.

0D Number

#### Number of Search Frequencies

This 8 bit field determines the number of frequency steps which occur during the frequency sweeping process. Combined with the frequency step size, this determines the frequency span of the carrier sweep.

#### Narrow Band AGC initial value

The six most significant bits of this field establish the initial gain of the AGC. High numbers correspond to low gain associated with low symbol rates. If the narrowband AGC function is enabled, this number is used as a starting point and the closed loop will seek the optimum setting without processor interaction.

0E

#### **Control Parameters**

#### Bit 0. Binary/Two's Complement

When this bit is a zero, the system expects the six bit modulation input samples in two's complement format, otherwise the input should be in offset binary format.

#### Bit 1. Spectrum Invert

When this bit is set to zero, the spectrum of the received signal is inverted. This has the effect of complementing the in-phase channel only.

#### Bit 2. Bias Cancel Enable

When this bit is a one, the internal circuit which cancels DC bias on the I and Q inputs is enabled. When this function is enabled, it is assumed that the input signal is scrambled with no significant DC component on either the I or Q.

#### Bit 3. Symbol Track Enable

When this bit is set to one, the symbol tracking function is enabled. When this bit is zero the symbol tracking frequency is forced to the nominal 20 bit programmed value.

#### Bit 4. Carrier Track Enable

When this bit is set to one, the carrier phase tracking function is enabled. When this bit is zero, the carrier frequency is forced to the 20 bit programmed value.

#### Bit 5. Sweep Hold

When this bit is set to one, the sweeping process is inhibited, and the nominal carrier frequency remains at the last value.

#### Bit 6. Narrowband AGC Mode 1 Enable

When this bit is set to one and the narrowband AGC is in Mode 1, the narrowband AGC self-adjusts to the optimum gain setting. When the bit is set to zero, the most recent value is held without updating.

#### Bit 7. Automatic Detection of Spectrum Inversion

When this bit is set to one, the spectrum inversion is detected automatically.

#### **Reset Functions**

#### Bit 0. Symbol Timing Frequency Accumulator

When this bit is set to zero, the frequency accumulator in the symbol tracking loop is cleared to zero. This bit must be set to one in normal tracking operation to implement a second order tracking loop, otherwise the loop is first order.

#### Bit 1. Carrier Phase Tracking Frequency Accumulator

When this bit is set to zero, the frequency accumulator in the carrier phase tracking loop is cleared to zero. This bit must be set to one in tracking operation to implement a second order loop filter otherwise the loop is first order.

#### Bit 2. Wideband AGC Accumulator

When this bit is set to zero, the accumulator in the wideband AGC is cleared to zero. In normal operation, this bit is set to one. When the wideband AGC is set to Mode 1, this bit has no effect as the integrator must be implemented in the external analog circuits.

#### Bit 3. Narrowband AGC Accumulator

When this bit is set to zero, the accumulator in the narrowband AGC is cleared to the initial value defined in location 0E. In normal operation, this bit is set to one.

#### Bit 4. Unused

#### **Bit 5. Carrier Sweep Function**

When this bit is set to zero, the sweep function is disabled and the carrier frequency is forced to the preset value defined in register locations 04, 05 and 06.

#### Bit 6. Viterbi Reset

When this bit is set to zero, the accumulator for the signal quality is cleared to zero. In normal operation, this bit is set to one.

#### Bit 7. Reed Solomon Error Counter

When this bit is set to zero, the counters for the number of corrected errors and the number of uncorrected code words are cleared to zero.

#### Wideband AGC Control

#### Bit 0. Wideband AGC Mode

When this bit is set to one (Mode 0), the WB AGC output must be filtered with an external integrating analog filter to implement a first order feedback loop. When this bit is zero (Mode 1), a digital integrator within the HDM8513A performs this function and the only external analog function required is a low pass filter to remove the high frequency components of the sigma delta converter output.

#### Bit 1. WB AGC Invert

When this bit is set to zero a high duty factor on the WB AGC output corresponds to too much gain. When the control bit is set to one, high duty factor corresponds to not enough gain.

#### Bit 2. WB AGC Hold

During normal tracking operation, this bit is set to one. When this bit is set to zero and the wideband AGC is in Mode 1, the digital integrator is held to the most recent value and loop updates are inhibited.

#### Bit 3. LNB Hold

When this bit is set to one, the output of LNB-Tone is held on zero.

#### Bit 4. I2C By-pass

When this bit is set to zero, SCL\_I2CO and SDA\_I2CO are disabled. The default is one and Data/clock can be by-passed.

#### Bits [7:5]. WB AGC Gain

This three bit field defines the time constant of the WB AGC in Mode 1. A value of zero corresponds to the shortest time constant and 7 corresponds to the slowest time constant.

12 LNB Tone

# This eight bit value establishes the control for LNB tone generator. If $f_c$ is the desired frequency and $f_c$ is the clock frequency, the value to be stored in this 8 bit field is the integer portion of $f_c(2^{17})/f_c$ . The default value(30H) generates 22KHz tone at 60MHz sampling clock.

#### 13 Sigma Delta

This eight bit input value establishes the control for Sigma Delta converter. This function is independent of other demodulator functions and is provided as control for external analog components.

#### Test Set-up

The eight bit data written to this location defines the data presented on the 16 bit test bus. For configurations where the data is updated once per symbol period, the data changes at the rising edge of SYMBOL\_CLOCK

(in the case that SYMBOL\_CLOCK remains high for consecutive CLOCK

cycles, the test port data will also change accordingly during the high period of SYMBOL\_CLOCK due to the arrival of another symbol).

#### Bits [2:0]. Test port configuration

**00H** Output is tristate.

**01H** Test bits [15:8] provide the I baseband filter output. Test bits [7:0] provide the Q baseband filter output. This information is updated once per symbol period.

**02H** Test bits [15:0] provide the sixteen most significant bits of the demodulator carrier phase test bits. This information is updated once per

symbol period.

**03H** Test bits [15:0] provide the sixteen most significant bits of the demodulator symbol phase test bits. This information is updated once per

symbol period.

**04H** Test bits [15:8] provide the Reed Solomon output data. Test bits [7:0] provide the deinterleaver output data. This information is updated at the Reed Solomon clock rate; when the transport stream output is configured to parallel output mode, DATA\_CLK may be used as an output clock for this data.

**05H** Test bits [15:10] provide the six bit narrowband AGC accumulator value. Test bits [9:6] provide the four bit value of symbol phase. Test bits [5:4] provide the two bit symbol count value. This information is updated once per symbol period.

**06H** Test bits [13:8] provide the six bit I-channel data from the ADC. Test bits [5:0] provides the six bit Q-channel data from the ADC. This information is updated at the fixed rate sample clock.

**07H** In this mode the test pins are used as input pins. The internal ADC is disabled, and the inputs at the test pins are fed directly to the demodulator. Test bits [13:8] are used as I-channel input and test bits [5:0] are used as Q-channel input. This information is updated at the fixed rate sample clock.

#### Bit 3. Transport error Indicator Enable/Disable

Enables/Disables the transport error indicator,1 bit indicator in transport header. When this bit is set to 1 and if transport error is internally detected the transport error indicator bit is set to 1. When zero this functionality is disabled.

#### Bit 4. This bit should be fixed to zero

#### **Bit 5. Regulated Data Clock**

Enables/Disables the data and data clock regulator. When this bit is set to 1, data output and data clock are regulated by FIFO operation. When this bit is set to 0, internal data output and internal data clock are by-passed

#### Bit 6. Serial Valid

When this bit is set to 1, DATA\_STB signal sustains high when valid bit is out (mode 2). When this bit is set to 0, DATA\_STB signal alternates when every valid bit is out (mode 1). Refer to figure 12 and figure 13.

#### Bit 7. Clock Polarity

This bit is used to select the DATA\_CLK polarity either for serial or parallel transport interface. If this bit is set to zero(default value), the transport data and control signals are latched at the positive edge of DATA\_CLK. Otherwise, the signals are latched at the negative edge of DATA\_CLK.

#### Viterbi Lock Threshold

Register 15 to 17 contain control parameters for synchronization in Viterbi decoder. Ordinary users are recommended to use the default value.

Bit[7:4] defines the lock threshold for VB\_NODESYNC. Viterbi decoder decides that the correct code rate has been found. A large number means it takes longer to find the correct code rate in automatic detection mode. It should be greater than 7. The default value is 12.

Bit[3:0] defines the lock fail threshold. Viterbi decoder rejects a code rate and moves on to the next code rate. A small number means Viterbi decoder tries more data before it moves to the next code rate. It should be less than 7. The default value is 2.

#### Viterbi Unlock Threshold

This number defines the threshold to maintain the Viterbi lock state. A large number means it needs more bad data to get out of the viterbi lock state and re-start searching the correct code rate. The default value is 1.

#### Viterbi Byte-Sync control

Once the viterbi lock(VB\_NODESYNC) is achieved, the Viterbi decoder tries to find the byte-sync. This 8-bit register is used to set "unlock-threshold" for the byte-sync. Large number means it needs more baddata to get out of the byte-sync state, i.e. less sensitive to noise. The default value is 1.

#### **Control Parameters for Viterbi and RS Decoders**

#### Bit 0. Parallel or Serial Output

Controls the transport stream output of the 8513A to serial or parallel mode.