# H1A424M167

# Image Signal Processor for Hyundai CMOS Image Sensor

# **Data Sheet**

Version 1.0

# **REVISION HISTORY**

| Revision | Issue Date       | Comments                                          |  |  |  |

|----------|------------------|---------------------------------------------------|--|--|--|

| 0.45     | April 28, 1999   | Draft                                             |  |  |  |

| 0.9      | June 15, 1999    | Added Suspend Pin(No.16)                          |  |  |  |

|          |                  | Added Flicker Free Banding noise filter           |  |  |  |

|          |                  | Added Histogram Equalization function             |  |  |  |

|          |                  | Added STATUS_FLAGS register                       |  |  |  |

|          |                  | Modified Gamma Correction function                |  |  |  |

|          |                  | Modified AWB/AE function                          |  |  |  |

| 0.95     | August 10, 1999  | Added CIF type CIS(HV7121X) support function      |  |  |  |

|          |                  | Added X-flip function                             |  |  |  |

|          |                  | Modified Edge Enhancement filter                  |  |  |  |

|          |                  | JFIF color space conversion equation              |  |  |  |

|          |                  | Modified BASE_ENB register                        |  |  |  |

|          |                  | Modified STATUS_FLAGS register                    |  |  |  |

|          |                  | Modified AWB/AE function                          |  |  |  |

| 1.0      | October 11, 1999 | Added Functional Description/Register Description |  |  |  |

|          |                  | Added Soldering Description                       |  |  |  |

|          |                  | Formal Release                                    |  |  |  |

# TABLE OF CONTENTS

| 1. FEATURES                                                       |

|-------------------------------------------------------------------|

| 2. PIN CONFIGURATION                                              |

| 3. PIN DEFINITION                                                 |

| 4. SYSTEM DIAGRAM                                                 |

| 5. BLOCK DIAGRAM                                                  |

| 6. VIDEO PROCESSING ENGINE BLOCK DIAGRAM                          |

| 7. FUNCTIONAL DESCRIPTION                                         |

| 7.1. Host Interface                                               |

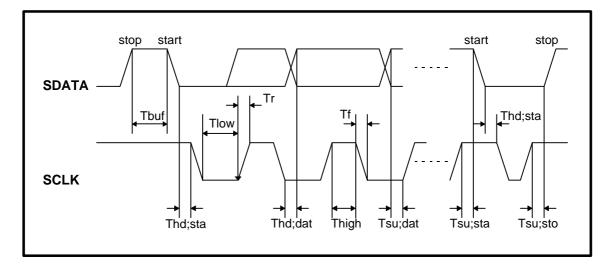

| 7.1.1. Serial Interface                                           |

| 7.1.2. Host Parallel Interface                                    |

| 7.1.3. Serial or Parallel Interface selection15                   |

| 7.2. CLOCK(MCLK, PCLK, VCLK) TIMING DIAGRAM                       |

| 7.3. VIDEO OUTPUT INTERFACE                                       |

| 7.4. RELATIONS BETWEEN INPUT VIDEO TIMING AND OUTPUT VIDEO TIMING |

| 7.4.1. VGA                                                        |

| 7.4.2. CIF                                                        |

| 7.4.3. SIF                                                        |

| 7.4.4. QCIF                                                       |

| 7.4.5. QSIF                                                       |

| 8. REGISTER DESCRIPTION                                           |

| 8.1. Registers Mnemonic Table                                     |

| 8.2. BASE REGISTER MAP                                            |

| 8.2.1. Normal Register[80h~83h]24                                 |

| 8.2.2. Color Matrix Coefficients Value[8Ah ~ 95h]                 |

| 8.3. AUTO REGISTER MAP                                            |

| 8.3.1. Function Enable Register[A0h]                              |

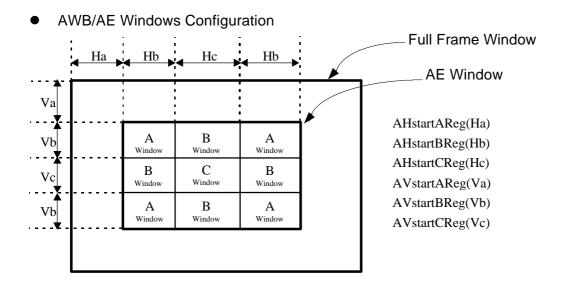

| 8.3.2. AWB/AE Windows Configuration Registers[A1h~A6h]            |

| 8.3.3. Normal Register[A7h~B8h]                                   |

| 8.4. OUT REGISTER MAP                                             |

| 8.4.1. Normal Register[C0h~C2h]                                   |

| 8.4.2. Histogram Equalization Control Register[C3h~C4h]   |

|-----------------------------------------------------------|

| 8.4.3. Gamma Control Register[E0h~F1h]                    |

| 9. ELECTRICAL CHARACTERISTICS                             |

| 9.1. Absolute Maximum Ratings                             |

| 9.2. DC CHARACTERISTICS                                   |

| 9.3. AC CHARACTERISTICS                                   |

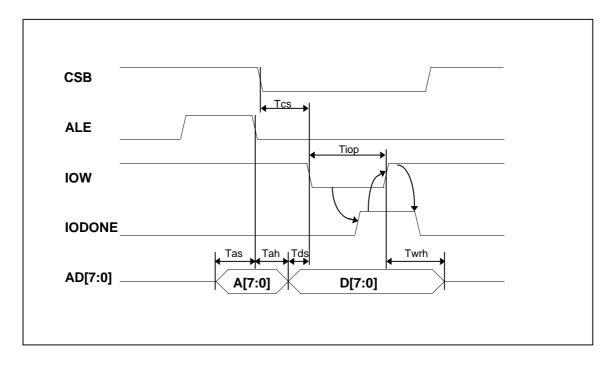

| 9.3.1. Microcontroller Bus Interface timing (Write cycle) |

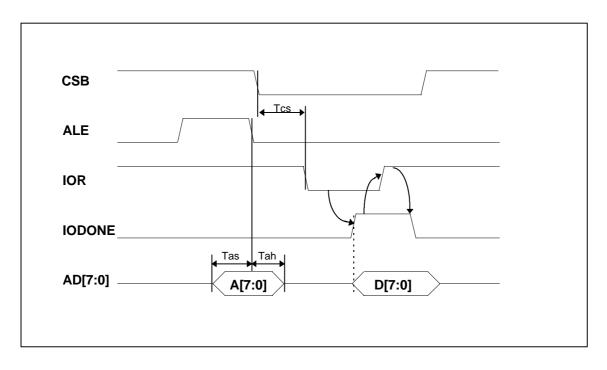

| 9.3.2. Microcontroller Bus Interface timing (Read cycle)  |

| 9.3.3. Serial Interface Control Timing                    |

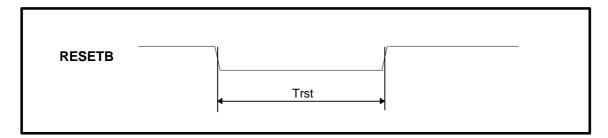

| 9.3.4. RESETB Timing                                      |

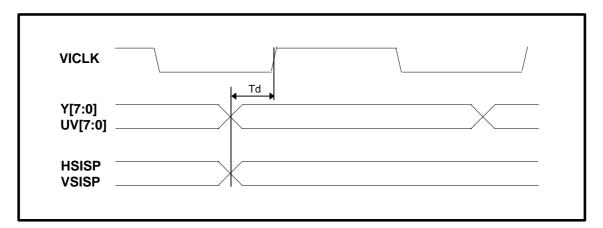

| 9.3.5. Video Output Timing                                |

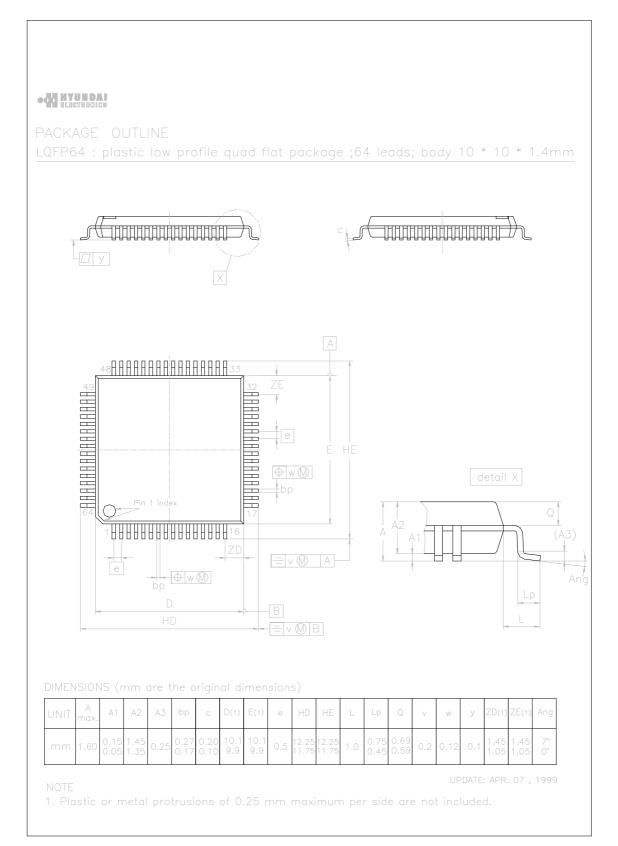

| 10. PACKAGE SPEC                                          |

| 11. SOLDERING                                             |

| 11.1. Solder reflow equipment                             |

| 11.2. Reflow Profiles                                     |

| 11.3. FLUX APPLICATION                                    |

| 11.4. CLEANING                                            |

| 11.5. Drying                                              |

## 1. Features

- Dedicated sensor control and signal processing chip for Hyundai CMOS Image Sensor

- CMOS 3.3V Device (0.5um CMOS TLM Process used)

- Serial-Bus interface or alternative 8-bit MCU parallel interface for register programming

- Serial-Bus interface for HYUNDAI CMOS Image Sensor Chip Control

- 8 bit Bayer format image input

- 3 x 3 Interpolation

- Color Correction matrix

- Gamma Correction

- Automatic Exposure Control

- Automatic White Balance Control

- Programmable AE/AWB windows

- Automatic Reset Level Control

- Edge Enhancement Support

- 2x2, 4x4 Sub-Sampling(CIF, QCIF)

- RGB to YCrCb Color Space Convert

- Histogram Equalization Logic

- 16bit YUV 4:2:2, YUV 4:2:0, 8bit YUV 4:2:2, YUV 4:2:0 video output format

- Flicker Free Banding noise filter

- X Flip Function for mirrored image

- Horizontal and Vertical Sync Information on Separate Pin

- 64 Pin LQFP Package(Standard JEDEC Package)

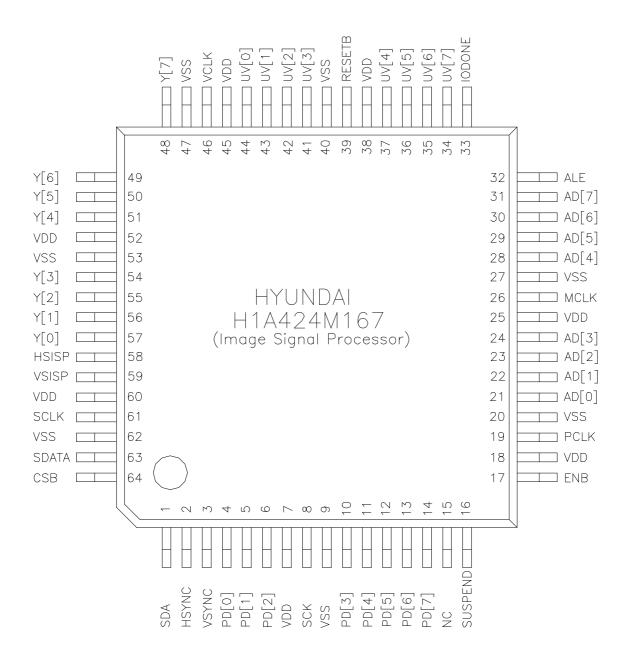

## 2. Pin Configuration

## 3. Pin Definition

| Pin Number | Pin Name | Туре | Description                                |  |  |  |

|------------|----------|------|--------------------------------------------|--|--|--|

| 1          | SDA      | В    | Serial Data for CMOS Image Sensor Control  |  |  |  |

| 2          | HSYNC    | Ι    | Horizontal SYNC Signal from CMOS Image     |  |  |  |

|            |          |      | Sensor                                     |  |  |  |

| 3          | VSYNC    | I    | Vertical SYNC Signal from CMOS Image       |  |  |  |

|            |          |      | Sensor                                     |  |  |  |

| 4          | PD[0]    |      | Raw Pixel Data from Image Sensor Chip      |  |  |  |

| 5          | PD[1]    | Ι    | Raw Pixel Data from Image Sensor Chip      |  |  |  |

| 6          | PD[2]    | Ι    | Raw Pixel Data from Image Sensor Chip      |  |  |  |

| 7          | VDD      | Р    | Power Pin, 3.3V                            |  |  |  |

| 8          | SCK      | 0    | Serial Clock for CMOS Image Sensor Control |  |  |  |

| 9          | VSS      | G    | Ground Pin                                 |  |  |  |

| 10         | PD[3]    | Ι    | Raw Pixel Data from Image Sensor Chip      |  |  |  |

| 11         | PD[4]    | Ι    | Raw Pixel Data from Image Sensor Chip      |  |  |  |

| 12         | PD[5]    | Ι    | Raw Pixel Data from Image Sensor Chip      |  |  |  |

| 13         | PD[6]    | Ι    | Raw Pixel Data from Image Sensor Chip      |  |  |  |

| 14         | PD[7]    | Ι    | Raw Pixel Data from Image Sensor Chip      |  |  |  |

| 15         | NC       | -    | No Connection                              |  |  |  |

| 16         | SUSPEND  | I    | Suspend Mode Support Pin, Active high      |  |  |  |

| 17         | ENB      | 0    | CMOS Image Sensor Enable                   |  |  |  |

| 18         | VDD      | Ρ    | Power Pin, 3.3V                            |  |  |  |

| 19         | PCLK     | 0    | Pixel Clock for CMOS Sensor (MCLK / 3)     |  |  |  |

| 20         | VSS      | G    | Ground Pin                                 |  |  |  |

| 21         | AD[0]    | В    | Address/Data Bus for MCU interface         |  |  |  |

| 22         | AD[1]    | В    | Address/Data Bus for MCU interface         |  |  |  |

| 23         | AD[2]    | В    | Address/Data Bus for MCU interface         |  |  |  |

| 24         | AD[3]    | В    | Address/Data Bus for MCU interface         |  |  |  |

| 25         | VDD      | Р    | Power Pin, 3.3V                            |  |  |  |

| 26         | MCLK     | I    | Master Clock Input                         |  |  |  |

| 27         | VSS      | G    | Ground Pin                                 |  |  |  |

| 28         | AD[4]    | В    | Address/Data Bus for MCU interface         |  |  |  |

| 29         | AD[5]    | В    | Address/Data Bus for MCU interface         |  |  |  |

| 30         | AD[6]    | В    | Address/Data Bus for MCU interface         |  |  |  |

| 31 | AD[7]     | В | Address/Data Bus for MCU interface           |  |

|----|-----------|---|----------------------------------------------|--|

| 32 | ALE       | I | Address Latch Enable                         |  |

| 33 | IODONE    | 0 | CIS/ISP Read/Write Done                      |  |

| 34 | UV[7]     | 0 | Video Data Output for CrCb                   |  |

| 35 | UV[6]     | 0 | Video Data Output for CrCb                   |  |

| 36 | UV[5]     | 0 | Video Data Output for CrCb                   |  |

| 37 | UV[4]     | 0 | Video Data Output for CrCb                   |  |

| 38 | VDD       | Р | Power Pin, 3.3V                              |  |

| 39 | RESETB    | Ι | ISP Reset, Active Low                        |  |

| 40 | VSS       | G | Ground Pin                                   |  |

| 41 | UV[3]     | 0 | Video Data Output for CrCb                   |  |

| 42 | UV[2]     | 0 | Video Data Output for CrCb                   |  |

| 43 | UV[1]     | 0 | Video Data Output for CrCb                   |  |

| 44 | UV[0]     | 0 | Video Data Output for CrCb                   |  |

| 45 | VDD       | Р | Power Pin, 3.3V                              |  |

| 46 | VCLK      | 0 | Pixel Clock for Video Output                 |  |

| 47 | VSS       | G | Ground Pin                                   |  |

| 48 | Y[7]      | 0 | Video Data Output for Y                      |  |

| 49 | Y[6]      | 0 | Video Data Output for Y                      |  |

| 50 | Y[5]      | 0 | Video Data Output for Y                      |  |

| 51 | Y[4]      | 0 | Video Data Output for Y                      |  |

| 52 | VDD       | Р | Power Pin, 3.3V                              |  |

| 53 | VSS       | G | Ground Pin                                   |  |

| 54 | Y[3]      | 0 | Video Data Output for Y                      |  |

| 55 | Y[2]      | 0 | Video Data Output for Y                      |  |

| 56 | Y[1]      | 0 | Video Data Output for Y                      |  |

| 57 | Y[0]      | 0 | Video Data Output for Y                      |  |

| 58 | HSISP     | 0 | Horizontal SYNC Signal for Video Data Output |  |

| 59 | VSISP     | 0 | Vertical SYNC Signal for Video Data Output   |  |

| 60 | VDD       | Р | Power Pin, 3.3V                              |  |

| 61 | SCLK/IOR  | Ι | Serial Bus Clock for programming ISP, Can be |  |

|    |           |   | used as IOR when MCU interface configuration |  |

| 62 | VSS       | G | Ground Pin                                   |  |

| 63 | SDATA/IOW | В | Serial Bus Data for programming ISP, Can be  |  |

|    |           |   | used as IOW when MCU interface configuration |  |

| 64 | CSB/MODE | I                                       | ISP chip select when MCU interface |

|----|----------|-----------------------------------------|------------------------------------|

|    |          |                                         | configuration                      |

|    |          | During reset time, this pin operates as |                                    |

|    |          |                                         | interface mode                     |

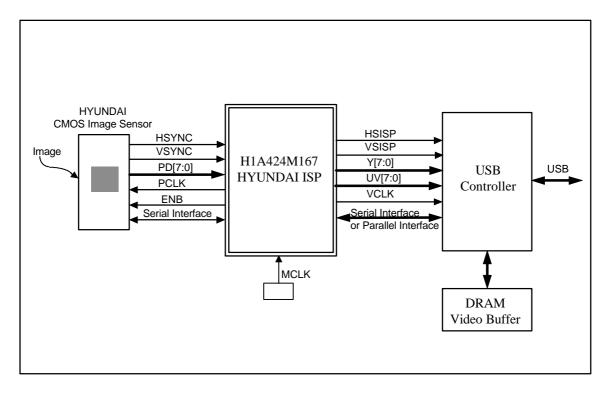

# 4. System Diagram

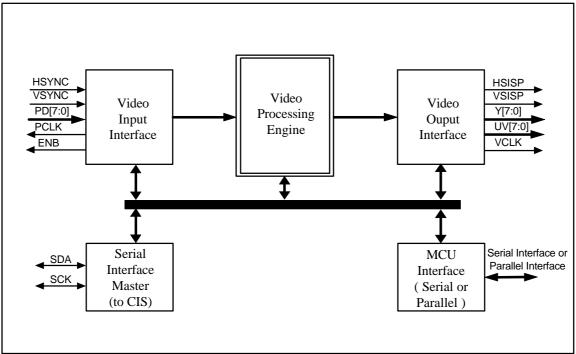

# 5. Block Diagram

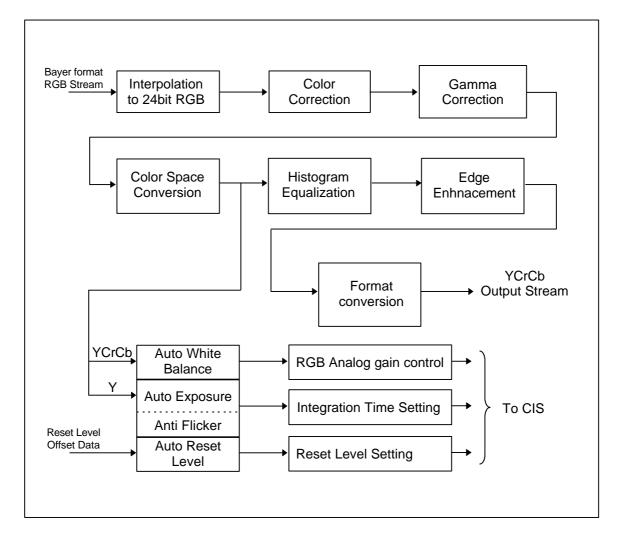

# 6. Video Processing Engine Block Diagram

## 7. Functional Description

## 7.1. Host Interface

Hyundai ISP chip supports two kinds of host interface, serial and 8bit parallel, to program ISP registers or to read ISP registers. And the host interface is also used to write or to read CMOS Image Sensor(CIS) registers through ISP.

#### 7.1.1. Serial Interface

The serial interface of Image Signal Processor[ISP] is implemented by the following pins.

SCLK: Serial Clock SDATA: Serial Data

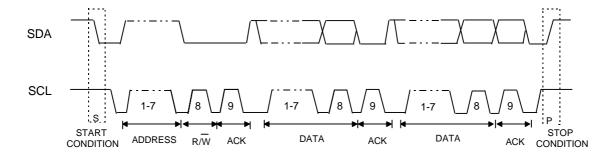

## 7.1.1.1. WRITE OPERATION

Write transaction between the ISP and a host is the similar as the well-known I2C serial interface except that only one byte transfer at each transaction is allowed. The transaction consists of START CONDITION, DEVICE ADDR + R/W[0], SUB ADDR, WRITE DATA, and STOP CONDITION states. The single write access sequence is as follows.

| S                           | DEVICE ADDR | A1                              | SUB ADDR                | A2     | WRITE DATA               | A3 | Р |  |

|-----------------------------|-------------|---------------------------------|-------------------------|--------|--------------------------|----|---|--|

|                             |             |                                 |                         |        |                          |    |   |  |

| [S]                         |             | Opera                           | ation start condit      | ion    |                          |    |   |  |

| [ DE\                       | ICE ADDR ]  | ISP 4                           | <b>0h</b> (010_0000 + 0 | 0), CI | S <b>22h</b> (001_0001 + | 0) |   |  |

|                             |             | ⇔ device address + R/W bit      |                         |        |                          |    |   |  |

| [A1]                        |             | Acknowledge from ISP            |                         |        |                          |    |   |  |

| [ SUE                       | B ADDR ]    | ISP Sub address space 80h ~ FFh |                         |        |                          |    |   |  |

|                             |             | CIS Sub address space 00h ~ 7Fh |                         |        |                          |    |   |  |

| [ A2 ] Acknowledge from ISP |             |                                 |                         |        |                          |    |   |  |

| [WR                         | TE DATA ]   | Register Value from host        |                         |        |                          |    |   |  |

| [ A3 ]                      |             | Acknowledge from ISP            |                         |        |                          |    |   |  |

| [P]                         |             | Opera                           | ation stop condit       | ion    |                          |    |   |  |

## 7.1.1.2. READ OPERATION

Read transaction between the ISP and a host proceeds as the following sequence. START CONDITION ⇒ DEVICE ADDR + R/W[0] ⇒ SUB ADDR ⇒ START CONDITION ⇒ DEVICE ADDR + R/W[1] ⇒ READ DATA ⇒ STOP CONDITION The ISP register access throughput is one byte at each read transaction. But the CMOS Image Sensor register access through the ISP chip needs two sequential read operations to compensate the read access delay from CMOS Image Sensor to ISP. The second read data for the CMOS image sensor register should be recognized as the right value of the accessed register. But when the ISP auto functions are enabled, there will be a variable delay for the right data transfer from the CMOS image sensor to the ISP at the first read access, so the second read access may not get acknowledge from the ISP until the first read access is completely processed in the ISP. To take care of the said situation, a system host should repeat the second read access until it get acknowledge from the ISP or there should be sufficient delay between two accesses. To summarize, the ISP general register read access is always completed by only one read transaction, and the CMOS image sensor register access needs two fully acknowledged read transactions and the last read data is the right value for the accessed register.

The single read access sequence is as follows.

| <b>S</b> 1                      | DADDR 1                             | A1                    | SADDR | A2         | S2     | DADDR 2             | A3   | READ DATA    | A4 | Ρ |

|---------------------------------|-------------------------------------|-----------------------|-------|------------|--------|---------------------|------|--------------|----|---|

| [ 64                            | [S1] Start condition                |                       |       |            |        |                     |      |              |    |   |

| [S1                             | -                                   |                       |       |            |        |                     | (    |              |    |   |

| [ DA                            | DDR 1]                              |                       |       |            |        |                     | (010 | 0_0000 + 0), |    |   |

|                                 |                                     |                       | CIS   | <b>22h</b> | (001   | _0001 + 0)          |      |              |    |   |

|                                 |                                     |                       | ⇒     | devi       | ce a   | ddress + R/         | /W b | it           |    |   |

| [ A1                            | ]                                   |                       | Ack   | nowl       | edge   | e from ISP          |      |              |    |   |

| [SA                             | DDR ]                               |                       | ISP   | Sub        | add    | ress space          | 80h  | ~ FFh        |    |   |

| CIS Sub address space 00h ~ 7Fh |                                     |                       |       |            |        |                     |      |              |    |   |

| [ A2                            | ]                                   |                       | Ack   | nowl       | edge   | e from ISP          |      |              |    |   |

| [ S2                            | ]                                   |                       | Sta   | rt cor     | nditio | n                   |      |              |    |   |

| [ DA                            | DDR 2 ]                             |                       | Dev   | vice A     | ddre   | ess ISP <b>41</b> h | (010 | 0_0000 + 1), |    |   |

|                                 |                                     |                       | CIS   | 23h        | (001   | _0001 + 1)          |      |              |    |   |

|                                 |                                     |                       | ⇔     | devi       | ce a   | ddress + R/         | /W b | it           |    |   |

| [ A3                            | [ A3 ] Acknowledge from ISP         |                       |       |            |        |                     |      |              |    |   |

| [RE                             | READ DATA ] Register Value from ISP |                       |       |            |        |                     |      |              |    |   |

| [ A4                            | ]                                   | Acknowledge from HOST |       |            |        |                     |      |              |    |   |

| [P]                             |                                     |                       | Sto   | p cor      | nditio | 'n                  |      |              |    |   |

|                                 |                                     |                       |       |            |        |                     |      |              |    |   |

\* Note (Importance !)

ISP General Register Read : 1 Read Operation needed.

CIS Register Read : 2 Read Operation needed, valid data at second read operation.

ISP recognize CIS read command at first read.

#### 7.1.1.3. Data Transfer Timing on the serial Interface

#### 7.1.2. Host Parallel Interface

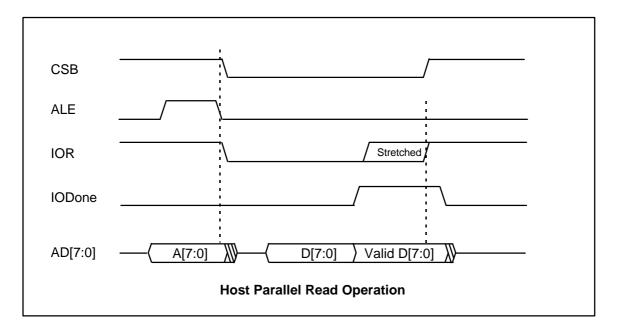

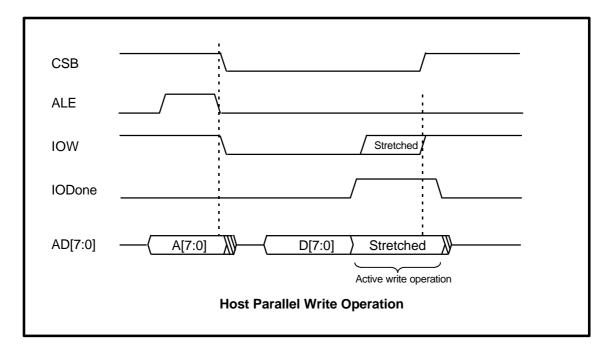

H1A424M167 ISP supports an external 8-bit microcontroller interface to access H1A424M167 internal registers.

Basically, the data transfer operations(8bits) are multiplexed on the address bus.

A Parallel read operation always needs only 1 read cycle different from the serial read operation. But the host must watch 'IODone' signal for a proper read operation. IODone signal indicates the completion of read/write operation. So the host must hold the IOR, CSB signals until IODone signal is active, to read the valid data on AD[7:0] lines. At the final stage, the host ends the bus cycle(CSB, IOR) then IODone signal become inactive.

Similar to parallel read operation, parallel write operation needs only 1 operation cycle. The host must watch 'IODone' signal for a proper write operation. IODone signal indicates the completion of read/write operation. So the host must hold the IOW, CSB, Write Data[7:0] signals until IODone signal become active. When IODone signal become active, ISP accept the write data internally. At the final stage, the host ends the bus cycle(CSB, IOW, Write Data[7:0]) and IODone signal become inactive.

ISP holds IODone active until read/write operation is completed. CIS register read/write operation needs more time than ISP register read/write operation. So IODone active signal for CIS register read/write operation is much longer than that of ISP register read/write operation.

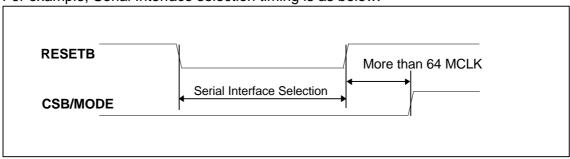

#### 7.1.3. Serial or Parallel Interface selection

The selection between serial interface and parallel interface is made at hardware reset time. If CSB/MODE pin, pin number 64, is pulled down during reset, Serial Interface is configured, and otherwise parallel interface is selected.

For example, Serial Interface selection timing is as below.

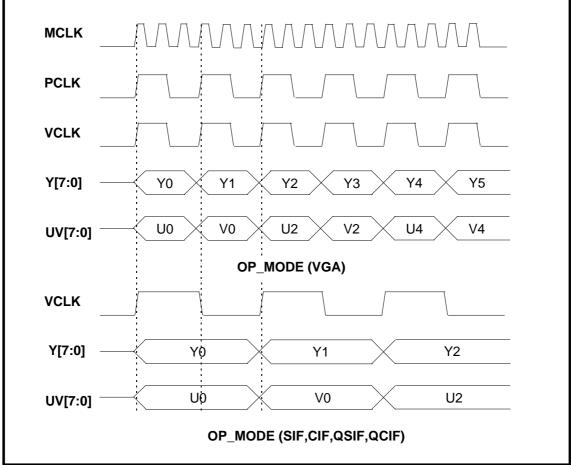

## 7.2. Clock(MCLK, PCLK, VCLK) Timing Diagram

This chart shows the timing diagram in the YCbCr 4:2:2, 16bit video mode.

\* Note : HV7131B(VGA) CMOS Sensor is used for this timing diagram.

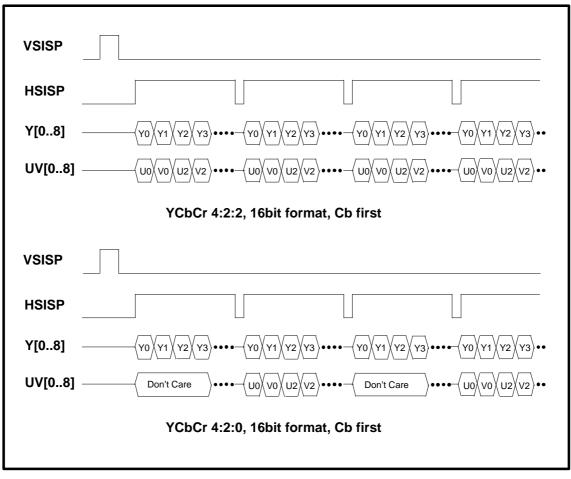

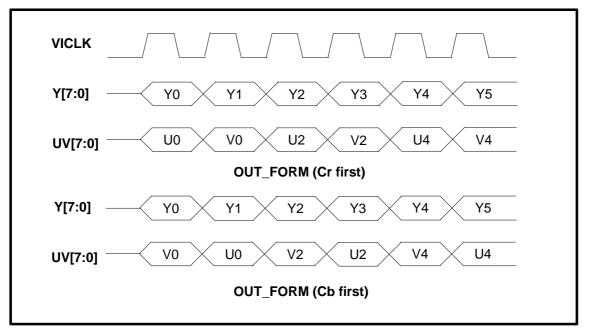

## 7.3. Video Output Interface

The H1A424M167 outputs video data in YUV 4:2:2 format through the 16-bit (Y[7:0] and UV[7:0]) data bus. Video data is changed at the rising edge of the VCLK signal. UV order can be selected by programming OUT\_FORM register. VCLK frequency is same to PCLK frequency in VGA mode when the 16-bit video mode is enabled. VCLK frequency is a half of PCLK frequency in SIF,CIF,QSIF,QCIF modes when the 16-bit video mode is enabled. (See OP\_MODE register description.)

Some video codec needs several HSYNC pulses within active VSYNC. So, The H1A424M167 can modify input VSYNC width by programming HSYNC\_COUNT register for VSISP pulse to contain several HSYNC pulses.

All YUV 16bit ports are active for every HSISP lines in YUV 4:2:2, 16bit video mode.

All YUV 16bit ports are active for even HSISP lines, and only Y 8bit ports are active for

odd HSYNC lines in YUV 4:2:0, 16bit video mode.

The following chart shows the video output data format in the 4:2:2, 4:2:0,16bit video mode.

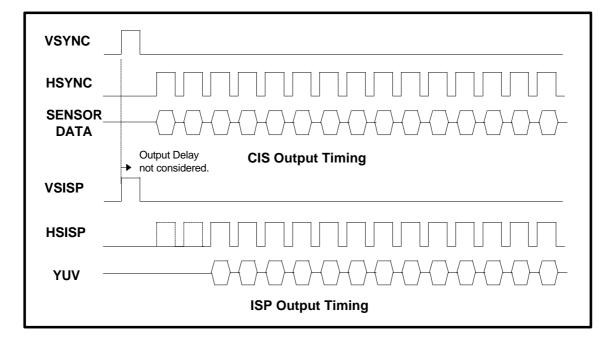

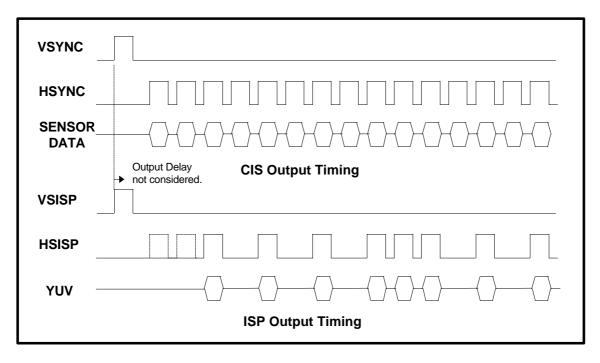

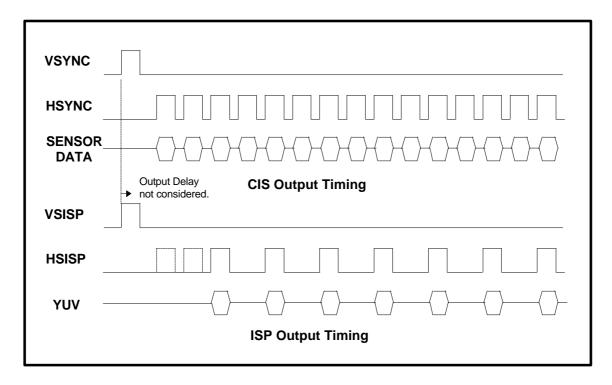

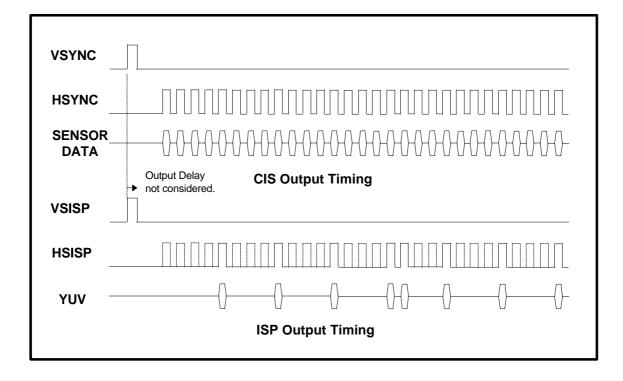

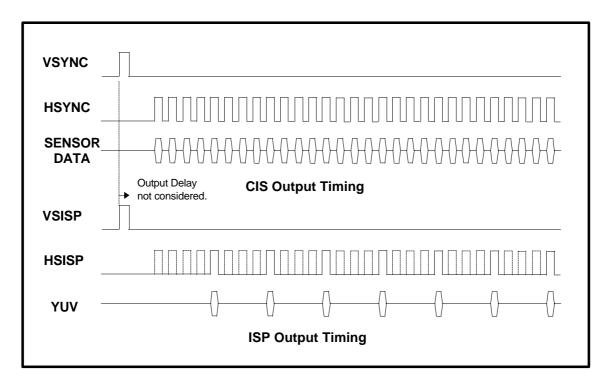

## 7.4. Relations between input video timing and output video timing

The H1A424M167 have five modes of video output timing - VGA(640X480), CIF(352X288), SIF(320X240), QCIF(176X144), QSIF(160X120) - , when the CMOS Image sensor operates in mode of VGA(640X480). The first pixel color of a frame should be "RED" in order to get correct color interpolated image.

The following timing diagrams show relations on each mode.

## 7.4.1. VGA

1999 October 11

## 7.4.3. SIF

## 7.4.4. QCIF

## 7.4.5. QSIF

## 8. Register Description

## 8.1. Registers Mnemonic Table

• BASE Registers Table

| Register Name                      | Mnemonic    | Address | Default |

|------------------------------------|-------------|---------|---------|

| Operating Mode Register            | OP_MODE     | 80h     | 02h     |

| Base Function Enable Register      | BASE_ENB    | 81h     | 01h     |

| Scale Width Control Upper Register | SCALE_UPPER | 82h     | 01h     |

| Scale Width Control Lower Register | SCALE_LOWER | 83h     | 40h     |

| CMA11 Register                     | CMA11       | 8Ah     | 5Ah     |

| CMA12 Register                     | CMA12       | 8Bh     | F3h     |

| CMA13 Register                     | CMA13       | 8Ch     | F3h     |

| CMA21 Register                     | CMA21       | 8Dh     | F3h     |

| CMA22 Register                     | CMA22       | 8Eh     | 5Ah     |

| CMA23 Register                     | CMA23       | 8Fh     | F3h     |

| CMA31 Register                     | CMA31       | 90h     | F3h     |

| CMA32 Register                     | CMA32       | 91h     | F3h     |

| CMA33 Register                     | CMA33       | 92h     | 5Ah     |

| OFSR Register                      | OFSR        | 93h     | 00h     |

| OFSG Register                      | OFSG        | 94h     | 00h     |

| OFSB Register                      | OFSB        | 95h     | 00h     |

#### • AUTO Registers Table

| Register Name                      | Mnemonic     | Address | Default |

|------------------------------------|--------------|---------|---------|

| Auto Function Enable Register      | AUTO_ENB     | A0h     | 00h     |

| AWB/AE Window Horizontal Start     | WIN_H_START  | A1h     | 2Dh     |

| Position Ha                        |              |         |         |

| Horizontal Side Segment Width Hb   | WIN_H_SIDE   | A2h     | 96h     |

| Horizontal Center Segment Width Hc | WIN_H_CENTER | A3h     | FAh     |

| AWB/AE Window Vertical Start       | WIN_V_START  | A4h     | 0Ah     |

| Position Va                        |              |         |         |

| Vertical Side Segment Height Vb    | WIN_V_SIDE   | A5h     | 50h     |

| Vertical Center Segment Height Vc  | WIN_V_CENTER | A6h     | 0Ah     |

| Analog Gain-Top Limit Register     | GAIN_TOP     | A7h     | 3Fh     |

| Analog Gain-Bottom Limit Register  | GAIN_BOTTOM  | A8h     | 14h     |

| AWB Function Control Register         | AWB_CONTROL    | A9h | 76h |

|---------------------------------------|----------------|-----|-----|

| AWB Lock Control Register             | AWB_LOCK       | AAh | B5h |

| AE Function Control Register          | AE_CONTROL     | ABh | 55h |

| AE Lock Control Register              | AE_LOCK        | ACh | B5h |

| Y-target Value Register               | Y_TARGET       | ADh | 80h |

| Reset Level Control Register          | RESET_LEVEL    | AEh | 20h |

| Exposure Time Limitation Value        | EXP_LMT_UPPER  | B0h | 14h |

| Upper Byte                            |                |     |     |

| Exposure Time Limitation Value        | EXP_LMT_MIDDLE | B1h | 58h |

| Middle Byte                           |                |     |     |

| Exposure Time Limitation Value        | EXP_LMT_LOWER  | B2h | 55h |

| Lower Byte                            |                |     |     |

| AWB Cr-target Value Register          | AWB_CR_TARGET  | B3h | 80h |

| AWB Cb-target Value Register          | AWB_CB_TARGET  | B4h | 80h |

| Anti Flicker Unit Time Upper Byte     | AF_UT_UPPER    | B5h | 01h |

| Anti Flicker Unit Time Middle Byte    | AF_UT_MIDDLE   | B6h | B2h |

| Anti Flicker Unit Time Lower Byte     | AF_UT_LOWER    | B7h | 07h |

| Lock Status Flags Register(Read Only) | STATUS_FLAGS   | B8h | XXh |

## • OUT Registers Table

| Register Name                             | Mnemonic     | Address | Default |

|-------------------------------------------|--------------|---------|---------|

| Edge Control Register                     | EDGE_CONTROL | C0h     | 0Dh     |

| Output Format Control Register            | OUT_FORM     | C1h     | 08h     |

| HSYNC Counter Register                    | HSYNC_COUNT  | C2h     | 06h     |

| Manual Histogram Mode Control Register    | HISTO_MODE   | C3h     | 00h     |

| Fixed Contrast Stretching Factor Register | FIXED_FACTOR | C4h     | 00h     |

| Gamma Start 0 Register                    | GMA_START0   | E0h     | 20h     |

| Gamma Start 1 Register                    | GMA_START1   | E1h     | 2Dh     |

| Gamma Start 2 Register                    | GMA_START2   | E2h     | 37h     |

| Gamma Start 3 Register                    | GMA_START3   | E3h     | 47h     |

| Gamma Start 4 Register                    | GMA_START4   | E4h     | 5Fh     |

| Gamma Start 5 Register                    | GMA_START5   | E5h     | 72h     |

| Gamma Start 6 Register                    | GMA_START6   | E6h     | 83h     |

| Gamma Start 7 Register                    | GMA_START7   | E7h     | B6h     |

| Gamma Start 8 Register                    | GMA_START8   | E8h     | DEh     |

| Gamma Slope 0 Register | GMA_SLOPE0 | E9h | 19h |

|------------------------|------------|-----|-----|

| Gamma Slope 1 Register | GMA_SLOPE1 | EAh | 28h |

| Gamma Slope 2 Register | GMA_SLOPE2 | EBh | 1Fh |

| Gamma Slope 3 Register | GMA_SLOPE3 | ECh | 18h |

| Gamma Slope 4 Register | GMA_SLOPE4 | EDh | 13h |

| Gamma Slope 5 Register | GMA_SLOPE5 | EEh | 10h |

| Gamma Slope 6 Register | GMA_SLOPE6 | EFh | 0Ch |

| Gamma Slope 7 Register | GMA_SLOPE7 | F0h | 09h |

| Gamma Slope 8 Register | GMA_SLOPE8 | F1h | 08h |

## 8.2. BASE Register Map

## (MCU Address Space 80h~95h)

## 8.2.1. Normal Register[80h~83h]

| Operati    | ing Mode R                   | egister[8               | 0h]            |                               |                     |              | [02h]       |

|------------|------------------------------|-------------------------|----------------|-------------------------------|---------------------|--------------|-------------|

| [7]        | [6]                          | [5]                     | [4]            |                               | [2]                 | [1]          | [0]         |

| [76]       | Sensor PCL                   | K divider               |                |                               |                     |              | [R/W]       |

|            | 0 : MCLK/3,                  |                         | •              | -                             |                     |              |             |

|            | Normally, us                 |                         | with VGA(F     | IV7131X), C                   | CIF(HV7121          | IX) CIS      |             |

| [ 54 ]     | ISP Clock di                 |                         |                |                               |                     |              | [R/W]       |

| * Note · I | 0 : MCLK/3,<br>Normally, use |                         |                |                               |                     | /6 with CIE( | (H\/7121X)  |

| CIS        | Normany, do                  |                         |                |                               | O, MOLIO            |              | (1107121)() |

| [ 20 ]     | Operating M                  | lode Set                |                |                               |                     |              | [R/W]       |

|            | 1 0 0 : VGA                  | (1 to 1 Mc              | ode)           |                               |                     |              |             |

|            | 011:CIF                      | · ·                     | ,              |                               |                     |              |             |

|            | 010:SIF<br>001:QCIF          | · ·                     | ,              |                               |                     |              |             |

|            | 0001.QCIF                    |                         | • • •          |                               |                     |              |             |

|            | These bits s                 | •                       | . ,            | color interp                  | olation met         | hods is use  | ed,         |

|            | VGA                          |                         | •              | on using 3x                   | •                   |              |             |

|            | CIF/SIF                      |                         | •              | on using 3/4                  | •                   | • •          |             |

|            | QCIF/QSIF<br>and also spo    |                         | •              | on using 3/1                  | •                   | • •          | 4x4 kernei  |

|            | VGA                          | : 1/1                   | scaling        | put image s                   | size scalling       | 3 13 0360.   |             |

|            | CIF/SIF                      |                         | scaling        |                               |                     |              |             |

|            | QCIF/QSIF                    | : 1/16                  | scaling        |                               |                     |              |             |

|            | a) Subsamp                   | •                       |                |                               |                     |              |             |

|            | 3/4 subsam                   |                         | •              | a for four se<br>a output pix | •                   |              |             |

|            |                              |                         |                | vindow mov                    |                     |              | ontal       |

|            |                              |                         | vertical dir   |                               | 00 0) <u>–</u> piik |              | ontai       |

|            | 3/16 subsa                   | mpling: 4x4             | 4 Bayer Da     | ta for sixtee                 | n sensor p          | ixels.       |             |

|            |                              |                         |                | a output pix                  |                     |              |             |

|            |                              |                         | • •            | vindow mov                    | es by 4 pix         | els in horiz | ontal       |

|            | b) In VGA(1                  |                         | l vertical dir |                               | eeds the ir         | nout image   | with 642 X  |

|            | 482 size fo                  |                         | •              |                               |                     | • •          |             |

|            | (Subsample                   |                         |                | -                             |                     |              |             |

|            | 482 for vert                 | -                       |                |                               |                     | -            | -           |

|            | 480 is that                  |                         | •              | •                             |                     | 0 0          |             |

|            | CIF/QCIF/X<br>must be larg   |                         |                |                               | izontai dia         | пк репоа с   | a sensor    |

|            |                              | 501 than 0 <del>4</del> |                | •                             |                     |              |             |

| Base I | Function En                  | able Regi     | ster[81h]                    |                           |               |                | [01h]       |

|--------|------------------------------|---------------|------------------------------|---------------------------|---------------|----------------|-------------|

|        |                              | [5]           | [4]                          | [3]                       | [2]           | [1]            | [0]         |

| [5]    | RB Interpola                 | tion Mode     | Set                          |                           |               |                | [R/W]       |

|        | Two R/B c                    | olor interp   | olation me                   | thods are                 | supported     | when R d       | or B color  |

|        | component                    | is interpola  | ted from ne                  | ighbor pixe               | ls's informa  | tion for full  | RGB color   |

|        | in VGA moo                   |               |                              |                           |               |                |             |

|        | a) average<br>R or B p       |               | t interpolate                | es missing F              | R or B by ju  | st averagin    | g neighbor  |

|        |                              |               | that interpo<br>, (R-G) or ( | lates missir<br>B-G).     | ng R or B fi  | rom utilizin   | g neighbor  |

|        |                              |               | , .                          | f the color i             | nterpolatior  | n methods      | is used     |

|        | 1 : Average,                 |               | 0 : Chro                     |                           |               |                |             |

| [4]    | G Interpola                  | ation Mode    | Set                          |                           |               |                | [R/W]       |

|        | Two G colo                   | •             |                              | • •                       |               |                | •           |

|        | interpolated                 | from neig     | hbor G pix                   | els's inform              | ation for fu  | II RGB col     | lor in VGA  |

|        | mode:                        |               |                              |                           | <b>.</b> .    |                |             |

|        | -                            |               | -                            | s missing (               |               |                | n neignbor  |

|        |                              | •             | -                            | /minimum r<br>tes missing | •             |                | oighbor G   |

|        | values.                      |               |                              | les missing               | G by aver     | aying all i    | leighbol G  |

|        |                              | specifies v   | vhich one o                  | f G color in              | terpolation   | methods is     | used        |

|        | 1 : Median,                  |               | 0 : Avera                    |                           |               |                |             |

| [3]    | X-Flip Funct                 | ion Enable    |                              | 0                         |               |                | [R/W]       |

|        | The functior                 | n enables th  | ne horizonta                 | al flip(left-rig          | ght changed   | l) of input ir | mage data.  |

|        | In oder to                   | •             |                              |                           | •             |                |             |

|        | interpolatior                |               | -                            | -                         | -             |                |             |

|        | that height s                |               |                              |                           | o account fo  | or Bayer in    | put data to |

|        | be flipped b                 |               | •                            |                           |               |                | the input   |

|        | For other fl<br>image size i | ••••••        |                              | •                         | ·             |                | •           |

|        | 1: X-Flip ON                 |               | 0 : X-Fli                    | • •                       | mage data     |                | 02.         |

| [2]    | Gamma Fur                    | -             | •                            |                           |               |                | [R/W]       |

|        | Piecewise li                 |               |                              | ation metho               | od is implen  | nented. Pre    |             |

|        | linear segm                  | ents are su   | pported an                   | d user-prog               | rammable.     |                |             |

|        | For more de                  | etails, refer | to gamma                     | register des              | scription see | ction.         |             |

|        | 1 : Gamma (                  | -             | 0 : Gam                      | ma OFF                    |               |                |             |

| [1]    | Color Matrix                 |               |                              |                           |               |                | [R/W]       |

|        | This functio                 |               |                              |                           |               |                | -           |

|        | circuits to ge               | -             | -                            | -                         |               |                |             |

|        | programmal supported.        |               | 27/04 10 12                  | 1/04. UIISEI              | compensa      | uon registe    | is are also |

|        | 1 : Color Ma                 | trix ON.      | 0 : Coloi                    | · Matrix OFI              | =             |                |             |

|        |                              |               | 0.000                        |                           |               |                |             |

[0] Color Interpolation Function Enable [R/W] This bit specifies whether color interpolation is processed or not. Color interpolation methods are defined by OP\_MODE register. Most importantly, in order to have a correct color interpolation, the first input pixel data type should be R pixel data.

1 : Interpolation ON, 0 : Interpolation OFF

\* Note : The start pixel of every input frame must be R for proper interpolation.

| Scale | Width Contr | ol Upper   | Register[8 | 32h] |  | [01h] |

|-------|-------------|------------|------------|------|--|-------|

|       |             |            |            |      |  | [0]   |

| [0]   | Scale Width | Control Up | per Value  |      |  | [R/W] |

| Scale Wi | idth Contr | ol Lower   | Register[8 | 33h] |     |     | [40h] |

|----------|------------|------------|------------|------|-----|-----|-------|

| [7]      | [6]        | [5]        | [4]        | [3]  | [2] | [1] | [0]   |

| [70] S   | cale Width | Control Lo | wer Value  |      |     |     | [R/W] |

\* Note : The scale width control register is only related to operating mode CIF/SIF/QCIF/QSIF, and controls how many column data in each line are output. Default value is 140h(340d), the half of standard VGA width size.

#### 8.2.2. Color Matrix Coefficients Value[8Ah ~ 95h]

These registers are used in color matrix function in order to compensates color spread effect of color filters and sensing circuits to get the optimal pure color reproduction. Color matrix coefficients are programmable from -127/64 to 127/64. Programming register value for intended color matrix coefficients should be resolved by the following sequence.

For positive values,

CMAxx = Integer(RealCoefficientValue x 64);

For negative values,

CMAxx = TwosComplement(Integer(RealCoefficientValue x 64)); RealCoefficientValue values from -127/64 to 127/64 can be programmed. Offset compensation registers are also supported. • Fundamental color matrix equation

| CMA11 | CMA12<br>CMA22 | CMA13 | $\begin{bmatrix} R \end{bmatrix}$ |   | OFSR | ] |

|-------|----------------|-------|-----------------------------------|---|------|---|

| CMA21 | CMA22          | CMA23 | G                                 | + | OFSG |   |

| CMA31 | CMA32          | CMA33 | B                                 |   | OFSB |   |

| [70]       CMA11 Value X 64       2's Complement       [R/W         CMA12 Register[8Bh]       [F3]         [7]       [6]       [5]       [4]       [3]       [2]       [1]       [C         [70]       CMA12 Value X 64       2's Complement       [R/W       [R/W         CMA13 Register[8Ch]       [F3]       [2]       [1]       [C         [7]       [6]       [5]       [4]       [3]       [2]       [1]       [C         [7]                                                           | 6 <b>h]</b><br>[0] |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| CMA12 Register[8Bh]       [F3]         [7]       [6]       [5]       [4]       [3]       [2]       [1]       [0]         [70]       CMA12 Value X 64       2's Complement       [R/W         CMA13 Register[8Ch]       [F3]         [7]       [6]       [5]       [4]       [3]       [2]       [1]       [0]         [7]       [6]       [5]       [4]       [3]       [2]       [1]       [0]         [7]       [6]       [5]       [4]       [3]       [2]       [1]       [0]         [7]       [6]       [5]       [4]       [3]       [2]       [1]       [0]         [7]       [6]       [5]       [4]       [3]       [2]       [1]       [0]         [7]       [6]       [5]       [4]       [3]       [2]       [1]       [0]         [7]       [6]       [5]       [4]       [3]       [2]       [1]       [0]         [7]       [6]       [5]       [4]       [3]       [2]       [1]       [0]         [7]       [6]       [5]       [4]       [3]       [2]       [1]       [0]         [7]       [6]                                                                  | 6 <b>h]</b><br>[0] |

| [7]       [6]       [5]       [4]       [3]       [2]       [1]       [0]         [70]       CMA12 Value X 64       2's Complement       [R/W <b>CMA13 Register[8Ch]</b> [7]       [6]       [5]       [4]       [3]       [2]       [1]       [0]         [7]       [6]       [5]       [4]       [3]       [2]       [1]       [0]         [7]       [6]       [5]       [4]       [3]       [2]       [1]       [0]         [7]       [6]       [5]       [4]       [3]       [2]       [1]       [0]         [7].0]       CMA13 Value X 64       2's Complement       [R/W       [R/W       [R/W       [R/W         [7].0]       CMA13 Value X 64       2's Complement       [R/W       [R | 0]                 |

| [70]       CMA12 Value X 64       2's Complement       [R/W         CMA13 Register[8Ch]       [F3]         [7]       [6]       [5]       [4]       [3]       [2]       [1]       [0]         [70]       CMA13 Value X 64       2's Complement       [R/W         CMA21 Register[8Dh]       [F3]       [F3]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                    |

| [F3I         [F3I         [7]       [6]       [5]       [4]       [3]       [2]       [1]       [0]         [70]       CMA13 Value X 64       2's Complement       [R/W         CMA21 Register[8Dh]       [F3I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ۸/۱                |

| [7]       [6]       [5]       [4]       [3]       [2]       [1]       [0]         [70]       CMA13 Value X 64       2's Complement       [R/W         CMA21 Register[8Dh]       [F3]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | , v ]              |

| [70]       CMA13 Value X 64       2's Complement       [R/W         CMA21 Register[8Dh]       [F3]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | h]                 |

| CMA21 Register[8Dh] [F3I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0]                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <i>N</i> ]         |

| [7] [6] [5] [4] [3] [2] [1] [0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | h]                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0]                 |

| [70] CMA21 Value X 64 2's Complement [R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <i>N</i> ]         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                    |

| CMA22 Register[8Eh] [5A]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <b>h</b> ]         |

| [7] [6] [5] [4] [3] [2] [1] [0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0]                 |

| [70] CMA22 Value X 64 2's Complement [R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <i>N</i> ]         |

| CMA23 Register[8Fh] [F3I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | h]                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0]                 |

| [7] [6] [5] [4] [3] [2] [1] [0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <i>N</i> ]         |

| [7]       [6]       [5]       [4]       [3]       [2]       [1]       [0]         [70]       CMA23 Value X 64       2's Complement       [R/W]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | h]                 |

| [70] CMA23 Value X 64       2's Complement       [R/W         CMA31 Register[90h]       [F3H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -                  |

| [70] CMA23 Value X 64       2's Complement       [R/W         CMA31 Register[90h]       [F3H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0]                 |

| [70] CMA23 Value X 64       2's Complement       [R/W         CMA31 Register[90h]         [7]       [6]       [5]       [4]       [3]       [2]       [1]       [0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <br>[0]<br>[//]    |

| [70] CMA23 Value X 64       2's Complement       [R/W         CMA31 Register[90h]       [F3]         [7]       [6]       [5]       [4]       [3]       [2]       [1]       [C         [70]       CMA31 Value X 64       2's Complement       [R/W         CMA32 Register[91h]       [F3]       [F3]       [F3]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <br>[0]<br>[//]    |

| CMA33 F                                                       | Register[9                        | 2h]                            | -                   |     |     |     | [5Ah]                |  |

|---------------------------------------------------------------|-----------------------------------|--------------------------------|---------------------|-----|-----|-----|----------------------|--|

| [7]                                                           | [6]                               | [5]                            | [4]                 | [3] | [2] | [1] | [0]                  |  |

| [70] CMA33 Value X 64 2's Complement                          |                                   |                                |                     |     |     |     |                      |  |

| OFSR Register[93h]                                            |                                   |                                |                     |     |     |     |                      |  |

| [7]                                                           | [6]                               | [5]                            | [4]                 | [3] | [2] | [1] | [ <b>00h]</b><br>[0] |  |

| [70] Color Matrix Red Offset Value -127 ~ +128 2's complement |                                   |                                |                     |     |     |     |                      |  |

| [1.0] C                                                       |                                   |                                |                     |     |     |     |                      |  |

| [70] C                                                        |                                   |                                |                     |     |     |     |                      |  |

|                                                               | egister[94                        |                                |                     |     |     |     | [00h]                |  |

|                                                               |                                   |                                | [4]                 | [3] | [2] | [1] | <b>[00h]</b><br>[0]  |  |

| OFSG R                                                        | egister[94<br>[6]                 | <b>h]</b><br>[5]               | [4]<br>set Value -1 |     |     |     |                      |  |

| OFSG R                                                        | egister[94<br>[6]                 | <b>h]</b><br>[5]               |                     |     |     |     | [0]                  |  |

| OFSG R<br>[7]<br>[70] C                                       | egister[94<br>[6]                 | <b>h]</b><br>[5]<br>Green Offs |                     |     |     |     | [0]                  |  |

| OFSG R<br>[7]<br>[70] C                                       | egister[94<br>[6]<br>Color Matrix | <b>h]</b><br>[5]<br>Green Offs |                     |     |     |     | [0]<br>[R/W]         |  |

\* Note : The values of CMA11~CMA33 are allowed between -2 and 2

## 8.3. AUTO Register Map

## ( MCU Address Space A0h ~ B4h )

## 8.3.1. Function Enable Register[A0h]

| Auto F | unction Ena                | able Regis  | ster[A0h]     |              |               |              | [00h]      |

|--------|----------------------------|-------------|---------------|--------------|---------------|--------------|------------|

| [7]    | [6]                        | [5]         | [4]           | [3]          |               | [1]          | [0]        |

| [7]    | Image Sense                | or ENB Co   | ntrol         |              |               |              | [R/W]      |

|        | 1 : ENB ena                | ble,        | 0 : ENB       | disable      |               |              |            |

| [6]    | AE Mode Co                 | ontrol 1    |               |              |               |              | [R/W]      |

|        | Used with A                | E mode co   | ntrol 0 at bi | t 0          |               |              |            |

| [5]    | Auto Histogr               | am Equaliz  | zation Enab   | le           |               |              | [R/W]      |

|        | Automaticall               | y enables   | the histo     | gram equ     | alization fu  | unction wh   | en larger  |

|        | exposure tin               | ne than exp | osure time    | limit value  | defined at    | the registe  | rs B0 ~ B2 |

|        | is needed to               | achieve     | r target bri  | ghtness. Th  | nis bit is no | ot valid whe | en manual  |

|        | histogram eo               | qualization | defined at I  | register C3  | n is enabled  | d.           |            |

|        | 1 : Auto Hist              | ogram Equ   | alization O   | N            |               |              |            |

|        | 0 : Auto Hist              | •           |               | FF           |               |              |            |

| [4]    | Automatic R                | eset Level  | Control       |              |               |              | [R/W]      |

|        | Automaticall               | y controls  | the Rese      | et Level o   | f CMOS        | Image Sei    | nsor. Low  |

|        | Reference (                | -           |               | -            |               | -            |            |

|        | CMOS Imag                  | •           | •             |              |               |              |            |

|        | current sam                |             |               |              |               |              | •          |

|        | these registe              |             | •             |              |               |              |            |

|        | Level Contro               | •           |               |              | ,             |              |            |