## Multi GF9102A Decimating / Interpolating Digital Filter

DATA SHEET

#### **FEATURES**

- improved performance over TMC2242 in applications not requiring 1:1 low pass filtering

- low power (60mA typical at f = 20MHz)

- 40 MHz maximum clock rate

- single device exceeds CCIR 601 lowpass filter requirements

- · true unity gain (0.0 dB) at DC

- reduced output ringing with constant input in interpolation mode

- · built-in TRS code protection

- 12 bit inputs and 16 bit outputs in 2's complement signed or unsigned formats

- user-selectable 8 to 16 bit output rounding

- can also be operated as a 9 or 21 tap chroma bandpass filter under user control

- single +5 V power supply

- · three state outputs

#### **APPLICATIONS**

- CCIR 601-compliant oversampling video A/D and D/A conversion

- 2:1 interpolation and decimation

- 4:2:2 to 4:4:4 format conversion

- Chroma bandpass filtering

#### **ORDERING INFORMATION**

| Part Number | Package Type     | Temperature Range |

|-------------|------------------|-------------------|

| GF9102ACPM  | 44 Pin PLCC      | 0° to 70° C       |

| GF9102ACTM  | 44 Pin PLCC Tape | 0° to 70° C       |

#### **DEVICE DESCRIPTION**

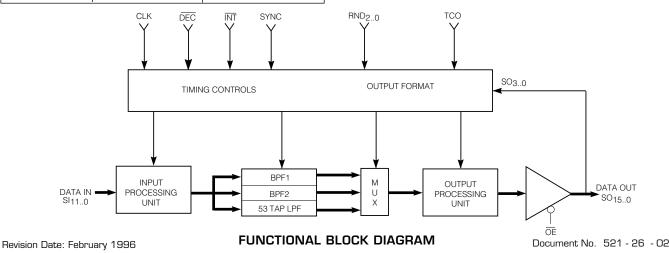

The GF9102A is a linear phase FIR digital filter that is usable in a variety of video signal processing applications. The device contains three separate fixed coefficient filters and can be operated in three basic modes: 53 tap low pass filter, 9 tap chroma bandpass filter or 21 tap chroma bandpass filter.

In the 53 tap low pass filter mode, the GF9102A can replace the TMC2242 in all applications, except those requiring 1:1 low pass filtering, for improved performance and full CCIR 601 compatibility. Specific improvements include true unity gain at DC, 12.4 dB attenuation at fs/4 with a single device, reduced output ringing with constant input in interpolate mode, support for signed and unsigned data formats, rounding to 10 and 8 bit CCIR 601 data formats, masking of serial digital TRS codes in the data stream, and elimination of the non-saturated-type overflow condition. The device can be operated in both TMC2242 compatible modes and in GF9102A enhanced modes.

When used as a decimating post-filter with a double speed oversampling analog-digital converter, the device greatly reduces the cost and complexity of the associated analog anti-aliasing pre-filter. In a similar fashion, when used as an interpolating pre-filter with a double speed oversampling digital-analog converter, the GF9102A simplifies the analog reconstruction post-filter. The GF9102A also exceeds the requirements for conversion between 4:2:2 and 4:4:4 signal formats.

For chroma filtering applications, the GF9102A can be operated as a 9 or 21 tap bandpass filter by selecting the appropriate operating mode.

The GF9102A is packaged in a 44 pin PLCC and is pin compatible with the TMC2242. The device operates with a single +5 V supply.

#### PIN DESCRIPTION

| SYMBOL            | PIN NO.                                                           | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------|-------------------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK               | 42                                                                | I    | System Clock. TTL input. All timing specifications are referenced to the rising edge of clock.                                                                                                                                                                                                                                                                                              |

| SYNC              | 43                                                                | I    | Data Synchronization. TTL input with internal pull-up. This input is used to synchronize the incoming data with the GF9102A by holding SYNC high on clock N and low on clock N+1 when the first data word is presented to the input SI <sub>110</sub> . SYNC may be held low until resynchronization is desired, or it may be clocked at half the clock rate.                               |

| SI <sub>110</sub> | 40, 37, 36, 35,<br>34, 33, 32, 31,<br>30, 27, 26, 25              | 1    | Input Data Port. TTL inputs with internal pull-downs. Data is presented to this registered 12-bit data input port. This port can be programmed as two's complement signed or unsigned binary format. See the following section on input data format. Data is latched internally on every clock in decimate mode, and on every other clock in interpolate mode. SI <sub>11</sub> is the MSB. |

| TCO               | 2                                                                 | I    | Two's Complement Output Format Control. TTL input with internal pull-down. When TCO is high, output data is presented in two's complement format. When TCO is low, the output is inverted offset binary, obtained by inverting bits SO <sub>14</sub> through SO <sub>0</sub> , leaving SO <sub>15</sub> unchanged.                                                                          |

| ĪNT               | 44                                                                | I    | Interpolate. Active low TTL input with internal pull-up. When the interpolate control is low, data is input at full clock speed and the chip inserts zeros between samples, padding the input to match the output rate. The GF9102A then interpolates between these alternate input data points to achieve full output data rate.                                                           |

| DEC               | 1                                                                 | I    | Decimate. Active low TTL input with internal pull-down. When the decimate control is low, the output register is driven at half system clock speed, decimating the output data stream. When DEC and INT are low, the GF9102A will be programmed as a 21 tap or 9 tap bandpass filter depending on the state of the SYNC input. See Operation Mode Control below for more detail.            |

| RND <sub>20</sub> | 22, 23, 24                                                        | I    | Output Rounding Control. TTL inputs with internal pull-down. These pins set the position of the effective least significant bit of the output port by adding a rounding bit to the next lower internal bit and zeroing all outputs below the rounding bit. Additional rounding functions are added with the SO <sub>1</sub> control input. See Table 6.                                     |

| SO <sub>150</sub> | 4, 5, 6, 7,<br>8, 9, 10, 11,<br>14, 15, 16, 17,<br>18, 19, 20, 21 | 0    | Output Data Port. TTL outputs ( $SO_{30}$ are bi-directional pins with an internal pull-down). The filtered result is available at this registered 16-bit output port, half LSB rounded as determined by the rounding control word RND <sub>20</sub> . $SO_{15}$ is the MSB. The $SO_{30}$ control inputs enable additional formatting and rounding features as described below.            |

| SO <sub>30</sub>  | 18, 19, 20, 21                                                    | I/O  | Output Data Port. TTL bi-directional pins with internal pull-down. The SO <sub>0</sub> control input enables the unsigned input and output format. The SO <sub>1</sub> control input enables 8-bit rounding or CCIR 601 8-bit and 10-bit modes of operation. SO <sub>32</sub> are reserved for future functions.                                                                            |

| ŌĒ                | 3                                                                 | I    | Output Enable. Active low TTL input with internal pull-up. When this asynchronous input is high, the output data port is in the high impedance state.                                                                                                                                                                                                                                       |

| VDD               | 13, 29, 38                                                        |      | $+5 \text{ V} \pm 5\%$ power supply.                                                                                                                                                                                                                                                                                                                                                        |

| GND               | 12, 28, 39, 41                                                    |      | Ground                                                                                                                                                                                                                                                                                                                                                                                      |

521 - 26 - 02

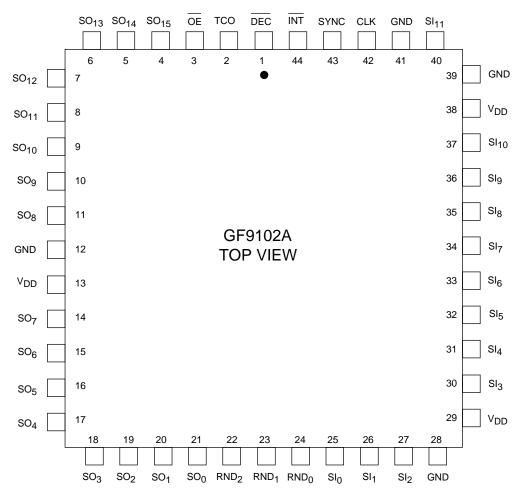

Fig. 1 GF9102A Pin Connections

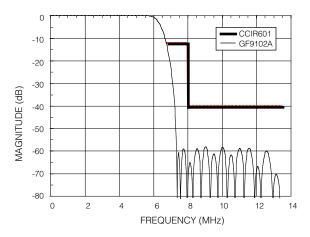

#### LOWPASS FILTER CHARACTERISTICS at SAMPLING FREQUENCY OF 27MHz

| PARAMETER                     | VALUE       |

|-------------------------------|-------------|

| Filter Order                  | 53          |

| Pass Band Ripple              | < ± 0.02 dB |

| Pass Band Edge                | 5.75 MHz    |

| DC Gain                       | 0.00 dB     |

| 6.75 MHz (fs/4) Attenuation   | 12.4 dB     |

| Minimum Stop Band Attenuation | >58 dB      |

| Stop Band Edge                | 7.4 MHz     |

Fig. 2 Frequency Response of the Decimation/Interpolation Filter (Sampling at 27 MHz)

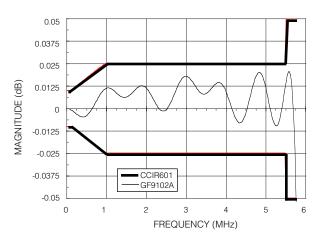

Fig. 3 Frequency Response of the Decimation/Interpolation Filter Passband (Sampling at 27 MHz)

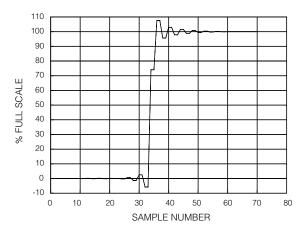

Fig. 4 Step Response of Decimation Filter

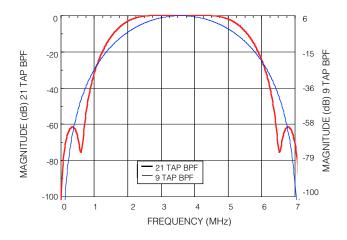

Fig. 5 Frequency Response of the Bandpass Filter (Sampling at 14.31818 MHz)

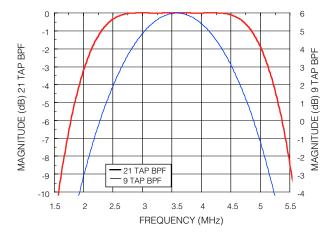

Fig. 6 Frequency Response of the Bandpass Filter Transition Band (Sampling at 14.31818 MHz)

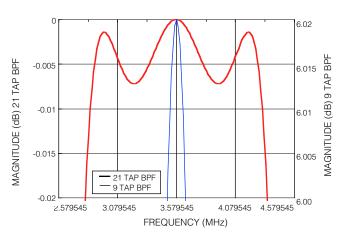

Fig. 7 Frequency Response of the Bandpass Filter Passband (Sampling at 14.31818 MHz)

521 - 26 - 02 4

#### Table 1: Input Data Format and Bit Weighting

Two's complement signed binary, data range:  $-1 \le SI < 1$

|   | SI <sub>11</sub> | SI <sub>10</sub> | SI <sub>9</sub> | SI <sub>8</sub> | SI <sub>7</sub> | SI <sub>6</sub> | SI <sub>5</sub> | SI <sub>4</sub> | SI <sub>3</sub> | SI <sub>2</sub> | SI <sub>1</sub> | SI <sub>0</sub>  |

|---|------------------|------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|------------------|

| I | -2 <sup>0</sup>  | 2-1              | 2-2             | 2-3             | 2 <sup>-4</sup> | 2 <sup>-5</sup> | 2 <sup>-6</sup> | 2 <sup>-7</sup> | 2 <sup>-8</sup> | 2-9             | 2-10            | 2 <sup>-11</sup> |

Unsigned binary, data range:  $0 \le SI < 256$

|   | SI <sub>11</sub> | SI <sub>10</sub> | SI <sub>9</sub> | SI <sub>8</sub> | SI <sub>7</sub> | SI <sub>6</sub> | SI <sub>5</sub> | SI <sub>4</sub> | SI <sub>3</sub> | SI <sub>2</sub> | SI <sub>1</sub> | SI <sub>0</sub> |

|---|------------------|------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| ı | 2 <sup>7</sup>   | 2 <sup>6</sup>   | 2 <sup>5</sup>  | 2 <sup>4</sup>  | 2 <sup>3</sup>  | 2 <sup>2</sup>  | 2 <sup>1</sup>  | 20              | 2-1             | 2-2             | 2-3             | 2 <sup>-4</sup> |

#### Table 2: Output Data Format and Bit Weighting

Two's complement signed binary, data range:  $-1 \le SO < 1$

| ſ | SO <sub>15</sub> | SO <sub>14</sub> | SO <sub>13</sub> | SO <sub>12</sub> | SO <sub>11</sub> | SO <sub>10</sub> | SO <sub>9</sub> | SO <sub>8</sub> | SO <sub>7</sub> | SO <sub>6</sub> | SO <sub>5</sub> | SO <sub>4</sub> | SO <sub>3</sub> | SO <sub>2</sub> | SO <sub>1</sub> | SO <sub>0</sub>  |

|---|------------------|------------------|------------------|------------------|------------------|------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|------------------|

| ľ | -20              | 2-1              | 2-2              | 2-3              | 2-4              | 2-5              | 2-6             | 2-7             | 2-8             | 2 <sup>-9</sup> | 2-10            | 2-11            | 2-12            | 2-13            | 2-14            | 2 <sup>-15</sup> |

Unsigned binary, data range: 0 ≤ SO < 256

| SO <sub>15</sub> | SO <sub>14</sub> | SO <sub>13</sub> | SO <sub>12</sub> | SO <sub>11</sub> | SO <sub>10</sub> | SO <sub>9</sub> | SO <sub>8</sub> | SO <sub>7</sub> | SO <sub>6</sub> | SO <sub>5</sub> | SO <sub>4</sub> | SO <sub>3</sub> | SO <sub>2</sub> | SO <sub>1</sub> | SO <sub>0</sub> |

|------------------|------------------|------------------|------------------|------------------|------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| 2 <sup>7</sup>   | 26               | 25               | 2 <sup>4</sup>   | 23               | 22               | 21              | 20              | 2-1             | 2-2             | 2-3             | 2-4             | 2-5             | 2-6             | 2-7             | 2-8             |

#### Table 3: Operation Mode Control

| DEC | ĪNT | Sync | Mode          | Description                            | Device Latency  | Notes |

|-----|-----|------|---------------|----------------------------------------|-----------------|-------|

| 0   | 0   | 0    | Bandpass1     | 21 Tap Bandpass                        | 18 Clock Cycles | 2     |

| 0   | 0   | 1    | Bandpass2     | 9 Tap Bandpass Gain=2                  | 18 Clock Cycles | 2     |

| 0   | 1   | Sync | Decimating    | Gain=1                                 | 33 Clock Cycles | 1     |

| 1   | 0   | Sync | Interpolating | Gain=0.5                               | 33 Clock Cycles | 1     |

| 1   | 0   | Sync | Interpolating | Gain=1 for unsigned input <sup>3</sup> | 33 Clock Cycles | 2     |

| 1   | 1   | Sync | Pass through  | Top 12 bit pass through                | 33 Clock Cycles | 2     |

- Notes: 1. This operating mode is compatible with TMC2242.

- 2. This is an enhanced operating mode of the GF9102A.

- 3. This mode is invoked using the  $SO_0$  pin. See I/O Format control below.

#### Table 4: I/O Format Control

| RND <sub>20</sub> | so <sub>0</sub> <sup>3</sup> | тсо | Input <sup>5</sup>    | Output <sup>5</sup> | Notes                      |

|-------------------|------------------------------|-----|-----------------------|---------------------|----------------------------|

| RND = 000         | Output                       | 0   | Signed                | I_Unsigned          | 1                          |

|                   |                              | 1   | Signed                | Signed              |                            |

| RND ≠ 000         | 0                            | 0   | Signed                | I_Unsigned          | 1                          |

|                   |                              | 1   | Signed                | Signed              |                            |

| RND ≠ 000         | 1                            | 0   | Unsigned <sup>4</sup> | Unsigned            | 2                          |

|                   |                              | 1   | Unsigned              | Signed              | Limit output up to 15 bits |

#### Notes:

- 1. This operating mode is compatible with TMC2242.

- 2. This is an enhanced operating mode of the GF9102A.

- 3. SO<sub>0</sub>, the LSB of the output is a bi-directional pad with a large pull-down resistor. This pin does not have to be connected. When this pin is not connected the GF9102A defaults to a mode compatible with the TMC2242.

- 4. Application notes for the TMC2242 suggest grounding the MSB of the input if the input data is unsigned as in most A/D converters. This method limits the input to 11 bits and leads to potential output non-saturated type overflow since the MSB of the output is ignored.

- 5. Signed: two's complement binary data.

I\_unsigned: invert all bits in signed data except for the MSB; also called inverted offset binary.

Unsigned: invert MSB of signed data; also called offset binary.

Table 5: Output Rounding Control

| RND <sub>20</sub> | SO <sub>1</sub> <sup>3</sup> | No. of Output Bits | Description                              | Notes |

|-------------------|------------------------------|--------------------|------------------------------------------|-------|

| 000               | Output                       | 16                 | Rounding to 16 bit                       | 1     |

| 001               | Output                       | 15                 | Rounding to 15 bit                       | 1     |

| 010               | 0                            | 14                 | Rounding to 14 bit                       | 1     |

| 011               | 0                            | 13                 | Rounding to 13 bit                       | 1     |

| 100               | 0                            | 12                 | Rounding to 12 bit                       | 1     |

| 101               | 0                            | 11                 | Rounding to 11 bit                       | 1     |

| 110               | 0                            | 10                 | Rounding to 10 bit                       | 1     |

| 111               | 0                            | 9                  | Rounding to 9 bit                        | 1     |

| 100               | 1                            | 8                  | Rounding to 8 bit                        | 2     |

| 110               | 1                            | 10                 | CCIR 601 10 bit data format <sup>4</sup> | 2     |

| 101               | 1                            | 8                  | CCIR 601 8 bit data format <sup>5</sup>  | 2     |

**Notes:** 1. This operating mode is compatible with TMC2242.

- 2. This is an enhanced operating mode of the GF9102A.

- 3. SO<sub>1</sub>, the second LSB of the output is a bi-directional pad with a large pull-down resistor. This pin does not have to be connected. When this pin is not connected the GF9102A defaults to a mode compatible with the TMC2242.

- 4. CCIR 601 10 bit data format range from Hex 004 to 3FB.

- 5. CCIR 601 8 bit data format range from Hex 01 to FE.

Table 6: Extra Control Input Pins using the Four Least Significant Bi-directional Output Pads SO<sub>3.0</sub>

| Conditions to allow Control Inputs | Output Pad <sup>1</sup> | Function                    | Notes |

|------------------------------------|-------------------------|-----------------------------|-------|

| RND≠ 000                           | SO <sub>0</sub> = 1     | Unsigned input              | 2     |

| RND = 100                          | SO <sub>1</sub> = 1     | 8 bit output rounding       | 2     |

| RND = 110                          | SO <sub>1</sub> = 1     | CCIR 601 10 bit data format | 2     |

| RND = 101                          | SO <sub>1</sub> = 1     | CCIR 601 8 bit data format  | 2     |

| RND = 1XX                          | SO <sub>2</sub>         | Reserved                    |       |

| RND = 1XX                          | SO <sub>3</sub>         | Reserved                    |       |

**Notes:** 1. SO<sub>3..0</sub> pins are bi-directional with a large pull-down resistor. These pins do not have to be connected. When these pins are not connected the GF9102A defaults to a mode compatible with the TMC2242.

2. This is an enhanced operating mode of the GF9102A.

521 - 26 - 02

Table 7: Input Step Response

| INPUT       |                                            | OUTF | PUT                                        |      |                 |

|-------------|--------------------------------------------|------|--------------------------------------------|------|-----------------|

|             | DECIMATION                                 |      | INTERPOLATION                              |      | ]               |

|             | $\overline{INT} = 1, \ \overline{DEC} = 0$ | SYNC | $\overline{INT} = 0, \ \overline{DEC} = 1$ | SYNC |                 |

| XXX         | XXX                                        | 1    | XXX                                        | 1    |                 |

| 400         | XX                                         | 0    | XX                                         | 0    |                 |

| 400         | XX                                         | 0    | XX                                         | 0    |                 |

| •           | •                                          | •    | •                                          | •    |                 |

| 55 cycles • | •                                          | •    | •                                          | •    |                 |

| •           | •                                          | •    | •                                          | •    |                 |

| 400         | 4000                                       | 0    | 2000                                       | 0    |                 |

| 400         | 4000                                       | 0    | 2000                                       | 0    |                 |

| 000         | 4000                                       | 0    | 2000                                       | 0    |                 |

| •           | •                                          | •    | •                                          | •    |                 |

| •           | •                                          | •    | •                                          | •    |                 |

| •           | •                                          | •    | •                                          | •    |                 |

| 000         | 44E2                                       | 0    | 244A                                       | 0    | Maximum Ringing |

| 000         | 44E2                                       | 0    | 1F6A                                       | 0    |                 |

| 000         | 2F6A                                       | 0    | 1000                                       | 0    |                 |

| 000         | 2F6A                                       | 0    | 0096                                       | 0    |                 |

| 000         | FC4C                                       | 0    | FBB6                                       | 0    | Minimum Ringing |

| 000         | FC4C                                       | 0    | FF68                                       | 0    |                 |

| •           | •                                          | •    | •                                          | •    |                 |

| •           | •                                          | •    | •                                          | •    |                 |

| •           | •                                          | •    | •                                          | •    |                 |

| 000         | 0000                                       | 0    | 0000                                       | 0    | Steady State    |

7

NOTE: TCO = 1

#### **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER                            | VALUE                                                              |

|--------------------------------------|--------------------------------------------------------------------|

| Supply Voltage                       | -0.3 to +7.0V                                                      |

| Input Voltage Range                  | 0.5 to (VDD + 0.5)V                                                |

| Operating Temperature Range          | $0^{\circ}\text{C} \le \text{T}_{\text{A}} \le 70^{\circ}\text{C}$ |

| Storage Temperature Range            | -65°C ≤ T <sub>S</sub> ≤ 150°C                                     |

| Lead Temperature (soldering, 10 sec) | 260°C                                                              |

# CAUTION ELECTROSTATIC SENSITIVE DEVICES DO NOT OPEN PACKAGES OR HANDLE EXCEPT AT A STATIC-FREE WORKSTATION

#### **ELECTRICAL CHARACTERISTICS**

Conditions:  $V_{DD} = 5 \text{ V}$ ,  $T_A = 0^{\circ}$  to  $70^{\circ}\text{C}$ ,  $R_L = 150 \ \Omega$  to GND and 144  $\Omega$  AC coupled unless otherwise shown.

| PARAMETER                      | SYMBOL           | CONDITIONS                                                 | MIN  | TYP             | MAX  | UNITS |

|--------------------------------|------------------|------------------------------------------------------------|------|-----------------|------|-------|

| Supply Voltage                 | V <sub>DD</sub>  |                                                            | 4.75 | 5               | 5.25 | volts |

| Supply Current Quiescent       | I <sub>DDQ</sub> | $V_{DD} = Max, V_{IN} = 0V$                                | -    | 5               | 10   | mA    |

| Supply Current Unloaded        | I <sub>DDU</sub> | $V_{DD} = Max, \overline{OE} = V_{DD}, f = 20 \text{ MHz}$ | -    | 60 <sup>1</sup> | 95   | mA    |

| Input Voltage, Logic Low       | V <sub>IL</sub>  |                                                            | -    | -               | 0.8  | volts |

| Input Voltage, Logic High      | V <sub>IH</sub>  |                                                            | 2.0  | -               | -    | volts |

| Switching Threshold            | V <sub>T</sub>   | TTL                                                        | -    | 1.5             | -    | volts |

| Input Current: (TTL Inputs)    | I <sub>IN</sub>  | V <sub>IN</sub> = V <sub>DD OR</sub> V <sub>SS</sub>       | -10  | ±1              | 10   | μΑ    |

| Inputs with Pulldown Resistors |                  | $V_{IN} = V_{DD}$                                          | 35   | 115             | 222  | μΑ    |

| Inputs with Pullup Resistors   |                  | $V_{IN} = V_{SS}$                                          | -35  | -115            | -214 | μА    |

| Ouput Voltage, Logic Low       | V <sub>OL</sub>  | V <sub>DD</sub> = Min, I <sub>OL</sub> = 6mA               | -    | 0.2             | 0.4  | volts |

| Ouput Voltage, Logic High      | V <sub>OH</sub>  | V <sub>DD</sub> = Min, I <sub>OH</sub> = -6mA              | 2.4  | 4.5             | -    | volts |

| Hi-Z Output Leakage Current    | I <sub>OZ</sub>  | $V_{DD} = Max, \overline{OE} = 1$                          | -10  | ±1              | 10   | μΑ    |

| Short Circuit Output Current   | I <sub>OS</sub>  | V <sub>DD</sub> = Max, output high one pin to              | -    | -               | 210  | mA    |

|                                |                  | ground, one second duration max                            |      |                 |      |       |

| Input Capacitance              | C <sub>IN</sub>  | $T_A = 25$ °C, $f = 1$ MHz                                 | -    | -               | 10   | pF    |

| Output Capacitance             | C <sub>OUT</sub> | $T_A = 25^{\circ}C, f = 1MHz$                              | -    | -               | 10   | pF    |

| Ambient Temperature, Still Air | T <sub>A</sub>   |                                                            | 0    | -               | 70   | °C    |

NOTE 1: Supply current may fluctuate with changes in data pattern.

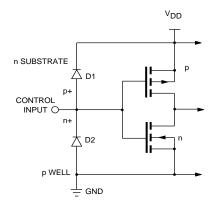

Fig. 8a Equivalent Input Circuit

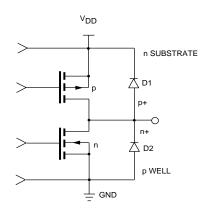

Fig. 8b Equivalent Output Circuit

521 - 26 - 02

### **SWITCHING CHARACTERISTICS,** $T_A$ from 0°C to 70°C unless otherwise specified.

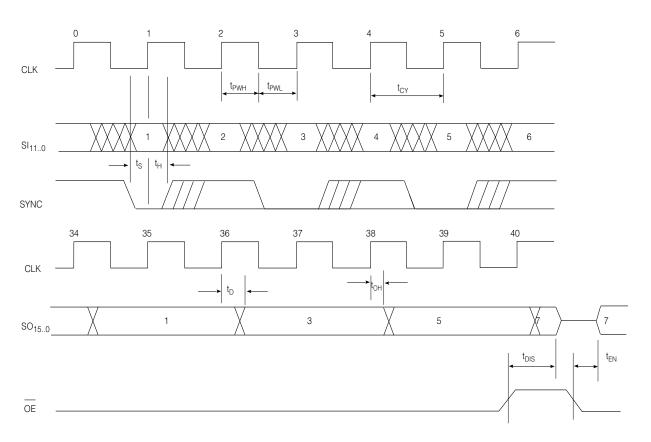

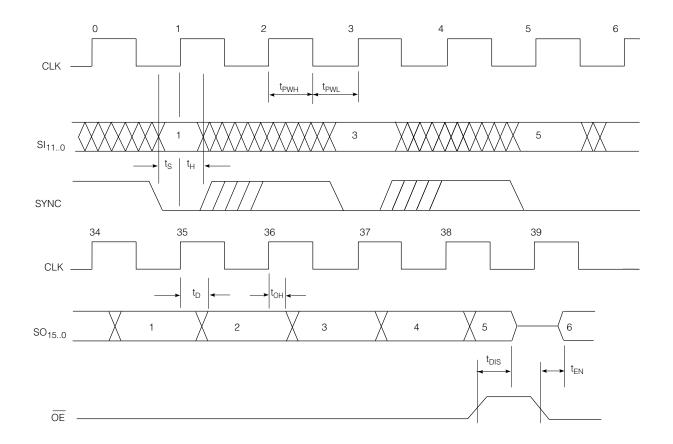

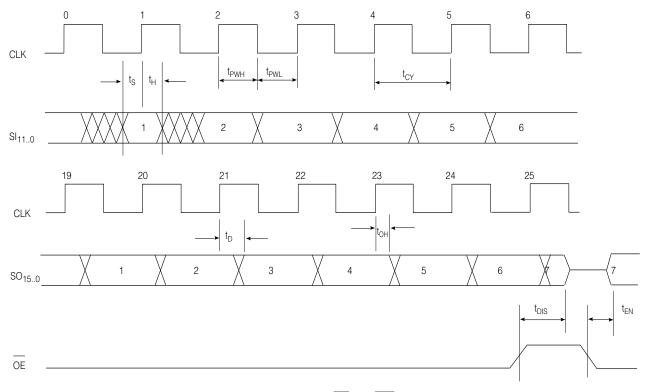

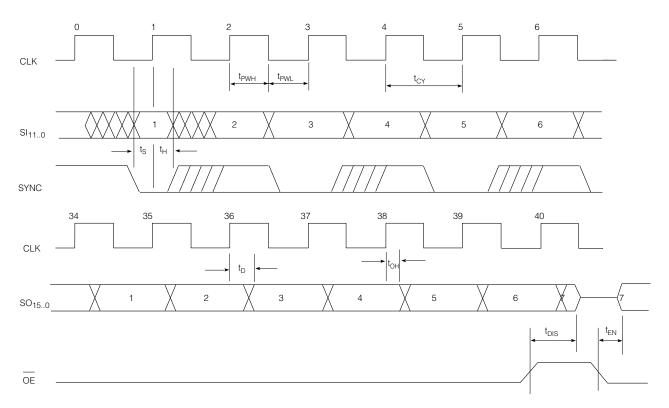

| NAME             | PARAMETER              | TEST CONDITIONS                             | MIN | TYP | MAX | UNITS |

|------------------|------------------------|---------------------------------------------|-----|-----|-----|-------|

| t <sub>D</sub>   | Output delay           | V <sub>DD</sub> =Min, C <sub>L</sub> =25 pF | -   | -   | 15  | ns    |

| t <sub>OH</sub>  | Output hold            | V <sub>DD</sub> =Max, C <sub>L</sub> =25 pF | 3   | -   | -   | ns    |

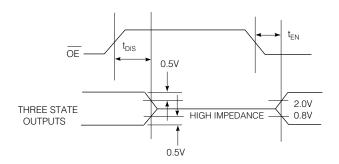

| t <sub>EN</sub>  | Output enable          | V <sub>DD</sub> =Min, C <sub>L</sub> =25 pF | -   | -   | 15  | ns    |

| t <sub>DIS</sub> | Output disable         | V <sub>DD</sub> =Min, C <sub>L</sub> =25 pF | -   | -   | 15  | ns    |

| t <sub>CY</sub>  | Cycle time             |                                             | 25  | -   | -   | ns    |

| t <sub>PWL</sub> | Clock pulse width low  |                                             | 10  | -   | -   | ns    |

| t <sub>PWH</sub> | Clock pulse width high |                                             | 10  | -   | -   | ns    |

| t <sub>S</sub>   | Input setup time       |                                             | 6   | -   | -   | ns    |

| t <sub>H</sub>   | Input hold time        |                                             | 0   | -   | -   | ns    |

Fig. 9 Timing Diagram - Decimation  $\overline{INT} = 1$ ,  $\overline{DEC} = 0$ , SYNC = SYNC

9 521 - 26 - 02

Fig. 10 Timing Diagram - Interpolation  $\overline{INT} = 0$ ,  $\overline{DEC} = 1$ , SYNC = SYNC

Fig. 11 Timing Diagram - Decimation  $\overline{INT} = 0$ ,  $\overline{DEC} = 0$ , SYNC = 0 or SYNC = 1

Fig. 12 Timing Diagram - Decimation  $\overline{INT}$  = 1,  $\overline{DEC}$  = 1, SYNC = SYNC

Fig. 13 Threshold Levels for Three State Measurement