# 32-bit Proprietary Microcontrollers

**CMOS**

# FR30 Family MB91151A Series

# **MB91151A**

### **■ DESCRIPTION**

The MB91151A is a single-chip microcontroller using a 32-bit RISC-CPU (FR30 family) as its core.

#### **■ FEATURES**

#### **CPU**

- 32-bit RISC (FR30), load/store architecture, 5-stage pipeline

- General-purpose registers : 32 bits × 16

- 16-bit fixed-length instructions (basic instructions), 1 instruction/ 1 cycle

- Memory-to-memory transfer, bit processing, barrel shift processing : Optimized for embedded applications

- Function entrance/exit instructions, and multiple load/store instructions of register contents, instruction systems supporting high level languages

- · Register interlock functions, efficient assembly language description

- · Branch instructions with delay slots: Reduced overhead time in branching executions

- Internal multiplier/supported at instruction level

Signed 32-bit multiplication: 5 cycles Signed 16-bit multiplication: 3 cycles

• Interrupt (PC and PS saving) : 6 cycles, 16 priority levels

(Continued)

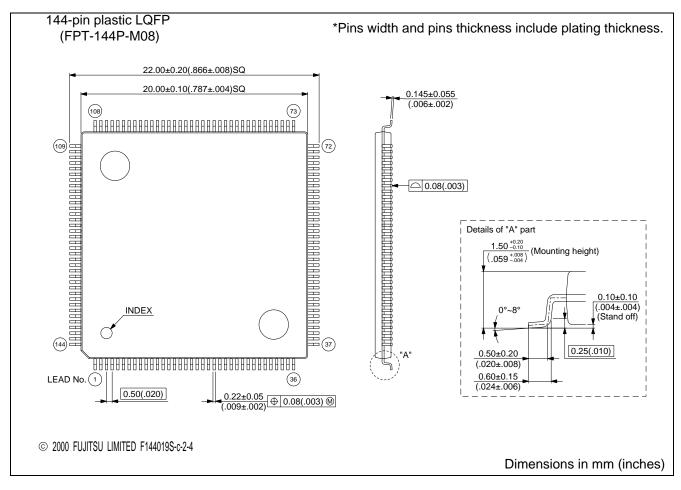

### ■ PACKAGE

144-pin plastic LQFP

(FPT-144P-M08)

#### (Continued)

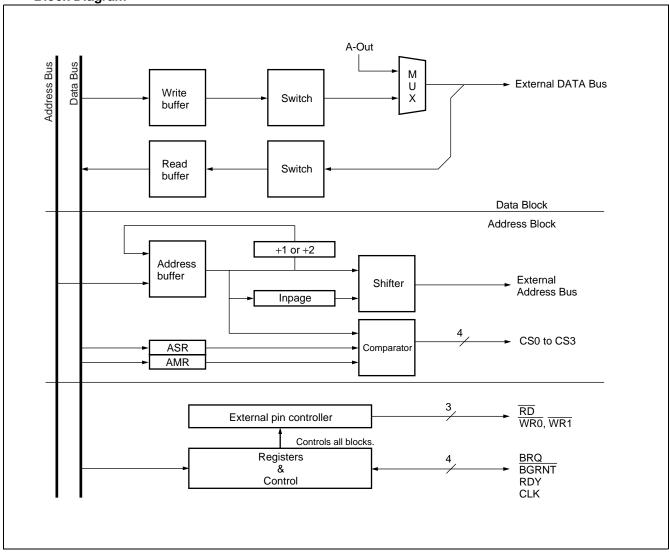

### **Bus Interface**

- 16-bit address output, 8/16-bit data input and output

- Basic bus cycle : 2-clock cycle

- Support for interface for various types of memory

- Unused data/address pins can be configured as input/output ports

- · Support for little endian mode

#### **Internal RAM**

Instruction RAM: 2 Kbytes

Data RAM: 32 Kbytes

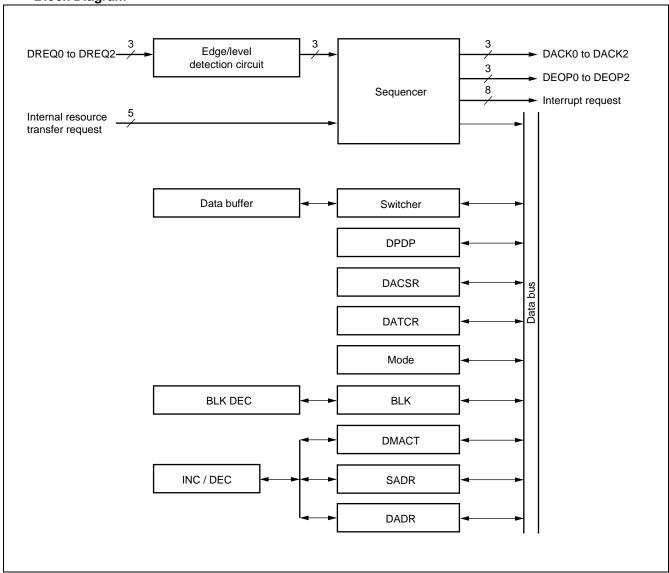

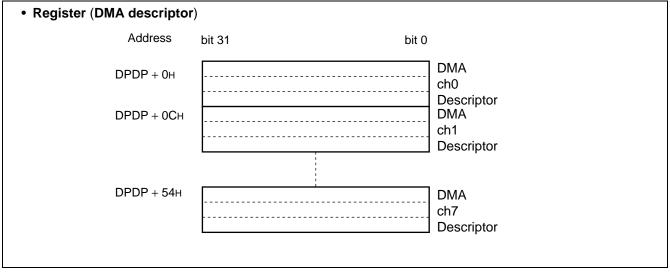

#### **DMAC**

DMAC in descriptor format for placing transfer parameters on to the main memory.

Capable of transferring a maximum of eight internal and external factors combined.

Three channels for external factors

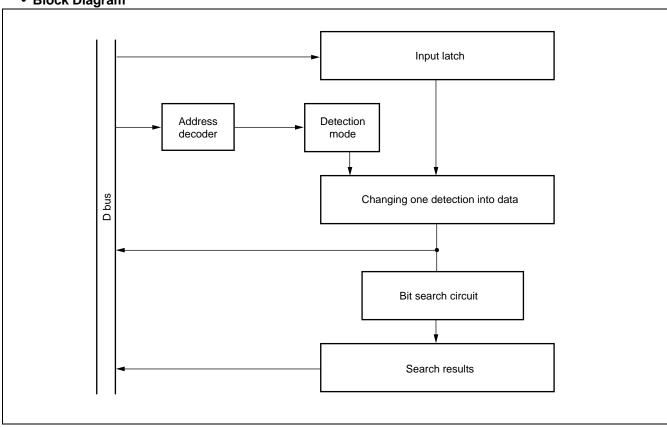

#### **Bit Search Module**

Searches in one cycle for the position of the bit that changes from the MSB in one word to the initial 1/0.

#### **Timers**

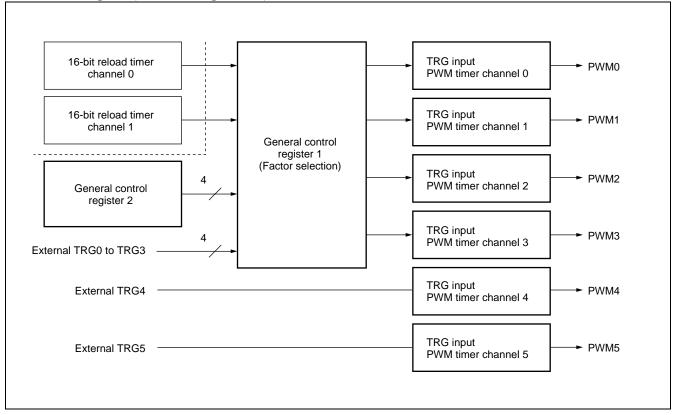

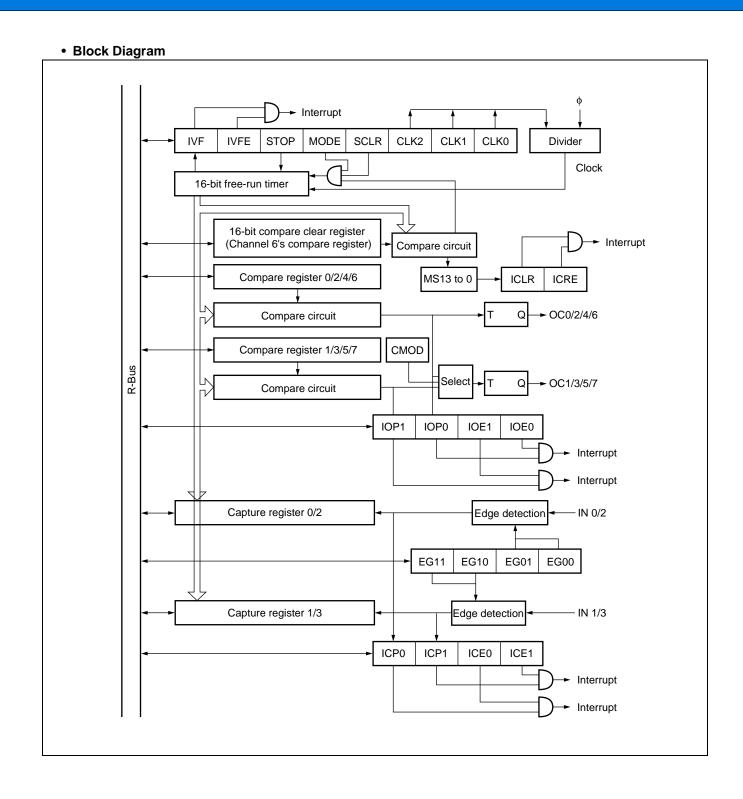

- 16-bit OCU × 8 channels, ICU × 4 channels, Free-run timer × 1 channel

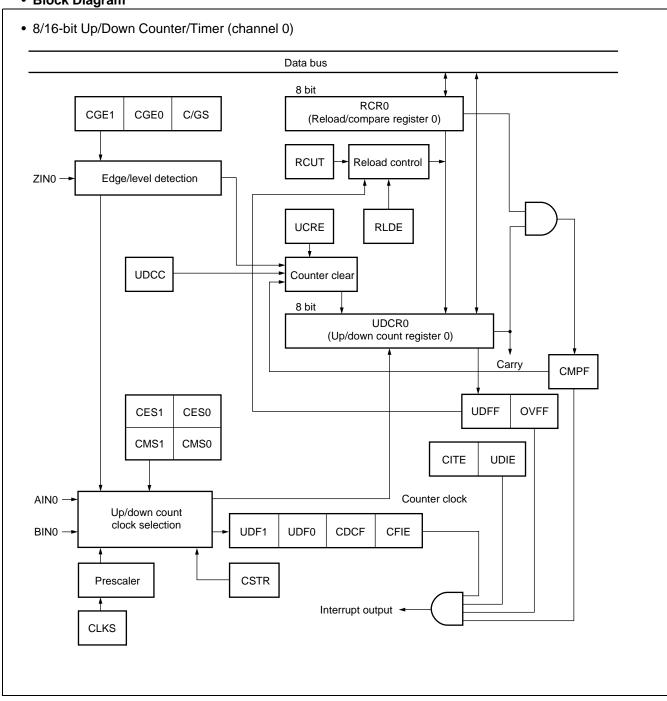

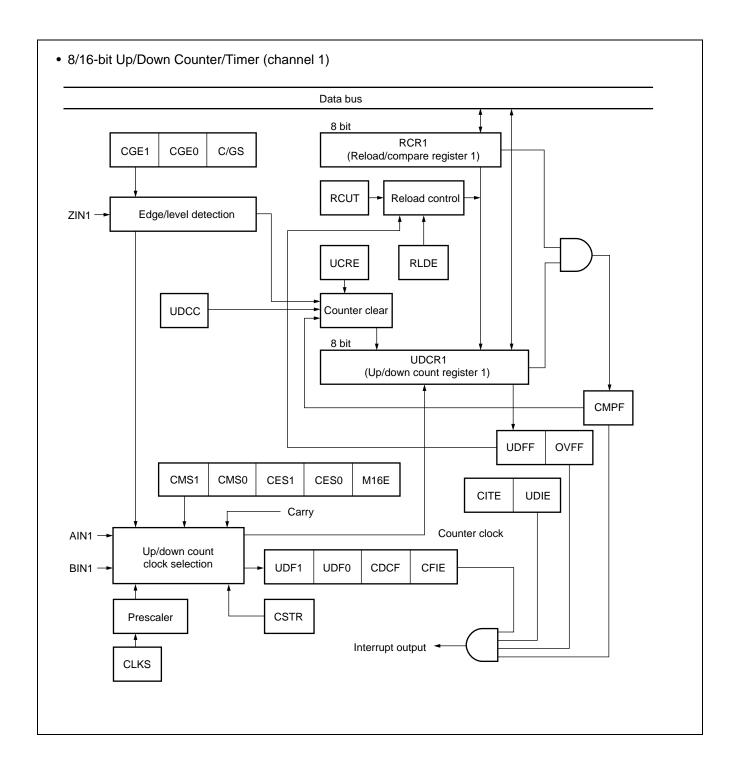

- 8/16-bit up/down timer/counter (8-bit × 2 channels or 16-bit × 1 channel)

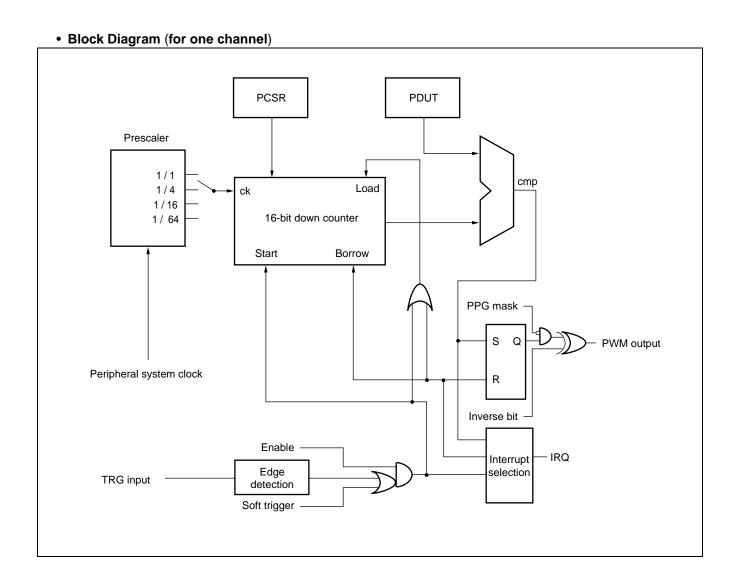

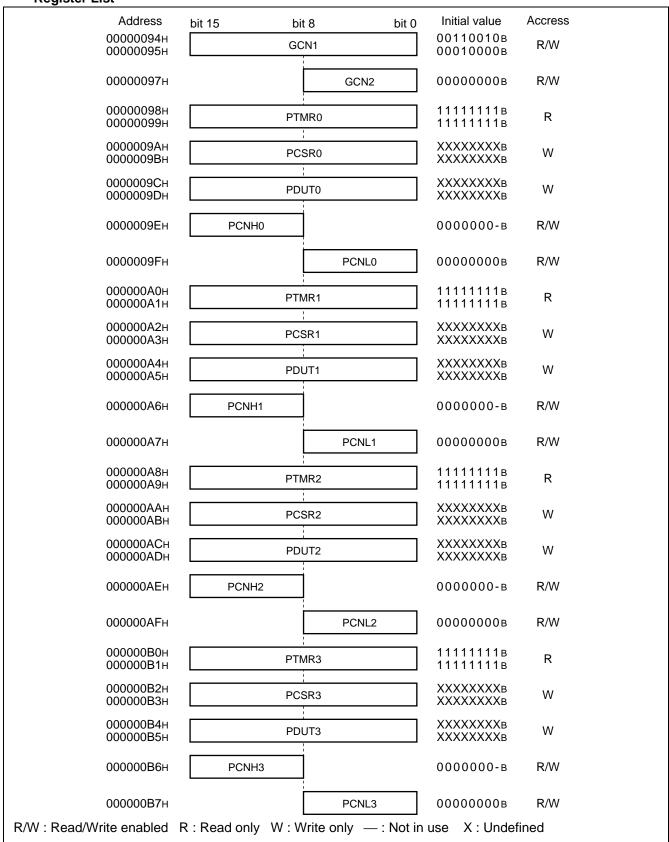

- 16-bit PPG timer × 6 channels. The output pulse cycle and duty can be varied as desired.

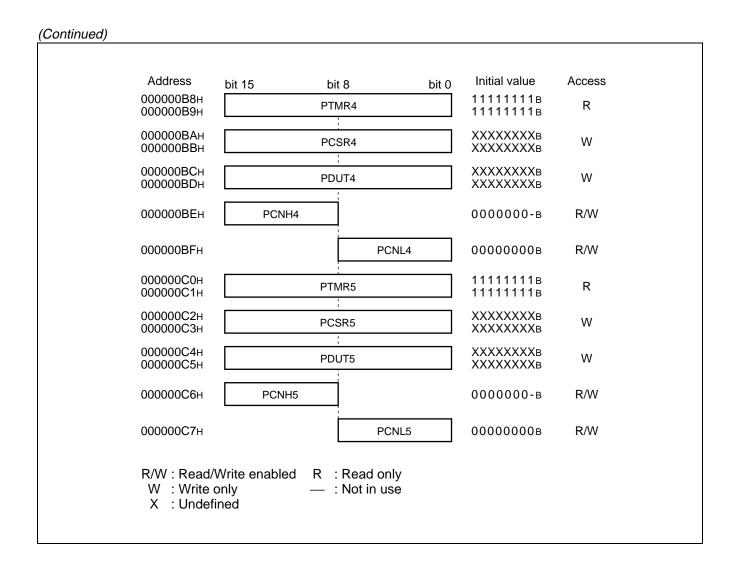

- 16-bit reload timer × 4 channels

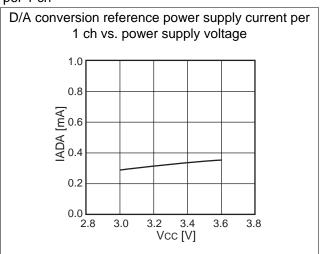

#### **D/A Converter**

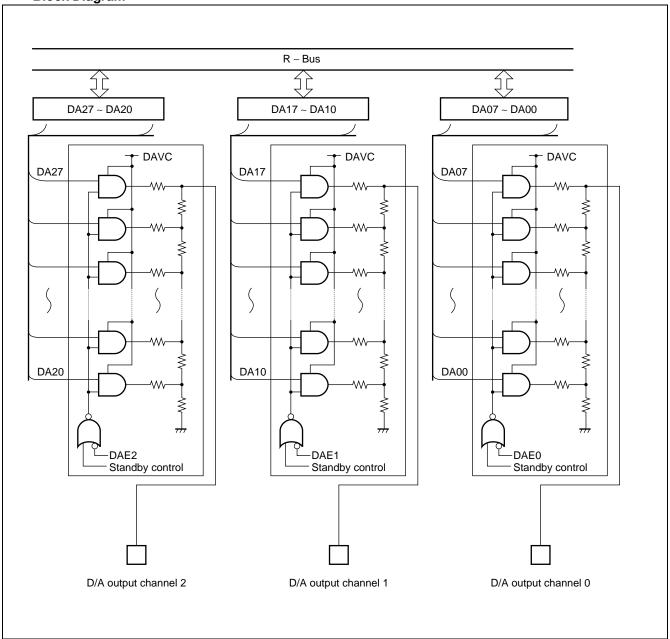

• 8-bit × 3 channels

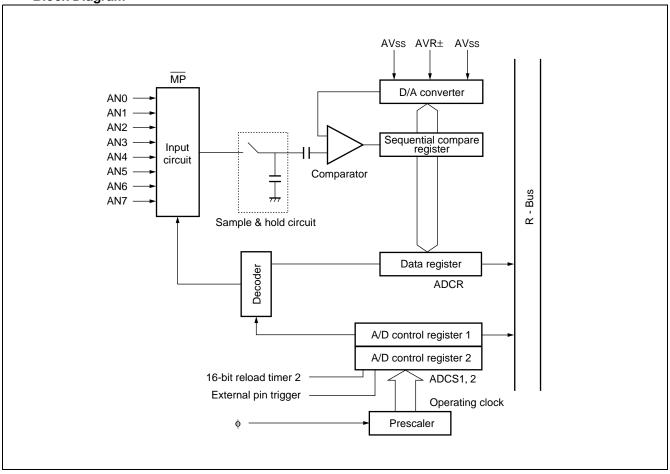

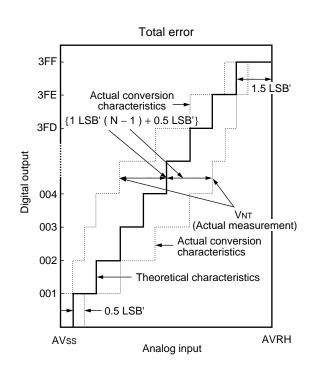

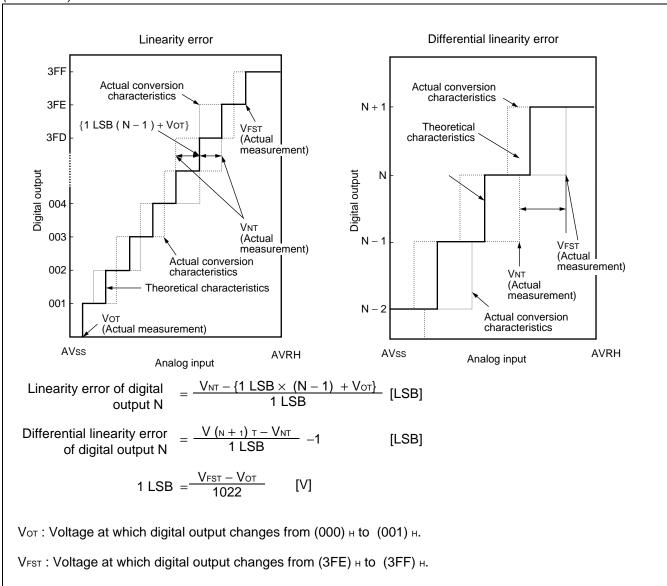

### A/D Converter (Sequential Comparison Type)

- 10-bit × 8 channels

- Sequential conversion method (conversion time : 5.0 μs@33 MHz)

- Single conversion or scan conversion can be selected, and one-shot or continuous or stop conversion mode can be set respectively.

- Conversion starting function by hardware/software.

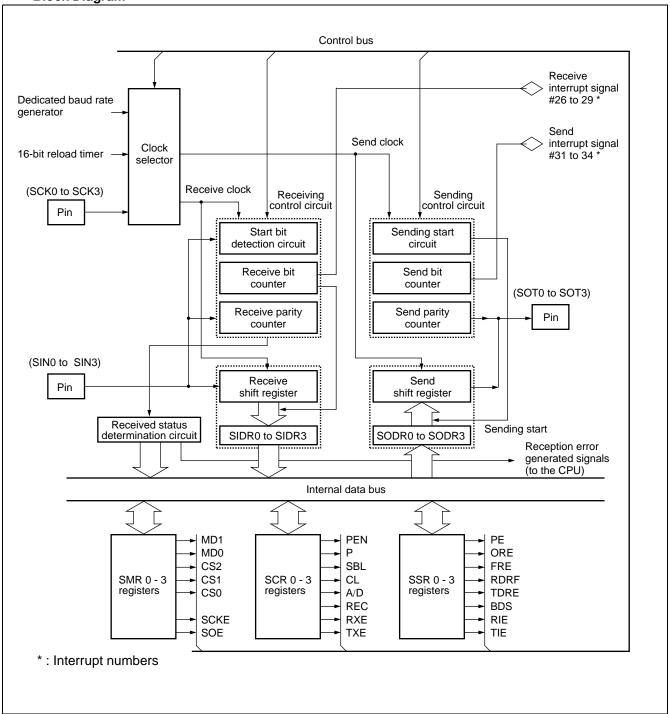

#### Serial I/O

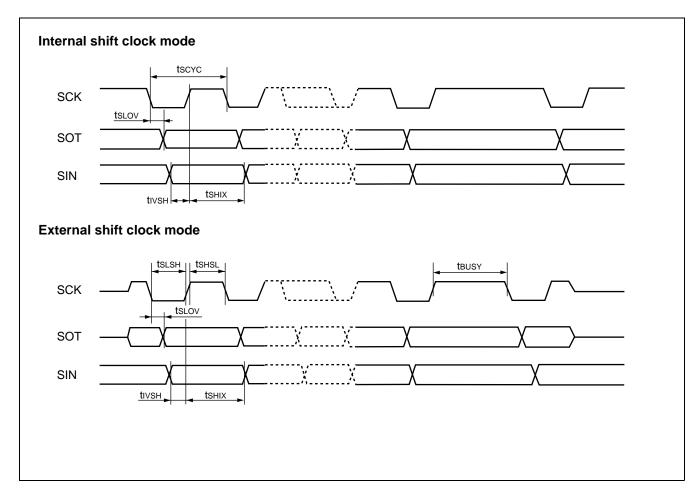

- UART × 4 channels. Any of them is capable of serial transfer in sync with clock attached with the LSB/MSB switching function.

- Serial data output and serial clock output are selectable by push-pull/open drain software.

- A 16-bit timer (U-timer) is contained as a dedicated baud rate generator allowing any baud rate to be generated.

### **Clock Switching Function**

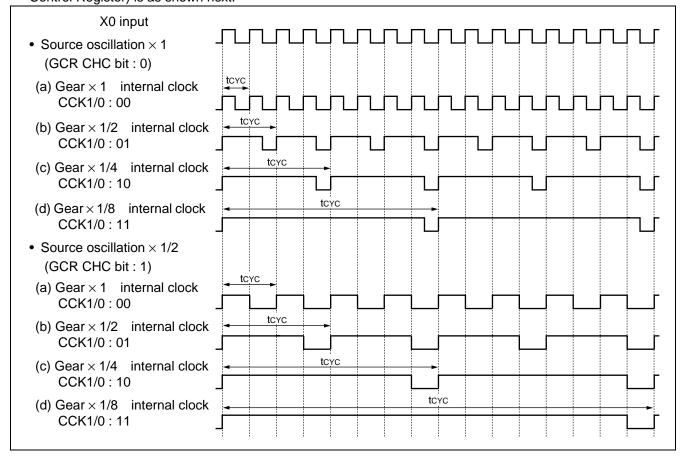

• Gear function: Operating clock ratios to the basic clock can be set independently for the CPU and peripherals from four types, 1:1, 1:2, 1:4 or 1:8.

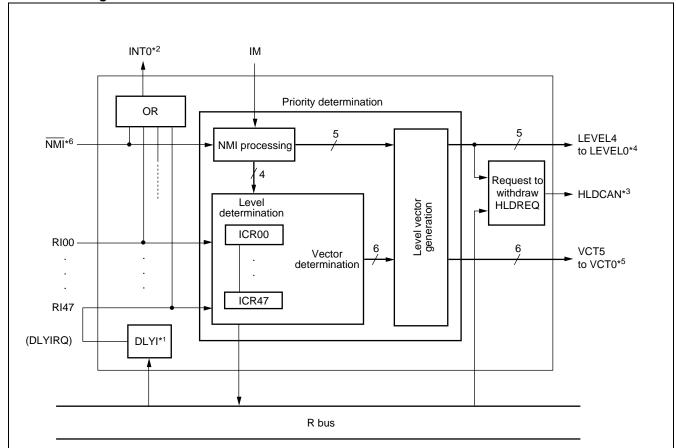

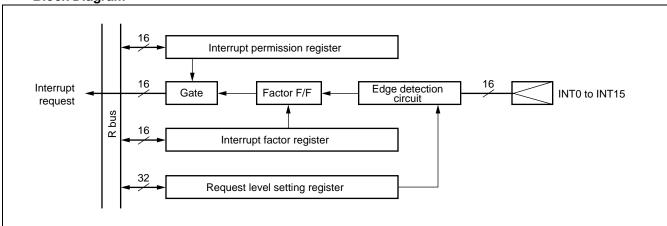

### **Interrupt Controller**

External interrupt input (16 channels in total)

• Allows the rising edge/falling edge/H level/L level to be set.

Internal interrupt factors

· Interrupt by resources and delay interrupt

### Others

- Reset cause: Power on reset/watchdog timer/software reset/external reset

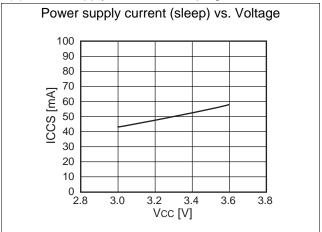

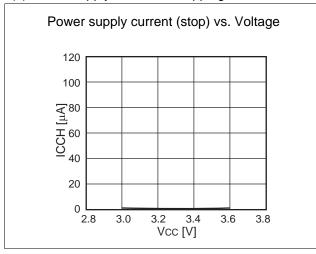

- Low power consumption mode : Sleep/stop

- Package: 144-pin LQFP

- CMOS technology (0.35 μm)

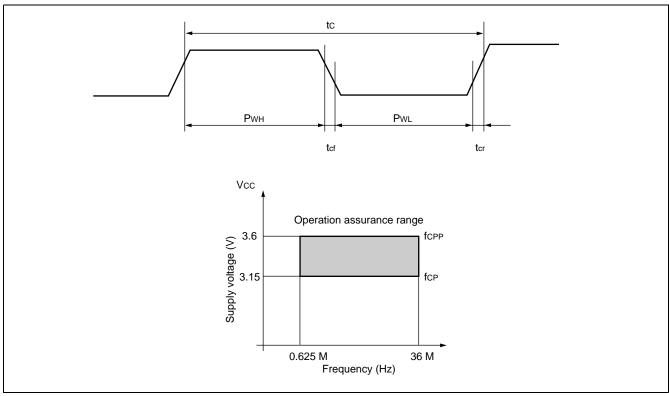

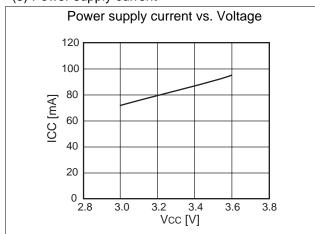

- Power supply voltage: 3.15 V to 3.6 V

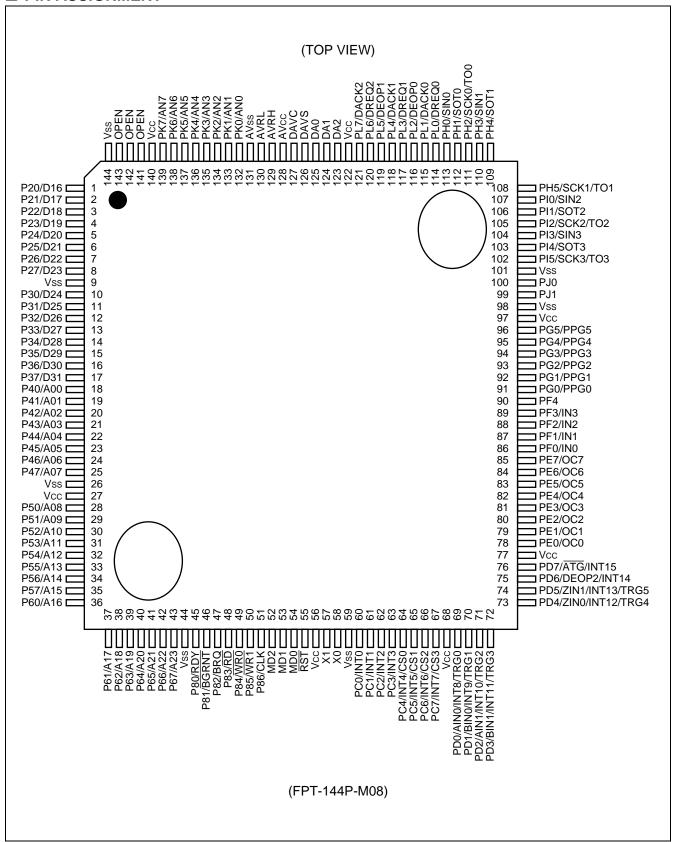

### **■ PIN ASSIGNMENT**

### **■ PIN DESCRIPTION**

| Pin No.                                                                                      | Pin name                                                                                                                                                                     | Circuit type | Function                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8                                                         | D16/P20<br>D17/P21<br>D18/P22<br>D19/P23<br>D20/P24<br>D21/P25<br>D22/P26<br>D23/P27                                                                                         | С            | Bit 16 to bit 23 of external data bus These pins are activated only in 16-bit external bus mode. These pins are available as ports in single-chip and 8-bit external bus modes.                                    |

| 10<br>11<br>12<br>13<br>14<br>15<br>16<br>17                                                 | D24/P30<br>D25/P31<br>D26/P32<br>D27/P33<br>D28P34<br>D29/P35<br>D30/P36<br>D31/P37                                                                                          | С            | Bit 24 to bit 31 of external data bus These pins are available as ports in single-chip mode.                                                                                                                       |

| 18<br>19<br>20<br>21<br>22<br>23<br>24<br>25<br>28<br>29<br>30<br>31<br>32<br>33<br>34<br>35 | A00/P40<br>A01/P41<br>A02/P42<br>A03/P43<br>A04/P44<br>A05/P45<br>A06/P46<br>A07/P47<br>A08/P50<br>A09/P51<br>A10/P52<br>A11/P53<br>A12/P54<br>A13/P55<br>A14/P56<br>A15/P57 | F            | Bit 0 to bit 15 of external address bus These pins are activated in external bus mode. These pins are available as ports in single-chip mode.                                                                      |

| 36<br>37<br>38<br>39<br>40<br>41<br>42<br>43                                                 | A16/P60<br>A17/P61<br>A18/P62<br>A19/P63<br>A20/P64<br>A21/P65<br>A22/P66<br>A23/P67                                                                                         | 0            | Bit 16 to bit 23 of external address bus These pins are available as ports when the address bus is not in use.                                                                                                     |

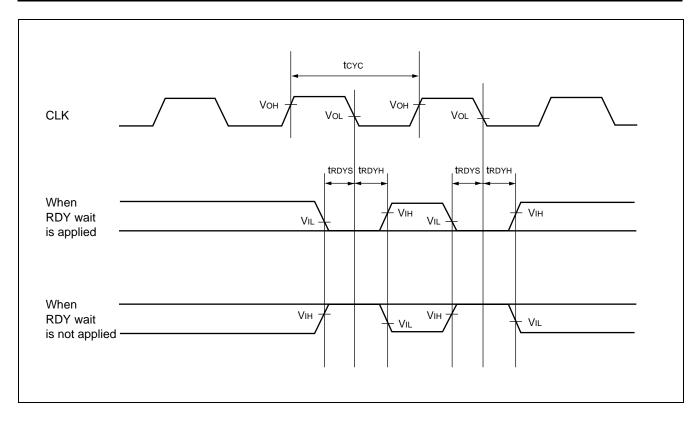

| 45                                                                                           | RDY/P80                                                                                                                                                                      | С            | External RDY input This function is activated when external RDY input is allowed. Input "0" when the bus cycle being executed does not end. This pin is available as a port when external RDY input is not in use. |

| Pin No.              | Pin name                                     | Circuit type | Function                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|----------------------|----------------------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 46                   | BGRNT/P81                                    | F            | External bus release acceptance output This function is activated when external bus release acceptance output allowed. Output "L" upon releasing of the external bus. This pin is available as a port when external bus release acceptance ou put is not allowed.                                                                                                                                                          |  |  |

| 47                   | BRQ/P82                                      | С            | External bus release request input This function is activated when external bus release request input is allowed. Input "1" when the release of the external bus is desired. This pin is available as a port when external bus release request input is not in use.                                                                                                                                                        |  |  |

| 48                   | RD/P83                                       | F            | External bus read strobe output This function is activated when external bus read strobe output is allowed. This pin is available as a port when external bus read strobe output is not allowed.                                                                                                                                                                                                                           |  |  |

| 49                   | WR0/P84                                      | F            | External bus write strobe output This function is activated in external bus mode. This pin is available as a port in single chip mode.                                                                                                                                                                                                                                                                                     |  |  |

| 50                   | WR1/P85                                      | F            | External bus write strobe output This function is activated in external bus mode when the bus width is 16 bits. This pin is available as a port in single chip mode or when the external bus width is 8 bits.                                                                                                                                                                                                              |  |  |

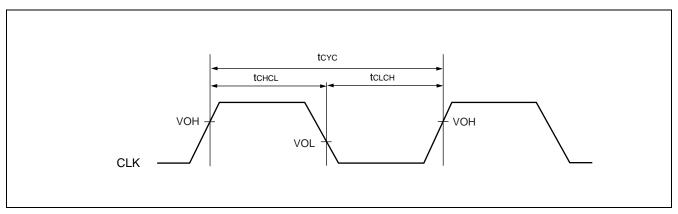

| 51                   | CLK/P86                                      | F            | System clock output The pin outputs the same clock as the external bus operating frequency. The pin is available as a port when it is not used to output the clock.                                                                                                                                                                                                                                                        |  |  |

| 52<br>53<br>54       | MD2<br>MD1<br>MD0                            | G            | Mode pins To use these pins, connect them directly to either Vcc or Vss. Use these pins to set the basic MCU operating mode.                                                                                                                                                                                                                                                                                               |  |  |

| 55                   | RST                                          | В            | External reset input                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 57<br>58             | X1<br>X0                                     | А            | High-speed clock oscillation pins                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 60<br>61<br>62<br>63 | INT0/PC0<br>INT1/PC1<br>INT2/PC2<br>INT3/PC3 | Н            | External interrupt request input 0-3 Since this input is used more or less continuously when the corresponding external interrupt is allowed, output by the port needs to be stopped except when it is performed deliberately. Since this port is allowed to input also in standby mode, it can be used to reset the standby state. These pins are available as ports when external interrupt request input is not in use. |  |  |

| Pin No.                          | Pin name                                                                                                                             | Circuit type | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 64<br>65<br>66<br>67             | INT4/PC4/CS0<br>INT5/PC5/CS1<br>INT6/PC6/CS2<br>INT7/PC7/CS3                                                                         | Н            | These pins also serve as the chip select output and external interrupt request input 4 to 7.  When the chip select output is not allowed, these pins are available as external interrupt requests or ports.  Since this input is used more or less continuously when the corresponding external interrupt is allowed, output by the port needs to be stopped except when it is performed deliberately.  Since this port is also allowed to input in standby mode, the port can be used to reset the standby state.  These pins are available as ports when external interrupt request input and chip select output are not in use. |

| 69<br>70<br>71<br>72<br>73<br>74 | PD0/AIN0/INT8/TRG0<br>PD1/BIN0/INT9/TRG1<br>PD2/AIN1/INT10/TRG2<br>PD3/BIN1/INT11/TRG3<br>PD4/ZIN0/INT12/TRG4<br>PD5/ZIN1/INT13/TRG5 | Н            | External interrupt request input 8 to 13 Since this input is used more or less continuously when the corresponding external interrupt is allowed, output by the port needs to be stopped except when it is performed deliberately.  [AIN, BIN] Up/down timer input.  [TRG] PPG external trigger input.  Since this input is used more or less continuously while input is allowed, output by the port needs to be stopped except when it is performed deliberately.  These pins are available as ports when the external interrupt request input, up timer counter input, and PPG external trigger input are not in use.           |

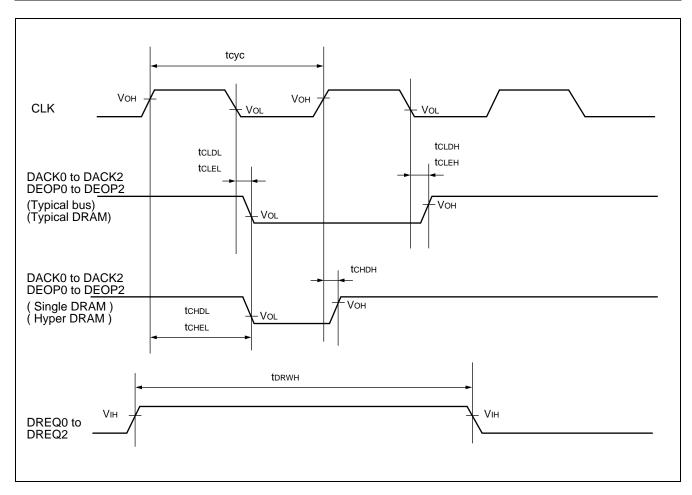

| 75                               | PD6/DEOP2/INT14                                                                                                                      | Н            | External interrupt request input 14 Since this input is used more or less continuously when the corresponding external interrupt is allowed, output by the port needs to be stopped except when it is performed deliberately. [DEOP2] DMA external transfer end output. This function is activated when DMAC external transfer end output is allowed. This pin is available as a port when it is not in use as the external interrupt request input or DMA external transfer end output.                                                                                                                                           |

| 76                               | PD7/ATG/INT15                                                                                                                        | Ħ            | External interrupt request input 15 Since this input is used more or less continuously when the corresponding external interrupt is allowed, output by the port needs to be stopped except when it is performed deliberately.  [ATG] A/D converter external trigger input.  Since this input is used more or less continuously when selected as an A/D activation factor, output by the port needs to be stopped except when it is performed deliberately.  This pin is available as a port when it is not in use as the external interrupt request input or A/D converter external trigger input.                                 |

| Pin No.                                      | Pin name                                                                             | Circuit type | Function                                                                                                                                                                                                                                                                     |  |

|----------------------------------------------|--------------------------------------------------------------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 78<br>79<br>80<br>81<br>82<br>83<br>84<br>85 | PE0/OC0<br>PE1/OC1<br>PE2/OC2<br>PE3/OC3<br>PE4/OC4<br>PE5/OC5<br>PE6/OC6<br>PE7/OC7 | F            | Output compare output These pins are available as ports when output compare output is not allowed.                                                                                                                                                                           |  |

| 86<br>87<br>88<br>89                         | PF0/IN0<br>PF1/IN1<br>PF2/IN2<br>PF3/IN3                                             | F            | Input capture input This function is activated when the input capture operation is input. These pins are available as ports when input capture input is not in use                                                                                                           |  |

| 90                                           | PF4                                                                                  | F            | General I/O port                                                                                                                                                                                                                                                             |  |

| 91<br>92<br>93<br>94<br>95<br>96             | PG0/PPG0<br>PG1/PPG1<br>PG2/PPG2<br>PG3/PPG3<br>PG4/PPG4<br>PG5/PPG5                 | F            | PPG timer output This function is activated when PPG timer output is allowed. These pins are available as ports when PPG timer output is not allowed.                                                                                                                        |  |

| 99<br>100                                    | PJ1<br>PJ0                                                                           | Q            | General I/O port                                                                                                                                                                                                                                                             |  |

| 102                                          | PI5/SCK3/TO3                                                                         | Р            | UART3 clock I/O, Reload timer 3 output When UART3 clock output is not allowed, reload timer 3 can be output by allowing it. This pin is available as a port when neither UART3 clock output nor reload timer output is allowed.                                              |  |

| 103                                          | PI4/SOT3                                                                             | Р            | UART3 data output This function is activated when UART3 data output is allowed. This pin is available as a port when UART3 clock output is not allowed.                                                                                                                      |  |

| 104                                          | PI3/SIN3                                                                             | Р            | UART3 data input Since this input is used more or less continuously while UART3 is engaged in input operations, output by the port needs to be stopped except when it is performed deliberately. This pin is available as a port when UART3 output data input is not in use. |  |

| Pin No. | Pin name     | Circuit type | Function                                                                                                                                                                                                                                                                                                 |  |  |  |

|---------|--------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 105     | PI2/SCK2/TO2 | Р            | UART2 clock I/O, Reload timer 2 output When UART2 clock output is not allowed, reload timer 2 can be output by allowing it. This pin is available as a port when neither UART2 clock output nor reload timer output is allowed.                                                                          |  |  |  |

| 106     | PI1/SOT2     | Р            | UART2 data output This function is activated when UART2 data output is allowed. This pin is available as a port when UART2 clock output is not allowed.                                                                                                                                                  |  |  |  |

| 107     | PI0/SIN2     | Р            | UART2 data input Since this input is used more or less continuously while UART2 is engaged in input operations, output by the port needs to be stopped except when it is performed deliberately. This pin is available as a port when UART2 data input is not in use.                                    |  |  |  |

| 108     | PH5/SCK1/TO1 | Р            | UART1 clock I/O, Reload timer 1 output When UART1 clock output is not allowed, reload timer 1 can be output by allowing it. This pin is available as a port when neither UART1 clock output nor reload timer output is allowed.                                                                          |  |  |  |

| 109     | PH4/SOT1     | Р            | UART1 data output This function is activated when UART1 data output is allowed. This pin is available as a port when UART1 clock output is not allowed.                                                                                                                                                  |  |  |  |

| 110     | PH3/SIN1     | Р            | UART1 data input Since this input is used more or less continuously while UART1 is engaged in input operations, output by the port needs to be stopped except when it is performed deliberately. This pin is available as a port when UART1 data input is not in use.                                    |  |  |  |

| 111     | PH2/SCK0/TO0 | Р            | UART0 clock I/O, Reload timer 0 output When UART0 clock output is not allowed, reload timer 0 can be output by allowing it. This pin is available as a port when neither UART0 clock output nor reload timer output is allowed.                                                                          |  |  |  |

| 112     | PH1/SOT0     | Р            | UART0 data output This function is activated when UART0 data output is allowed. This pin is available as a port when UART0 clock output is not allowed.                                                                                                                                                  |  |  |  |

| 113     | PH0/SIN0     | Р            | UART0 data input Since this input is used more or less continuously while UART0 is engaged in input operations, output by the port needs to be stopped except when it is performed deliberately. This pin is available as a port when UART0 data input is not in use.                                    |  |  |  |

| 114     | DREQ0/PL0    | F            | DMA external transfer request input Since this input is used more or less continuously when selected as a DMAC transfer factor, output by the port needs to be stopped except when it is performed deliberately. This pin is available as a port when DMA external transfer request input is not in use. |  |  |  |

| Pin No.           | Pin name          | Circuit type | Function                                                                                                                                                                                                                                                                                                 |  |  |

|-------------------|-------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 115               | DACK0/PL1         | F            | DMA external transfer request acceptance output This function is activated when the DMAC external transfer request acceptance is allowed to be output. This pin is available as a port when the DMAC transfer request acceptance is not allowed to be output.                                            |  |  |

| 116               | DEOP0/PL2         | F            | DMA external transfer end output This function is activated when the end of DMAC external transfer is allowed to be output.                                                                                                                                                                              |  |  |

| 117               | DREQ1/PL3         | F            | DMA external transfer request input Since this input is used more or less continuously when selected as a DMAC transfer factor, output by the port needs to be stopped except when it is performed deliberately. This pin is available as a port when DMA external transfer request input is not in use. |  |  |

| 118               | DACK1/PL4         | F            | DMA external transfer request acceptance output This function is activated when the DMAC external transfer request acceptance is allowed to be output. This pin is available as a port when DMAC transfer request acceptance output is not allowed.                                                      |  |  |

| 119               | DEOP1/PL5         | F            | DMA external transfer end output This function is activated when the end of DMAC external transfer is a lowed to be output.                                                                                                                                                                              |  |  |

| 120               | DREQ2/PL6         | F            | DMA external transfer request input Since this input is used more or less continuously when selected as a DMAC transfer factor, output by the port needs to be stopped except when it is performed deliberately. This pin is available as a port when DMA external transfer request input is not in use. |  |  |

| 121               | DACK2/PL7         | F            | DMA external transfer request acceptance output This function is activated when the DMAC external transfer request acceptance is allowed to be output. This pin is available as a port when DMAC transfer request acceptance output is not allowed.                                                      |  |  |

| 123<br>124<br>125 | DA2<br>DA1<br>DA0 | _            | D/A converter output This function is activated when D/A converter output is allowed.                                                                                                                                                                                                                    |  |  |

| 126               | DAVS              | _            | Power supply pin for the D/A converter                                                                                                                                                                                                                                                                   |  |  |

| 127               | DAVC              | _            | Power supply pin for the D/A converter                                                                                                                                                                                                                                                                   |  |  |

| 128               | AVcc              | _            | Vcc power supply for the A/D converter                                                                                                                                                                                                                                                                   |  |  |

| 129               | AVRH              |              | A/D converter reference voltage (high potential side) Be sure to turn on/off this pin with potential higher than AVRH applied to Vcc.                                                                                                                                                                    |  |  |

| 130               | AVRL              |              | A/D converter reference voltage (low potential side)                                                                                                                                                                                                                                                     |  |  |

| 131               | AVss              |              | Vss power supply for the A/D converter                                                                                                                                                                                                                                                                   |  |  |

### (Continued)

| Pin No.                                              | Pin name                                                                             | Circuit type | Function                                                                                                                                                                                   |

|------------------------------------------------------|--------------------------------------------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 132<br>133<br>134<br>135<br>136<br>137<br>138<br>139 | AN0/PK0<br>AN1/PK1<br>AN2/PK2<br>AN3/PK3<br>AN4/PK4<br>AN5/PK5<br>AN6/PK6<br>AN7/PK7 | N            | A/D converter analog input These pins are activated when the AIC register is designated for analog input. These pins are available as ports when A/D converter analog input is not in use. |

| 27, 56, 68,<br>77, 97,<br>122, 140                   | Vcc                                                                                  | _            | Power supply pin (Vcc) for digital circuit Always power supply pin (Vcc) must be connected to the power supply.                                                                            |

| 9, 26, 44,<br>59, 98,<br>101, 144                    | Vss                                                                                  | _            | Earth level (Vss) for digital circuit Always power supply pin (Vss) must be connected to the power supply.                                                                                 |

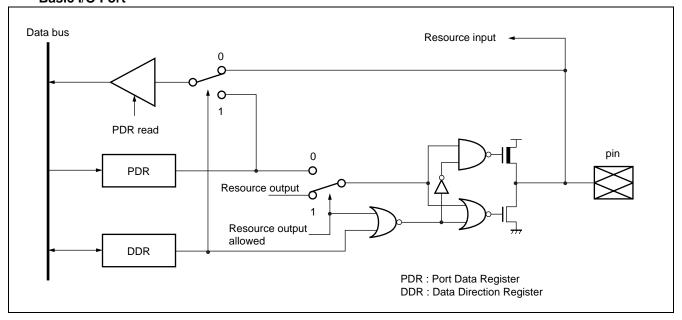

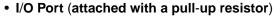

Note: On the majority of pins listed above, the I/O port and the resource I/O are multiplexed, such as XXXX/Pxx. When the port and the resource output compete against each other on these pins, priority is given to the resource.

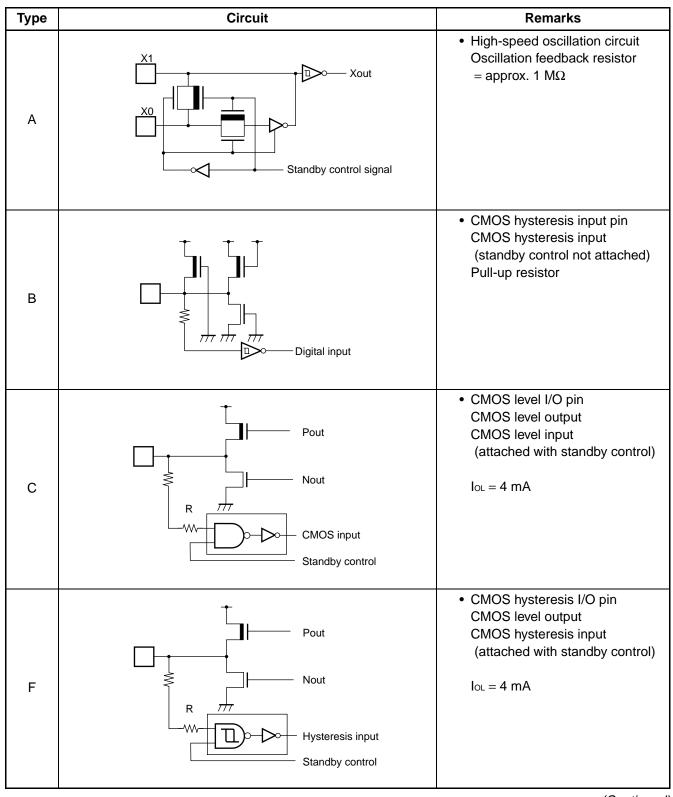

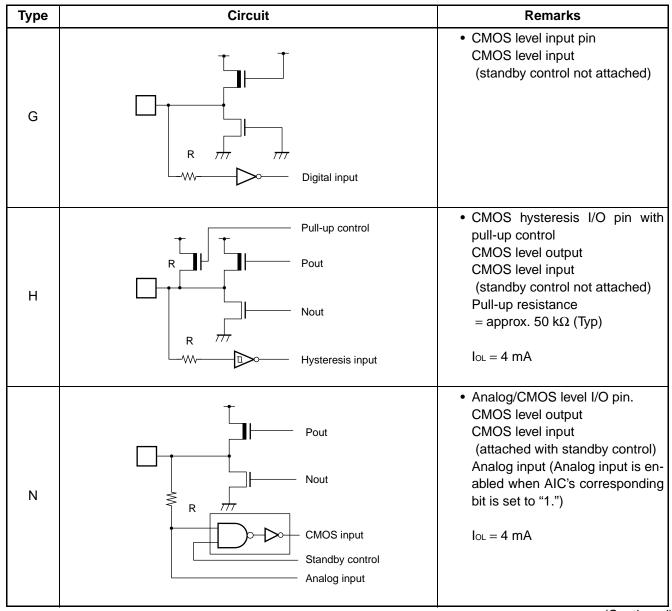

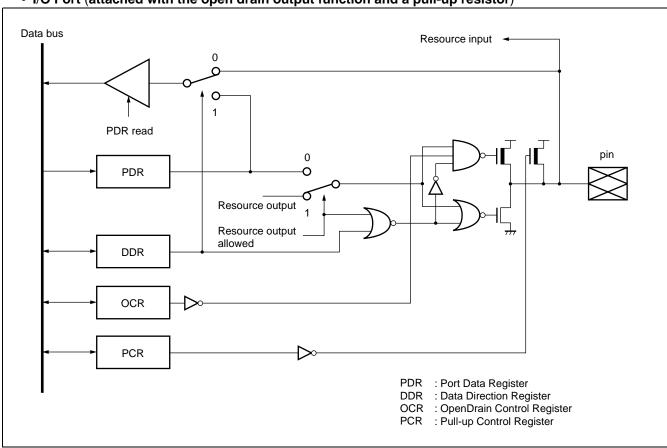

### **■ I/O CIRCUIT TYPE**

| Circuit                            | Remarks                                                                                                                                                              |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pull-up control                    | CMOS hysteresis I/O pin<br>with pull-up control<br>CMOS level output<br>CMOS hysteresis input                                                                        |

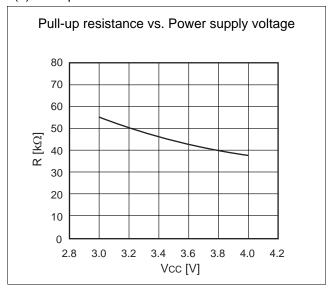

| Nout                               | (attached with standby control) Pull-up resistance = approx. 50 kΩ (Typ)                                                                                             |

| Hysteresis input                   | IoL = 4 mA                                                                                                                                                           |

| Standby control                    |                                                                                                                                                                      |

| Pull-up control                    | CMOS hysteresis I/O pin<br>with pull-up control.                                                                                                                     |

| R P Open drain control             | CMOS level output (attached with open drain control)                                                                                                                 |

| Nout R 777                         | CMOS hysteresis input (attached with standby control) Pull-up resistance                                                                                             |

| Hysteresis input                   | = approx. 50 kΩ (Typ)                                                                                                                                                |

| Standby control                    | IoL = 4 mA                                                                                                                                                           |

| Nout                               | Open drain I/O pin     5 V tolerance of voltage     CMOS hysteresis input     (attached with standby control)                                                        |

| R Hysteresis input Standby control | IoL = 15 mA                                                                                                                                                          |

|                                    | Pull-up control  Pout  Nout  Hysteresis input  Standby control  Open drain control  Nout  Hysteresis input  Standby control  Nout  Hysteresis input  Standby control |

### **■ HANDLING DEVICES**

### 1. Preventing Latchup

In CMOS ICs, applying voltage higher than  $V_{CC}$  or lower than  $V_{SS}$  to input/output pin or applying voltage over rating across  $V_{CC}$  and  $V_{SS}$  may cause latchup.

This phenomenon rapidly increases the power supply current, which may result in thermal breakdown of the device. Make sure to prevent the voltage from exceeding the maximum rating.

#### 2. Treatment of Pins

### · Treatment of unused pins

Unused pins left open may cause malfunctions. Make sure to connect them to pull-up or pull-down resistors.

### · Treatment of open pins

Be sure to use open pins in open state.

### · Treatment of output pins

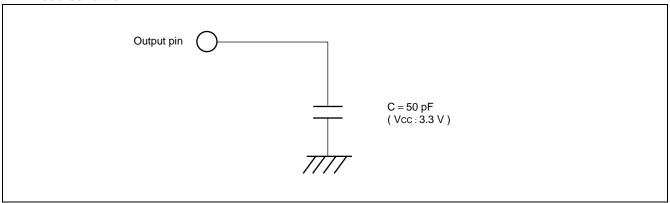

Shortcircuiting an output pin with the power supply or with another output pin or connecting a large-capacity load may causes a flow of large current. If this conditions continues for a lengthy period of time, the device deteriorates. Take great care not to exceed the absolute maximum ratings.

### • Mode pins (MD0-MD2)

These pins should be used directly connected to either Vcc or Vss. In order to prevent noise from causing accidental entry into test mode, keep the pattern length as short as possible between each mode pin and Vcc or Vss on the board and connect them with low impedance.

### · Power supply pins

When there are several Vcc and Vss pins, each of them is equipotentially connected to its counterpart inside of the device, minimizing the risk of malfunctions such as latch up. To further reduce the risk of malfunctions, to prevent EMI radiation, to prevent strobe signal malfunction resulting from creeping-up of ground level and to observe the total output current standard, connect all Vcc and Vss pins to the power supply or GND.

It is preferred to connect Vcc and Vss of MB91151A to power supply with minimal impedance possible.

It is also recommended to connect a ceramic capacitor as a bypass capacitor of about 0.1  $\mu$ F between Vcc and Vss at a position as close as possible to MB91151A.

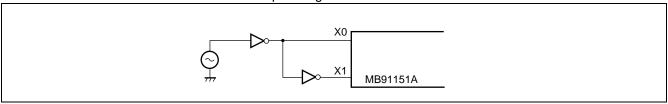

### Crystal oscillator circuit

Noises around X0 and X1 pins may cause malfunctions of MB91151A. In designing the PC board, layout X0 and X1 and crystal oscillator (or ceramic oscillator) and bypass capacitor for grounding as close as possible.

It is strongly recommended to design PC board so that X0, X1 pins are surrounded by grounding area for stable operation

### 3. Precautions

### External Reset Input

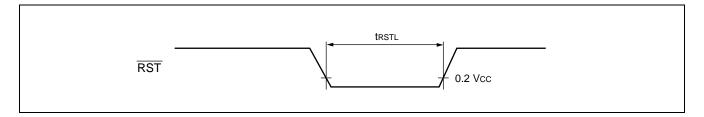

It takes at least 5 machine cycle to input "L" level to the RST pin and to ensure inner reset operation properly.

### External Clocks

When using an external clock, normally, a clock of which the phase is opposite to that of X0 must be supplied to the X0 and X1 pins simultaneously. However, when using the clock along with STOP (oscillation stopped) mode, the X1 pin stops when "H" is input in STOP mode. To prevent one output from competing against another, an external resistor of about 1  $k\Omega$  should be provided.

The following figure shows an example usage of an external clock.

An example usage of an external clock

### 4. Caution During Powering Up

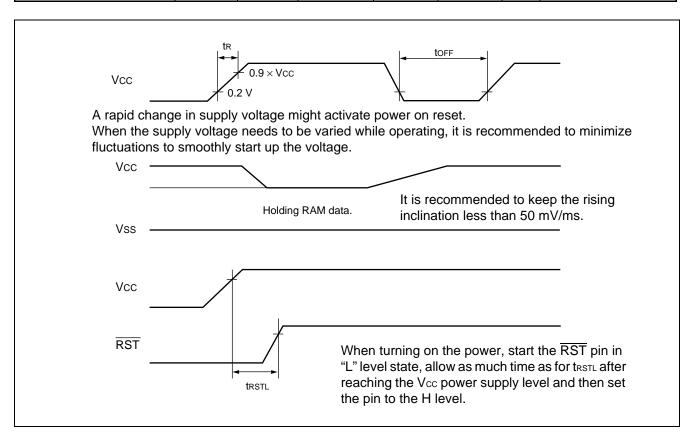

### When powering up

When turning on the power supply, never fail to start from setting the  $\overline{RST}$  pin to "L" level. And after the power supply voltage goes to Vcc level, at least after ensuring the time for 5 machine cycles, then set to "H" level.

### • Source oscillation input

At turning on the power supply, never fail to input the clock before cancellation of the oscillation stabilizing waiting.

### Power on resetting

When powering up or when turning the power back on after the supply voltage drops below the operation assurance range, be sure to reset the power.

### • Power on sequence

Turn on the power in the order of Vcc, AVcc and AVRH. The power should be disconnected in inverse order.

- Even when an AD converter is not in use, connect AVcc to the Vcc level and AVss to the Vss level.

- Even when a DA converter is not in use, connect DAVC to the Vcc level and DAVS to the Vss level.

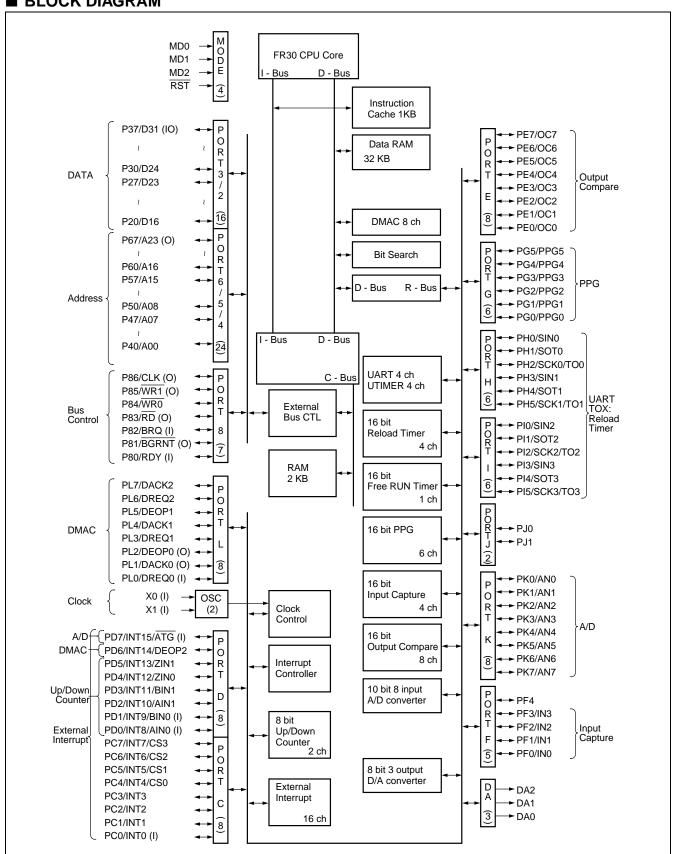

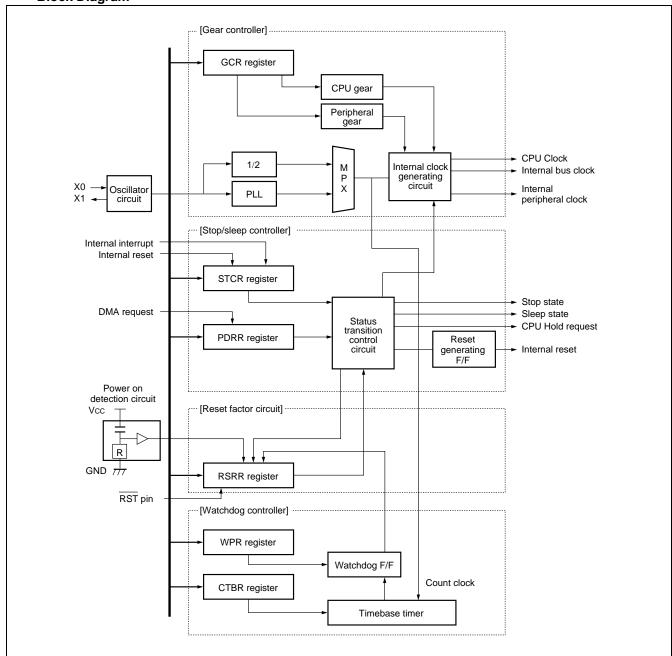

### **■ BLOCK DIAGRAM**

### **■ CPU CORE**

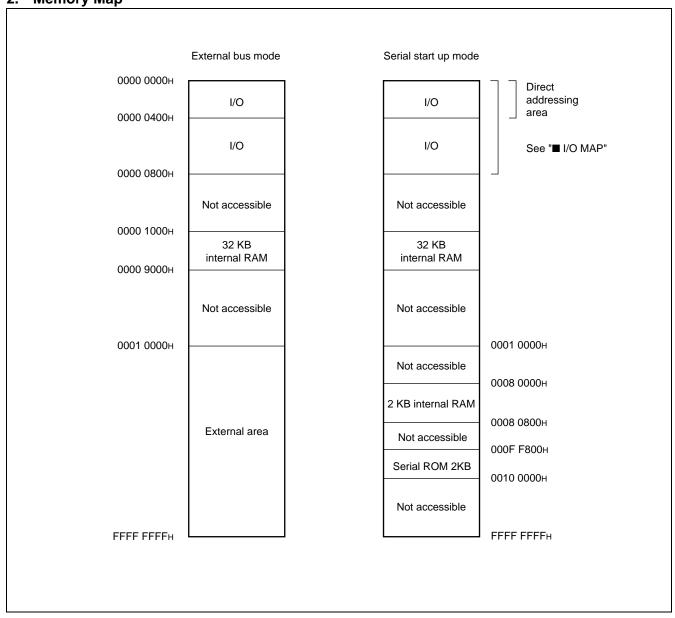

### 1. Memory Space

The FR family has a logical address space of 4 Gbytes (2<sup>32</sup> bytes) and the CPU linearly accesses the memory space.

### · Direct addressing area

The following area in the address space is used for I/O.

This area is called direct addressing area and an operand address can be specified directly in an instruction. The direct addressing area varies with the data size to be accessed as follows:

ightarrow byte data access : 000н-0FFн ightarrow half word data access : 000н-1FFн

ightarrow half word data access : 000н-1FFн ightarrow word data access : 000н-3FFн

### 2. Memory Map

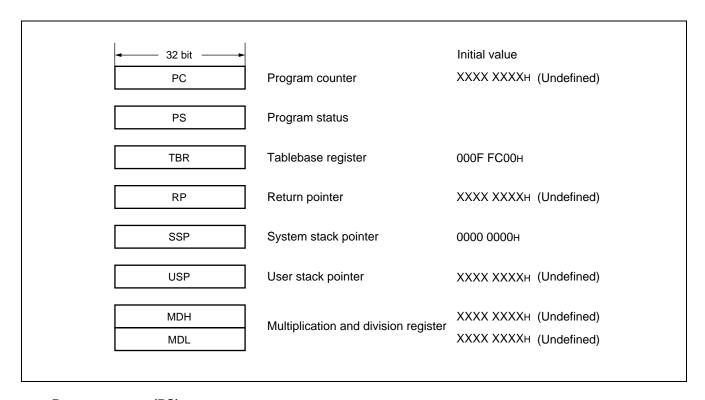

### 3. Registers

The family of FR microcontrollers has two types of registers: the registers residing in the CPU which are dedicated to applications and the general-purpose registers residing in the memory.

### • Dedicated registers :

Program counter (PC) : A 32-bit register to indicate the location where an instructions is stored.

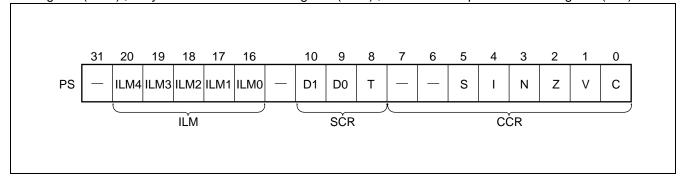

Program status (PS) : A 32-bit register to store a register pointer or a condition code.

Tablebase register (TBR) : Holds the vector table lead address used when EIT (exceptions/interrupt/

trap) is processed.

Return pointer (RP) : Holds the address to return from a subroutine.

System stack pointer (SSP) : Points to the system stack space.

User stack pointer (USP) : Points to the user stack space.

Multiplication and division result register (MDH/MDL): A 32-bit multiplication and division register.

### • Program status (PS)

The PS register holds program status and is further divided into three registers which are a Condition Code Register (CCR), a System condition Code Register (SCR), and an Interrupt Level Mask register (ILM).

### • Condition Code Register (CCR)

S flag : Designates the stack pointer for use as R15.

I flag : Controls enabling and disabling of user interrupt requests.

N flag : Indicates the sign when arithmetic operation results are considered to be an integer represented

by 2's complement.

Z flag : Indicates if arithmetic results were "0."

V flag : Considers the operand used for an arithmetic operation to be an integer represented by 2's com-

plement and indicates if the operation resulted in an overflow.

C flag : Indicates whether or not an arithmetic operation resulted in a carry or a borrow from the most sig-

nificant bit.

### • System condition Code Register (SCR)

T flag : Designates whether or not to enable step trace trap.

### • Interrupt Level Mask register (ILM)

ILM4 to ILM0 : Holds an interrupt level mask value to be used for level masking.

An interrupt request is accepted only if the corresponding interrupt level among interrupt

requests input to the CPU is higher than the value indicated by the ILM register.

| ILM4 | ILM3     | ILM2 | ILM1 | ILMO | Interrupt level | High-Low |

|------|----------|------|------|------|-----------------|----------|

| 0    | 0        | 0    | 0    | 0    | 0               | Higher   |

|      |          | 1    |      |      | :               | <b>†</b> |

| 0    | 1        | 0    | 0    | 0    | 15              |          |

|      | <u> </u> | !    |      |      | :               | ļ        |

| 1    | 1        | 1    | 1    | 1    | 31              | Lower    |

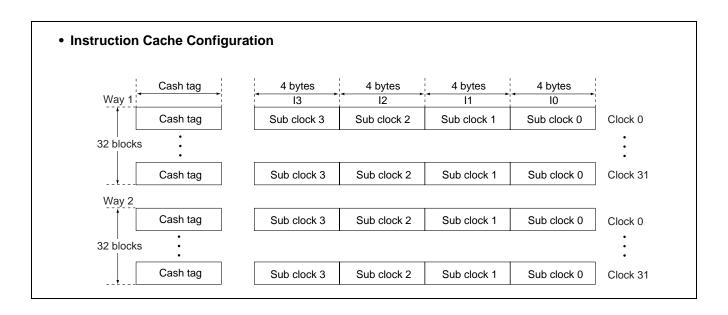

### **■** Instruction Cache

### • Description

The instruction cache is a temporary storage memory. In the event that the instruction codes are accessed from a low speed external memory, it holds the accessed codes internally, and is used to increase the access speed for all subsequent accesses.

Direct read or write access can not be done by instruction cache or instruction cache tag using software.

### • Instruction cache configuration

- Basic instruction length of FR series: 2 bytes

- Block layout: 2-way set associative type

- Block

- 1 way is configured of 32 blocks.

- 1 block is 16 bytes ( = 4 sub blocks)

- 1 sub block is 4 bytes ( = 1 bus access unit)

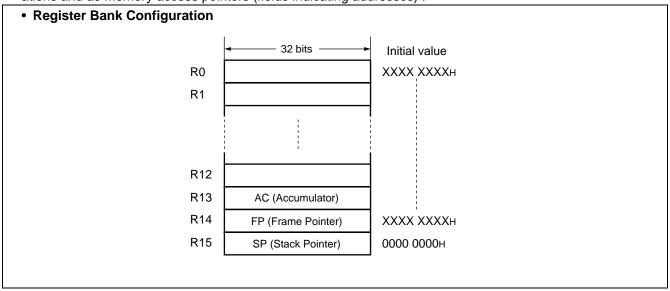

### **■ GENERAL-PURPOSE REGISTERS**

General-purpose registers are CPU registers R0 through R15 and used as accumulators during various operations and as memory access pointers (fields indicating addresses) .

Of the 16 general-purpose registers, the following registers are assumed for specific applications. For this reason, some instructions are enhanced.

R13: Virtual accumulator (AC)

R14: Frame pointer (FP)

R15 : Stack pointer (SP)

Initial values to which R0 through R14 are reset are not defined. The initial value of R15 is  $0000\ 0000 \text{H}$  (the SSP value) .

### **■ MODE SETTING**

### 1. Mode Pins

As shown below, three pins, MD2, MD1, and MD0 are used to indicate an operation.

### Mode pins and set modes

| N   | Mode pin |     | Mode name              | Reset vector                       | External data   | Bus modes                          |  |

|-----|----------|-----|------------------------|------------------------------------|-----------------|------------------------------------|--|

| MD2 | MD1      | MD0 | access area            |                                    | bus width       | bus modes                          |  |

| 0   | 0        | 0   | External vector mode 0 | External                           | 8 bits          | External bus mode                  |  |

| 0   | 0        | 1   | External vector mode 1 | External vector mode 1 External 16 |                 | External bus mode                  |  |

| 0   | 1        | 0   | External vector mode 2 | External                           | 32 bits         | Not available on this product type |  |

| 0   | 1        | 1   | External vector mode   | Internal                           | (Mode register) | Single-chip mode*                  |  |

| 1   | _        | _   | _                      | _                                  |                 | Not available                      |  |

<sup>\*:</sup> Not available on this product type

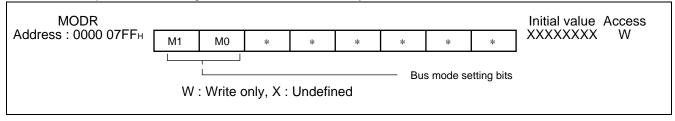

### 2. Mode Data

The data which the CPU writes to "0000 07FFH" after reset is called mode data.

It is the mode register (MODR) that exists at "0000 07FFH." Once a mode is set in this register, operations will take place in that mode. The mode register can be written only once after reset.

The mode specified in the register is enabled immediately after it is written.

[bits 7 and 6]: M1, M0

These are bus mode setting bits. Specify the bus mode to be set to after writing to the mode register.

| M1 | МО | Function                       | Remarks             |

|----|----|--------------------------------|---------------------|

| 0  | 0  | Single-chip mode               | Setting not allowed |

| 0  | 1  | Internal RAM-external bus mode |                     |

| 1  | 0  | External bus mode              |                     |

| 1  | 1  | _                              | Setting not allowed |

Note: Of the above options, only "01" or "10" should be set for this model.

[bits 5 to 0]: \*

These bits are reserved for the system.

"0" should be written to these bits at all times.

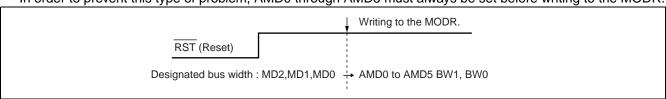

### [Precautions When Writing to the MODR]

Before writing to the MODR, be sure to set AMD0 through AMD5 and determine the bus width in each CS (Chip Select) area.

The MODR does not have bus width setting bits.

The bus width value set with mode pins MD2 through MD0 is enabled before writing to the MODR and the bus width value set with BW1 and BW0 of AMD0 through AMD5 is enabled after writing to the MODR.

For example, the external reset vector is normally executed with area 0 (the area where CS0 is active) and the bus width at that time is determined by pins MD2 through MD0. Suppose that the bus width is set to 32 or 16 bits in MD2 though MD0 but no value is specified in AMD0. If the MODR is written in this state, area 0 then switches to 8-bit bus mode and operates the bus since the initial bus width in AMD0 is set to 8 bits. This causes a malfunction.

In order to prevent this type of problem, AMD0 through AMD5 must always be set before writing to the MODR.

### ■ I/O MAP

| Address |                           | Block                             |                           |                          |                    |  |

|---------|---------------------------|-----------------------------------|---------------------------|--------------------------|--------------------|--|

| Address | +0                        | +1                                | +2                        | +3                       | - BIOCK            |  |

| 000000н | PDR3 (R/W)<br>XXXXXXXX    | PDR2 (R/W)<br>XXXXXXXX            | _                         | _                        |                    |  |

| 000004н | _                         | PDR6 (R/W)<br>XXXXXXXX            | PDR5 (R/W)<br>XXXXXXXX    | PDR4 (R/W)<br>XXXXXXXX   |                    |  |

| 000008н |                           | <u> </u>                          |                           | PDR8 (R/W)<br>- XXXXXXX  |                    |  |

| 00000Сн |                           | _                                 | _                         |                          | Port Data Register |  |

| 000010н | PDRF (R/W)<br>XXXXX       | PDRE (R/W)<br>XXXXXXXX            | PDRD (R/W)<br>XXXXXXXX    | PDRC (R/W)<br>XXXXXXXX   |                    |  |

| 000014н | PDRJ (R/W)<br>11          | PDRI (R/W)<br>XXXXXX              | PDRH (R/W)<br>XXXXXX      | PDRG (R/W)<br>XXXXXX     |                    |  |

| 000018н | _                         | _                                 | PDRL (R/W)<br>XXXXXXXX    | PDRK (R/W)<br>XXXXXXXX   | †                  |  |

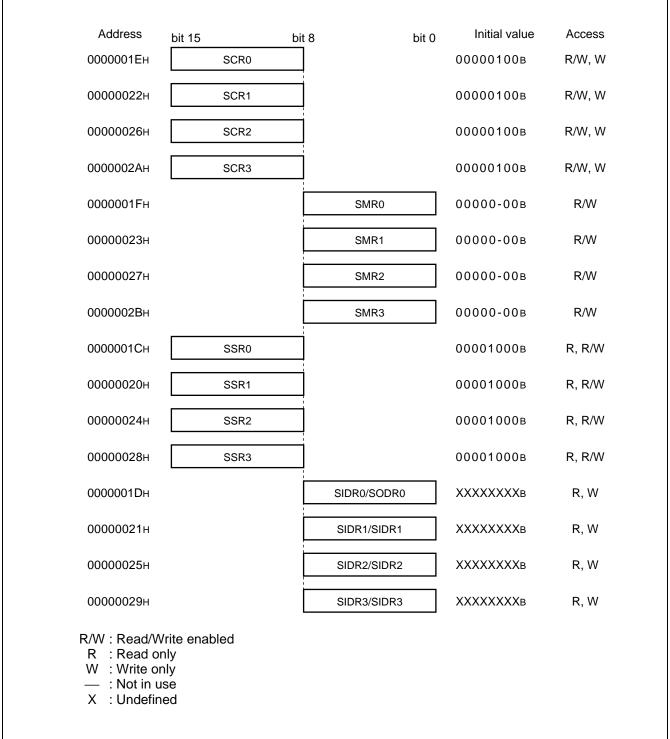

| 00001Сн | SSR0 (R, R/W)<br>00001000 | SIDR0/SODR0<br>(R, W)<br>XXXXXXXX | SCR0 (R/W, W)<br>00000100 | SMR0 (R/W)<br>00000 - 00 | UART0              |  |

| 000020н | SSR1 (R, R/W)<br>00001000 | SIDR1/SODR1<br>(R, W)<br>XXXXXXXX | SCR1 (R/W, W)<br>00000100 | SMR1 (R/W)<br>00000 - 00 | UART1              |  |

| 000024н | SSR2 (R, R/W)<br>00001000 | SIDR2/SODR2<br>(R, W)<br>XXXXXXXX | SCR2 (R/W, W)<br>00000100 | SMR2 (R/W)<br>00000 - 00 | UART2              |  |

| 000028н | SSR3 (R, R/W)<br>00001000 | SIDR3/SODR3<br>(R, W)<br>XXXXXXXX | SCR3 (R/W, W)<br>00000100 | SMR3 (R/W)<br>00000 - 00 | UART3              |  |

| 00002Сн | TMRLI<br>XXXXXXXX         | ` ,                               | TMR<br>XXXXXXX            | ` '                      | Daland Timer 0     |  |

| 000030н | _                         |                                   | TMCSR<br>0000             | 2000000                  | Reload Timer 0     |  |

| 000034н | TMRLI<br>XXXXXXXX         |                                   | TMR<br>XXXXXXX            | 1 (R)<br>XXXXXXXX        | Reload Timer 1     |  |

| 000038н | _                         | _                                 | TMCSR<br>0000             |                          | - Reidau Hiller I  |  |

| 00003Сн | TMRLI<br>XXXXXXXX         |                                   | TMR<br>XXXXXXX            | 2 (R)<br>XXXXXXXX        | Reload Timer 2     |  |

| 000040н | _                         | _                                 | TMCSR<br>0000             |                          | Reidad Hitter 2    |  |

| A alal # 0 0 0           |                                                | Block                       |                                    |                           |                       |  |

|--------------------------|------------------------------------------------|-----------------------------|------------------------------------|---------------------------|-----------------------|--|

| Address                  | +0                                             | +1                          | +2                                 | +3                        | - BIOCK               |  |

| 000044н                  | TMRLR3 (W) TMR3 (R) XXXXXXXX XXXXXXXX XXXXXXXX |                             |                                    | Reload Timer 3            |                       |  |

| 000048н                  | _                                              | _                           | TMCSR<br>0000                      | 3 (R/W)<br>00000000       | Reload Timer 5        |  |

| 00004Сн                  | CDCR1 (R/W)<br>0 0000                          | _                           | CDCR0 (R/W)<br>0 0000              | _                         | Communications        |  |

| 000050н                  | CDCR3 (R/W)<br>0 0000                          | _                           | CDCR2 (R/W)<br>0 0000              | _                         | prescaler 1           |  |

| 000054н<br>to<br>000058н |                                                | -                           | _                                  |                           | Reserved              |  |

| 00005Сн                  | RCR1 (W)<br>00000000                           | RCR0 (W)<br>00000000        | UDCR1 (R)<br>00000000              | UDCR0 (R)<br>00000000     |                       |  |

| 000060н                  | CCRH0 (R/W)<br>00000000                        | CCRL0 (R/W, W)<br>- 000X000 |                                    | CSR0 (R/W, R)<br>00000000 | 8/16 bit U/D Counter  |  |

| 000064н                  | CCRH1 (R/W)<br>- 0000000                       | CCRL1 (R/W, W)<br>- 000X000 |                                    | CSR1 (R/W, R)<br>00000000 |                       |  |

| 000068н                  | IPCP<br>XXXXXXXX                               | 1 (R)<br>XXXXXXXX           | IPCP<br>XXXXXXXX                   | 0 (R)<br>XXXXXXXX         |                       |  |

| 00006Сн                  | IPCP<br>XXXXXXXX                               | 3 (R)<br>XXXXXXXX           | IPCP<br>XXXXXXXX                   | 2 (R)<br>XXXXXXXX         | 16 bit ICU            |  |

| 000070н                  | _                                              | ICS23 (R/W)<br>00000000     |                                    | ICS01 (R/W)<br>00000000   |                       |  |

| 000074н                  |                                                | I (R/W)<br>XXXXXXX          | OCCP(<br>XXXXXXXX                  | O (R/W)<br>XXXXXXXX       |                       |  |

| 000078н                  | OCCP3<br>XXXXXXXX                              | 3 (R/W)<br>XXXXXXXX         | OCCP2<br>XXXXXXXX                  | 2 (R/W)<br>XXXXXXXX       |                       |  |

| 00007Сн                  | OCCP5<br>XXXXXXXX                              | 5 (R/W)<br>XXXXXXXX         | OCCP4<br>XXXXXXXX                  | 4 (R/W)<br>XXXXXXXX       | - 16 bit OCU          |  |

| 000080н                  |                                                | 7 (R/W)<br>XXXXXXXX         |                                    | 6 (R/W)<br>XXXXXXXX       | 10 811 000            |  |

| 000084н                  |                                                | 3 (R/W)<br>0000XX00         |                                    | 1 (R/W)<br>0000XX00       |                       |  |

| 000088н                  | OCS6,<br>XXX00000                              | 7 (R/W)<br>0000XX00         | OCS4, 5 (R/W)<br>XXX00000 0000XX00 |                           |                       |  |

| 00008Сн                  | TCDT<br>00000000                               |                             | TCCS<br>0                          | (R/W)<br>00000000         | 16 bit Freerun Timer  |  |

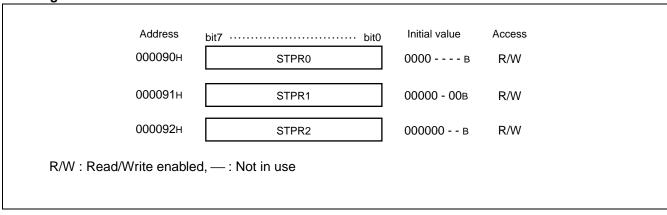

| 000090н                  | STPR0 (R/W)<br>0000                            | STPR1 (R/W)<br>00000 - 00   | STPR2 (R/W)<br>000000              | _                         | Stop Register 0, 1, 2 |  |

| 000094н                  | GCN1<br>00110010                               |                             | _                                  | GCN2 (R/W)<br>00000000    | PPG ctl               |  |

| Address                  |                               | Block                   |                            |                               |                                 |  |

|--------------------------|-------------------------------|-------------------------|----------------------------|-------------------------------|---------------------------------|--|

| Address                  | +0                            | +1                      | +2                         | +3                            | BIOCK                           |  |

| 000098н                  | PTMF<br>11111111              |                         |                            | PCSR0 (W)<br>XXXXXXXX XXXXXXX |                                 |  |

| 00009Сн                  | PDUT<br>XXXXXXXX              | O (W)<br>XXXXXXXX       | PCNH0 (R/W)<br>0000000 -   | PCNL0 (R/W)<br>00000000       | - PPG0                          |  |

| 0000А0н                  | PTMF<br>11111111              |                         | PCSR<br>XXXXXXXX           |                               | PPG1                            |  |

| 0000А4н                  | PDUT<br>XXXXXXXX              | 1 (W)<br>XXXXXXXX       | PCNH1 (R/W)<br>0000000 -   | PCNL1 (R/W)<br>00000000       | - PPG1                          |  |

| 0000А8н                  | PTMF<br>11111111              | R2 (R)<br>11111111      | PCSR<br>XXXXXXXX           |                               | PPG2                            |  |

| 0000АСн                  | PDUT2 (W)<br>XXXXXXXX XXXXXXX |                         | PCNH2 (R/W)<br>0000000 -   | PCNL2 (R/W)<br>00000000       | FFG2                            |  |

| 0000В0н                  | PTMF<br>11111111              |                         | PCSR<br>XXXXXXXX           |                               | PPG3                            |  |

| 0000В4н                  | PDUT<br>XXXXXXX               | 3 (W)<br>XXXXXXX        | PCNH3 (R/W)<br>0000000 -   | PCNL3 (R/W)<br>00000000       | 7                               |  |

| 0000В8н                  | PTMF<br>11111111              | R4 (R)<br>11111111      | PCSR<br>XXXXXXXX           | ` '                           | PPG4                            |  |

| 0000ВСн                  | PDUT<br>XXXXXXXX              | 4 (W)<br>XXXXXXXX       | PCNH4 (R/W)<br>0000000 -   | PCNL4 (R/W)<br>00000000       | FFG4                            |  |

| 0000С0н                  | PTMF<br>11111111              |                         | PCSR<br>XXXXXXXX           |                               | PPG5                            |  |

| 0000С4н                  | PDUT<br>XXXXXXXX              |                         | PCNH5 (R/W)<br>0000000 -   | PCNL5 (R/W)<br>00000000       | 7 7793                          |  |

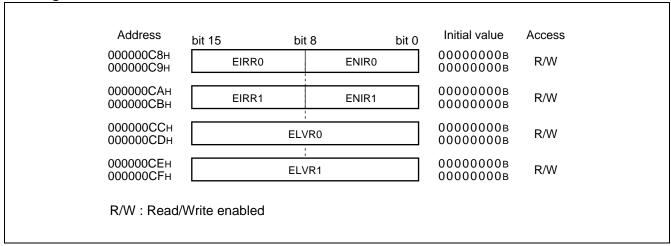

| 0000С8н                  | EIRR0 (R/W)<br>00000000       | ENIR0 (R/W)<br>00000000 | EIRR1 (R/W)<br>00000000    | ENIR1 (R/W)<br>00000000       | Ext int                         |  |

| 0000ССн                  | ELVR0<br>00000000             | ` ,                     | ELVR1<br>00000000          |                               | - EXTIII                        |  |

| 0000D0н<br>to<br>0000D8н |                               | -                       | _                          |                               | Reserved                        |  |

| 0000DСн                  | _                             | DACR2 (R/W)             | DACR1 (R/W)                | DACR0 (R/W)                   | D/A Conventor                   |  |

| 0000Е0н                  | _                             | DADR2 (R/W)<br>XXXXXXXX | DADR1 (R/W)<br>XXXXXXXX    | DADR0 (R/W)<br>XXXXXXXX       | D/A Converter                   |  |

| 0000Е4н                  | ADCR<br>00101- XX             | (R, W)<br>XXXXXXX       | ADCS1 (R/W, W)<br>00000000 | ADCS0 (R/W)<br>00000000       | A/D Converter (Sequential type) |  |

| 0000Е8н                  |                               | _                       |                            | AICK (R/W)<br>00000000        | Analog Input Control            |  |

| 0000ECн<br>to<br>0000F0н |                               | -                       | _                          |                               | Reserved                        |  |

| Address                  |                      | Disale                    |                             |                        |                              |  |

|--------------------------|----------------------|---------------------------|-----------------------------|------------------------|------------------------------|--|

| Address                  | +0                   | +1                        | +2                          | +3                     | Block                        |  |

| 0000F4н                  | PCRI (R/W)<br>000000 | PCRH (R/W)<br>000000      | PCRD (R/W)<br>00000000      | PCRC (R/W)<br>00000000 | Pull Up Control              |  |

| 0000F8н                  | OCRI (R/W)<br>000000 | OCRH (R/W)<br>000000      | _                           | _                      |                              |  |

| 0000FСн                  | DDRF (R/W)<br>00000  | DDRE (R/W)<br>00000000    | DDRD (R/W)<br>00000000      | DDRC (R/W)<br>00000000 |                              |  |

| 000100н                  | _                    | DDRI (R/W)<br>- 0000000   | DDRH (R/W)<br>000000        | DDRG (R/W)<br>000000   | Data Direction Reg-<br>ister |  |

| 000104н                  | _                    | _                         | DDRL (R/W)<br>00000000      | DDRK (R/W)<br>00000000 |                              |  |

| 000108н<br>to<br>0001FCн |                      | _                         | _                           | Reserved               |                              |  |

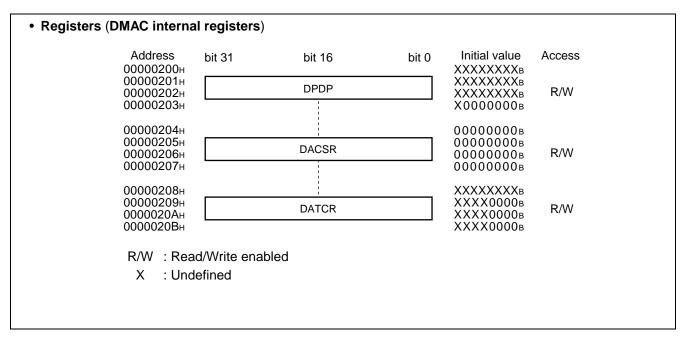

| 000200н                  |                      | DPDP (R/W)<br>0000000     |                             |                        |                              |  |

| 000204н                  | 0                    | DACSF<br>0000000 00000000 | R (R/W)<br>00000000 0000000 | 00                     | DMAC                         |  |

| 000208н                  | XXX                  |                           |                             |                        |                              |  |

| 00020Сн<br>to<br>0003Е0н |                      | Reserved                  |                             |                        |                              |  |

| 0003Е4н                  | ICHCR (R/W)          |                           |                             |                        | Instruction cache            |  |

| 0003E8н<br>to<br>0003EСн |                      | Reserved                  |                             |                        |                              |  |

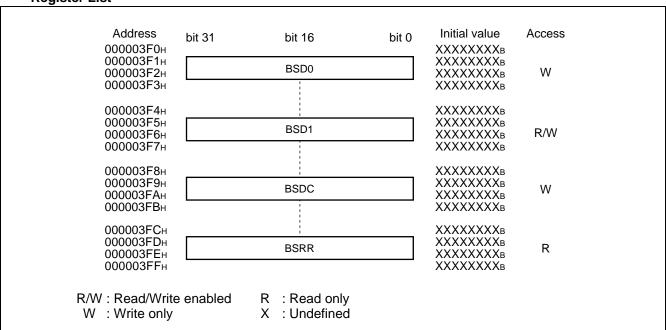

| 0003F0н                  | XXXX                 | BSD(<br>XXXXX XXXXXXX     | 0 (W)<br>XXXXXXXX XXXX      | xxxx                   |                              |  |

| 0003Е4н                  | XXXX                 | BSD1<br>XXXXX XXXXXXX     | (R/W)<br>XXXXXXXX XXXX      | XXXX                   | Dit Cooreb Module            |  |

| 0003F8н                  | XXX>                 | BSD(<br>XXXXX XXXXXXXX    | C (W)<br>XXXXXXXX XXXX      | XXXX                   | Bit Search Module            |  |

| 0003FСн                  | XXXX                 | BSR<br>XXXXX XXXXXXX      | R (R)<br>XXXXXXXX XXXX      | XXXX                   |                              |  |

| Adduses                  |                                 | Dlack                   |                     |                      |                        |

|--------------------------|---------------------------------|-------------------------|---------------------|----------------------|------------------------|

| Address                  | +0                              | +1                      | +2                  | +3                   | Block                  |

| 000400н                  | ICR00 (R/W)<br>1111             | ICR01 (R/W)<br>1111     | ICR02 (R/W)<br>1111 | ICR03 (R/W)<br>1111  |                        |

| 000404н                  | ICR04 (R/W)<br>1111             | ICR05 (R/W)<br>1111     | ICR06 (R/W)<br>1111 | ICR07 (R/W)<br>1111  | 1                      |

| 000408н                  | ICR08 (R/W)<br>1111             | ICR09 (R/W)<br>1111     | ICR10 (R/W)<br>1111 | ICR11 (R/W)<br>1111  | 1                      |

| 00040Сн                  | ICR12 (R/W)<br>1111             | ICR13 (R/W)<br>1111     | ICR14 (R/W)<br>1111 | ICR15 (R/W)<br>1111  |                        |

| 000410н                  | ICR16 (R/W)                     | ICR17 (R/W)             | ICR18 (R/W)<br>1111 | ICR19 (R/W)          |                        |

| 000414н                  | ICR20 (R/W)                     | ICR21 (R/W)<br>1111     | ICR22 (R/W)<br>1111 | ICR23 (R/W)<br>1111  | 1                      |

| 000418н                  | ICR24 (R/W)<br>1111             | ICR25 (R/W)<br>1111     | ICR26 (R/W)<br>1111 | ICR27 (R/W)<br>1111  | Interrupt Control unit |

| 00041Сн                  | ICR28 (R/W)<br>1111             | ICR29 (R/W)<br>1111     | ICR30 (R/W)         | ICR31 (R/W)          |                        |

| 000420н                  | ICR32 (R/W)                     | ICR33 (R/W)             | ICR34 (R/W)<br>1111 | ICR35 (R/W)          |                        |

| 000424н                  | ICR36 (R/W)<br>1111             | ICR37 (R/W)             | ICR38 (R/W)<br>1111 | ICR39 (R/W)<br>1111  |                        |

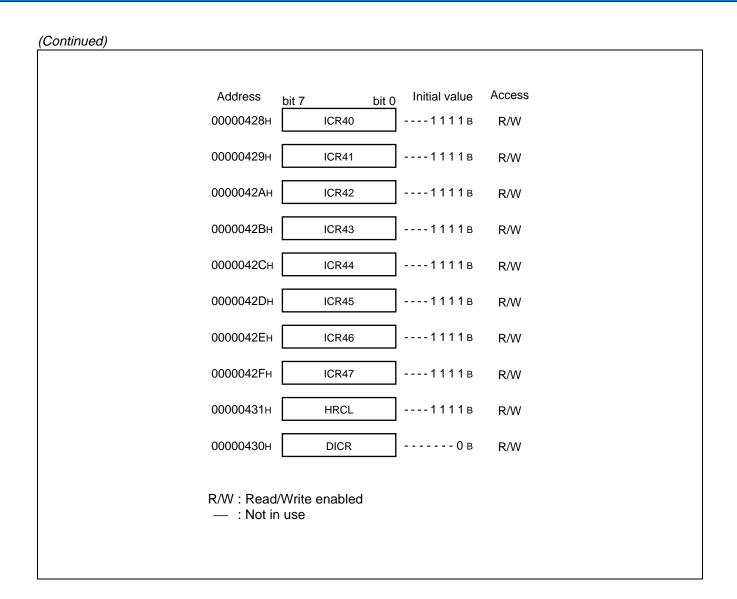

| 000428н                  | ICR40 (R/W)<br>1111             | ICR41 (R/W)<br>1111     | ICR42 (R/W)<br>1111 | ICR43 (R/W)<br>1111  |                        |

| 00042Сн                  | ICR44 (R/W)<br>1111             | ICR45 (R/W)<br>1111     | ICR46 (R/W)<br>1111 | ICR47 (R/W)<br>1111  |                        |

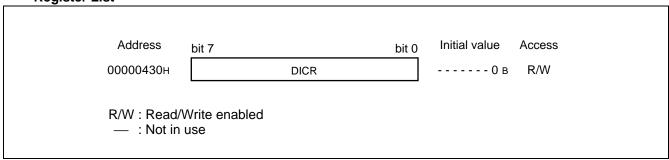

| 000430н                  | DICR (R/W)                      | HRCL (R/W)<br>1111      | _                   | _                    | Delay int              |

| 000434н<br>to<br>00047Сн |                                 | _                       | _                   |                      | Reserved               |

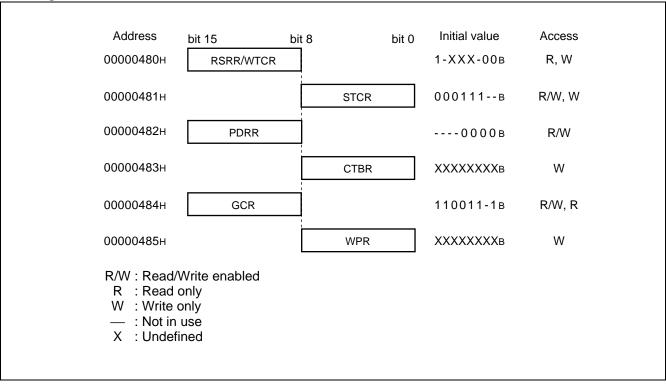

| 000480н                  | RSRR/WTCR<br>(R, W)<br>1-XXX-00 | STCR (R/W, W)<br>000111 | PDRR (R/W)<br>0000  | CTBR (W)<br>XXXXXXXX | Clock Control unit     |

| 000484н                  | GCR (R/W, R)<br>110011-1        | WPR (W)<br>XXXXXXXX     | _                   | _                    |                        |

| 000488н                  | PTCR (R/W)<br>00XX0XXX          |                         | _                   | PLL Control          |                        |

| 00048Сн<br>to<br>0005FСн |                                 | _                       | _                   |                      | Reserved               |

(Continued)

| Address                  |                       | Block                  |                         |                       |                                            |

|--------------------------|-----------------------|------------------------|-------------------------|-----------------------|--------------------------------------------|

| Address                  | +0                    | +1                     | +2                      | +3                    | DIOCK                                      |

| 000600н                  | DDR3 (W)<br>00000000  | DDR2 (W)<br>00000000   | _                       | _                     |                                            |

| 000604н                  | _                     | DDR6 (W)<br>00000000   | DDR5 (W)<br>00000000    | DDR4 (W)<br>00000000  | Data Direction<br>Register                 |

| 000608н                  |                       | _                      |                         | DDR8 (W)<br>- 0000000 |                                            |

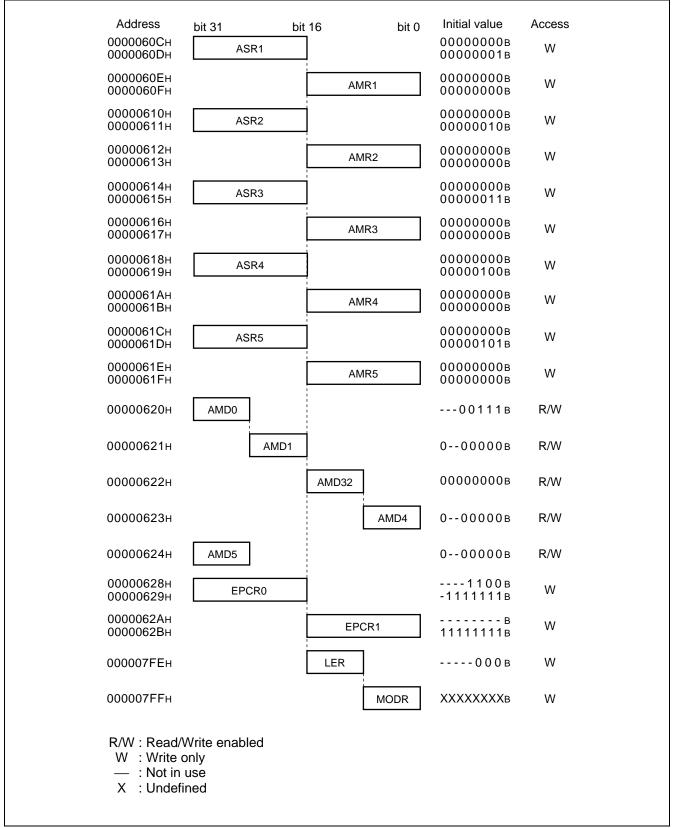

| 00060Сн                  | ASR<br>00000000       |                        | AMR<br>00000000         |                       |                                            |

| 000610н                  | ASR:<br>00000000      |                        | AMR:<br>00000000        |                       |                                            |

| 000614н                  | ASR:<br>00000000      |                        | AMR:<br>00000000        |                       | T-unit                                     |

| 000618н                  | ASR/<br>00000000      |                        | AMR-<br>00000000        |                       |                                            |

| 00061Сн                  | ASR:<br>00000000      |                        | AMR:<br>00000000        |                       | 1-unit                                     |

| 000620н                  | AMD0 (R/W)<br>00111   | AMD1 (R/W)<br>0 00000  | AMD32 (R/W)<br>00000000 | AMD4 (R/W)<br>0 00000 |                                            |

| 000624н                  | AMD5 (R/W)<br>0 00000 |                        | _                       |                       |                                            |

| 000628н                  | EPCR<br>1100          | 0 (W)<br>-1111111      | EPCR                    |                       |                                            |

| 00062Сн                  |                       | -                      | _                       |                       | Reserved                                   |

| 000630н                  | _                     | PCR6 (R/W)<br>00000000 | _                       |                       | Pull Up Control                            |

| 000634н<br>to<br>0007F8н |                       | _                      | _                       | Reserved              |                                            |

| 0007FСн                  | _                     | _                      | LER (W)                 | MODR (W)<br>XXXXXXXX  | Little Endian<br>Register<br>Mode Register |

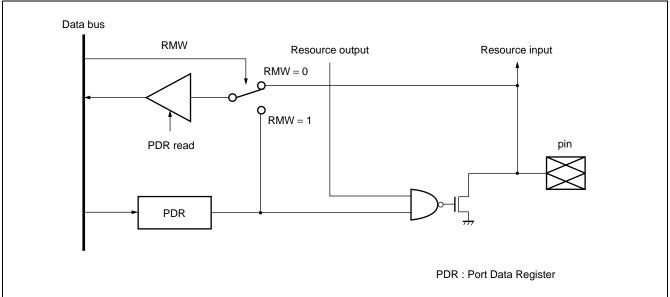

Note: Do not execute RMW instructions on registers having a write-only bit.

RMW instructions (RMW : Read Modify Write)

AND EOR Rj, @Ri Rj, @Ri OR Rj, @Ri ANDH Rj, @Ri ORH Rj, @Ri **EORH** Rj, @Ri ANDB Rj, @Ri ORB Rj, @Ri **EORB** Rj, @Ri BANDL #u4, @Ri BORL #u4, @Ri BEORL #u4, @Ri BANDH #u4, @Ri BORH #u4, @Ri BEORH #u4, @Ri

Data is undefined in "Reserved" or (—) areas.

(): Access

R/W: Read/Write enabled

R: Read only

W: Write only

Not in use

X: Undefined

### ■ INTERRUPT FACTORS AND ASSIGNMENT OF INTERRUPT VECTORS AND RESISTERS

| Footor                          | Interru | Interrupt No. |                    | Offers | Default TBR |

|---------------------------------|---------|---------------|--------------------|--------|-------------|

| Factor                          | Decimal | Hex.          | Interrupt<br>level | Offset | address     |

| Reset                           | 0       | 00            | _                  | 3FСн   | 000FFFCн    |

| Reserved for the system         | 1       | 01            | _                  | 3F8н   | 000FFFF8н   |

| Reserved for the system         | 2       | 02            | _                  | 3F4н   | 000FFFF4н   |

| Reserved for the system         | 3       | 03            | _                  | 3F0н   | 000FFF0н    |

| Reserved for the system         | 4       | 04            | _                  | 3ЕСн   | 000FFFECн   |

| Reserved for the system         | 5       | 05            | _                  | 3Е8н   | 000FFFE8н   |

| Reserved for the system         | 6       | 06            | _                  | 3Е4н   | 000FFFE4н   |

| Reserved for the system         | 7       | 07            | _                  | 3Е0н   | 000FFFE0н   |

| Reserved for the system         | 8       | 08            | _                  | 3DСн   | 000FFFDCн   |

| Reserved for the system         | 9       | 09            | _                  | 3D8н   | 000FFFD8н   |

| Reserved for the system         | 10      | 0A            | _                  | 3D4н   | 000FFFD4н   |

| Reserved for the system         | 11      | 0B            | _                  | 3D0н   | 000FFFD0н   |

| Reserved for the system         | 12      | 0C            | _                  | 3ССн   | 000FFFCCн   |

| Reserved for the system         | 13      | 0D            | _                  | 3С8н   | 000FFFC8н   |

| Undefined instruction exception | 14      | 0E            | _                  | 3С4н   | 000FFFC4н   |

| Reserved for the system         | 15      | 0F            | _                  | 3С0н   | 000FFFC0н   |

| External interrupt 0            | 16      | 10            | ICR00              | 3ВСн   | 000FFFBCн   |

| External interrupt 1            | 17      | 11            | ICR01              | 3В8н   | 000FFFB8н   |

| External interrupt 2            | 18      | 12            | ICR02              | 3В4н   | 000FFFB4н   |

| External interrupt 3            | 19      | 13            | ICR03              | 3В0н   | 000FFFB0н   |

| External interrupt 4            | 20      | 14            | ICR04              | 3АСн   | 000FFFACн   |

| External interrupt 5            | 21      | 15            | ICR05              | 3А8н   | 000FFFA8н   |

| External interrupt 6            | 22      | 16            | ICR06              | 3А4н   | 000FFFA4н   |

| External interrupt 7            | 23      | 17            | ICR07              | 3А0н   | 000FFFA0н   |

| External interrupts 8 to 15     | 24      | 18            | ICR08              | 39Сн   | 000FFF9Сн   |

| Reserved for the system         | 25      | 19            | _                  | 398н   | 000FFF98н   |

| UART0 (receiving complete)      | 26      | 1A            | ICR10              | 394н   | 000FFF94н   |

| UART1 (receiving complete)      | 27      | 1B            | ICR11              | 390н   | 000FFF90н   |

| UART2 (receiving complete)      | 28      | 1C            | ICR12              | 38Сн   | 000FFF8Сн   |

| UART3 (receiving complete)      | 29      | 1D            | ICR13              | 388н   | 000FFF88н   |

| Reserved for the system         | 30      | 1E            | _                  | 384н   | 000FFF84н   |

| UART0 (sending complete)        | 31      | 1F            | ICR15              | 380н   | 000FFF80н   |

| UART1 (sending complete)        | 32      | 20            | ICR16              | 37Сн   | 000FFF7Сн   |

| UART2 (sending complete)        | 33      | 21            | ICR17              | 378н   | 000FFF78н   |

| Factor                                                              | Interrupt No. |      | Interrupt | 0" 1   | Default TBR |

|---------------------------------------------------------------------|---------------|------|-----------|--------|-------------|

| Factor                                                              | Decimal       | Hex. | level     | Offset | address     |

| UART3 (sending complete)                                            | 34            | 22   | ICR18     | 374н   | 000FFF74н   |

| System reservation                                                  | 35            | 23   | _         | 370н   | 000FFF70н   |

| DMAC (End, Error)                                                   | 36            | 24   | ICR20     | 36Сн   | 000FFF6Сн   |

| Reload timer 0                                                      | 37            | 25   | ICR21     | 368н   | 000FFF68н   |

| Reload timer 1                                                      | 38            | 26   | ICR22     | 364н   | 000FFF64н   |

| Reload timer 2                                                      | 39            | 27   | ICR23     | 360н   | 000FFF60н   |

| Reload timer 3                                                      | 40            | 28   | ICR24     | 35Сн   | 000FFF5Сн   |

| A/D (sequential type)                                               | 42            | 2A   | ICR26     | 354н   | 000FFF54н   |

| PPG0                                                                | 43            | 2B   | ICR27     | 350н   | 000FFF50н   |

| PPG1                                                                | 44            | 2C   | ICR28     | 34Сн   | 000FFF4Сн   |

| PPG2                                                                | 45            | 2D   | ICR29     | 348н   | 000FFF48н   |

| PPG3                                                                | 46            | 2E   | ICR30     | 344н   | 000FFF44н   |

| PPG4                                                                | 47            | 2F   | ICR31     | 340н   | 000FFF40н   |

| PPG5                                                                | 48            | 30   | ICR32     | 33Сн   | 000FFF3Сн   |