# 16-bit Proprietary Microcontroller

**CMOS**

# F<sup>2</sup>MC-16L MB90670/675 Series

# MB90671/672/673/T673/P673 (MB90670 Series) MB90676/677/678/T678/P678 (MB90675 Series)

### **■** DESCRIPTION

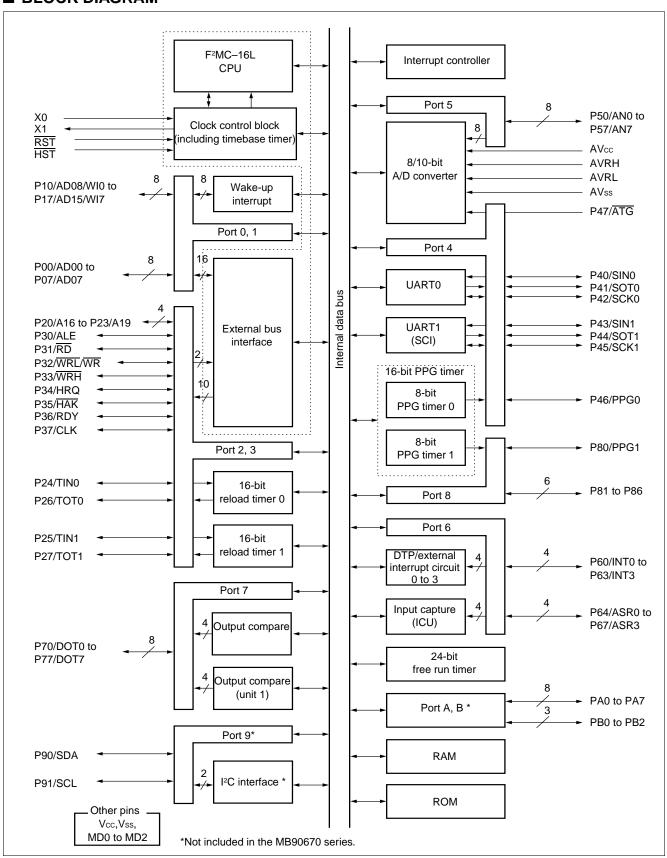

The MB90670/675 series is a member of 16-bit proprietary single-chip microcontroller F<sup>2</sup>MC\*<sup>1</sup>-16L family designed to be combined with an ASIC (Application Specific IC) core. The MB90670/675 series is a high-performance general-purpose 16-bit microcontroller for high-speed real-time processing in various industrial equipment, OA equipment, and process control.

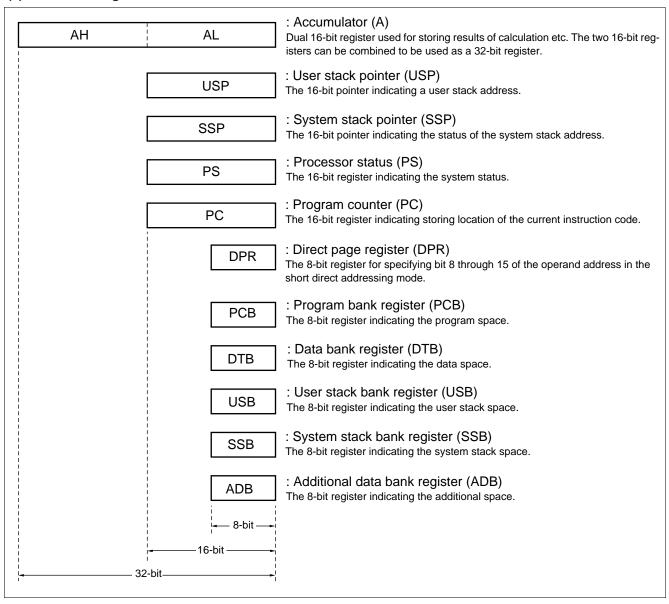

The instruction set of F<sup>2</sup>MC-16L CPU core inherits AT architecture of F<sup>2</sup>MC-8 family with additional instruction sets for high-level languages, extended addressing mode, enhanced multiplication/division instructions, and enhanced bit manipulation instructions. The microcontroller has a 32-bit accumulator for processing long word data (32-bit).

The MB90670/675 series has peripheral resources of UART0, UART1(SCI), an 8/10-bit A/D converter, an 8/16-bit PPG timer, a 16-bit reload timer, a 24-bit free run timer, an output compare (OCU), an input capture (ICU), DTP/external interrupt circuit, an I<sup>2</sup>C\*<sup>2</sup> interface (in MB90675 series only). Embedded peripheral resources performs data transmission with an intelligent I/O service function without the intervention of the CPU, enabling real-time control in various applications.

- \*1: F2MC stands for FUJITSU Flexible Microcontroller.

- \*2: Purchase of Fujitsu I<sup>2</sup>C components conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

### ■ PACKAGES

#### **■ FEATURES**

Clock

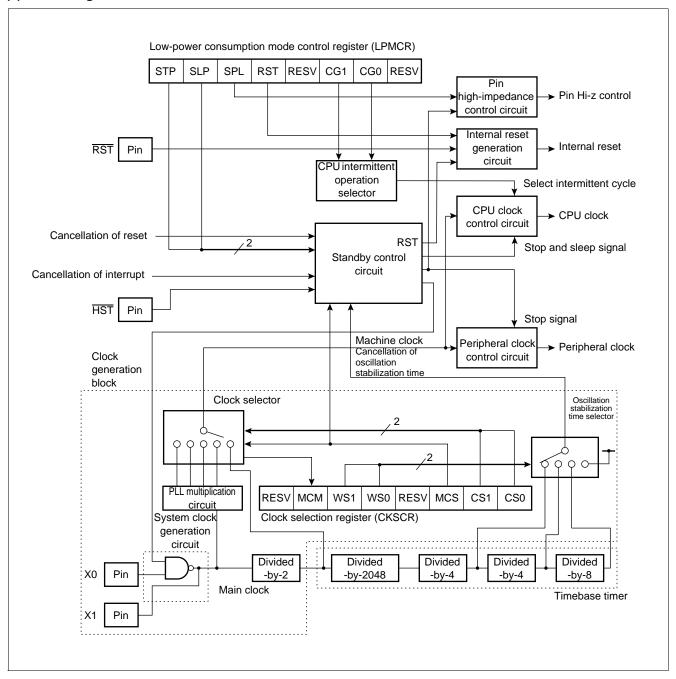

Embedded PLL clock multiplication circuit

Operating clock (PLL clock) can be selected from divided-by-2 of oscillation or one to four times the oscillation (at oscillation of 4 MHz, 4 MHz to 16 MHz).

Minimum instruction execution time of 62.5 ns (at oscillation of 4 MHz, four times the PLL clock, operation at Vcc of 5.0 V)

CPU addressing space of 16 Mbytes

Internal addressing of 24-bit

External accessing can be performed by selecting 8/16-bit bus width (external bus mode)

• Instruction set optimized for controller applications

Rich data types (bit, byte, word, long word)

Rich addressing mode (23 types)

High code efficiency

Enhanced precision calculation realized by the 32-bit accumulator

Instruction set designed for high level language (C) and multi-task operations

Adoption of system stack pointer

Enhanced pointer indirect instructions

Barrel shift instructions

Enhanced execution speed

4-byte instruction queue

• Enhanced interrupt function

8 levels, 32 factors

Automatic data transmission function independent of CPU operation

Extended intelligent I/O service function (EI<sup>2</sup>OS)

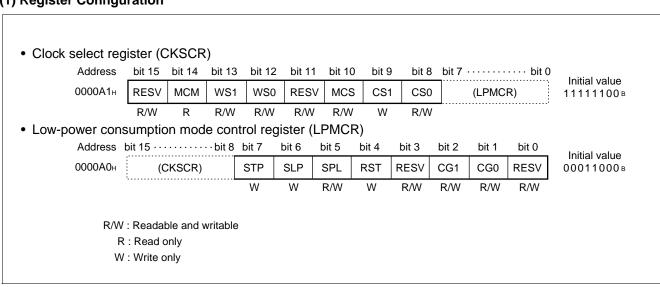

• Low-power consumption (standby) mode

Sleep mode (mode in which CPU operating clock is stopped)

Timebase timer mode (mode in which other than oscillation and timebase timer are stopped)

Stop mode (mode in which oscillation is stopped)

CPU intermittent operation mode

Hardware standby mode

Process

CMOS technology

• I/O port

MB90670 series: Maximum of 65 ports MB90675 series: Maximum of 84 ports

• Timer

Timebase timer/watchdog timer: 1 channel

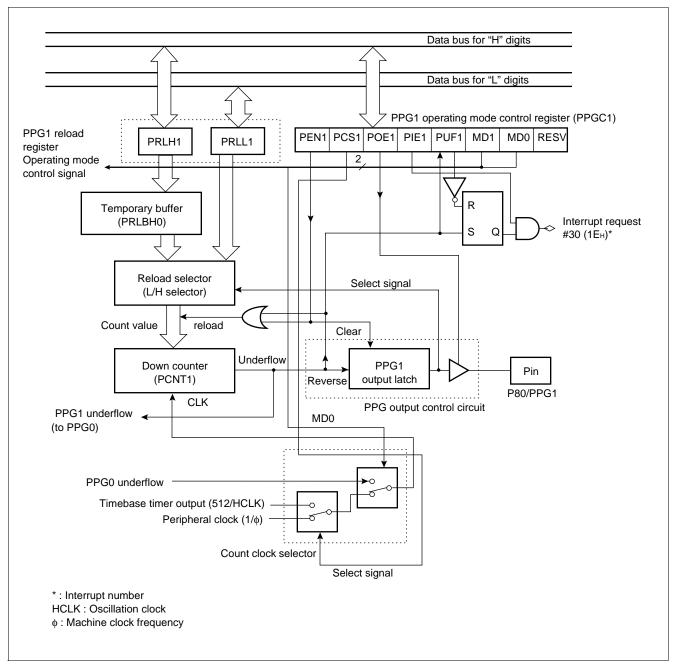

8/16-bit PPG timer: 8-bit  $\times$  2 channels or 16-bit  $\times$  1 channel

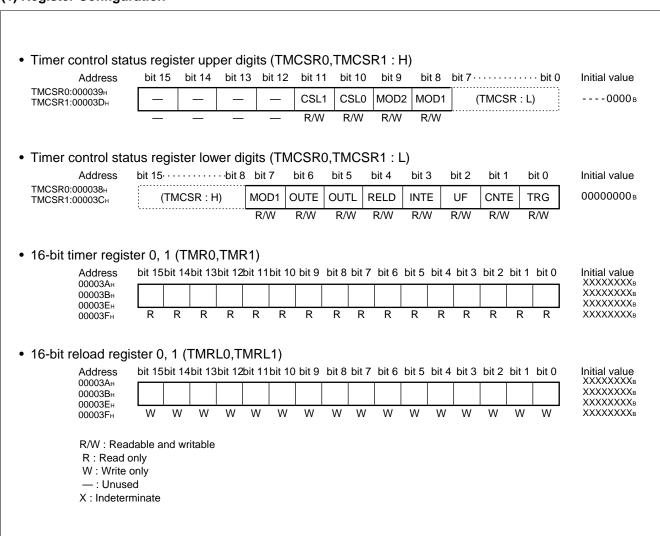

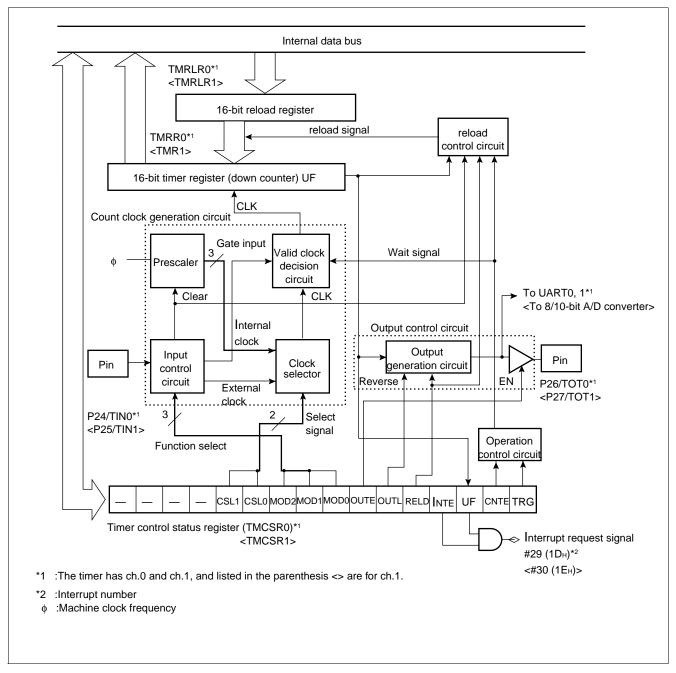

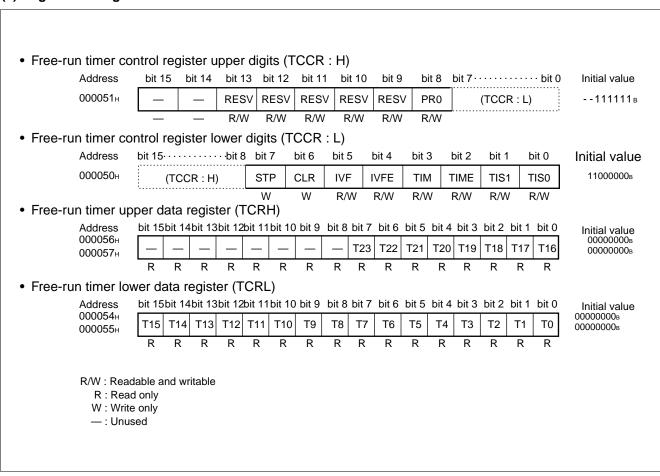

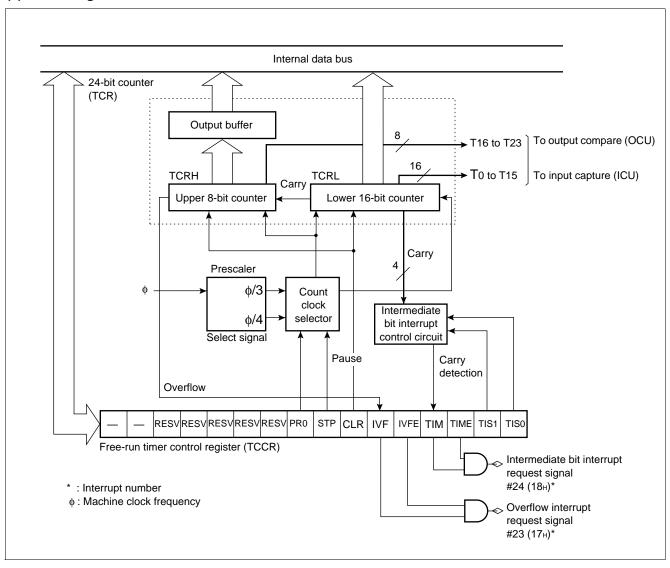

16-bit reload timer: 2 channels 24-bit free run timer: 1 channel

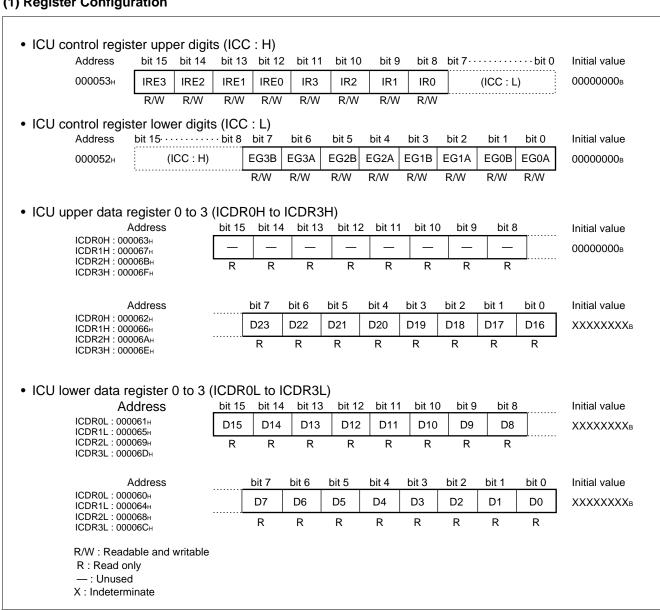

• Input capture (ICU)

Generates an interrupt request by latching a 24-bit free run timer counter value upon detection of an edge input to the pin.

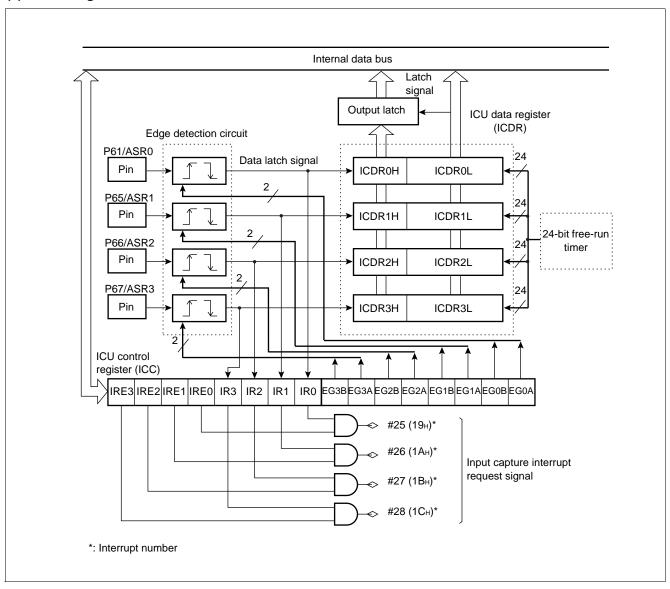

• Output compare (OCU)

Generates an interrupt request and reverse the output level upon detection of a match between the 24-bit free run timer counter value and the compare setting value.

- I<sup>2</sup>C interface (in MB90675 series only)

- Serial I/O port for supporting Inter IC BUS

#### (Continued)

• UARTO

With full-duplex double buffer (8-bit length)

Clock asynchronized or clock synchronized transmission (with start and stop bits) can be selectively used.

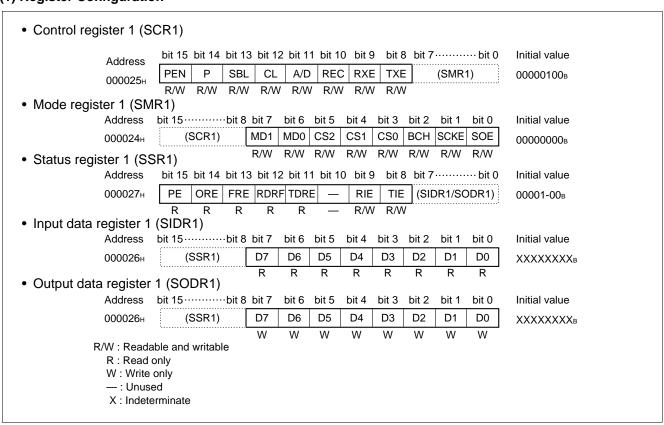

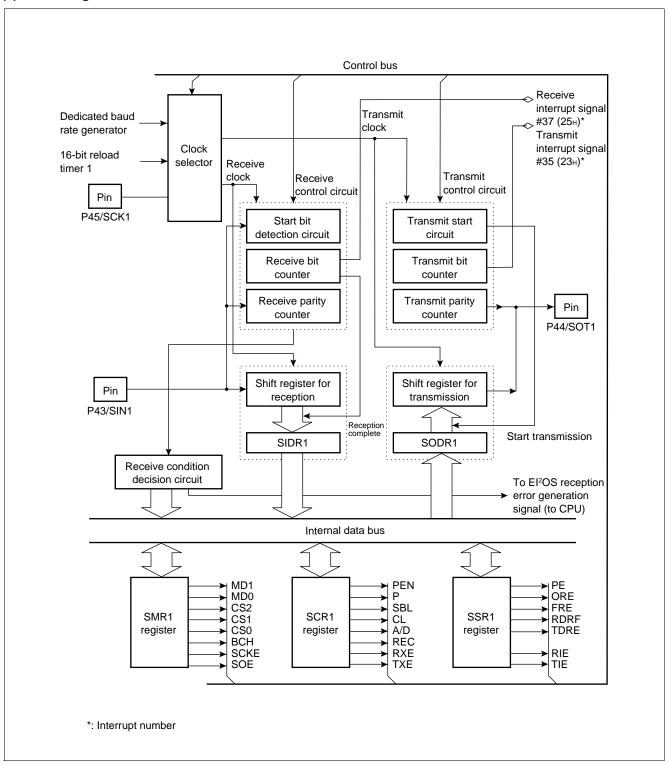

• UART1 (SCI)

With full-duplex double buffer (8-bit length)

Clock asynchronized or clock synchronized serial transmission (I/O extended serial) can be selectively used.

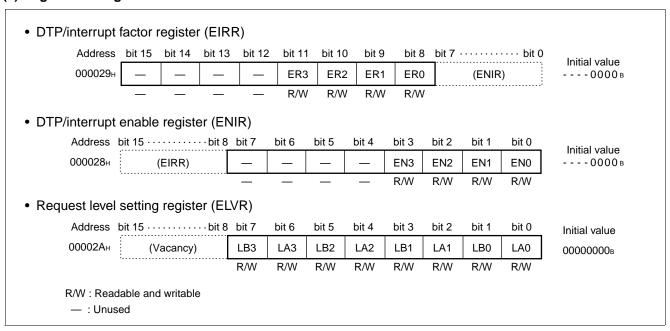

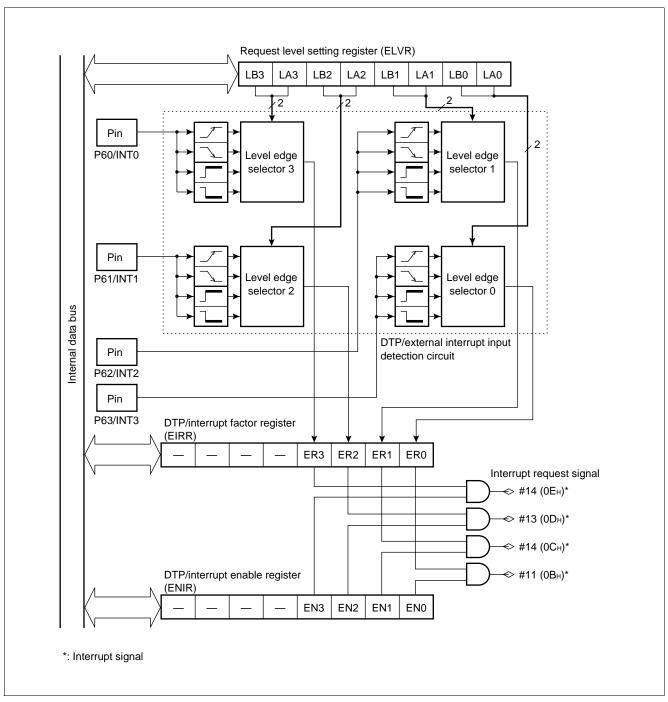

• DTP/external interrupt circuit (4 channels)

A module for starting extended intelligent I/O service (EI<sup>2</sup>OS) and generating an external interrupt triggered by an external input.

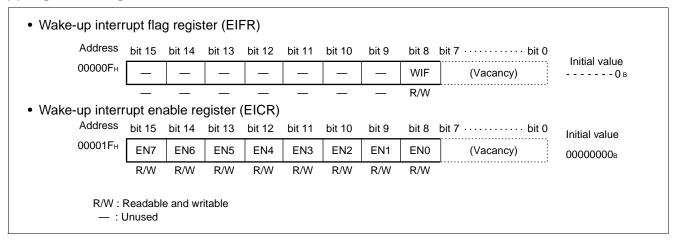

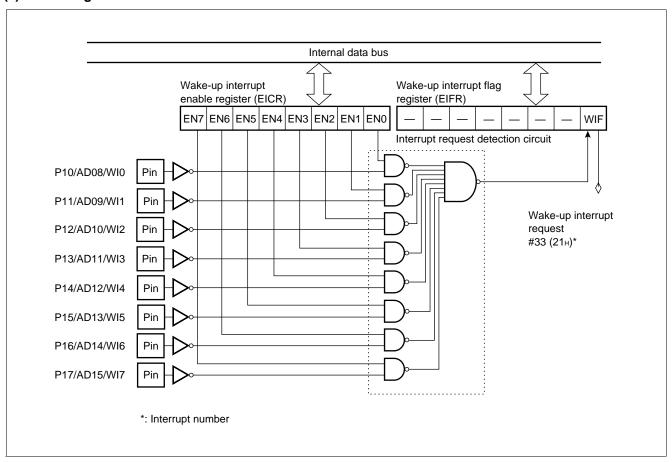

• Wake-up interrupt

Receives external interrupt requests and generates an interrupt request upon an "L" level input.

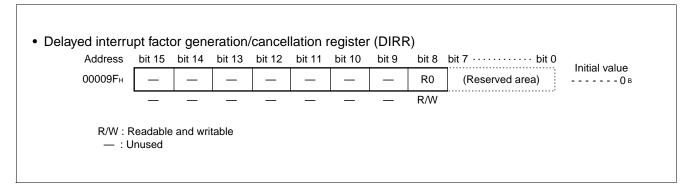

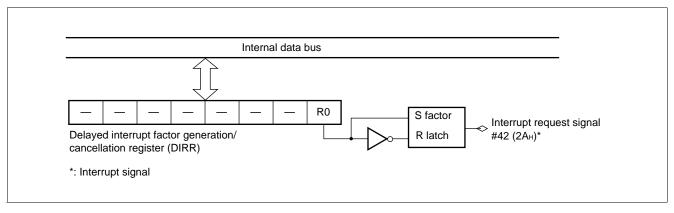

• Delayed interrupt generation module

Generates an interrupt request for switching tasks.

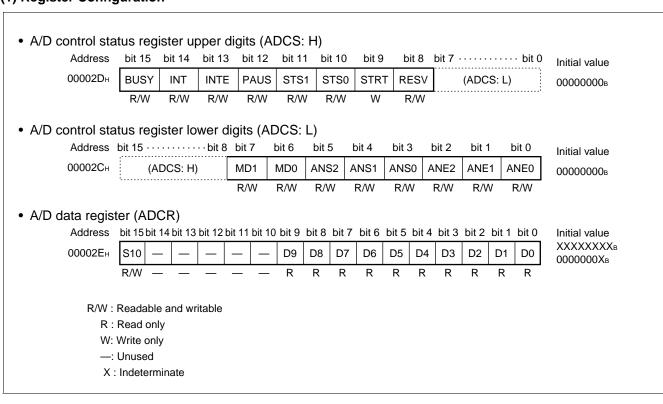

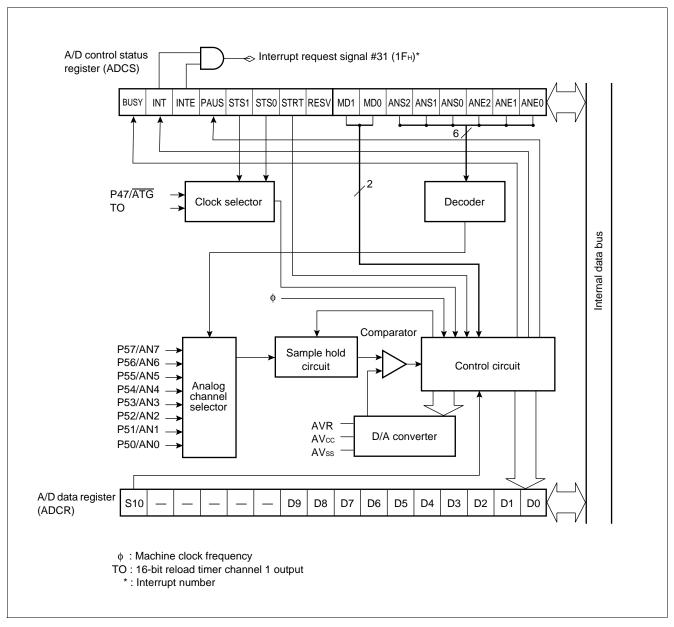

• 8/10-bit A/D converter (8 channels)

8-bit or 10-bit resolution can be selectively used.

Starting by an external trigger input.

### **■ PRODUCT LINEUP**

### • MB90670 series

| Part number Item             | MB90671                                                                                                                                                                                                                                                                                    | MB90672           | MB90673                                                                            | МВ90Т673                                                     | MB90P673  |  |  |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------------------------------------------------------------------------|--------------------------------------------------------------|-----------|--|--|

| Classification               | N                                                                                                                                                                                                                                                                                          | /lask ROM produc  | External ROM product                                                               | One-time<br>PROM<br>product                                  |           |  |  |

| ROM size                     | 16 Kbytes                                                                                                                                                                                                                                                                                  | 32 Kbytes         | 48 Kbytes                                                                          | External ROM                                                 | 48 Kbytes |  |  |

| RAM size                     | 640 bytes                                                                                                                                                                                                                                                                                  | 1.64 Kbytes       |                                                                                    | 2 Kbytes                                                     |           |  |  |

| CPU functions                | Ins<br>Minimu                                                                                                                                                                                                                                                                              | m execution time: | 8 bits, 16 bits<br>1 byte to 7 bytes<br>1 bit, 8 bits, 16 bit<br>62.5 ns (at machi | ts<br>ne clock of 16 MH<br>e clock of 16 MHz,                |           |  |  |

| Ports                        |                                                                                                                                                                                                                                                                                            |                   | (CMOS output): 5<br>(N-ch open-drain o                                             |                                                              |           |  |  |

| UART0                        | Clock synchronized transmission (500 Kbps to 2 Mbps) Clock asynchronized transmission (4800 Kbps to 500 Kbps) Transmission can be performed by bi-directional serial transmission or by master/slave connection.                                                                           |                   |                                                                                    |                                                              |           |  |  |

| UART1 (SCI)                  | Cloc                                                                                                                                                                                                                                                                                       | ck asynchronized  | transmission (240                                                                  | 0 Kbps to 2 Mbps)<br>0 Kbps to 62500 b<br>al transmission or | ps)       |  |  |

| 8/10-bit A/D converter       | Conversion precision: 10-bit or 8-bit selectable  Number of inputs: 8  One-shot conversion mode (converts selected channel only once)  Continuous conversion mode (converts selected channel continuously)  Stop conversion mode (converts selected channel and stop operation repeatedly) |                   |                                                                                    |                                                              |           |  |  |

| 8/16-bit PPG timer           | Number of channels: 2 8-bit or 16-bit PPG operation A Pulse wave of given intervals and given duty ratios can be output. Pulse cycle: 125 ns to 16.78 s (at oscillation of 4 MHz, machine clock of 16 MHz)                                                                                 |                   |                                                                                    |                                                              |           |  |  |

| 16-bit reload timer          | Number of channels: 2 16-bit reload timer operation Interval: 125 ns to 131 ms (at machine clock of 16 MHz) External event count can be performed.                                                                                                                                         |                   |                                                                                    |                                                              |           |  |  |

| 24-bit free run timer        | Number of channel :1 Overflow interrupts or intermediate bit interrupts may be generated.                                                                                                                                                                                                  |                   |                                                                                    |                                                              |           |  |  |

| Output compare unit<br>(OCU) |                                                                                                                                                                                                                                                                                            |                   | mber of channels.<br>A match signal of o                                           | -                                                            |           |  |  |

| Part number Item                     | MB90671                                                                                                    | MB90672            | MB90673                                                 | MB90T673                                     | MB90P673     |  |  |

|--------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------|---------------------------------------------------------|----------------------------------------------|--------------|--|--|

| Input capture unit (ICU)             | Number of channels: 4 Rewriting a register value upon a pin input (rising, falling, or both edges)         |                    |                                                         |                                              |              |  |  |

| DTP/external interrupt circuit       |                                                                                                            | sing edge, a falli |                                                         | 4<br>level input, or an<br>/O service (El²OS |              |  |  |

| Wake-up interrupt                    |                                                                                                            |                    | umber of inputs:<br>ed by an "L" level                  |                                              |              |  |  |

| Delayed interrupt generation module  | An interrupt generation module for switching tasks used in real-time operating systems.                    |                    |                                                         |                                              |              |  |  |

| I <sup>2</sup> C interface           |                                                                                                            |                    | None                                                    |                                              |              |  |  |

| Timebase timer                       | Interru                                                                                                    | •                  | 18-bit counter<br>I ms, 4.096 ms,<br>oscillation of 4 N | 16.384 ms, 131.0<br>IHz)                     | 072 ms       |  |  |

| Watchdog timer                       | Reset generation interval: 3.58 ms, 14.33 ms, 57.23 ms, 458.75 ms (at oscillation of 4 MHz, minimum value) |                    |                                                         |                                              | 58.75 ms     |  |  |

| Low-power consumption (standby) mode | Sleep/stop/CPU intermittent operation/timebase timer/hardware stand-by                                     |                    |                                                         |                                              | are stand-by |  |  |

| Process                              | CMOS                                                                                                       |                    |                                                         |                                              |              |  |  |

| Operating voltage*                   | 2.7 V to 5.5 V                                                                                             |                    |                                                         |                                              |              |  |  |

<sup>\*:</sup> Varies with conditions such as the operating frequency. (See section "■ Electrical Characteristics.")

### • MB90675 series

| Part number Item            | MB90676                                                                                                                                                                                                                                                                                                  | MB90677                                                                                                                                                                                                          | MB90678                                                                    | MB90T678                                                | MB90P678                    | MB90V670           |  |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------|-----------------------------|--------------------|--|

| Classification              | Ma                                                                                                                                                                                                                                                                                                       | ask ROM produ                                                                                                                                                                                                    | cts                                                                        | External ROM product                                    | One-time<br>PROM<br>product | Evaluation product |  |

| ROM size                    | 32 Kbytes                                                                                                                                                                                                                                                                                                | 48 Kbytes                                                                                                                                                                                                        | 64 Kbytes                                                                  | None                                                    | 64 Kbytes                   | _                  |  |

| RAM size                    | 1.64 Kbytes                                                                                                                                                                                                                                                                                              | 2 Kbytes                                                                                                                                                                                                         |                                                                            | 3 Kbytes                                                |                             | 4 Kbytes           |  |

| CPU functions               | Instru<br>Ins<br>Minimum                                                                                                                                                                                                                                                                                 | Data bit length: execution time:                                                                                                                                                                                 | 8 bits, 16 bits<br>1 byte to 7 byte<br>1 bit, 8 bits, 16<br>62.5 ns (at ma |                                                         |                             | n value)           |  |

| Ports                       |                                                                                                                                                                                                                                                                                                          | ral-purpose I/O                                                                                                                                                                                                  | ports (CMOS o<br>ports (N-ch ope                                           | output): 74<br>en-drain output)                         | : 10                        |                    |  |

| UART0                       | Transmission connection.                                                                                                                                                                                                                                                                                 | Clock synchronized transmission (500 Kbps to 2 Mbps) Clock asynchronized transmission (4800 Kbps to 500 Kbps) Transmission can be performed by bi-directional serial transmission or by master/slave connection. |                                                                            |                                                         |                             |                    |  |

| UART1 (SCI)                 | Transmission connection.                                                                                                                                                                                                                                                                                 | Clock asynchro                                                                                                                                                                                                   | onized transmis                                                            | ission (500 Kbp<br>sion (2400 Kbp:<br>nal serial transn | s to 62500 bps)             |                    |  |

| 8/10-bit A/D con-<br>verter | Conversion precision: 10-bit or 8-bit can be selectively used.  Number of inputs: 8  One-shot conversion mode (converts selected channel only once)  Continuous conversion mode (converts selected channel continuously)  Stop conversion mode (converts selected channel and stop operation repeatedly) |                                                                                                                                                                                                                  |                                                                            |                                                         |                             |                    |  |

| 8/16-bit PPG timer          | Number of channels: 2 PPG operation of 8-bit or 16-bit Pulse of given intervals and given duty ratios can be output Pulse interval 125 ns to 16.78 s (at oscillation of 4 MHz, machine clock of 16 MHz)                                                                                                  |                                                                                                                                                                                                                  |                                                                            |                                                         |                             |                    |  |

| 16-bit reload timer         | Number of channels: 2 16-bit reload timer operation Interval: 125 ns to 131 ms (at machine clock of 16 MHz) External event count can be performed.                                                                                                                                                       |                                                                                                                                                                                                                  |                                                                            |                                                         |                             |                    |  |

| 24-bit free run timer       | Number of channel :1 Overflow interrupts or intermediate bit interrupts may be generated.                                                                                                                                                                                                                |                                                                                                                                                                                                                  |                                                                            |                                                         |                             |                    |  |

| Output compare<br>(OCU)     |                                                                                                                                                                                                                                                                                                          | Pin input f                                                                                                                                                                                                      |                                                                            | channels: 8<br>signal of compa                          | re register                 |                    |  |

### (Continued)

| Part number Item                      | MB90676                                                                | MB90677                                                                                                    | MB90678            | MB90T678                                  | MB90P678                          | MB90V670 |  |  |

|---------------------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------|-------------------------------------------|-----------------------------------|----------|--|--|

| Input capture (ICU)                   | Rewr                                                                   | iting a register                                                                                           |                    | channels: 4<br>n input (rising, f         | alling, or both e                 | dges)    |  |  |

| DTP/external inter-<br>rupt circuit   |                                                                        |                                                                                                            | e, a falling edge  |                                           | put, or an "L" levice (El²OS) can |          |  |  |

| Wake-up interrupt                     |                                                                        |                                                                                                            |                    | of inputs: 8<br>"L" level input.          |                                   |          |  |  |

| Delayed interrupt generation module   | An interrupt                                                           | An interrupt generation module for switching tasks used in realtime operating systems.                     |                    |                                           |                                   |          |  |  |

| I <sup>2</sup> C interface            |                                                                        | Seria                                                                                                      | I I/O port for sup | pporting Inter IC                         | BUS                               |          |  |  |

| Timebase timer                        | ı                                                                      | Interrupt interva                                                                                          | al: 1.024 ms, 4.0  | counter<br>196 ms, 16.384<br>on of 4 MHz) | ms, 131.072 ms                    | 3        |  |  |

| Watchdog timer                        | Re                                                                     | Reset generation interval: 3.58 ms, 14.33 ms, 57.23 ms, 458.75 ms (at oscillation of 4 MHz, minimum value) |                    |                                           |                                   |          |  |  |

| Low-power consumption (stand-by) mode | Sleep/stop/CPU intermittent operation/timebase timer/hardware stand-by |                                                                                                            |                    |                                           |                                   |          |  |  |

| Process                               | CMOS                                                                   |                                                                                                            |                    |                                           |                                   |          |  |  |

| Power supply voltage for operation*   |                                                                        | 2.7 V to 5.5 V                                                                                             |                    |                                           |                                   |          |  |  |

<sup>\*:</sup> Varies with conditions such as the operating frequency. (See section "■ ELECTRICAL CHARACTERISTICS.") Assurance for the MB90V670 is given only for operation with a tool at a power voltage of 2.7 V to 5.5 V, an operating temperature of 0°C to 70°C, and an operating frequency of 1.5 MHz to 16 MHz.

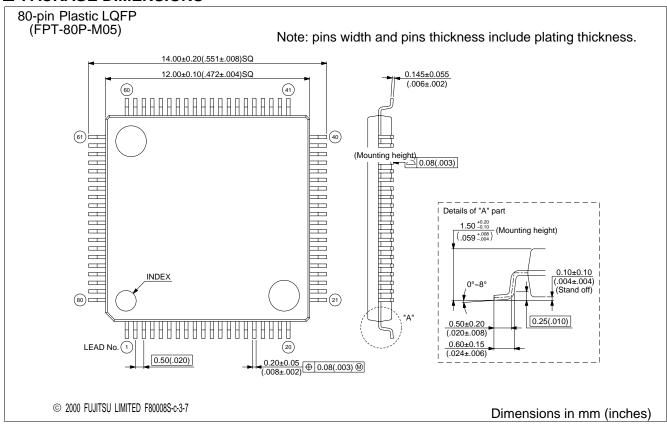

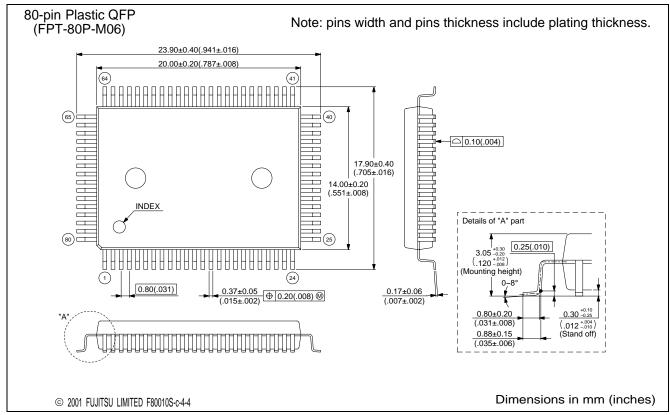

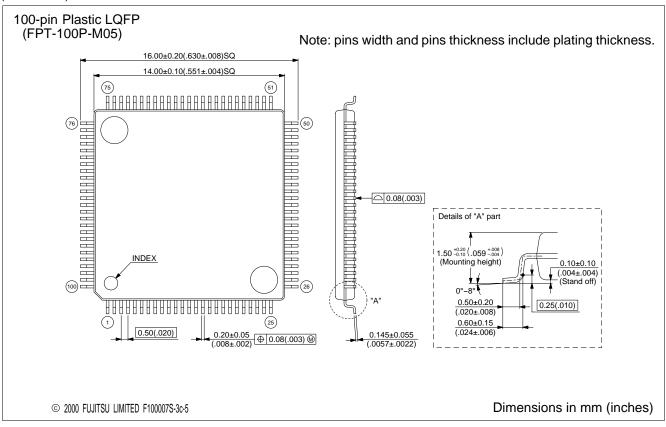

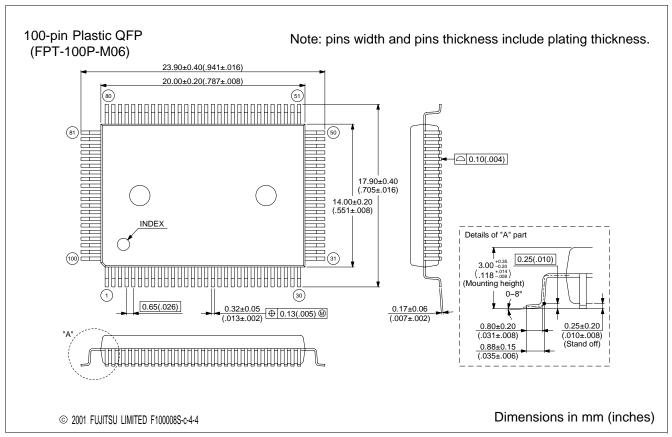

### ■ PACKAGE AND CORRESPONDING PRODUCTS

| Package      | MB90671<br>MB90672<br>MB90673<br>MB90T673 | MB90P673 | MB90676<br>MB90677<br>MB90678<br>MB90T678 | MB90P678 | MB90V670 |

|--------------|-------------------------------------------|----------|-------------------------------------------|----------|----------|

| FPT-80P-M05  | 0                                         | 0        | ×                                         | ×        | ×        |

| FPT-80P-M06  | 0                                         | 0        | ×                                         | ×        | ×        |

| FPT-100P-M05 | ×                                         | ×        | 0                                         | 0        | ×        |

| FPT-100P-M06 | ×                                         | ×        | 0                                         | 0        | ×        |

○ : Available ×: Not available

Note: For more information about each package, see section "■ PACKAGE DIMENSIONS."

### **■ DIFFERENCES AMONG PRODUCTS**

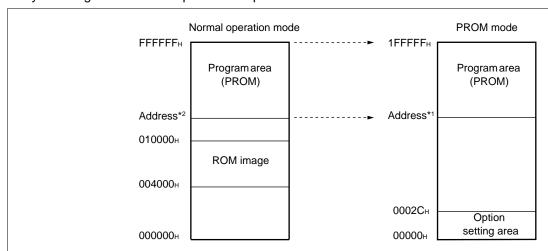

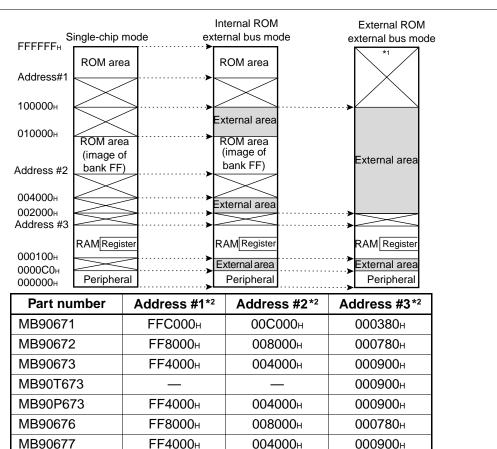

### 1. Memory Size

In evaluation with an evaluation product, note the difference between the evaluation chip and the chip actually used. The following items must be taken into consideration.

- The MB90V670 does not have an internal ROM, however, operations equivalent to chips with an internal ROM

can be evaluated by using a dedicated development tool, enabling selection of ROM size by settings of the

development tool.

- In the MB90V670, images from FF4400H to FFFFFFH are mapped to bank 00, and FE0000H to FF3FFFH to mapped to bank FEH and FFH only. (This setting can be changed by configuring the development tool.)

- In the MB90678/MB90P678, images from FF4000<sub>H</sub> to FFFFFF<sub>H</sub> are mapped to bank 00, and FF0000<sub>H</sub> to FF3FFF<sub>H</sub> to bank FF only.

### 2. Mask Options

Functions selected by optional settings and methods for setting the options are dependent on the product types. Refer to "

Mask Options" for detailed information.

Note that mask option is fixed in MB90V670 series.

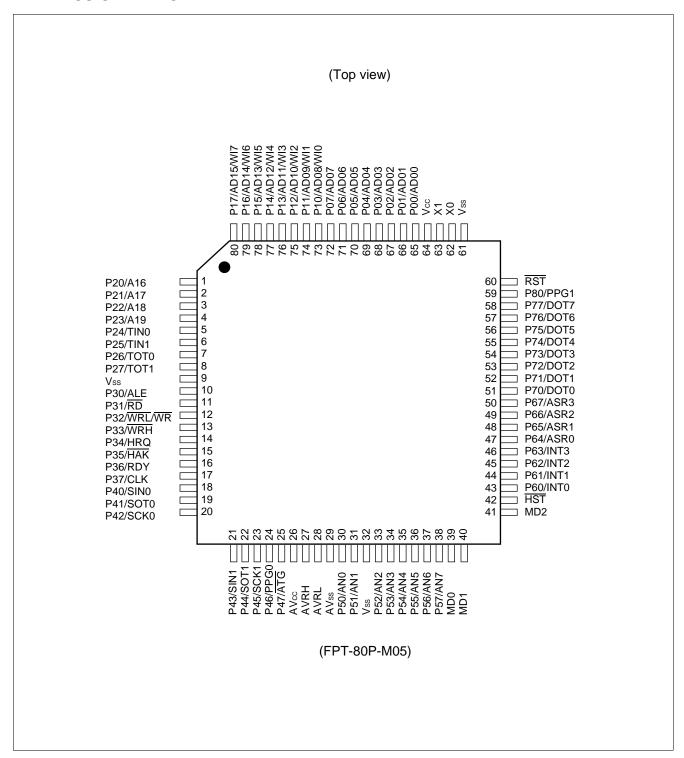

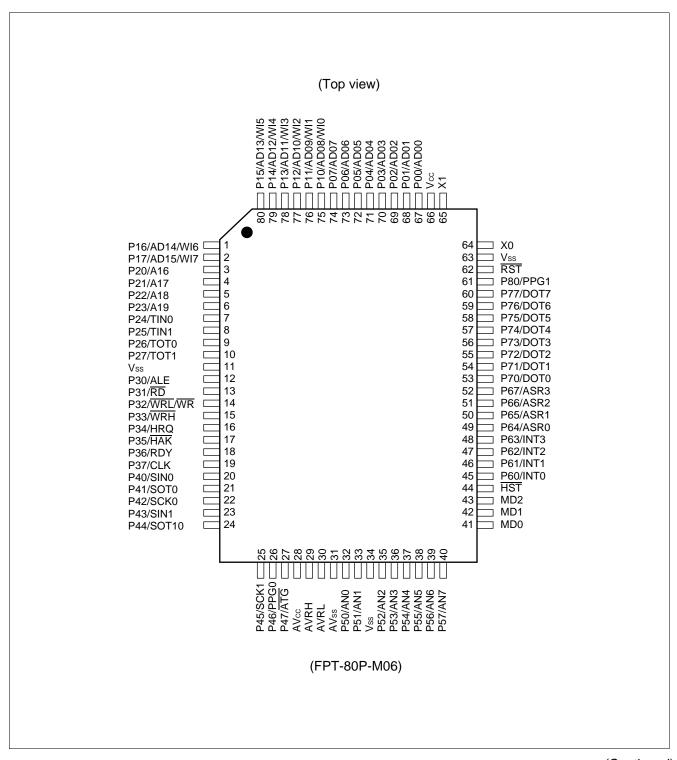

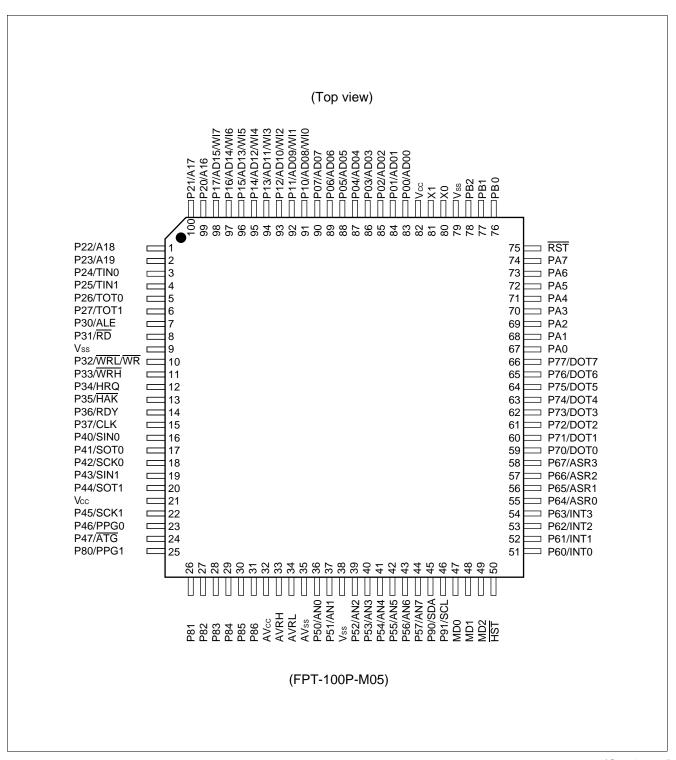

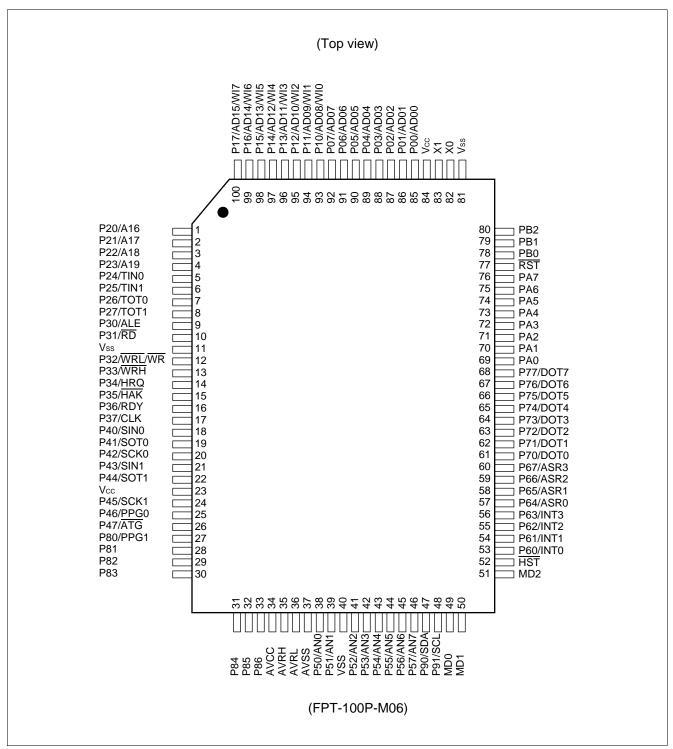

### **■ PIN ASSIGNMENTS**

### **■ PIN DESCRIPTION**

|               | Pin no.                                                 |                      |                         |                                                                                                                                                                                               |                                                                          |                                                                                                                                                                                                                                                                                                                    |  |

|---------------|---------------------------------------------------------|----------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

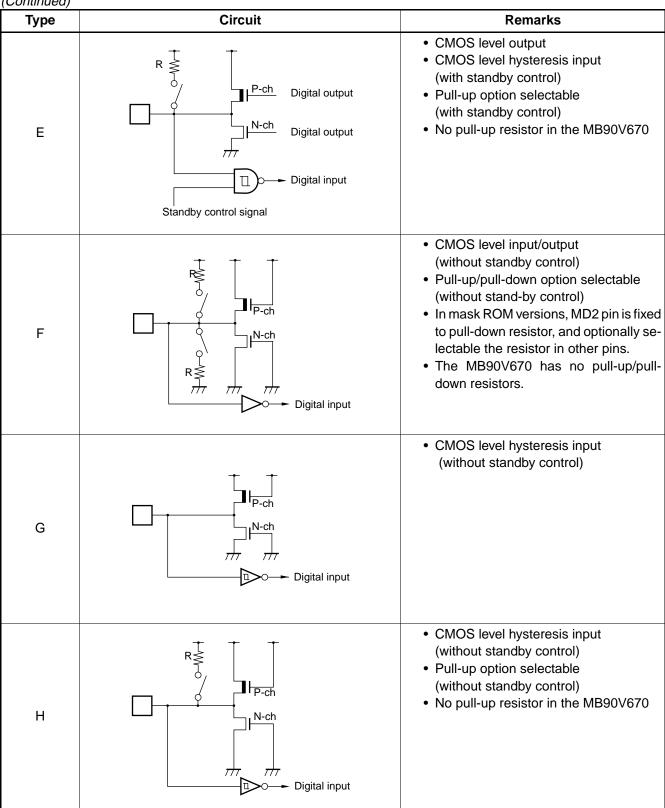

| LQFP<br>-80*1 | QFP<br>-80*2                                            | LQFP<br>-100*3       | QFP<br>-100*4           | Pin name                                                                                                                                                                                      | Circuit type                                                             | Function                                                                                                                                                                                                                                                                                                           |  |

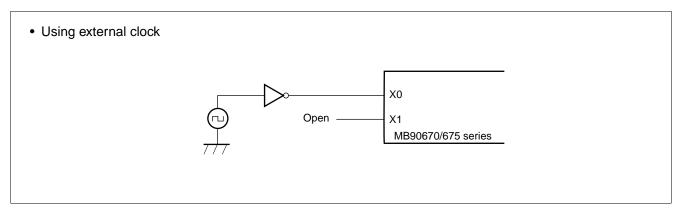

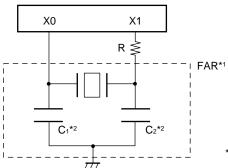

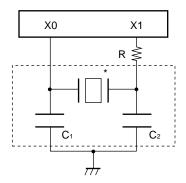

| 62            | 64                                                      | 80                   | 82                      | X0                                                                                                                                                                                            | А                                                                        | Crystal oscillator pins                                                                                                                                                                                                                                                                                            |  |

| 63            | 65                                                      | 81                   | 83                      | X1                                                                                                                                                                                            | (Oscillation)                                                            | Crystal Oscillator piris                                                                                                                                                                                                                                                                                           |  |

| 39 to 41      | 41 to 43                                                | 47 to 49             | 49 to 51                | MD0 to<br>MD2                                                                                                                                                                                 | F<br>(CMOS)                                                              | Input pins for selecting operation modes Connect directly to Vcc or Vss.                                                                                                                                                                                                                                           |  |

| 60            | 62                                                      | 75                   | 77                      | RST                                                                                                                                                                                           | H<br>(CMOS/H)                                                            | External reset request input                                                                                                                                                                                                                                                                                       |  |

| 42            | 44                                                      | 50                   | 52                      | HST                                                                                                                                                                                           | G<br>(CMOS/H)                                                            | Hardware standby input pin                                                                                                                                                                                                                                                                                         |  |

|               |                                                         |                      |                         | P00 to P07                                                                                                                                                                                    |                                                                          | General-purpose I/O port This function is valid in the single-chip mode.                                                                                                                                                                                                                                           |  |

| 65 to 72      | 67 to 74                                                | 83 to 90             | 85 to 92                | AD00 to<br>AD07                                                                                                                                                                               | AD00 to (CMOS) of AD07                                                   | I/O pins for the lower 8-bit of the external address data bus This function is valid in the mode where the external bus is valid.                                                                                                                                                                                  |  |

|               |                                                         |                      | P10 to P15,<br>P16, P17 |                                                                                                                                                                                               | General-purpose I/O port This function is valid in the single-chip mode. |                                                                                                                                                                                                                                                                                                                    |  |

| 73 to 78,     | 75 to 80,                                               |                      |                         | AD08 to<br>AD13,<br>AD14,<br>AD15                                                                                                                                                             | AD13, AD14, AD15  B (CMOS)  I WI0 to WI5, WI6, WI7                       | I/O pins for the upper 8-bit of the external address data bus This function is valid in the mode where the external bus is valid.                                                                                                                                                                                  |  |

| 79, 80        | 1, 2                                                    | 97, 98               | 99, 100                 | WI0 to WI5,<br>WI6, WI7                                                                                                                                                                       |                                                                          | I/O pins for wake-up interrupts This function is valid in the single-chip mode. Because the input of the DTP/external interrupt circuit is used as required when the DTP/external interrupt circuit is enabled, and it is necessary to stop outputs by other functions unless such outputs are made intentionally. |  |

|               |                                                         | 99 100               |                         | P20, P21,<br>P22, P23                                                                                                                                                                         | В                                                                        | General-purpose I/O port This function becomes valid in the single-chip mode or the external address output control register is set to select a port.                                                                                                                                                              |  |

| 1, 2, 3, 4    | 1, 3, 4 3, 4, 5, 6 99, 100, 1, 2, 3, 4 A16, A17 A18, 19 | A16, A17,<br>A18, 19 | (CMOS)                  | Output pins for the external address bus of A16 to A19 This function is valid in the mode where the external bus is valid and the upper address control register is set to select an address. |                                                                          |                                                                                                                                                                                                                                                                                                                    |  |

(Continued)

\*1: FPT-80P-M05

\*2: FPT-80P-M06

\*3: FPT-100P-M05

\*4: FPT-100P-M06

|               | Pin no.      |                |               |               |              |                                                                                                                                                                                                                             |            |            |                                                                                                                                                                                                              |               |                                                                                                                                                                                                                                                        |                                                                                                     |

|---------------|--------------|----------------|---------------|---------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| LQFP<br>-80*1 | QFP<br>-80*2 | LQFP<br>-100*3 | QFP<br>-100*4 | Pin name      | Circuit type | Function                                                                                                                                                                                                                    |            |            |                                                                                                                                                                                                              |               |                                                                                                                                                                                                                                                        |                                                                                                     |

|               |              |                |               | P24, P25      |              | General-purpose I/O port This function is always valid.                                                                                                                                                                     |            |            |                                                                                                                                                                                                              |               |                                                                                                                                                                                                                                                        |                                                                                                     |

| 5, 6          | 7, 8         | 3, 4           | 3, 4          | 3, 4          | 3, 4         | 5, 6                                                                                                                                                                                                                        | TINO, TIN1 | TINO, TIN1 |                                                                                                                                                                                                              | E<br>(CMOS/H) | Event input pins of 16-bit reload timer 0 and 1 Because this input is used as required when the 16-bit reload timer is performing input operations, and it is necessary to stop outputs by other functions unless such outputs are made intentionally. |                                                                                                     |

| 7, 8          | 9, 10        | 5, 6           | 7, 8          | P26, P27      | E            | General-purpose I/O port This function is valid when outputs from 16-bit reload timer 0 and 1 are disabled.                                                                                                                 |            |            |                                                                                                                                                                                                              |               |                                                                                                                                                                                                                                                        |                                                                                                     |

| 7,0           | 9, 10        | 3, 0           | 7,0           | TOT0,<br>TOT1 | (CMOS/H)     | Output pins for 16-bit reload timer 0 and 1<br>This function is valid when output from 16-bit reload timer 0 and 1 are enabled.                                                                                             |            |            |                                                                                                                                                                                                              |               |                                                                                                                                                                                                                                                        |                                                                                                     |

|               |              |                |               | P30           | В            | General-purpose I/O port This function is valid in the single-chip mode.                                                                                                                                                    |            |            |                                                                                                                                                                                                              |               |                                                                                                                                                                                                                                                        |                                                                                                     |

| 10            | 12           | 7              | 7             | 7             | 7            | 7                                                                                                                                                                                                                           | 7          | 9          | 9                                                                                                                                                                                                            | ALE           | (CMOS)                                                                                                                                                                                                                                                 | Address latch enable output pin This function is valid in the mode where the external bus is valid. |

|               |              |                |               | P31           | В            | General-purpose I/O port This function is valid in the single-chip mode.                                                                                                                                                    |            |            |                                                                                                                                                                                                              |               |                                                                                                                                                                                                                                                        |                                                                                                     |

| 11            | 13           | 8              | 10            | RD            | (CMOS)       | Read strobe output pin for the data bus This function is valid in the mode where the external bus is valid.                                                                                                                 |            |            |                                                                                                                                                                                                              |               |                                                                                                                                                                                                                                                        |                                                                                                     |

|               |              |                |               | P32           |              | General-purpose I/O port  This function is valid in the single-chip mode or WRL/WR pin output is disabled.                                                                                                                  |            |            |                                                                                                                                                                                                              |               |                                                                                                                                                                                                                                                        |                                                                                                     |

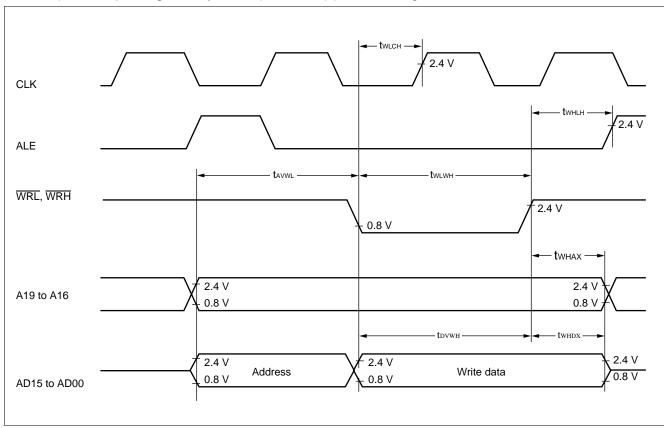

| 40            | 4.4          | 40             | 40            | WRL           | В            | Write strobe output pin for the data bus This function is valid when WRL/WR pin output is                                                                                                                                   |            |            |                                                                                                                                                                                                              |               |                                                                                                                                                                                                                                                        |                                                                                                     |

| 12            | 14           | 10             | 12            | WR            | (CMOS)       | enabled in the mode where external bus is valid. WRL is used for holding the lower 8-bit for write strobe in 16-bit access operations, while WR is used for holding 8-bit data for write strobe in 8-bit access operations. |            |            |                                                                                                                                                                                                              |               |                                                                                                                                                                                                                                                        |                                                                                                     |

|               |              |                |               | P33           | В            | General-purpose I/O port This function is valid in the single-chip mode, in the external bus 8-bit mode, or WRH pin output is disabled.                                                                                     |            |            |                                                                                                                                                                                                              |               |                                                                                                                                                                                                                                                        |                                                                                                     |

| 13            | 15           | 11             | 13            | WRH           | WRH          | WRH                                                                                                                                                                                                                         | WRH        | (CMOS)     | Write strobe output pin for the upper 8-bit of the data bus This function is valid when the external bus 16-bit mode is selected in the mode where the external bus is valid, and WRH output pin is enabled. |               |                                                                                                                                                                                                                                                        |                                                                                                     |

<sup>\*1:</sup> FPT-80P-M05

<sup>\*2:</sup> FPT-80P-M06

<sup>\*3:</sup> FPT-100P-M05

<sup>\*4:</sup> FPT-100P-M06

|               | Pin no.      |                |               |          |               |                                                                                                                                                                                                                       |                                                                                                                                 |

|---------------|--------------|----------------|---------------|----------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| LQFP<br>-80*1 | QFP<br>-80*2 | LQFP<br>-100*3 | QFP<br>-100*4 | Pin name | Circuit type  | Function                                                                                                                                                                                                              |                                                                                                                                 |

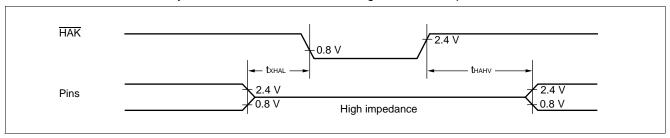

|               |              |                |               | P34      | В             | General-purpose I/O port This function is valid when both the single-chip mode and the hold function are disabled.                                                                                                    |                                                                                                                                 |

| 14            | 16           | 12             | 14            | HRQ      | (CMOS)        | Hold request input pin This function is valid in the mode where the external bus is valid or when the hold function is enabled.                                                                                       |                                                                                                                                 |

|               |              |                |               | P35      | В             | General-purpose I/O port This function is valid when both the single-chip mode and the hold function are disabled.                                                                                                    |                                                                                                                                 |

| 15            | 17           | 13             | 15            | HAK      | (CMOS)        | Hold acknowledge output pin This function is valid in the mode where the external bus is valid or when the hold function is enabled.                                                                                  |                                                                                                                                 |

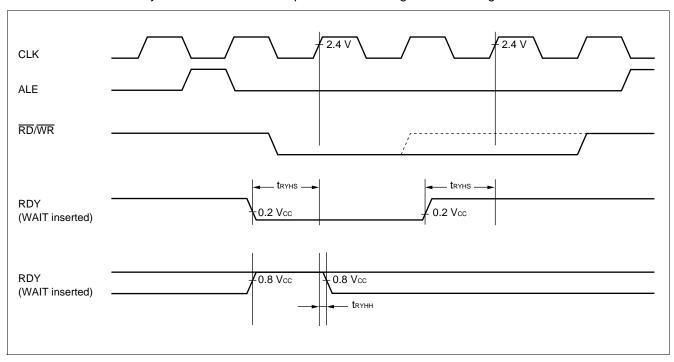

|               |              |                |               | P36      | В             | General-purpose I/O port This function is valid when both the single-chip mode and the external ready function are disabled.                                                                                          |                                                                                                                                 |

| 16            | 18           | 14             | 16            | ,        | RDY           | (CMOS)                                                                                                                                                                                                                | Ready input pin This function is valid when the external ready function is enabled in the mode where the external bus is valid. |

| 17            | 19           | 15             | 17            | P37      | В             | General-purpose I/O port This function is valid in the single-chip mode or when the CLK output is disabled.                                                                                                           |                                                                                                                                 |

| 17            | 19           | 15             | 17            | CLK      | (CMOS)        | CLK output pin This function is valid when CLK output is disabled in the mode where the external bus is valid.                                                                                                        |                                                                                                                                 |

|               |              |                |               | P40      |               | General-purpose I/O port This function is always valid.                                                                                                                                                               |                                                                                                                                 |

| 18            | 20           | 16             | 18            | SIN0     | E<br>(CMOS/H) | Serial data input pin of UART0 Because this input is used as required when UART0 is performing input operations, and it is necessary to stop outputs by other functions un- less such outputs are made intentionally. |                                                                                                                                 |

| 19            | 21           | 17             | 19            | P41      | E<br>(CMOS/H) | General-purpose I/O port This function is valid when serial data output from UART0 is disabled.                                                                                                                       |                                                                                                                                 |

| 19            | ۷ ۱          | 17             | 13            | SOT0     |               | Serial data output pin of UART0 This function is valid when serial data output from UART0 is enabled.  (Continued)                                                                                                    |                                                                                                                                 |

<sup>\*1:</sup> FPT-80P-M05

<sup>\*2:</sup> FPT-80P-M06

<sup>\*3:</sup> FPT-100P-M05

<sup>\*4:</sup> FPT-100P-M06

|               | Pin no.      |                |               |          |               |                                                                                                                                                                                                                                                                                                 |                                                                                           |      |                 |                                                                                                                                                                                                                                   |

|---------------|--------------|----------------|---------------|----------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LQFP<br>-80*1 | QFP<br>-80*2 | LQFP<br>-100*3 | QFP<br>-100*4 | Pin name | Circuit type  | Function                                                                                                                                                                                                                                                                                        |                                                                                           |      |                 |                                                                                                                                                                                                                                   |

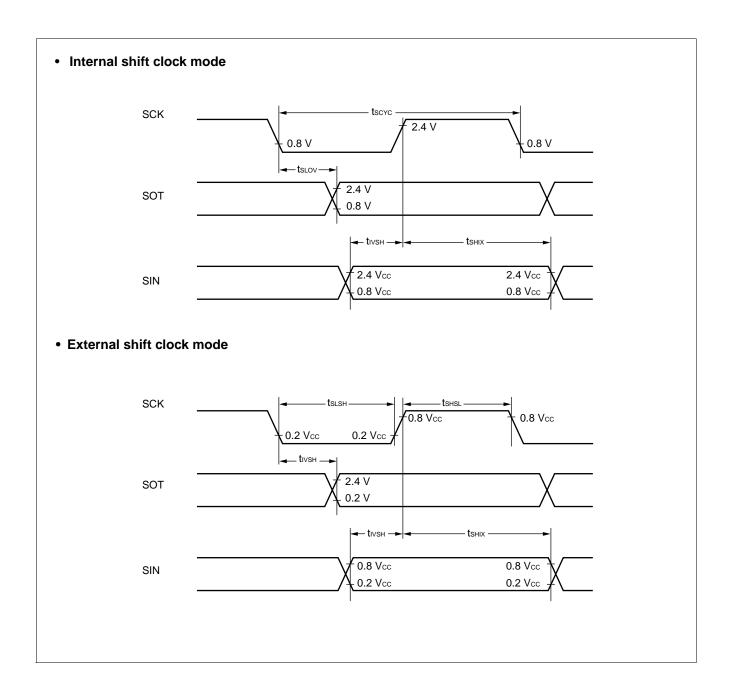

|               |              |                |               |          | P42           |                                                                                                                                                                                                                                                                                                 | General-purpose I/O port This function is valid when clock output from UART0 is disabled. |      |                 |                                                                                                                                                                                                                                   |

| 20            | 22           | 18             | 20            | SCK0     | E<br>(CMOS/H) | Clock I/O pin of UART0 This function is valid when clock output from UART0 is enabled. Because this input is used as required when UART0 is performing input operations, and it is necessary to stop outputs by other functions unless such outputs are made intentionally.                     |                                                                                           |      |                 |                                                                                                                                                                                                                                   |

|               |              |                |               | P43      |               | General-purpose I/O port This function is always valid.                                                                                                                                                                                                                                         |                                                                                           |      |                 |                                                                                                                                                                                                                                   |

| 21            | 23           | 19             | 21            | SIN1     | SIN1          | SIN1                                                                                                                                                                                                                                                                                            | SIN1                                                                                      | SIN1 | SIN1 E (CMOS/H) | Serial data input pin of UART1 (SCI) Because this input is used as required when UART1 (SCI) is performing input operations, and it is necessary to stop outputs by other functions un- less such outputs are made intentionally. |

| 22            | 24           | 20             | 22            | P44      | E             | General-purpose I/O port This function is valid when serial data output from UART1 (SCI) is disabled.                                                                                                                                                                                           |                                                                                           |      |                 |                                                                                                                                                                                                                                   |

| 22            | 24           | 20             | 22            | SOT1     | SOT1          | Serial data output pin of UART1 (SCI) This function is valid when serial data output from UART1 (SCI) is enabled.                                                                                                                                                                               |                                                                                           |      |                 |                                                                                                                                                                                                                                   |

|               |              |                |               |          |               |                                                                                                                                                                                                                                                                                                 |                                                                                           | P45  |                 | General-purpose I/O port This function is valid when clock output from UART1 (SCI) is disabled.                                                                                                                                   |

| 23            | 25           | 22             | 24            | SCK1     | E<br>(CMOS/H) | Clock I/O pin of UART1 (SCI) This function is valid when clock output from UART1 (SCI) is enabled. Because this input is used as required when UART1 (SCI) is performing input operations, and it is necessary to stop outputs by other functions un- less such outputs are made intentionally. |                                                                                           |      |                 |                                                                                                                                                                                                                                   |

| 24            | 26           | 23             | 25            | P46      | E             | General-purpose I/O port This function is valid when waveform output from 8/16-bit PPG timer 0 is disabled.                                                                                                                                                                                     |                                                                                           |      |                 |                                                                                                                                                                                                                                   |

| 24            | 20           | 23             | 23            | PPG0     | (CMOS/H)      | Output pin of 8/16-bit PPG timer 0 This function is valid when waveform output from 8/16-bit PPG timer 0 is enabled.  (Continued)                                                                                                                                                               |                                                                                           |      |                 |                                                                                                                                                                                                                                   |

(Continued)

\*1: FPT-80P-M05

\*2: FPT-80P-M06

\*3: FPT-100P-M05

\*4: FPT-100P-M06

|                    | Pin no.      |                    |                    |                                      |               |                                                                                                                                                                                                                                                                              |

|--------------------|--------------|--------------------|--------------------|--------------------------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LQFP<br>-80*1      | QFP<br>-80*2 | LQFP<br>-100*3     | QFP<br>-100*4      | Pin name                             | Circuit type  | Function                                                                                                                                                                                                                                                                     |

|                    |              |                    |                    | P47                                  |               | General-purpose I/O port This function is always valid.                                                                                                                                                                                                                      |

| 25                 | 27           | 24                 | 26                 | ĀTG                                  | E<br>(CMOS/H) | Trigger input pin of the 8/10-bit A/D converter Because this input is used as required when the 8/10-bit A/D converter is performing input operations, and it is necessary to stop outputs by other functions unless such outputs are made intentionally.                    |

| 30, 31,<br>33, 34, |              | 36, 37,<br>38, 39, | 38, 39,<br>40, 41, | P50, P51,<br>P52, P53,<br>P54 to P57 | С             | I/O port of an open-drain type The input function is valid when the analog input enable register is set to select a port.                                                                                                                                                    |

|                    | 37 to 40     |                    |                    | AN0, AN1,<br>AN2, AN3,<br>AN4 to AN7 | (CMOS/H)      | Analog input pins of the 8/10-bit A/D converter This function is valid when the analog input enable register is set to select AD.                                                                                                                                            |

|                    |              |                    |                    | P60 to P63                           |               | General-purpose I/O port This function is always valid.                                                                                                                                                                                                                      |

| 43 to 46           | 45 to 48     | 51 to 54           | 53 to 56           | INT0 to<br>INT3                      | E<br>(CMOS/H) | Request input pins of the DTP/external interrupt circuit Because this input is used as required when the DTP/external interrupt circuit is performing input operations, and it is necessary to stop outputs from other functions unless such outputs are made intentionally. |

|                    |              |                    |                    | P64 to P67                           |               | General-purpose I/O port This function is always valid.                                                                                                                                                                                                                      |

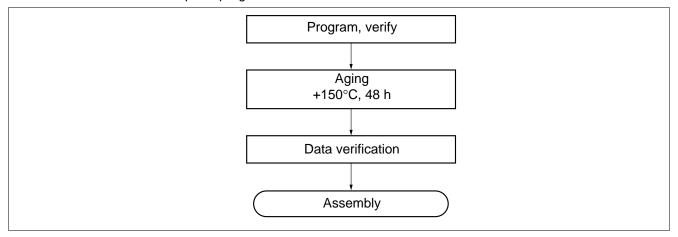

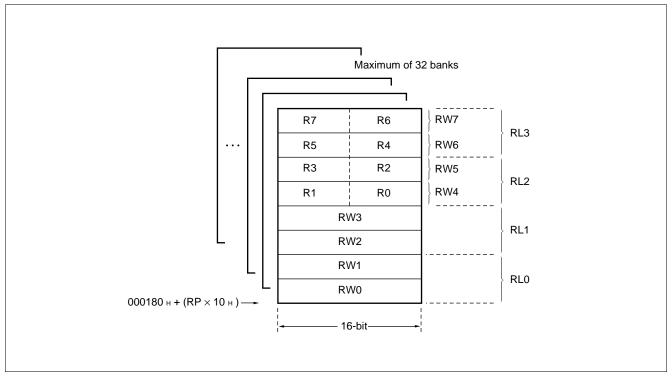

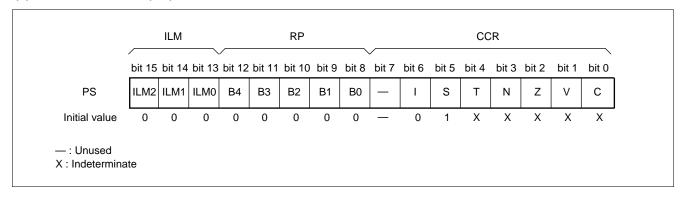

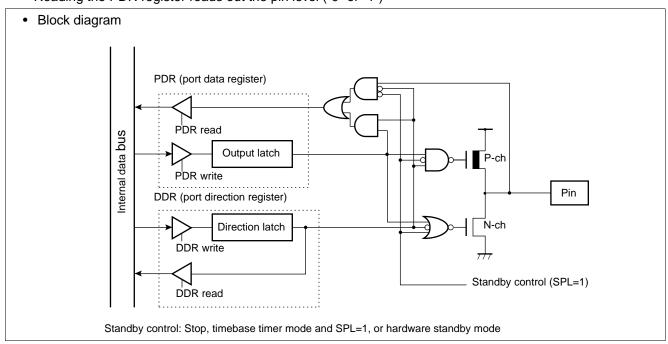

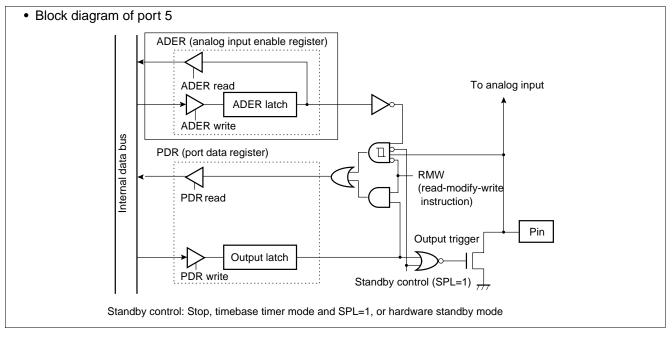

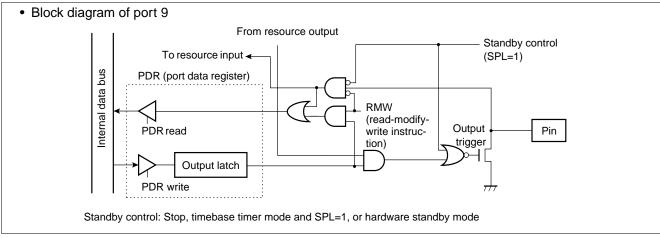

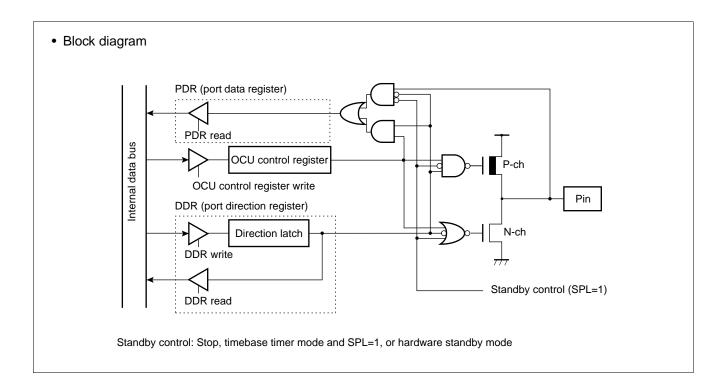

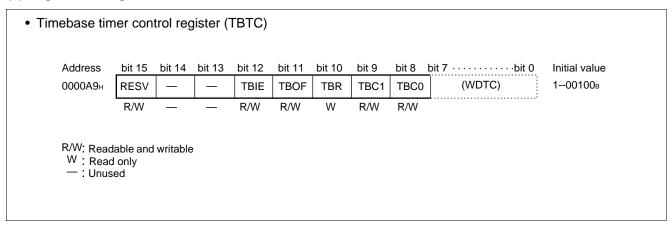

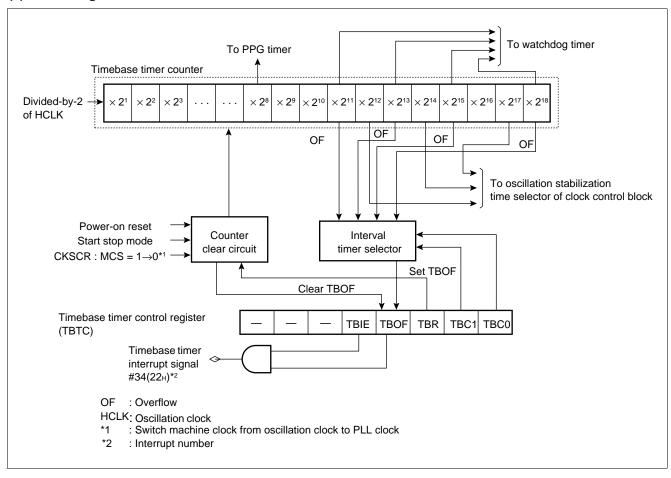

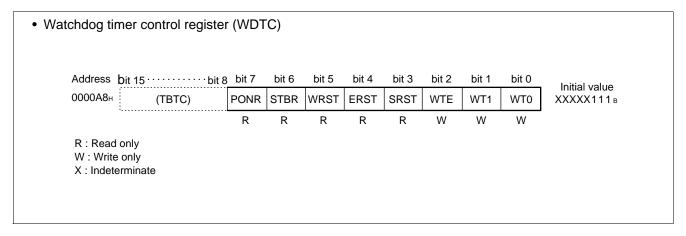

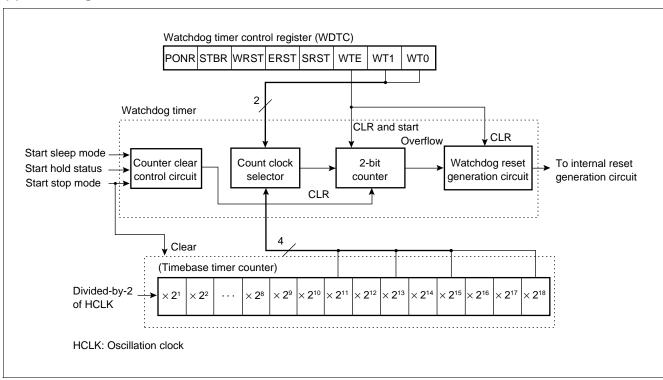

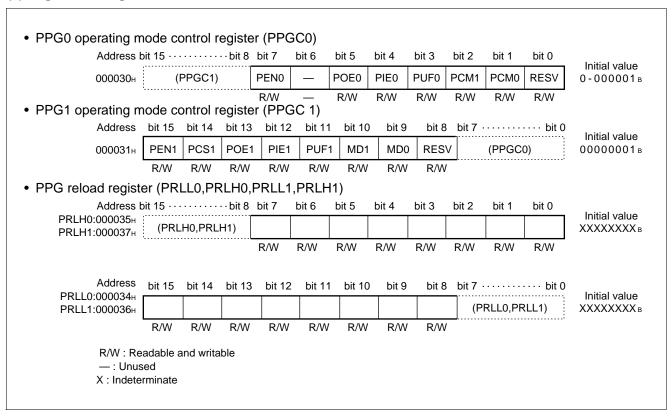

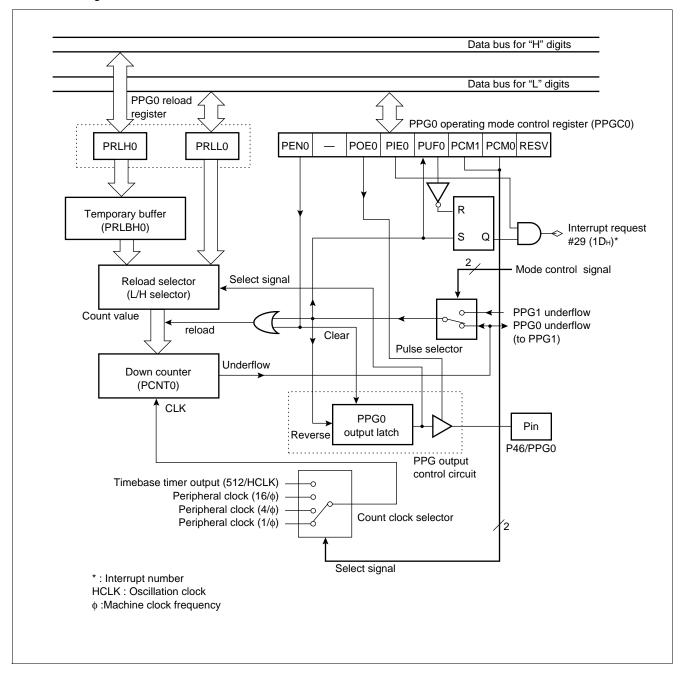

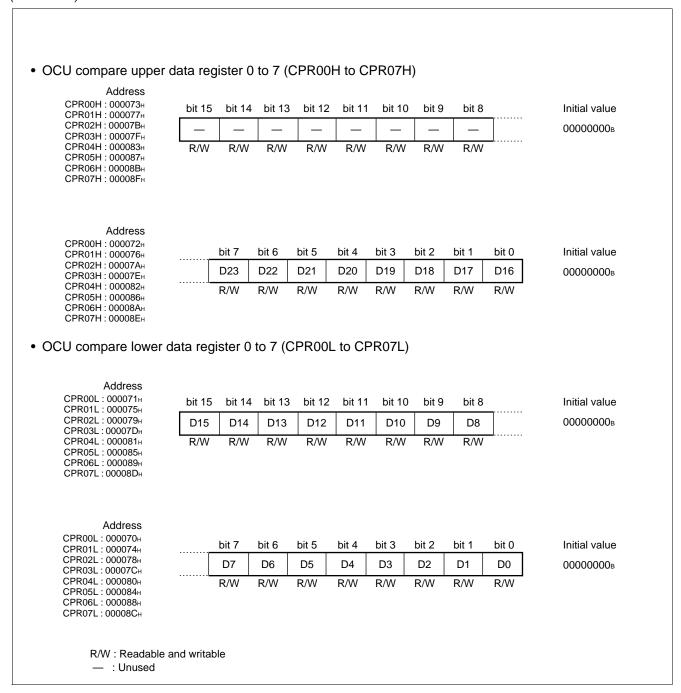

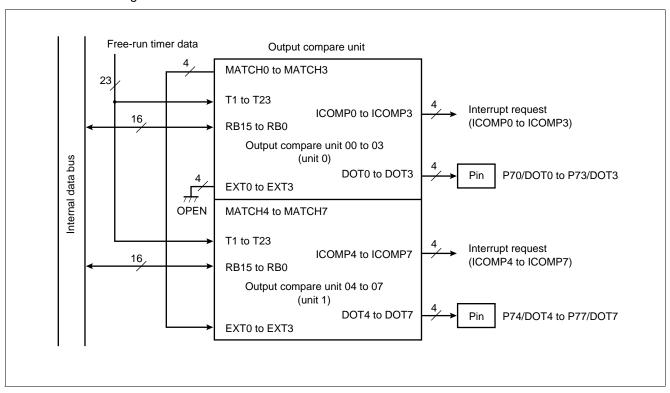

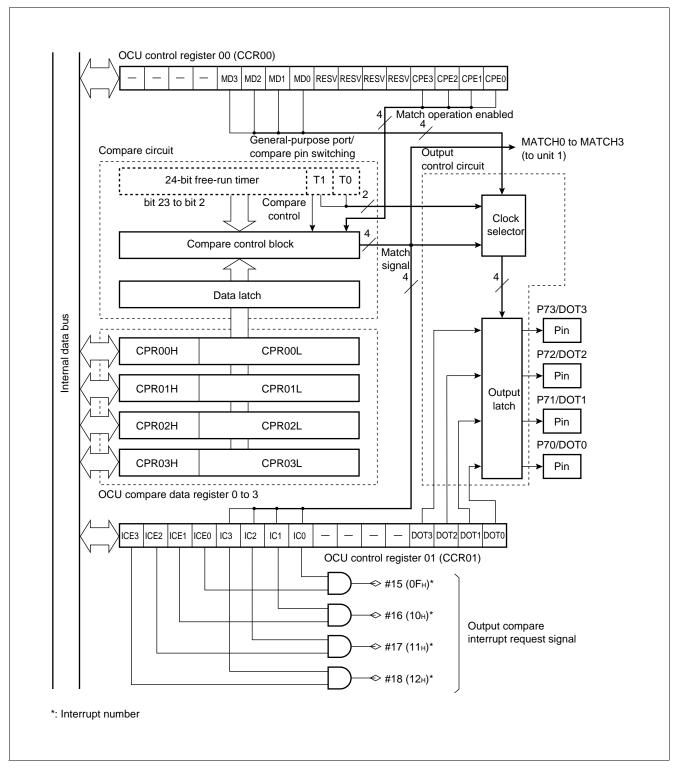

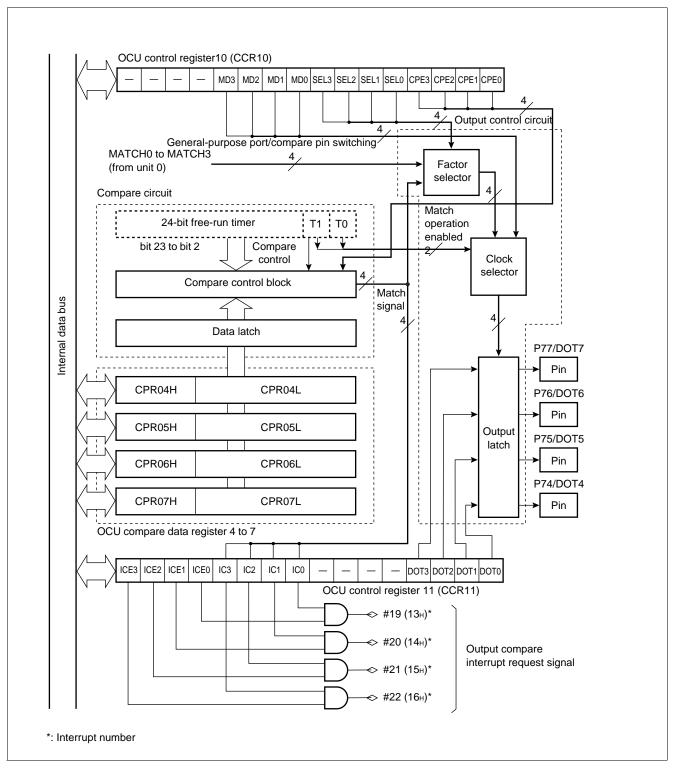

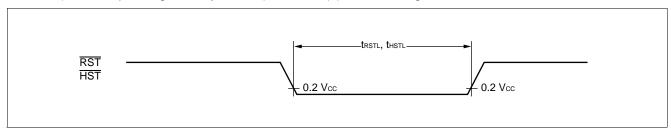

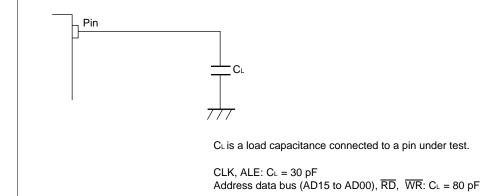

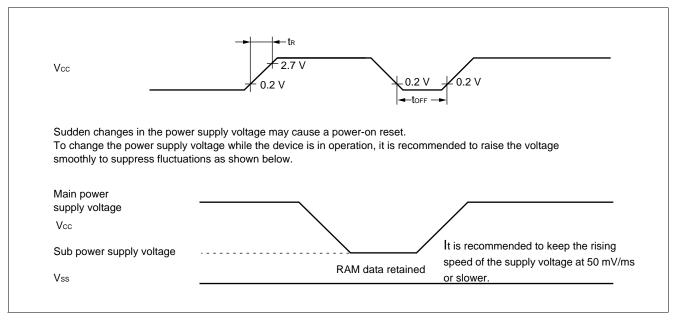

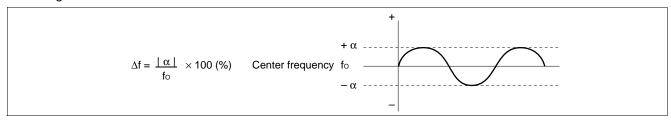

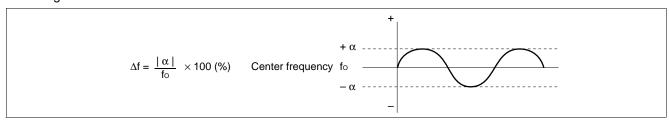

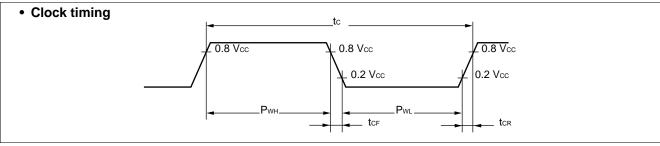

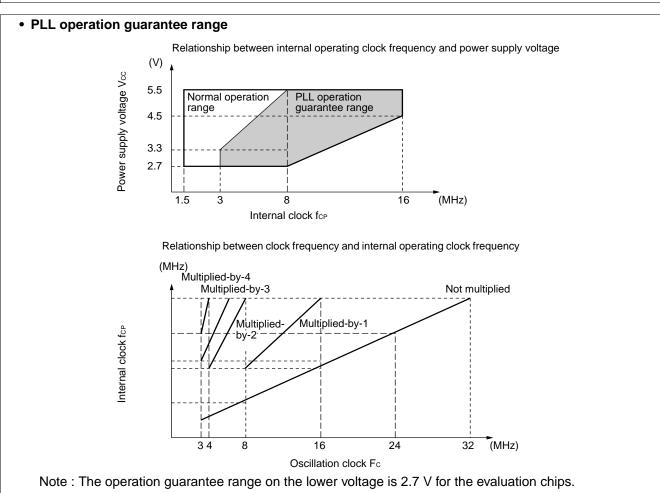

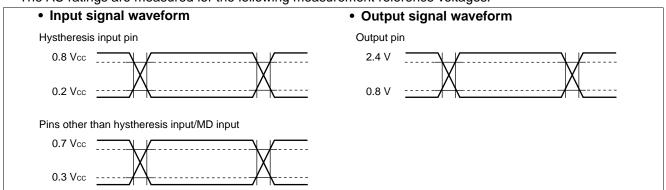

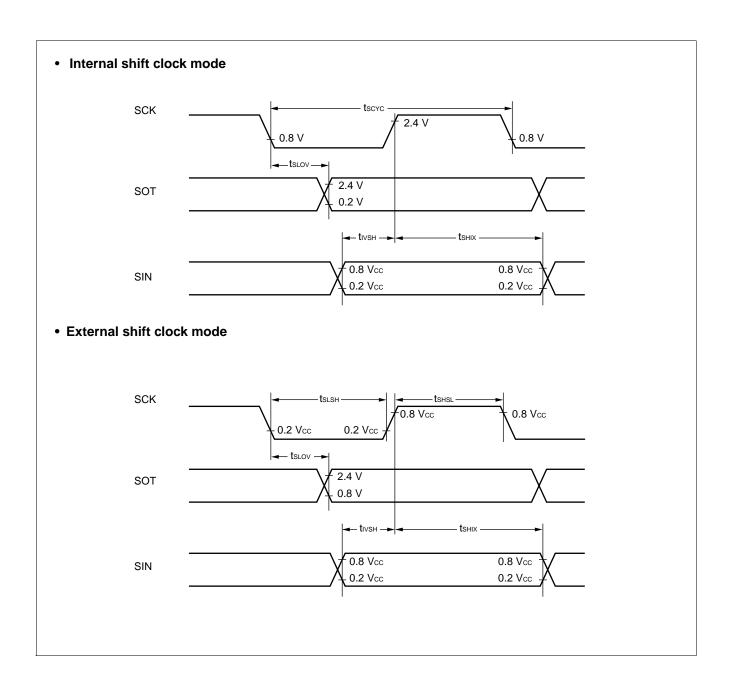

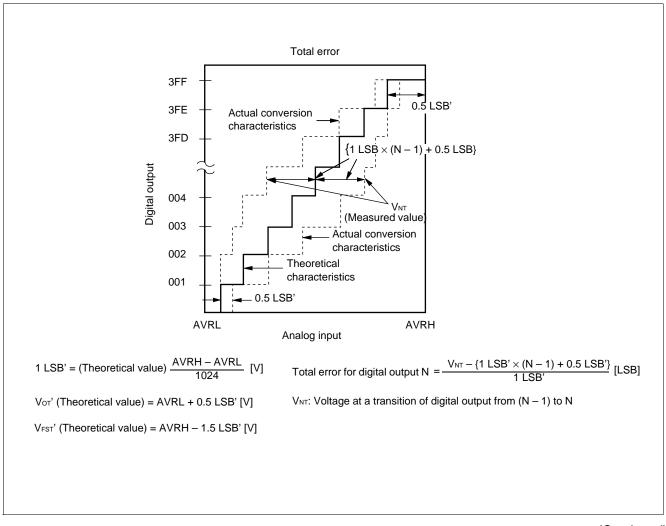

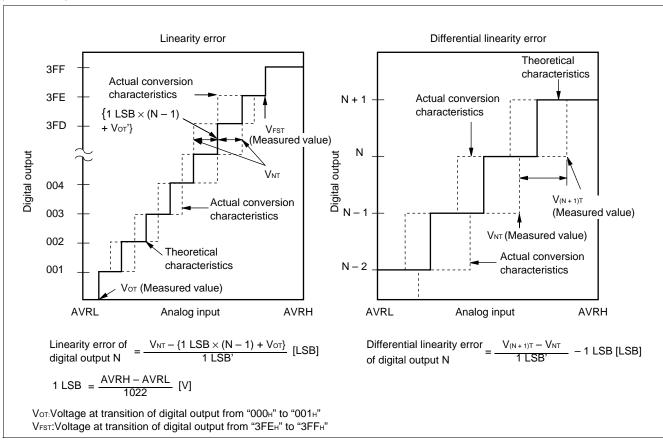

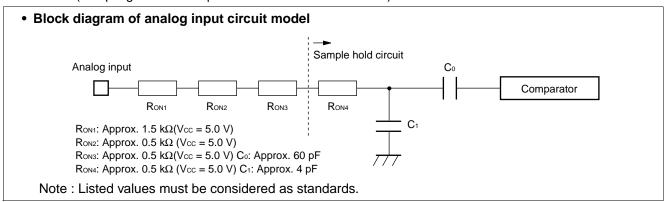

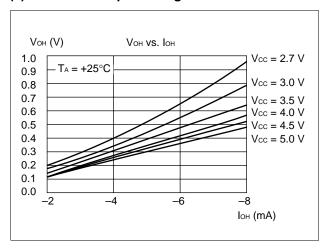

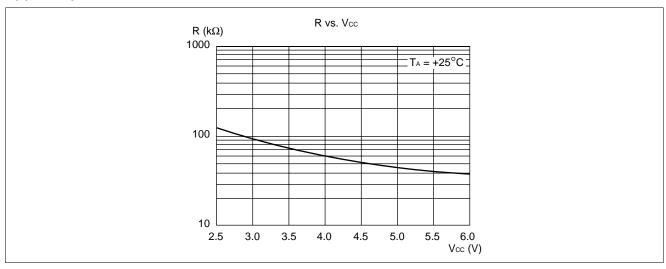

| 47 to 50           | 49 to 52     | 55 to 58           | 57 to 60           | ASR0 to<br>ASR3                      | E<br>(CMOS/H) | Sample data input pins for ICU0 to ICU3 Because this input is used as required when the input capture (ICU) is performing input operations, and it is necessary to stop outputs from other functions unless such outputs are made intentionally.                             |