# SEVEN CHANNEL E1 LINE INTERFACE UNIT WITH CLOCK RECOVERY

JULY 2001 REV. P1.0.3

## **GENERAL DESCRIPTION**

The XRT81L27 is an optimized seven-channel, analog, 3.3V, line interface unit, fabricated using low power CMOS technology. The device contains seven independent E1 channels, including data and clock recovery circuits. It is primarily targeted towards the SDH multiplexers that accomodate TU12 Tributary Unit Frames. Line cards in these units mutiplex 21 E1 channels into higher SDH rates. Devices with seven E1 interfaces such as the XRT81L27 provide the most efficient method of implementing 21-channel line cards. Each channel performs the driver and receiver functions necessary to convert bipolar signals to logical levels and vice versa.

The receiver input accepts transformer or capacitor coupled signals, while the transmitter is coupled to the line using a 1:2 step-up transformer. The same transformer configuration can be used for both balanced 120  $\Omega$  and unbalanced 75  $\Omega$  interfaces. The Receiver Loss of Signal Detection is compliant to G.775 and in Host Mode, the number of zeros received before LOS is declared can be increased to 4096 bits. This feature provides the user with the flexability to implement LOS specifications that require greater than G.775 requirements

#### **FEATURES**

- Consists of Seven (7) Independent E1 (CEPT) Line Interface Units (Transmitter and Receiver)

- Generates Transmit Output Pulses that are Compliant with the ITU-T G.703 Pulse Template Requirement for 2.048Mbps (E1) Rates

- On-Chip Pulse Shaping for both  $75\Omega$  and  $120\Omega$  line drivers

- Receiver Can Either Be Transformer or Capacitive-Coupled to the Line

- Detects and Clears LOS (Loss of Signal) Per ITU-T G.775

- Compliant with the ITU-T G.823 Jitter Tolerance Requirements

# **APPLICATIONS**

- IPDH Multiplexers

- SDH Multiplexers

- Digital Cross-Connect Systems

- DECT (Digital European Cordless Telephone) Base Stations

- CSU/DSU Equipment

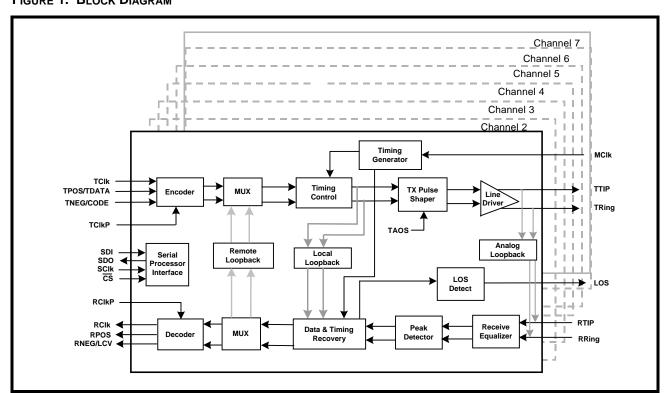

FIGURE 1. BLOCK DIAGRAM

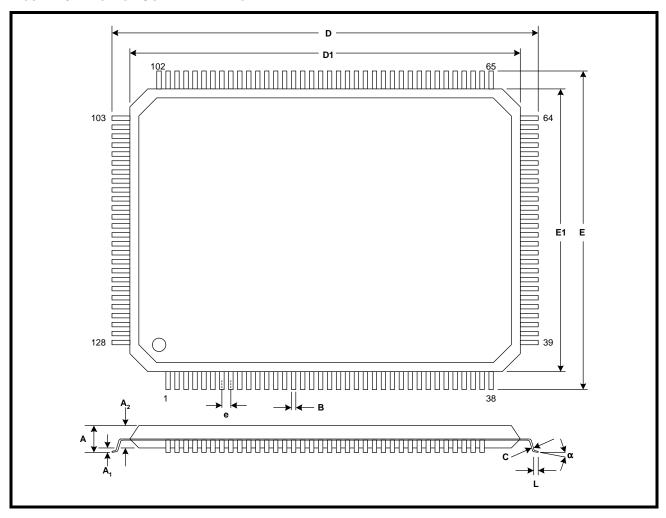

## ORDERING INFORMATION

| Part No.   | PACKAGE       | OPERATING TEMPERATURE RANGE |

|------------|---------------|-----------------------------|

| XRT81L27IV | 128 Lead TQFP | -40°C to +85°C              |

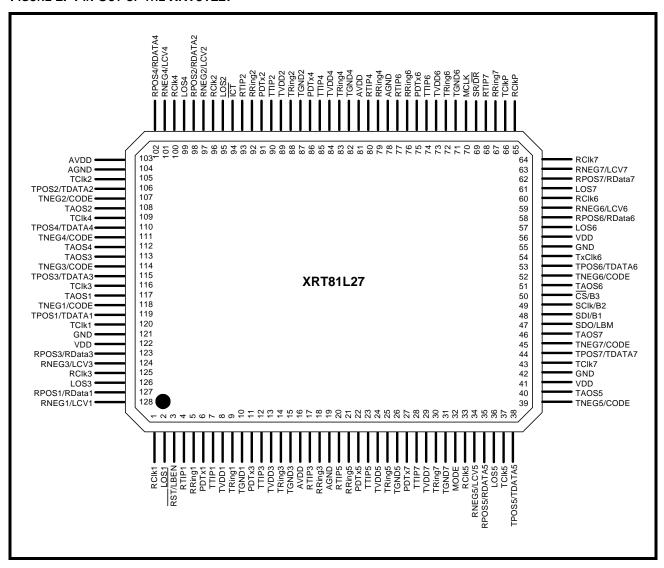

FIGURE 2. PIN OUT OF THE XRT81L27

# **TABLE OF CONTENTS**

| GENERAL DESCRIPTION                                                                                                                                  | <i>'</i> |

|------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| FEATURES                                                                                                                                             | 1        |

| APPLICATIONS                                                                                                                                         | 1        |

| Figure 1. Block Diagram                                                                                                                              | 1        |

| Ordering Information                                                                                                                                 |          |

| Figure 2. Pin Out of the XRT81L27                                                                                                                    | 2        |

| TABLE OF CONTENTS                                                                                                                                    |          |

| PIN DESCRIPTIONS                                                                                                                                     | 3        |

| TABLE 1: RECEIVER ELECTRICAL CHARACTERISTICS                                                                                                         | 12       |

| TABLE 2: TRANSMITTER ELECTRICAL CHARACTERISTICS                                                                                                      |          |

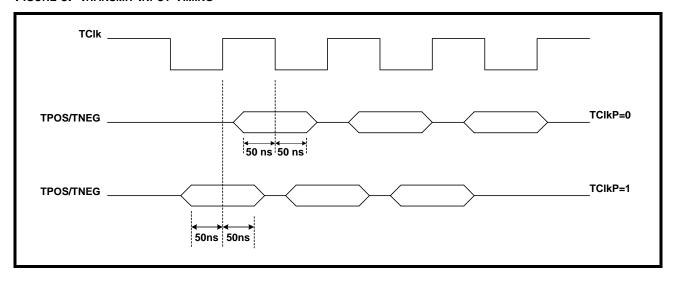

| Figure 3. Transmit Input Timing                                                                                                                      | 13       |

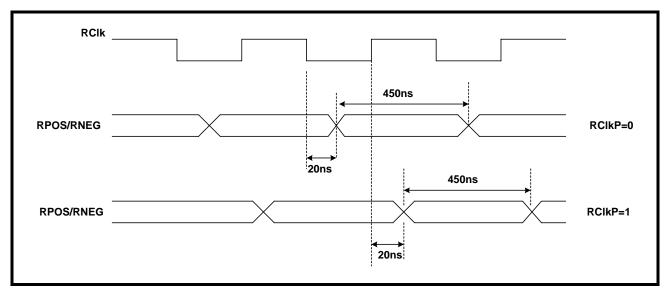

| Figure 4. Receive Output Timing                                                                                                                      | 14       |

| Table 3: DC Electrical Characteristics                                                                                                               | 14       |

| 1.0 The Microprocessor Serial Interface                                                                                                              |          |

| 1.1 DESCRIPTION OF THE COMMAND REGISTERS                                                                                                             |          |

| TABLE 4: MICROPROCESSOR REGISTER ADDRESS AND CONTROL                                                                                                 |          |

| Table 5: Register Control Bit Description                                                                                                            |          |

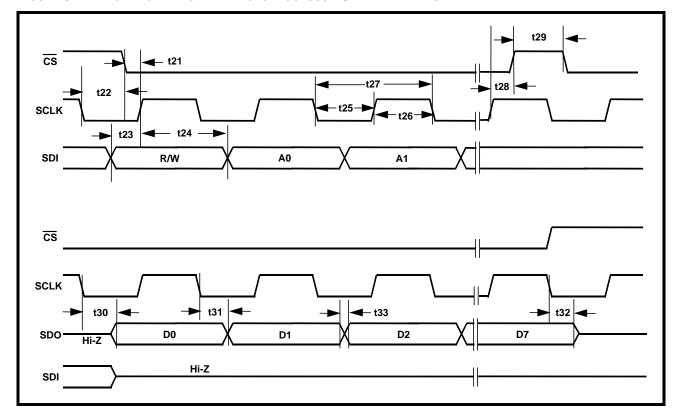

| Figure 5. Timing Diagram for the Microprocessor Serial Interface                                                                                     |          |

| MICROPROCESSOR SERIAL INTERFACE TIMING (SEE FIGURE 5)                                                                                                |          |

| Figure 6. Microprocessor Serial Interface Data Structure                                                                                             |          |

| Table 6: AC Electrical Characteristics                                                                                                               |          |

| TABLE 7: PER CHANNEL POWER CONSUMPTION INCLUDING LINE POWER DISSIPATION, TRANSMISSION AND RECE                                                       |          |

| PATHS ALL ACTIVE                                                                                                                                     |          |

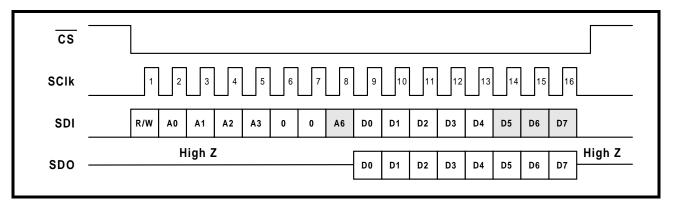

| Figure 7. Illustration of the ITU-T G.703 Pulse Template for E1 Applications                                                                         |          |

| 2.0 The Pulse Shaping Circuit                                                                                                                        | 21       |

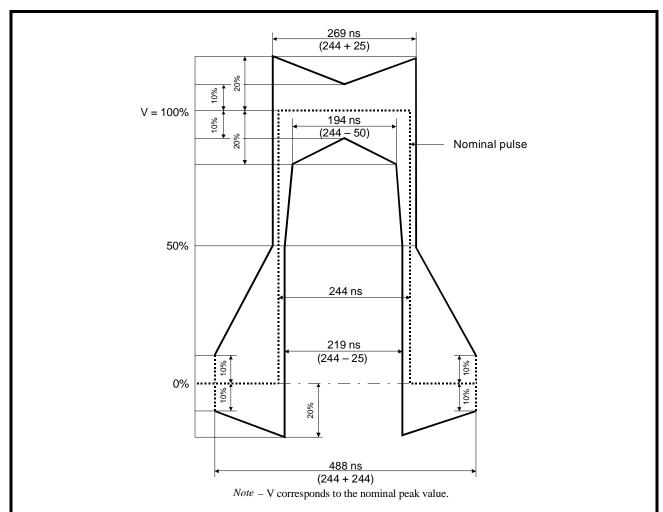

| 2.1 Interfacing the Transmit Sections of the XRT81L27 to the Line                                                                                    |          |

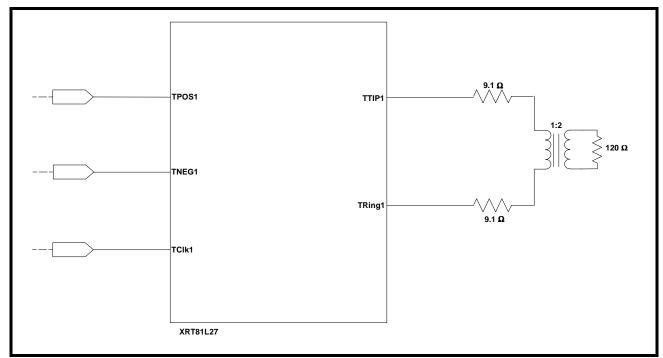

| Figure 8. Illustration of how to interface the Transmit Sections of the XRT81L27 to the Line (for 75W Appl                                           |          |

| tions)                                                                                                                                               |          |

| Figure 9. Illustration of how to interface the Transmit Sections the XRT81L27 to the Line (for 120W Applicati                                        | ,        |

| 3.0 The Receive Section                                                                                                                              |          |

| 3.1 Interfacing the Receive Sections to the Line                                                                                                     |          |

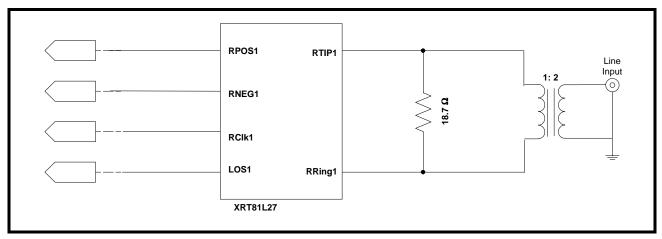

| Figure 10. Recommended Schematic for Interfacing the Receive Sections of the XRT81L27 to the Line for Table 10. Applications (Transferment Counting) |          |

| Applications (Transformer-Coupling)                                                                                                                  |          |

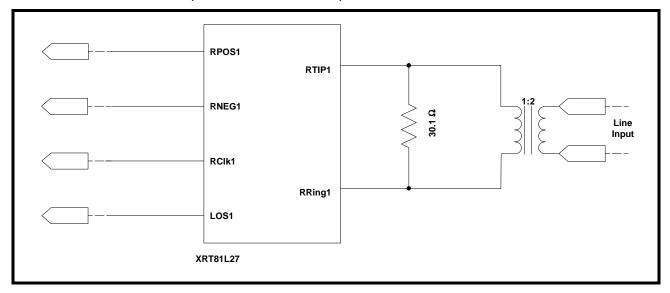

| Figure 11. Recommended Schematic for Interfacing the Receive Sections of the XRT81L27 to the Line for 12 Applications (Transformer-Coupling)         | 2000     |

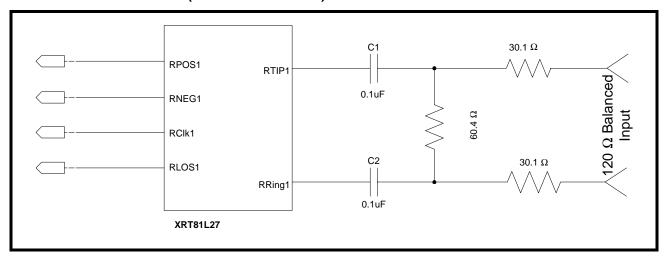

| Figure 12. Recommended Schematic for Interfacing the Receive Sections of the XRT81L27 to the Line for 12                                             |          |

|                                                                                                                                                      |          |

| Applications (Capacitive-Coupling)  3.2 The Receive Equalizer Bock                                                                                   |          |

| 3.3 THE PEAK DETECTOR AND SLICER BLOCK                                                                                                               | 24       |

| 3.4 THE LOS DETECTOR BLOCK                                                                                                                           |          |

| Figure 13. Package Outline Drawing                                                                                                                   |          |

| PEVICIONS                                                                                                                                            |          |

# **PIN DESCRIPTIONS**

| Pin# | NAME     | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                              |

|------|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | RClk1    | 0    | Receiver 1 Clock Output                                                                                                                                                                                                                                                                                                                  |

| 2    | LOS1     | 0    | Receiver 1 Loss of Signal: This signal is asserted High to indicate loss of signal at the receive input.                                                                                                                                                                                                                                 |

| 3    | RST/LBEN | I    | Reset (Active-low): In Host Mode, tie this pin "Low" to reset the serial register contents to zero. Loop-back Enable (Active-low): In Hardware Mode, when this pin is tied "Low", Loop-back mode is enabled. Notes:  1. See description of pin 47 to pin 50 for Local or Remote Loop-back selection. 2. Internally pulled-high with 50KΩ |

| 4    | RTIP1    | I    | Receiver 1 Bipolar Positive Input                                                                                                                                                                                                                                                                                                        |

| 5    | RRing1   | I    | Receiver 1 Bipolar Negative Input                                                                                                                                                                                                                                                                                                        |

| 6    | PDTx1    | I    | Powered-down Transmitter 1: This pin is operational for both Host or Hardware mode, tie this pin High to power-down channel 1 transmitter and set TTIP1 and TRing1 output to high impedance.  Note: Internally pulled-high with 50ΚΩ.                                                                                                    |

| 7    | TTIP1    | 0    | Transmitter 1 Tip Output: Positive bipolar data output to the line                                                                                                                                                                                                                                                                       |

| 8    | TVDD1    | ***  | Transmitter 1 Positive Supply (3.3V± 5%)                                                                                                                                                                                                                                                                                                 |

| 9    | TRing1   | 0    | Transmitter 1 Ring Output: Negative bipolar data output to the line.                                                                                                                                                                                                                                                                     |

| 10   | TGND1    | ***  | Transmitter 1 Supply Ground                                                                                                                                                                                                                                                                                                              |

| 11   | PDTx3    | I    | Powered-down Transmitter 3: This pin is operational for both <b>Host</b> or <b>Hardware mode</b> , tie this pin High to power-down channel 3 transmitter and set TTIP3 and TRing3 output to high impedance. <b>Note:</b> Internally pulled- high with 50KΩ                                                                               |

| 12   | TTIP3    | 0    | Transmitter 3 Tip Output: Positive bipolar data output to the line.                                                                                                                                                                                                                                                                      |

| 13   | TVDD3    | ***  | Transmitter 3 Positive Supply(3.3V± 5%)                                                                                                                                                                                                                                                                                                  |

| 14   | TRing3   | 0    | Transmitter 3 Ring Output: Negative bipolar data output to the line.                                                                                                                                                                                                                                                                     |

| 15   | TGND     | ***  | Transmitter 3 Supply Ground                                                                                                                                                                                                                                                                                                              |

| 16   | AVDD     | ***  | Analog Positive Supply(3.3V± 5%)                                                                                                                                                                                                                                                                                                         |

| 17   | RTIP3    | I    | Receiver 3 Bipolar Positive Input                                                                                                                                                                                                                                                                                                        |

| 18   | RRing3   | I    | Receiver 3 Bipolar Negative Input                                                                                                                                                                                                                                                                                                        |

| 19   | AGND     | ***  | Analog Supply Ground                                                                                                                                                                                                                                                                                                                     |

| 20   | RTIP5    | I    | Receiver 5 Bipolar Positive Input                                                                                                                                                                                                                                                                                                        |

# SEVEN CHANNEL E1 LINE INTERFACE UNIT WITH CLOCK RECOVERY

REV. P1.0.3

| PIN# | NAME         | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                |  |  |

|------|--------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 21   | RRing5       | I    | Receiver 5 Bipolar Negative Input                                                                                                                                                                                                                                                                                                                          |  |  |

| 22   | PDTx5        | I    | Powered-down Transmitter 5: This pin is operational for both Host or Hardware mode, tie this pin High to power-down channel 5 transmitter and set TTIP5 and TRing5 output to high impedance.  Note: Internally pulled- high with 50ΚΩ                                                                                                                      |  |  |

| 23   | TTIP5        | 0    | Transmitter 5 Tip Output: Positive bipolar data output to the line.                                                                                                                                                                                                                                                                                        |  |  |

| 24   | TVDD5        | **** | Transmitter 5 Positive Supply(3.3V± 5%)                                                                                                                                                                                                                                                                                                                    |  |  |

| 25   | TRing5       | 0    | Transmitter 5 Ring Output: Negative bipolar data output to the line.                                                                                                                                                                                                                                                                                       |  |  |

| 26   | TGND5        | **** | Transmitter 5 Supply Ground                                                                                                                                                                                                                                                                                                                                |  |  |

| 27   | PDTx7        |      | Powered-down Transmitter 7: This pin is operational for both Host or Hardware mode, tie this pin High to power-down channel 7 transmitter and set TTIP7 and TRing7 output to high impedance.  Note: Internally pulled- high with $50KΩ$                                                                                                                    |  |  |

| 28   | TTIP7        | 0    | Transmitter 7 Tip Output: Positive bipolar data output to the line.                                                                                                                                                                                                                                                                                        |  |  |

| 29   | TVDD7        | **** | Transmitter 7 Positive Supply(3.3V± 5%)                                                                                                                                                                                                                                                                                                                    |  |  |

| 30   | TRing7       | 0    | Transmitter 7 Ring Output: Negative bipolar data output to the line.                                                                                                                                                                                                                                                                                       |  |  |

| 31   | TGND7        | ***  | Transmitter 7 Supply Ground                                                                                                                                                                                                                                                                                                                                |  |  |

| 32   | MODE         | I    | Mode Control Input: This pin is used for selecting Hardware Mode or Host Mode control of the device. Left this pin unconnected or tie Low to select Host Mode and tie this pin High to select Hardware mode.  Note: Internally pulled-down with 50KΩ.                                                                                                      |  |  |

| 33   | RClk5        | 0    | Receiver 5 Clock Output                                                                                                                                                                                                                                                                                                                                    |  |  |

| 34   | RNEG5/LCV5   | 0    | Receiver 5 Negative Data Output: In dual-rail mode, this signal is the receive n-rail output data. Line Code Violation Output: In single-rail mode, this signal output High for one clock cycle to indicate a code violation is detected in the received data. If AMI coding is selected, every bipolar violation received will cause this pin to go High. |  |  |

| 35   | RPOS5/RDATA5 | 0    | Receiver 5 Positive Data Output: In dual-rail mode, this signal is the receive p-rail output data. Receiver 5 NRZ Data Output: In single-rail mode, this signal is the receive output data                                                                                                                                                                 |  |  |

| 36   | LOS5         | 0    | Receiver 5 Loss of Signal: This signal is asserted High to indicate loss of signal at the receive input.                                                                                                                                                                                                                                                   |  |  |

| 37   | TClk5        | I    | Transmitter 5 Clock Input:<br>E1 rate at 2.048MHz ± 50ppm.                                                                                                                                                                                                                                                                                                 |  |  |

| Pin # | NAME         | ТҮРЕ | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|-------|--------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 38    | TPOS5/TDATA5 | I    | Transmitter 5 Positive Data Input: In dual-rail mode, this signal is the p-rail input data for transmitter 5. Transmitter 5 NRZ Data Input: In single-rail mode, this signal is used as the NRZ input data for transmitter 5.                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 39    | TNEG5/CODE   | I    | Transmitter 5 Negative Data Input: In dual-rail mode, this signal is the n-rail data input for transmitter 5. In single-rail mode (pin 69 = "1") and with this pin tied High, input data at the transmit input is encoded in HDB3 format and the substitution code in the corresponding receive channel will be removed. Tie this pin Low to enable AMI encoding and decoding.  Note: Internally pulled-down with $50KΩ$ .                                                                                                                                                       |  |  |

| 40    | TAOS5        | I    | Transmit All Ones: This pin is set to insert AMI all ones data to the line using MCLK as reference. In Host Mode, this pin can be left unconnected. Note: Internally pulled-down with $50K\Omega$                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| 41    | VDD          | **** | Digital Positive Supply(3.3V± 5%).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 42    | GND          | **** | Digital Supply Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 43    | TClk7        | I    | Transmitter 7 Clock Input:<br>E1 rate at 2.048MHz ± 50ppm.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 44    | TPOS7/TDATA7 | I    | Transmitter 7 Positive Data Input: In dual-rail mode, this signal is the p-rail input data for transmitter 7. Transmitter 7 NRZ Data Input: In single-rail mode, this signal is used as the NRZ input data for transmitter 7.                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 45    | TNEG7/CODE   | I    | Transmitter 7 Negative Data Input: In dual-rail mode, this signal is the n-rail data input for transmitter 7. See pin 39 description for single-rail mode operation.  Note: Internally pulled-down with 50KΩ.                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 46    | TAOS7        | I    | Transmit All Ones: This pin is set to insert AMI all ones data to the line using MCLK as reference. In Host Mode, this pin can be left unconnected.  Note: Internally pulled- down with 50KΩ.                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 47    | SDO/LBM      | 0    | Serial Data Output: In Host Mode, this pin is the Serial Data Output port for the Microprocessor Serial Interface access. This pin serially outputs the contents of the specified Command Register during Read Operations. The data on this pin is updated on the falling edge of the SCLK input signal. This pin is tri-stated upon completion of data transfer.  Loop-back Mode: In Hardware Mode, when this pin is tied High, Analog Local loop-back is selected. Connect this pin Low to select remote loop-back. Digital Local loop-back is not supported in Hardware mode. |  |  |

# SEVEN CHANNEL E1 LINE INTERFACE UNIT WITH CLOCK RECOVERY

**PRELIMINARY**

REV. P1.0.3

| Pin# | NAME         | TYPE |                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DESCR                                                                                                                        | IPTION                                                                                                                 |                                                                                                                           |                                                                        |

|------|--------------|------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| 48   | SDI/B1       | I    | In Host Mod This pin is u Microproces the Comman tions are ap This input is In Hardwar bits used to | Input Port for de, this pin is a seed to read or seed to read or seed to read or seed to this pin is sampled on the Mode, B1, the select which or Analog or Re    Loop-back   Cop-back   Co | the serial dat<br>r write data ir<br>erface. The<br>and Data Valu<br>in.<br>the rising edg<br>cogether with<br>one of the se | a input port<br>nto the Com<br>Read/Write<br>ue to be wri-<br>ge of the SC<br>B2 (pin49)<br>ven channe<br>ack is deter | (see Figure 5<br>mand Registe<br>bit, the Addre<br>tten during W<br>LK pin (pin 48<br>and B3 (pin 50<br>Is is to be place | ers of the ess Values of rite Opera-  9).  0) are control ced in Loop- |

| 49   | SClk/B2      | I    | In Host Mod<br>clock signal.<br>Interface up<br>In Hardward                                         | essor Serial Inde, The data of Additionally, dates the SDO e Mode, B2, to fithe seven chon)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | on the SDI pir<br>during Read<br>O output on tl<br>ogether with                                                              | n is sampled<br>operations t<br>he falling ed<br>B1 and B3 a                                                           | the Microproc<br>Ige of this signare control bits                                                                         | essor Serial<br>nal.<br>s to select                                    |

| 50   | CS/B3        | I    | tion with the                                                                                       | de, this pin mu<br>device via the<br>e Mode, B3, to<br>of the seven ch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | e Serial Intertogether with                                                                                                  | face.<br>B1 and B2 a                                                                                                   | are control bit                                                                                                           | s to select                                                            |

| 51   | TAOS6        | I    | ence.<br>In <b>Host Mo</b>                                                                          | II Ones: et to insert AM de, this pin ca rnally pulled-d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | n be left unco                                                                                                               | onnected.                                                                                                              | e using MCL                                                                                                               | ⟨ as refer-                                                            |

| 52   | TNEG6/CODE   | I    | In dual-rail r<br>See pin 39                                                                        | r 6 Negative I<br>mode, this sign<br>description fo<br>rnally pulled-c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | nal is the n-ra<br>r single-rail m                                                                                           | node operat                                                                                                            |                                                                                                                           | er 6.                                                                  |

| 53   | TPOS6/TDATA6 | I    | In dual-rail n<br>Transmitter                                                                       | r 6 Positive D<br>mode, this sign<br>r 6 NRZ Data<br>I mode this sig                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | nal is the p-ra                                                                                                              | •                                                                                                                      |                                                                                                                           |                                                                        |

| 54   | TClk6        | I    |                                                                                                     | r <b>6 Clock Inp</b> u<br>.048MHz ± 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                              |                                                                                                                        |                                                                                                                           |                                                                        |

REV. P1.0.3

| PIN# | NAME         | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                |  |  |

|------|--------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 55   | GND          | **** | Digital Supply Ground                                                                                                                                                                                                                                                                                                                                      |  |  |

| 56   | VDD          | **** | Digital Positive Supply(3.3V± 5%)                                                                                                                                                                                                                                                                                                                          |  |  |

| 57   | LOS6         | 0    | Receiver 6 Loss of Signal: This signal is asserted High to indicate loss of signal at the receive input.                                                                                                                                                                                                                                                   |  |  |

| 58   | RPOS6/RDATA6 | 0    | Receiver 6 Positive Data Output: In dual-rail mode, this signal is the receive p-rail output data. Receiver 6 NRZ Data Output: In single-rail mode, this signal is the receive output data.                                                                                                                                                                |  |  |

| 59   | RNEG6/LCV6   | 0    | Receiver 6 Negative Data Output: In dual-rail mode, this signal is the receive n-rail output data. Line Code Violation Output: In single-rail mode, this signal output High for one clock cycle to indicate a code violation is detected in the received data. If AMI coding is selected, every bipolar violation received will cause this pin to go High. |  |  |

| 60   | RClk6        | 0    | Receiver 6 Clock Output                                                                                                                                                                                                                                                                                                                                    |  |  |

| 61   | LOS7         | 0    | Receiver 7 Loss of Signal: This signal is asserted High to indicate loss of signal at the receive input.                                                                                                                                                                                                                                                   |  |  |

| 62   | RPOS7/RDATA7 | 0    | Receiver 7 Positive Data Output: In dual-rail mode, this signal is the receive p-rail output data. Receiver 7 NRZ Data Output: In single-rail mode, this signal is the receive output data.                                                                                                                                                                |  |  |

| 63   | RNEG7/LCV7   | 0    | Receiver 6 Negative Data Output: In dual-rail mode, this signal is the receive n-rail output data. Line Code Violation Output: In single-rail mode, this signal output High for one clock cycle to indicate a code violation is detected in the received data. If AMI coding is selected, every bipolar violation received will cause this pin to go High. |  |  |

| 64   | RClk7        | 0    | Receiver 7 Clock Output                                                                                                                                                                                                                                                                                                                                    |  |  |

| 65   | RCIkP        | I    | Receiver Clock Output Polarity: In Hardware Mode and with this pin tied to Low, All channels RPOS /RDATA and RNEG/LCV output data are updated on the falling edge of RClk. Tie this pin High to select data update on rising edge of RClk. Note: Internally pulled-down with $50 \mathrm{K}\Omega$                                                         |  |  |

| 66   | TCIkP        | I    | Transmit Clock Polarity: In Hardware Mode and with this pin tied to Low, transmit input data is sampled using the falling edge of TClk. Tie this pin High to select rising edge of TClk for data sampling.  Note: Internally pulled-down with $50K\Omega$ .                                                                                                |  |  |

| 67   | RRING7       | I    | Receiver 7 Bipolar Negative Input                                                                                                                                                                                                                                                                                                                          |  |  |

| 68   | RTIP7        | I    | Receiver 7 Bipolar Positive Input                                                                                                                                                                                                                                                                                                                          |  |  |

| 69   | SR/DR        | I    | Single-rail/Dual-rail Select: In Hardware Mode and with this pin tied to High, input transmit data and receive output data is selected for single-rail mode operation. Tie this pin Low to select dual-rail mode.  Note: Internally pulled-down with 50ΚΩ                                                                                                  |  |  |

# SEVEN CHANNEL E1 LINE INTERFACE UNIT WITH CLOCK RECOVERY

REV. P1.0.3

| PIN# | NAME   | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                   |  |

|------|--------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 70   | MClk   | I    | Master Clock Input: This signal is an independent 2.048MHz clock with accuracy better than ±50ppm and duty cycle within 40% to 60%. The function of MCLK is to provide timing source for the PLL clock recovery circuit, reference clock to inser All Ones data in the transmit as well as the receive paths. |  |

| 71   | TGND6  | ***  | Transmitter 6 Supply Ground                                                                                                                                                                                                                                                                                   |  |

| 72   | TRing6 | 0    | Transmitter 6 Ring Output: Negative bipolar data output to the line                                                                                                                                                                                                                                           |  |

| 73   | TVDD6  | ***  | Transmitter 6 Positive Supply (3.3V± 5%)                                                                                                                                                                                                                                                                      |  |

| 74   | TTIP6  | 0    | TTIP6 O Transmitter 6 Tip Output: Positive bipolar data output to the line.                                                                                                                                                                                                                                   |  |

| 75   | PDTx6  | I    | Powered-down Transmitter 6: This pin is operational for both Host or Hardware mode, tie this pin High to power-down channel 6 transmitter and set TTIP6 and TRing6 output to high impedance.                                                                                                                  |  |

| 76   | RRing6 | I    | Receiver 6 Bipolar Negative Input                                                                                                                                                                                                                                                                             |  |

| 77   | RTIP6  | I    | Receiver 6 Bipolar Positive Input                                                                                                                                                                                                                                                                             |  |

| 78   | AGND   | ***  | Analog Supply Ground                                                                                                                                                                                                                                                                                          |  |

| 79   | RRing4 | I    | Receiver 4 Bipolar Negative Input                                                                                                                                                                                                                                                                             |  |

| 80   | RTIP4  | -    | Receiver 4 Bipolar Positive Input                                                                                                                                                                                                                                                                             |  |

| 81   | AVDD   | ***  | Analog Positive Supply(3.3V± 5%)                                                                                                                                                                                                                                                                              |  |

| 82   | TGND4  | ***  | Transmitter 4 Supply Ground                                                                                                                                                                                                                                                                                   |  |

| 83   | TRing4 | 0    | Transmitter 4 Ring Output: Negative bipolar data output to the line.                                                                                                                                                                                                                                          |  |

| 84   | TVDD4  | ***  | Transmitter 4 Positive Supply(3.3V± 5%)                                                                                                                                                                                                                                                                       |  |

| 85   | TTIP4  | 0    | Transmitter 4 Tip Output: Positive bipolar data output to the line.                                                                                                                                                                                                                                           |  |

| 86   | PDTx4  | I    | Powered-down Transmitter 4: This pin is operational for both Host or Hardware mode, tie this pin High to power-down channel 4 transmitter and set TTIP4 and TRing4 output to high impedance.  Note: Internally pulled- high with 50ΚΩ                                                                         |  |

| 87   | TGND2  | ***  | Transmitter 2 Supply Ground                                                                                                                                                                                                                                                                                   |  |

| 88   | TRing2 | 0    | Transmitter 2 Ring Output: Negative bipolar data output to the line.                                                                                                                                                                                                                                          |  |

| 89   | TVDD2  | ***  | Transmitter 2 Positive Supply(3.3V± 5%)                                                                                                                                                                                                                                                                       |  |

| 90   | TTIP2  | 0    | Transmitter 2 Tip Output: Positive bipolar data output to the line.                                                                                                                                                                                                                                           |  |

REV. P1.0.3

| P |                  | , , |    | A I I | A I | Λ  | V |

|---|------------------|-----|----|-------|-----|----|---|

|   | $\boldsymbol{r}$ |     | IV |       | M.  | Α. | - |

| PIN# | NAME         | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                |

|------|--------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 91   | PDTx2        | I    | Powered-down Transmitter 2: This pin is operational for both Host or Hardware mode, tie this pin High to power-down channel 2 transmitter and set TTIP2 and Tring2 output to high impedance.  Note: Internally pulled-high with 50ΚΩ.                                                                                                                      |

| 92   | RRing2       | I    | Receiver 2 Bipolar Negative Input                                                                                                                                                                                                                                                                                                                          |

| 93   | RTIP2        | I    | Receiver 2 Bipolar Positive Input                                                                                                                                                                                                                                                                                                                          |

| 94   | īст          | I    | In-Circuit Testing (Active Low): When this pin is tied to Low, all output pins are forced to high impedance state for in-circuit testing.  Note: Internally pulled High with 50ΚΩ.                                                                                                                                                                         |

| 95   | LOS2         | 0    | Receiver 2 Loss of Signal: This signal is asserted High to indicate loss of signal at the receive input.                                                                                                                                                                                                                                                   |

| 96   | RClk2        | 0    | Receiver 2 Clock Output                                                                                                                                                                                                                                                                                                                                    |

| 97   | RNEG2/LCV2   | 0    | Receiver 2 Negative Data Output: In dual-rail mode, this signal is the receive n-rail output data. Line Code Violation Output :In single-rail mode, this signal output High for one clock cycle to indicate a code violation is detected in the received data. If AMI coding is selected, every bipolar violation received will cause this pin to go High. |

| 98   | RPOS2/RDATA2 | 0    | Receiver 2 Positive Data Output: In dual-rail mode, this signal is the receive p-rail output data. Receiver 2 NRZ Data Output: In single-rail mode, this signal is the receive output data.                                                                                                                                                                |

| 99   | LOS4         | 0    | Receiver 4 Loss of Signal: This signal is asserted High to indicate loss of signal at the receive input.                                                                                                                                                                                                                                                   |

| 100  | RClk4        | 0    | Receiver 4 Clock Output                                                                                                                                                                                                                                                                                                                                    |

| 101  | RNEG4/LCV4   | 0    | Receiver 4 Negative Data Output: In dual-rail mode, this signal is the receive n-rail output data. Line Code Violation Output: In single-rail mode, this signal output High for one clock cycle to indicate a code violation is detected in the received data. If AMI coding is selected, every bipolar violation received will cause this pin to go High. |

| 102  | RPOS4/RDATA4 | 0    | Receiver 4 Positive Data Output: In dual-rail mode, this signal is the receive p-rail output data. Receiver 4 NRZ Data Output: In single-rail mode, this signal is the receive output data.                                                                                                                                                                |

| 103  | AVDD         | ***  | Analog Positive Supply(3.3V± 5%)                                                                                                                                                                                                                                                                                                                           |

| 104  | AGND         | ***  | Analog Supply Ground                                                                                                                                                                                                                                                                                                                                       |

| 105  | TClk2        | I    | Transmitter 2 Clock Input:<br>E1 rate at 2.048MHz ± 50ppm.                                                                                                                                                                                                                                                                                                 |

| 106  | TPOS2/TDATA2 | I    | Transmitter 2 Positive Data Input: In dual-rail mode, this signal is the p-rail input data for transmitter 2. Transmitter 2 NRZ Data Input: In single-rail mode, this signal is used as the NRZ input data for transmitter 2.                                                                                                                              |

| Pin # | NAME         | TYPE | DESCRIPTION                                                                                                                                                                                                                   |

|-------|--------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 107   | TNEG2/CODE   | I    | Transmitter 2 Negative Data Input: In dual-rail mode, this signal is the n-rail data input for transmitter 2. See pin 39 description for single-rail mode operation.  Note: Internally pulled-down with 50KΩ.                 |

| 108   | TAOS2        | I    | Transmit All Ones: This pin is set to insert AMI all ones data to the line using MCLK as reference. In Host Mode, this pin can be left unconnected. Note: Internally pulled-down with $50K\Omega$ .                           |

| 109   | TClk4        | I    | Transmitter 4 Clock Input:<br>E1 rate at 2.048MHz ± 50ppm.                                                                                                                                                                    |

| 110   | TPOS4/TDATA4 | I    | Transmitter 4 Positive Data Input: In dual-rail mode, this signal is the p-rail input data for transmitter 4. Transmitter 4 NRZ Data Input: In single-rail mode, this signal is used as the NRZ input data for transmitter 4. |

| 111   | TNEG4/CODE   | I    | Transmitter 4 Negative Data Input: In dual-rail mode, this signal Is the n-rail data input for the transmitter 4. See pin 39 description for single-rail mode operation. Note: Internally pulled-down with 50K $\Omega$       |

| 112   | TAOS4        | I    | Transmit All Ones: This pin is set to insert AMI all ones data to the line using MCLK as reference. In Host Mode, this pin can be left unconnected.  Note: Internally pulled-down with 50ΚΩ.                                  |

| 113   | TAOS3        | I    | Transmit All Ones: This pin is set to insert AMI all ones data to the line using MCLK as reference. In Host Mode, this pin can be left unconnected.  Note: Internally pull-down with 50ΚΩ                                     |

| 114   | TNEG3/CODE   | I    | Transmitter 3 Negative Data Input: In dual-rail mode, this signal is the n-rail data input for transmitter 3. See pin 39 description for single-rail mode operation.  Note: Internally pulled-down with 50ΚΩ.                 |

| 115   | TPOS3/TDATA3 | I    | Transmitter 3 Positive Data Input: In dual-rail mode, this signal is the p-rail input data for transmitter 3. Transmitter 3 NRZ Data Input: In single-rail mode, this signal is used as the NRZ input data for transmitter 3. |

| 116   | TClk3        | I    | Transmitter 3 Clock Input:<br>E1 rate at 2.048MHz ± 50ppm.                                                                                                                                                                    |

| 117   | TAOS1        | ı    | Transmit All Ones: This pin is set to insert AMI all ones data to the line using MCLK as reference. In Host Mode, this pin can be left unconnected. Note: Internally pulled-down with $50K\Omega$ .                           |

| 118   | TNEG1/CODE   | I    | Transmitter 1 Negative Data Input: In dual-rail mode, this signal is the n-rail data input for transmitter 1. See pin 39 description for single-rail mode operation.  Note: Internally pulled-down with 50ΚΩ.                 |