# VP-1606 Digital Voice Processor

#### **FEATURES**

- Plays messages stored in external EPROM chips

- CVSD technique with adjustable sampling rate from 16K to 128K bps for different voice quality

- Direct access to 64 segments, more segments are possible with external decoding circuitry

- Built-in RC oscillator or use external clock

# **GENERAL DESCRIPTIONS**

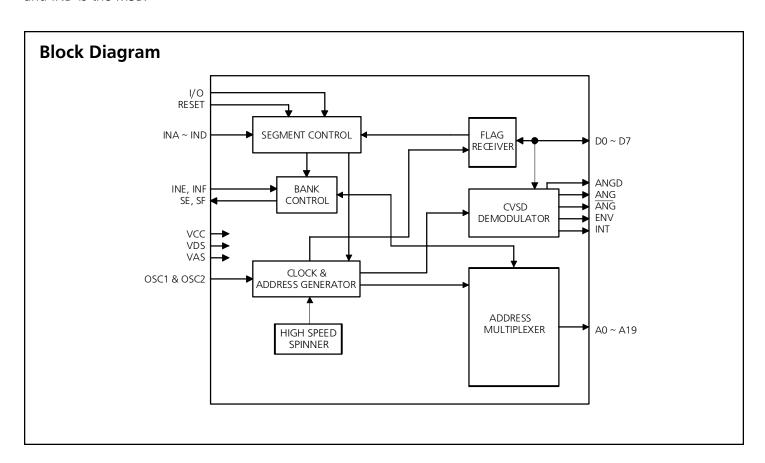

The VP-1606 is a CMOS LSI speech processor chip based on the CVSD (Continuously Variable Slope Delta) modulation technique. The VP-1606 is designed to replace the combination of the VP1000 and the VP1600. It also provides extended direct EPROM addressing (up to 8M bits), with possible expansion.

The VP1606 can randomly access and play back up to 64 sound segments (or messages) stored in 4 EPROM banks, with up to 16 segments in each bank.

- Direct EPROM addressing up to 8M bits, easy memory expansion with external bank switching

- Low power, single voltage operation

- Microprocessor interface

- Low-cost VP-880 system available for quick and easy voice development

Each segment stored in the EPROM is represented by a unique binary code: 2 bits for the bank code and 4 bits for the segment code. A valid code plus a strobe signal are all it takes to activate a certain segment.

The VP-1606 can operate within a wide range of sampling rates (from 16 to 128 Kbps). A higher sampling rate usually produces a better sound quality at the expense of higher memory cost. As a rule of thumb, start with the standard 32 Kbps rate. A 1M EPROM can store 32 seconds of sound at this rate.

Thanks to the chip's high internal integration, very little external components are required to build a VP-1606 based design. Also, the VP880 Voice Development System is available for quick and easy in-house voice development and programming. Therefore the VP-1606 is an ideal choice for both high-end and low-end applications.

# **APPLICATIONS**

- Voice memo recorder

- Sound effects generator

- Digital announcer for consumer, industrial, security and telecommunication products

**Eletech Enterprise Co., Ltd.** 531-3F Chung-Cheng Road

531-3F Chung-Cheng Road Hsin Tien, Taipei Hsien, Taiwan Tel:+886 2-2218-0068 Fax:+886 2-2218-0254 http://www.eletech.com

ELETECH

Eletech Electronics, Inc.

16019 Kaplan Avenue Industry, CA 91744, U.S.A.

Tel: (626) 333-6394 Fax: (626) 333-6494

# **ABSOLUTE MAXIMUM RATINGS\***

| Supply Voltage, V <sub>CC</sub> - V <sub>DS</sub> | 0 to 5.5V            |

|---------------------------------------------------|----------------------|

| Input Volotage, V <sub>IN</sub>                   | $V_{DS}$ to $V_{CC}$ |

| Operating Temperature, T <sub>OP</sub>            | 10°C to 60°C         |

| Storage Temperature, T <sub>ST</sub>              | 20°C to 80°C         |

\* Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

# **ELECTRICAL CHARACTERISTICS**

| Symbol             | Parameter                            | Min. | Тур. | Max. | Units |

|--------------------|--------------------------------------|------|------|------|-------|

| V <sub>cc</sub>    | Supply Voltage                       | 4.5  | 5    | 5.5  | V     |

| I <sub>DD</sub>    | Standby Current                      |      | 50   |      | uA    |

| I <sub>DRIVE</sub> | Output Current V <sub>OH</sub> =2.4V |      | 4    |      | mA    |

| I <sub>SINK</sub>  | Output Current V <sub>oL</sub> =0.4V |      | 4    |      | mA    |

| V <sub>IH</sub>    | Input Voltage (High)                 |      | 3.5  |      | V     |

| V <sub>IL</sub>    | Input Voltage (Low)                  |      | 1.5  |      | V     |

| F <sub>C</sub>     | Internal Scan Clock                  |      | 8    |      | MHz   |

| F <sub>s</sub>     | Sampling Clock                       | 20   | 32   | 128  | KHz   |

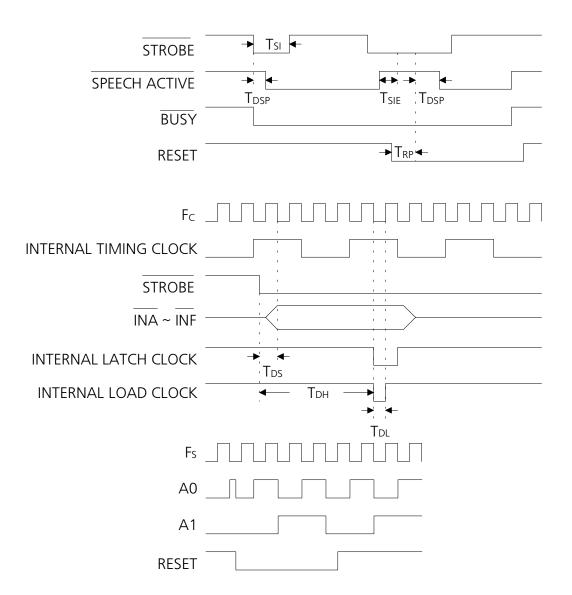

| T <sub>RESET</sub> | Reset Pulse Width                    |      | 1    |      | us    |

| T <sub>SI</sub>    | Strobe Input Pulse Width             |      | 1    |      | us    |

| T <sub>SIE</sub>   | Strobe Inhibit Time After EOS (1)    |      | 1.5  |      | ms    |

| T <sub>DSP</sub>   | Delay Time From Strobe To Play (2)   |      |      | 150  | ms    |

| T <sub>RP</sub>    | Edge-Triggered Reset Interval        |      | 1    |      | us    |

| T <sub>DS</sub>    | Data Setup Time For INA ~ INF        |      |      | 350  | ns    |

| T <sub>DH</sub>    | Data Hold Time For INA ~ INF         |      | 1    |      | us    |

| T <sub>DL</sub>    | Internal Load Pulse For INA ~ INF    |      | 65   |      | ns    |

#### Note:

- (1) EOS = End-Of-Speech

- (2) Based on 1M EPROM scanning.

# **TIMING DIAGRAM**

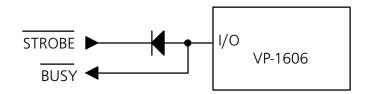

# **TEST CIRCUIT FOR I/O PIN**

#### PIN DESCRIPTIONS

#### A0 ~ A19:

Address output to EPROM.

#### ANG & ANG\:

Differential audio output, connect to LM324 or LM358.

#### ANGD:

Audio feedback input.

#### D0 ~ D7:

Data input from EPROM.

#### ENV:

Envelop input, connect to INT with a feedback resistor.

#### INT:

Integrator output, to be connected to an external RC integration circuitry.

#### 1/0:

Strobe input/Busy output, active low. To play a message, place the segment/bank code on INA to INE and strobe this pin with a low pulse. During the playback this pin becomes an active-low "busy" output. If this pin is held low at the end of playback, the message will be re-triggered.

#### INA ~ IND:

Input for segment code in binary format. INA is the LSB and IND is the MSB.

#### INE, INF:

Input for bank code in binary format, max. 4 banks. INE is the LSB and INF is the MSB.

# OSC1, OSC2:

Internal oscillator pins for external RC components. It external clock source is to be used, feed it through the OSC2 pin.

#### **RESET:**

Reset input, active low. On the falling edge of this reset signal, message playback is stopped and all internal counters are cleared.

# SE, SF:

Output for EPROM bank select. These two pins are actually latched outputs for INE and INF.

#### **VDD**

Input, supply voltage.

#### VDS & VAS:

VDS is digital ground and VAS is analog ground. Connect the two grounds together close to the power source to minimize noise.

#### **APPLICATION NOTES**

### 1. EOM (End Of Message) Flag

The EOM flag consists of six consecutive bytes of "AA", or "10101010" in binary format. After a trigger signal is received, the VP-1606 uses the internal 8MHz system clock to scan through memory space and finds the correct message by counting the number of EOM flags. For example, to find the 5th message, it must scan through each and every memory location until it finds 4 EOM flags. The first byte following the 4th EOM flag is the first byte of the 5th message.

- 2. Creating Master EPROM File on the VP-880 System Follow these steps to create the master EPROM file:

- 1. To maximize the EPROM usage, arrange your sound seaments in banks of 16 or less, so that the total combined length for each bank is about the same. Do not mix channel A and channel B together.

- 2. Based on the total combined length of the largest bank, select a highest sampling rate that will fully utilize the EPROM. Use the following equation:

Sampling Rate (Kbps) = EPROM Size (K-bits) / Total Length (Second)

- 3. Digitize and edit each segment as a separate file. Use the "ROM Data Management" function to combine up to 16 messages into a "bank file". The first filename entered in the "ROM Data Management" is the first segment in that bank, and etc.

- 4. Depending on the hardware design, each EPROM chip may contain one or more sound banks. If you need to combine several bank files into one for programming into one EPROM chip, use the following DOS command:

Do not use the "ROM Data Management" function to combine bank files, otherwise each bank file will be considered as a single message file.

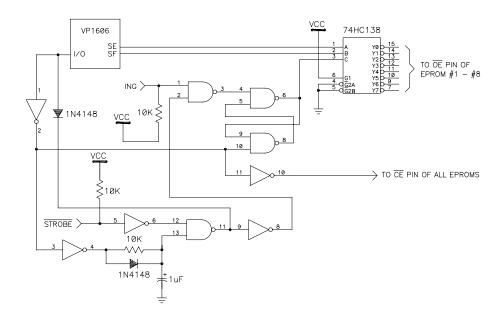

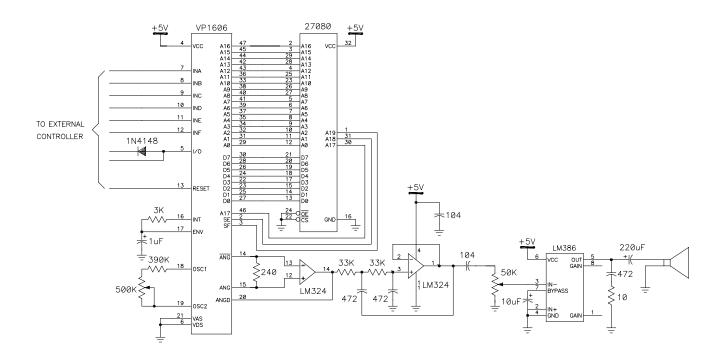

#### CIRCUIT DESIGN EXAMPLES

## 1. 64-Message Playback, 8M EPROM, 2M Per Bank

# 2. Segment Expansion (128 Segments)