# CMOS 4-BIT SINGLE CHIP MICROCOMPUTER S1C63406/408 Technical Manual S1C63406/408 Technical Hardware

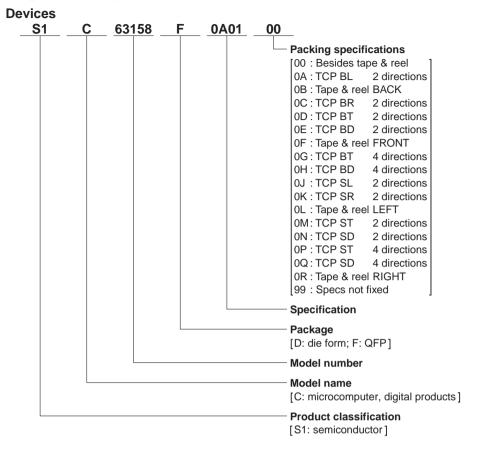

# Configuration of product number

# **CONTENTS**

| CHAPTER 1 | OU' | TLINE                                                    | 1  |

|-----------|-----|----------------------------------------------------------|----|

|           | 1.1 | Features                                                 | 1  |

|           | 1.2 | Block Diagram                                            | 3  |

|           | 1.3 | Pin Layout Diagram                                       |    |

|           |     | •                                                        |    |

|           | 1.4 | Pin Description                                          |    |

|           | 1.5 | Mask Option                                              | 9  |

| CHAPTER 2 | Pov | WER SUPPLY AND INITIAL RESET                             | 11 |

|           | 2.1 | Power Supply                                             | 11 |

|           |     | 2.1.1 Voltage <vd1> for internal circuits</vd1>          |    |

|           |     | 2.1.2 Voltage <vosc> for OSC1 oscillation circuit</vosc> |    |

|           |     | 2.1.3 Voltage < VC1, VC2, VC4, VC5> for LCD driving      |    |

|           | 2.2 | Initial Reset                                            |    |

|           |     | 2.2.1 Reset terminal (RESET)                             |    |

|           |     | 2.2.2 Simultaneous low input to terminals K00–K03        |    |

|           |     | 2.2.4 Internal register at initial resetting             |    |

|           |     | 2.2.5 Terminal settings at initial resetting             |    |

|           | 2.3 | Test Terminal (TEST)                                     |    |

|           | ~-  |                                                          |    |

| CHAPTER 3 | CP  | U, ROM, RAM                                              | 16 |

|           | 3.1 | CPU                                                      |    |

|           | 3.2 | Code ROM                                                 | 16 |

|           | 3.3 | RAM                                                      |    |

|           | 3.4 | Data ROM                                                 | 17 |

| CHAPTER 4 | PER | RIPHERAL CIRCUITS AND OPERATION                          | 18 |

|           | 4.1 | Memory Map                                               |    |

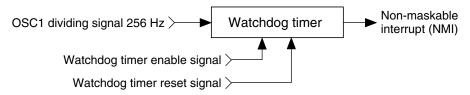

|           | 4.2 | Watchdog Timer                                           | 23 |

|           |     | 4.2.1 Configuration of watchdog timer                    |    |

|           |     | 4.2.2 Interrupt function                                 |    |

|           |     | 4.2.3 I/O memory of watchdog timer                       |    |

|           |     | 4.2.4 Programming notes                                  | 24 |

|           | 4.3 | • • • • • • • • • • • • • • • • • • • •                  |    |

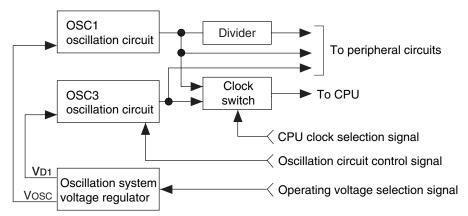

|           |     | 4.3.1 Configuration of oscillation circuit               |    |

|           |     | 4.3.2 OSC1 oscillation circuit                           |    |

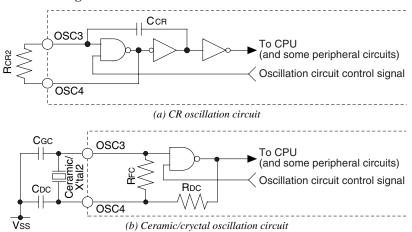

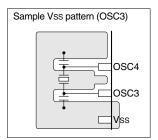

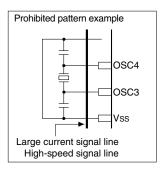

|           |     | 4.3.3 OSC3 oscillation circuit                           |    |

|           |     | 4.3.5 Clock frequency and instruction execution time     |    |

|           |     | 4.3.6 I/O memory of oscillation circuit                  |    |

|           |     | 4.3.7 Programming notes                                  |    |

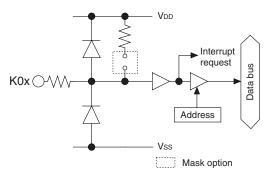

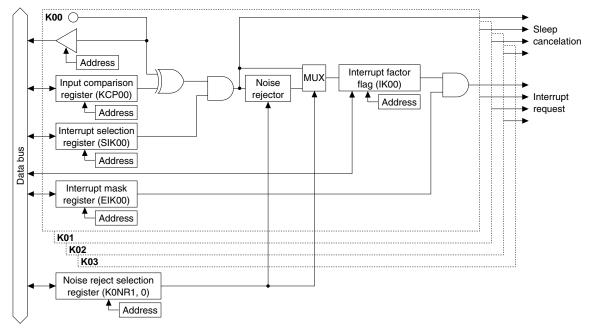

|           | 4.4 | <i>Input Ports (K00–K03)</i>                             | 31 |

|           |     | 4.4.1 Configuration of input ports                       |    |

|           |     | 4.4.2 Mask option                                        |    |

|           |     | 4.4.3 Interrupt function                                 |    |

|           |     | 4.4.4 I/O memory of input ports                          |    |

|           |     | 4.4.5 Programming notes                                  | 35 |

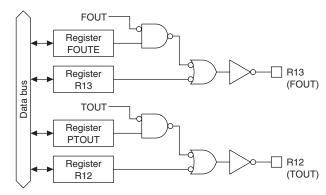

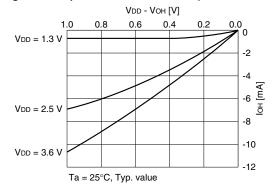

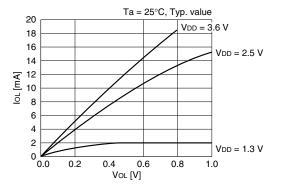

| 4.5  | Output Ports (R10–R13)                                     |    | 36 |

|------|------------------------------------------------------------|----|----|

|      | 4.5.1 Configuration of output ports                        |    |    |

|      | 4.5.2 Mask option                                          | 36 |    |

|      | 4.5.3 DC output                                            | 37 |    |

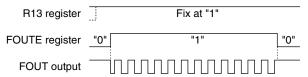

|      | 4.5.4 Special output                                       | 37 |    |

|      | 4.5.5 I/O memory of output ports                           | 39 |    |

|      | 4.5.6 Programming notes                                    | 40 |    |

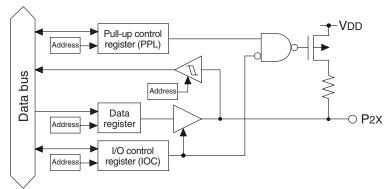

| 4.6  | I/O Ports (P20–P23)                                        |    | 41 |

| 7.0  | 4.6.1 Configuration of I/O ports                           |    | ,, |

|      | 4.6.2 Mask option                                          |    |    |

|      | 4.6.3 I/O control registers and input/output mode          |    |    |

|      | 4.6.4 Pull-up during input mode                            |    |    |

|      | 4.6.5 I/O memory of I/O ports                              |    |    |

|      | 4.6.6 Programming note                                     |    |    |

| 17   |                                                            |    | 10 |

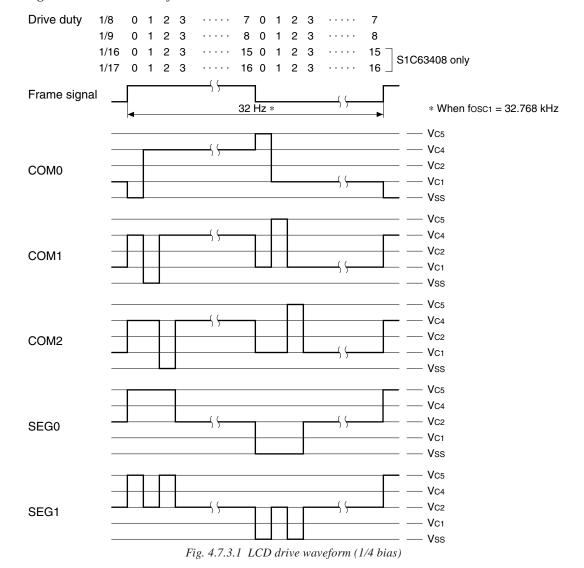

| 4.7  | LCD Driver                                                 |    | 40 |

|      | 4.7.1 Configuration of LCD driver                          |    |    |

|      | 4.7.2 Power supply for LCD driving                         |    |    |

|      | 4.7.3 LCD display control (ON/OFF) and switching of duty   |    |    |

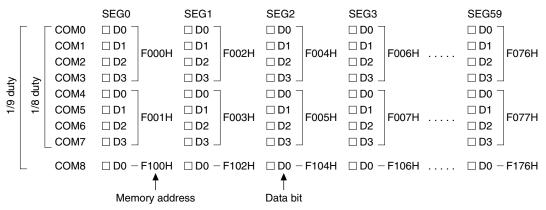

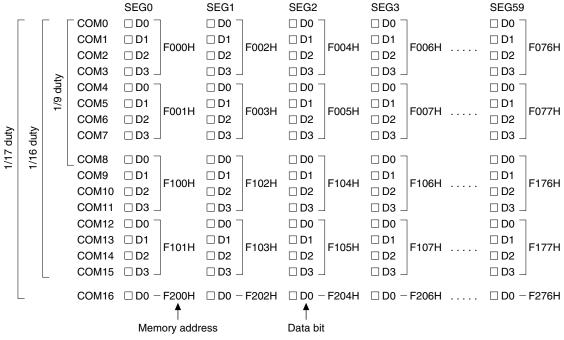

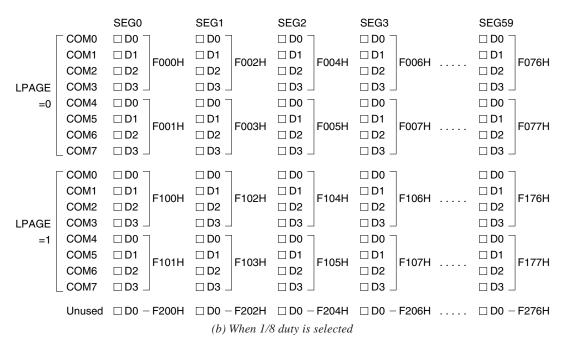

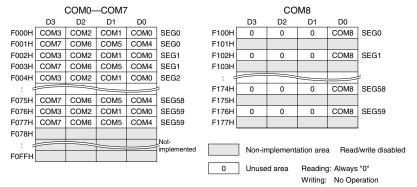

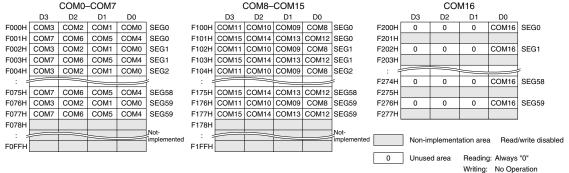

|      | 4.7.4 Display memory                                       |    |    |

|      | 4.7.5 LCD contrast adjustment                              |    |    |

|      | 4.7.6 I/O memory of LCD driver                             |    |    |

|      | 4.7.7 Programming notes                                    | 53 |    |

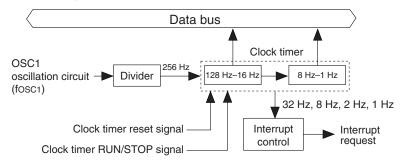

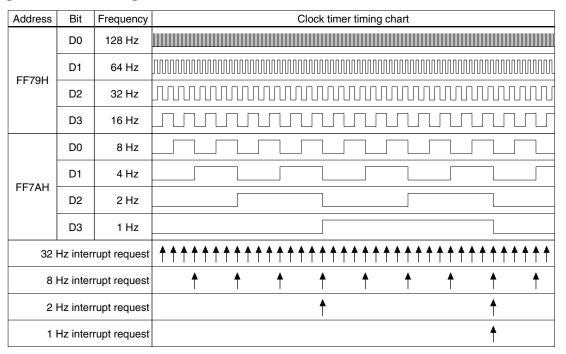

| 4.8  | Clock Timer                                                |    | 54 |

|      | 4.8.1 Configuration of clock timer                         | 54 |    |

|      | 4.8.2 Data reading and hold function                       | 54 |    |

|      | 4.8.3 Interrupt function                                   | 55 |    |

|      | 4.8.4 I/O memory of clock timer                            | 56 |    |

|      | 4.8.5 Programming notes                                    | 58 |    |

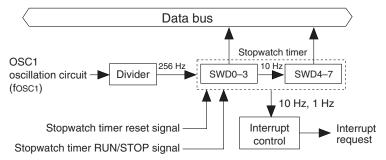

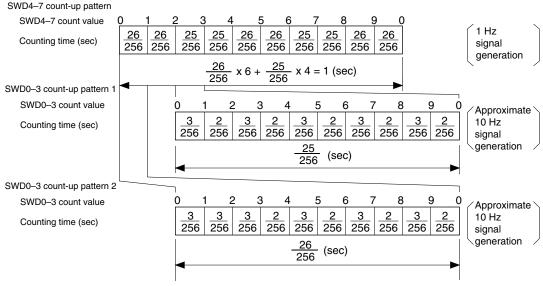

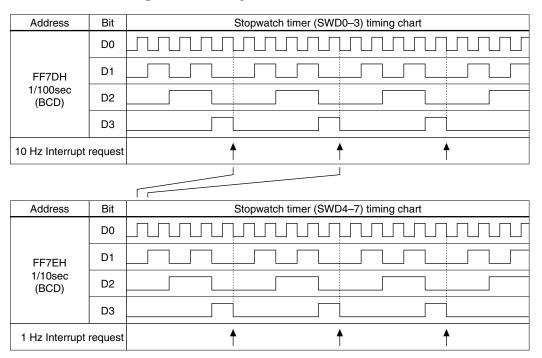

| 4.9  | Stopwatch Timer                                            |    | 59 |

| 1.7  | 4.9.1 Configuration of stopwatch timer                     |    | 57 |

|      | 4.9.2 Count-up pattern                                     |    |    |

|      | 4.9.3 Interrupt function                                   |    |    |

|      | 4.9.4 I/O memory of stopwatch timer                        |    |    |

|      | 4.9.5 Programming notes                                    |    |    |

| 1 10 |                                                            |    | () |

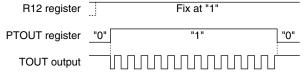

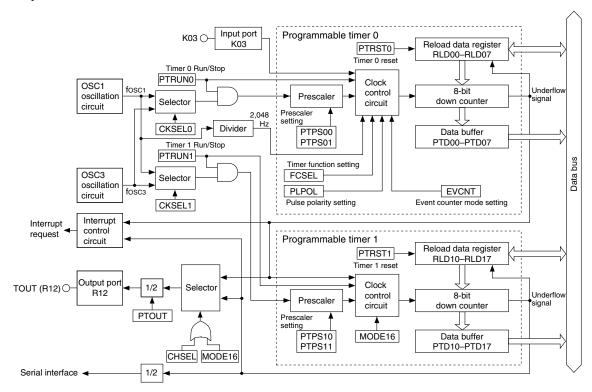

| 4.10 | Programmable Timer                                         |    | 03 |

|      | 4.10.1 Configuration of programmable timer                 |    |    |

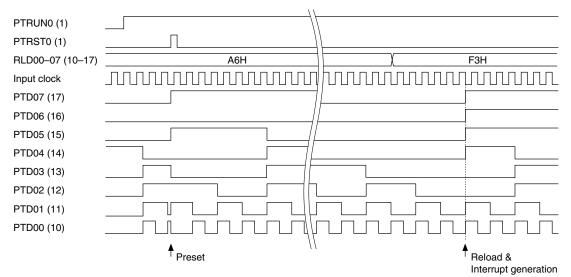

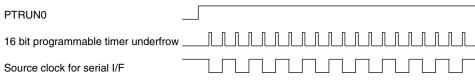

|      | 4.10.2 Tow separate 8-bit timer (MODE16 = "0") operation   |    |    |

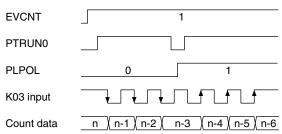

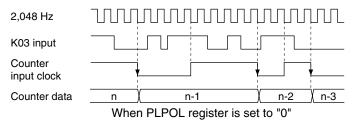

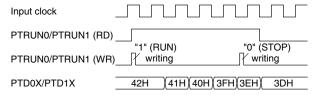

|      | 4.10.2.1 Setting of initial value and counting down        |    |    |

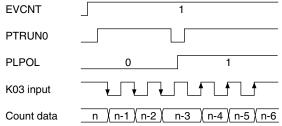

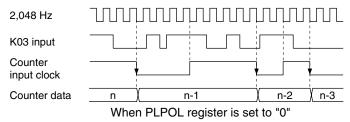

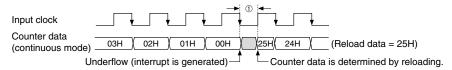

|      | 4.10.2.2 Counter mode                                      |    |    |

|      | 4.10.2.3 Setting of input clock in timer mode              |    |    |

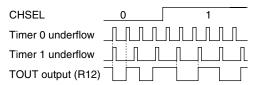

|      | 4.10.2.4 Interrupt function                                |    |    |

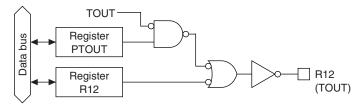

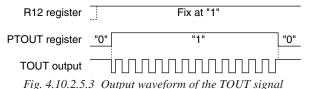

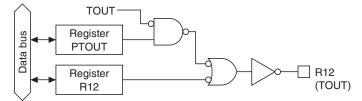

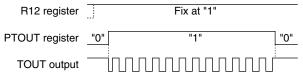

|      | 4.10.2.5 Setting of TOUT output                            |    |    |

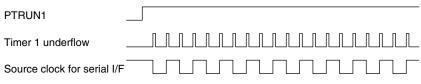

|      | 4.10.2.6 Transfer rate setting for serial interface        |    |    |

|      | 4.10.3 One channel × 16-bit timer (MODE16 = "1") operation |    |    |

|      | 4.10.3.1 Setting of initial value and counting down        |    |    |

|      | 4.10.3.2 Counter mode                                      |    |    |

|      | 4.10.3.3 Setting of input clock in timer mode              |    |    |

|      | 4.10.3.4 Interrupt function                                |    |    |

|      | 4.10.3.5 Setting of TOUT output                            |    |    |

|      | 4.10.3.6 Transfer rate setting for serial interface        |    |    |

|      | 4.10.4 I/O memory of programmable timer                    |    |    |

|      | 4.10.5 Programming notes                                   | 78 |    |

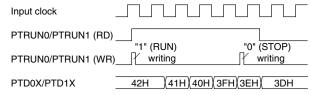

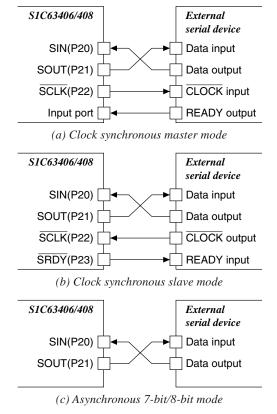

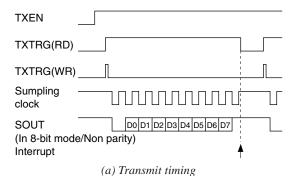

|           | 4.11 | Serial Interface                                             | 79  |

|-----------|------|--------------------------------------------------------------|-----|

|           |      | 4.11.1 Configuration of serial interface                     |     |

|           |      | 4.11.2 Mask option                                           |     |

|           |      | 4.11.3 Transfer modes                                        | 80  |

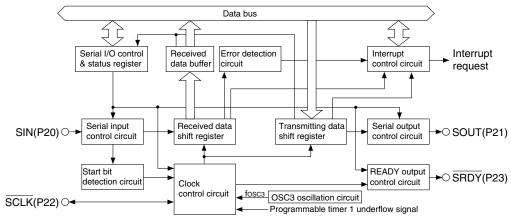

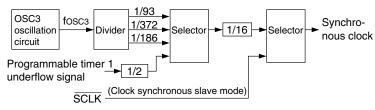

|           |      | 4.11.4 Clock source                                          | 82  |

|           |      | 4.11.5 Transmit-receive control                              |     |

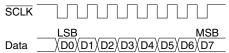

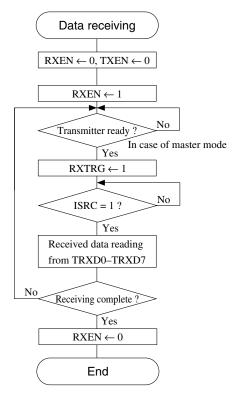

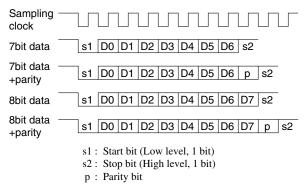

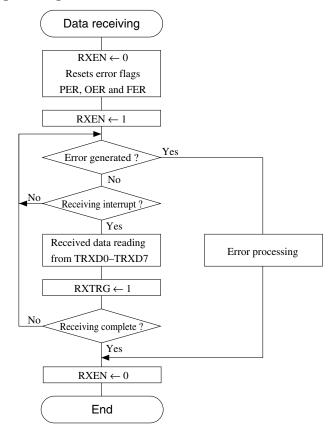

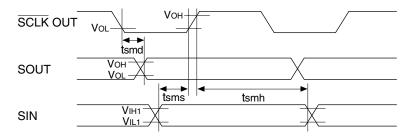

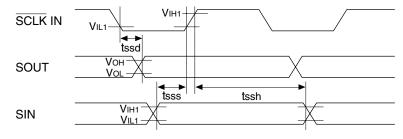

|           |      | 4.11.6 Operation of clock synchronous transfer               |     |

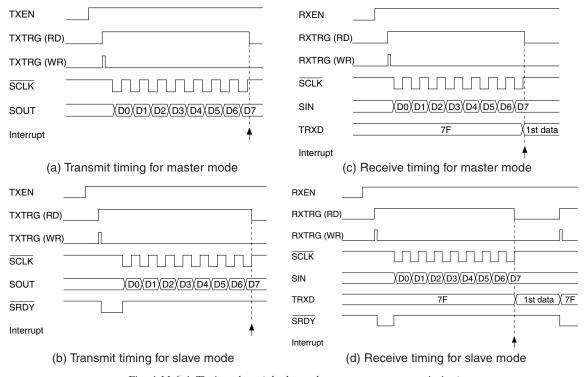

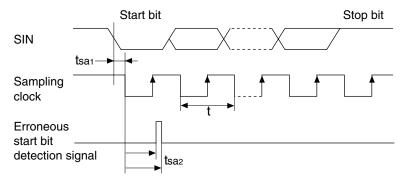

|           |      | 4.11.7 Operation of asynchronous transfer                    |     |

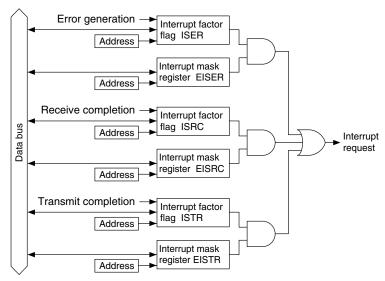

|           |      | 4.11.8 Interrupt function                                    |     |

|           |      | 4.11.9 I/O memory of serial interface                        |     |

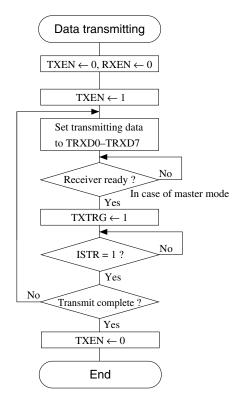

|           |      | 4.11.10 Programming notes                                    |     |

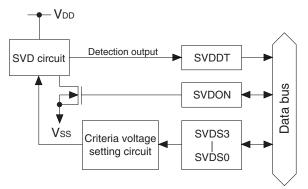

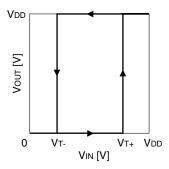

|           | 4.12 | SVD (Supply Voltage Detection) Circuit                       |     |

|           |      | 4.12.1 Configuration of SVD circuit                          |     |

|           |      | 4.12.2 SVD operation                                         |     |

|           |      | 4.12.3 I/O memory of SVD circuit                             |     |

|           |      | 4.12.4 Programming notes                                     |     |

|           | 4.13 | Heavy Load Protection Function                               |     |

|           |      | 4.13.1 Outline of heavy load protection function             |     |

|           |      | 4.13.2 I/O memory of heavy load protection function          |     |

|           |      | 4.13.3 Programming note                                      |     |

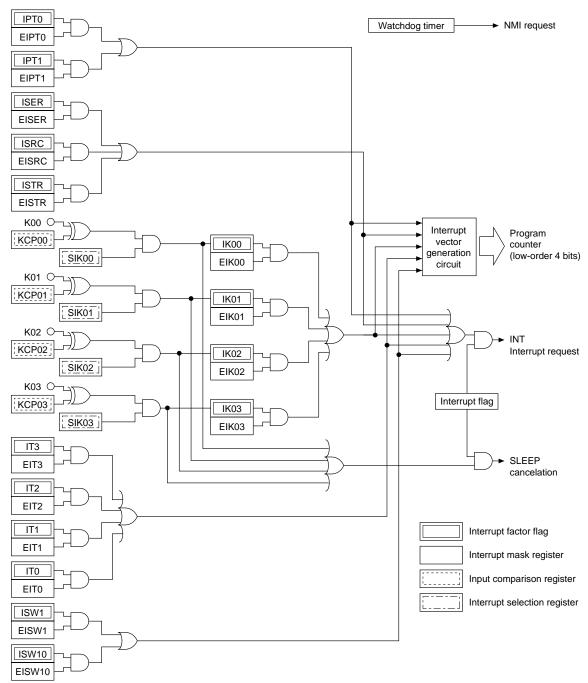

|           | 4.14 | Interrupt and HALT/SLEEP                                     | 104 |

|           |      | 4.14.1 Interrupt factor                                      |     |

|           |      | 4.14.2 Interrupt mask                                        |     |

|           |      | 4.14.3 Interrupt vector                                      |     |

|           |      | 4.14.4 I/O memory of interrupt                               |     |

|           |      | 4.14.5 Programming notes                                     | 109 |

| CHAPTER 5 | SUM  | MMARY OF NOTES                                               | 110 |

|           | 5.1  | Notes for Low Current Consumption                            | 110 |

|           | 5.2  | Summary of Notes by Function                                 | 111 |

|           | 5.3  | Notes on Mounting                                            |     |

|           |      |                                                              |     |

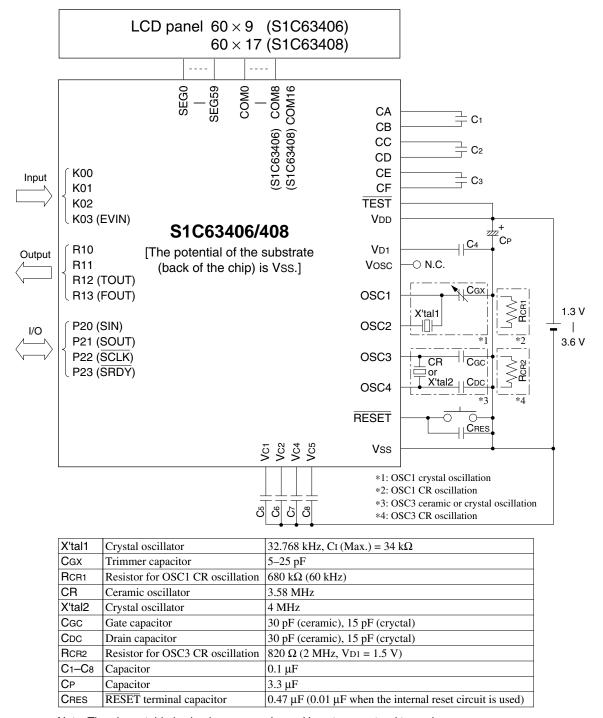

| CHAPTER 6 | BAS  | IC EXTERNAL WIRING DIAGRAM                                   | 117 |

| CHAPTER 7 | ELE  | ECTRICAL CHARACTERISTICS                                     | 118 |

|           | 7.1  | Absolute Maximum Rating                                      | 118 |

|           | 7.2  | Recommended Operating Conditions                             | 118 |

|           | 7.3  | DC Characteristics                                           | 119 |

|           | 7.4  | Analog Circuit Characteristics and Power Current Consumption | 120 |

|           | 7.5  | Oscillation Characteristics                                  |     |

|           | 7.6  | Serial Interface AC Characteristics                          |     |

|           | 7.7  | Timing Chart                                                 |     |

|           | /./  | Tuning Citari                                                | 12/ |

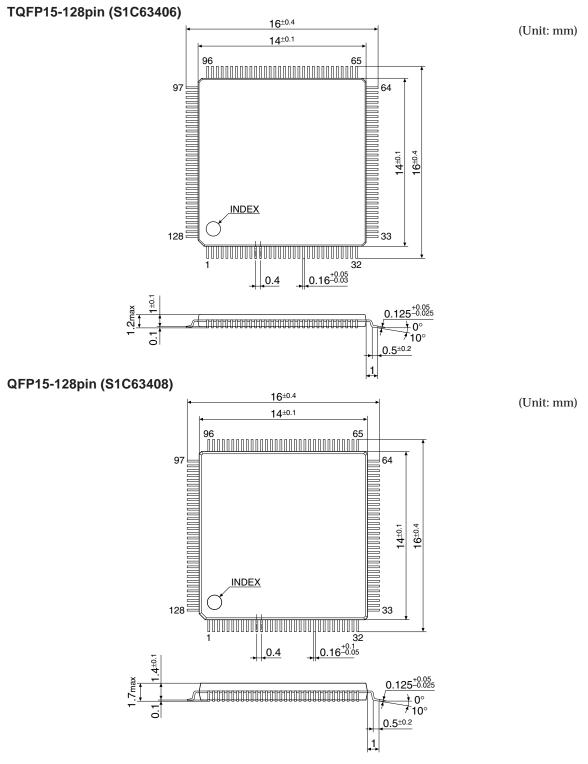

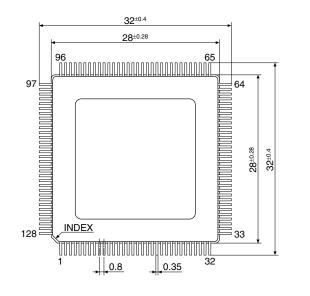

| CHAPTER 8 | PAC  | KAGE                                                         | 128 |

|           | 8.1  | Plastic Package                                              | 128 |

|           | 82   | Ceramic Package for Test Samples                             | 129 |

#### **CONTENTS**

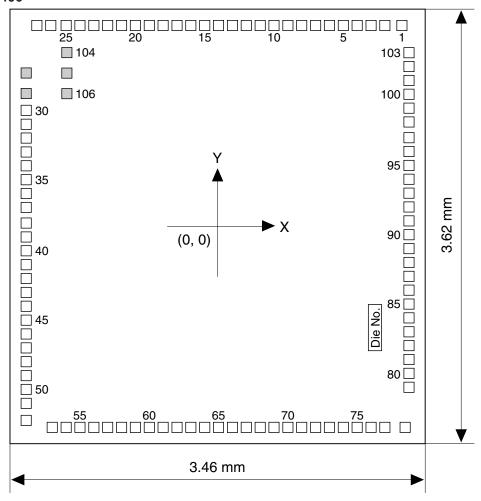

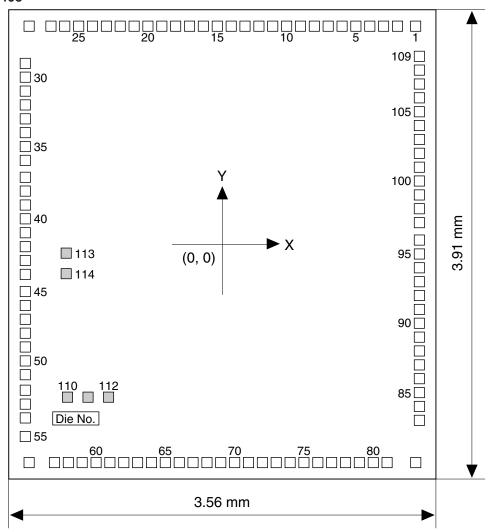

| CHAPTER 9 | $P_{AL}$ | LAYOUT                                                       | 130   |

|-----------|----------|--------------------------------------------------------------|-------|

|           | 9.1      | Diagram of Pad Layout                                        | . 130 |

|           | 9.2      | Pad Coordinates                                              | . 132 |

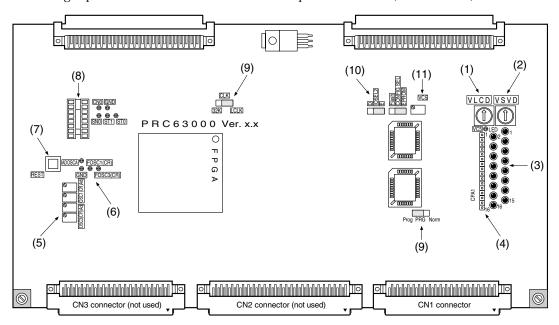

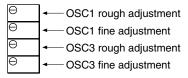

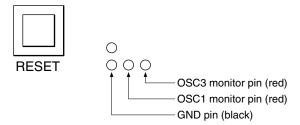

| APPENDIX  | S5U      | J1C63000P Manual (Peripheral Circuit Board for S1C63406/408) | 134   |

|           | A.1      | Names and Functions of Each Part                             | . 134 |

|           | A.2      | Connecting to the Target System                              | . 137 |

|           | A.3      | Usage Precautions                                            |       |

|           |          | A.3.1 Operational precautions                                |       |

|           |          | A 3.2 Differences with the actual IC                         | :9    |

# CHAPTER 1 OUTLINE

The S1C63406/408 is a microcomputer which has a high-performance 4-bit CPU S1C63000 as the core CPU, code ROM, RAM, data ROM, serial interface, watchdog timer, programmable timer, time base counters (2 systems) and a dot-matrix LCD driver. Furthermore, the built-in reset circuit (with power-on reset function) can detect the power supply voltage to reset the S1C63406/408 when the power is turned on or an instantaneous power interruption occurs. The S1C63406/408 features high speed operation with a low operating voltage (1.3 V to 3.6 V) and low current consumption, this makes it suitable for applications working with batteries, such as portable MD and CD player systems.

Table 1.1 lists the differences between the S1C63406 and S1C63408.

Table 1.1 Differences between the S1C63406 and S1C63408

| Model               | S1C63406                                     | S1C63408                                     |

|---------------------|----------------------------------------------|----------------------------------------------|

| Code ROM size       | $6,144 \text{ words} \times 13 \text{ bits}$ | $8,192 \text{ words} \times 13 \text{ bits}$ |

| Data ROM size       | $3,072 \text{ words} \times 4 \text{ bits}$  | $4,096 \text{ words} \times 4 \text{ bits}$  |

| RAM size            | $1,024 \text{ words} \times 4 \text{ bits}$  | $1,024 \text{ words} \times 4 \text{ bits}$  |

| Display memory size | 540 bits                                     | 1,020 bits                                   |

| LCD driver          | 60 segments                                  | 60 segments                                  |

|                     | 8 or 9 commons                               | 8, 9, 16 or 17 commons                       |

#### 1.1 Features

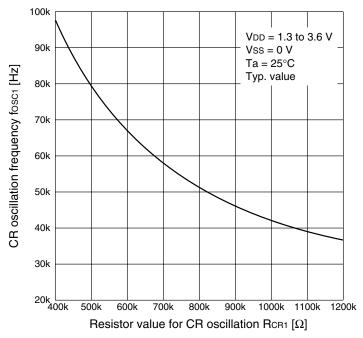

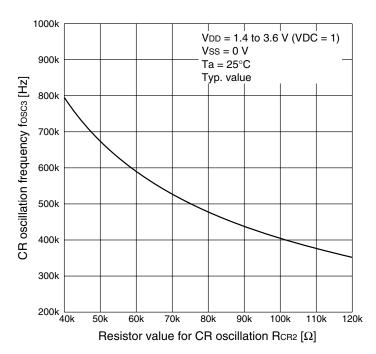

| OSC1 oscillation circuit   | 32.768 kHz (Typ.) crystal or 60 kHz (Typ.) CR oscillation circuit (*1)       |

|----------------------------|------------------------------------------------------------------------------|

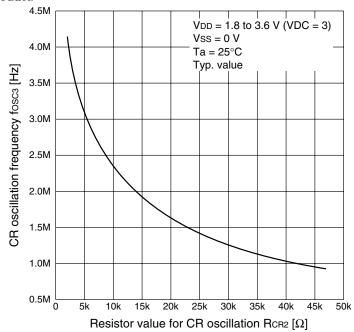

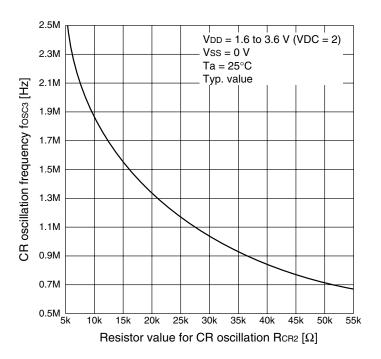

| OSC3 oscillation circuit   | 4 MHz (Typ.) crystal, 3.58 MHz (Typ.) ceramic                                |

|                            | or 2 MHz (Typ.) CR oscillation circuit (*1)                                  |

| Instruction set            | Basic instruction: 47 types (411 instructions with all)                      |

|                            | Addressing mode: 8 types                                                     |

| Instruction execution time | During operation at 32.768 kHz: 61 µsec 122 µsec 183 µsec                    |

|                            | During operation at 60 kHz: 33 µsec 67 µsec 100 µsec                         |

|                            | During operation at 2 MHz: 1 µsec 2 µsec 3 µsec                              |

|                            | During operation at 3.58 MHz: 0.56 µsec 1.12 µsec 1.68 µsec                  |

|                            | During operation at 4 MHz: 0.5 μsec 1 μsec 1.5 μsec                          |

| ROM capacity               | Code ROM: 6,144 words × 13 bits (S1C63406)                                   |

|                            | $8,192 \text{ words} \times 13 \text{ bits (S1C63408)}$                      |

|                            | Data ROM: $3,072 \text{ words} \times 4 \text{ bits}$ (S1C63406)             |

|                            | $4,096 \text{ words} \times 4 \text{ bits}$ (S1C63408)                       |

| RAM capacity               | Data memory: $1,024 \text{ words} \times 4 \text{ bits}$                     |

|                            | Display memory: 540 bits (S1C63406)                                          |

|                            | $(120 \text{ words} \times 4 \text{ bits} + 60 \times 1 \text{ bit})$        |

|                            | 1,020 bits (S1C63408)                                                        |

|                            | $(240 \text{ words} \times 4 \text{ bits} + 60 \times 1 \text{ bit})$        |

| Input port                 | 4 bits (Pull-up resistors may be supplemented *1)                            |

| Output port                | 4 bits (It is possible to switch the 2 bits to special outputs *2)           |

| I/O port                   | 4 bits with Schmitt trigger input                                            |

|                            | (Built-in pull-up resistors may be disabled *2                               |

|                            | It is possible to switch to serial I/F inputs/outputs *2)                    |

| Serial interface           | 1 port (8-bit clock synchronous or asynchronous system *2)                   |

| LCD driver                 | 60 segments × 8 or 9 commons (S1C63406 *2)                                   |

|                            | 60 segments × 8, 9, 16 or 17 commons (S1C63408 *2)                           |

|                            | 2 systems (Clock timer, stopwatch timer)                                     |

| Programmable timer         | 8 bits $\times$ 2 ch. or 16 bits $\times$ 1 ch., with event counter function |

| Watchdog timer             | Built-in                                                                     |

|                            | . 16 values, programmable (1.30 V to 2.80 V)                                 |

| Reset circuit              | Built-in (1.8 V, 1.6 V or 1.4 V $*$ 1), with power-on reset function         |

|                            |                                                                              |

#### **CHAPTER 1: OUTLINE**

| External interrupt          | Input port interrupt:          | 4 systems              |               |

|-----------------------------|--------------------------------|------------------------|---------------|

| Internal interrupt          |                                | 4 systems              |               |

|                             | Stopwatch timer interrupt:     | 2 systems              |               |

|                             | Programmable timer interrupt   | : 2 systems            |               |

|                             | Serial interface interrupt:    | 3 systems              |               |

| Power supply voltage        | 1.3 V to 3.6 V                 |                        |               |

|                             | (Min. 1.4 V when 700 kHz (Ma   | x.) OSC3 CR oscillato  | or is used)   |

|                             | (Min. 1.6 V when 2.2 MHz (Ma   | x.) OSC3 CR oscillato  | or is used)   |

|                             | (Min. 1.8 V when 4.2 MHz (Ma   | x.) OSC3 oscillator is | used)         |

| Operating temperature range | -40°C to 85°C                  |                        |               |

| Current consumption         | Low-power operation (*3):      |                        |               |

|                             | During SLEEP                   |                        | 1.2 μA (Typ.) |

|                             | During HALT (32 kHz cryctal    | l oscillation)         |               |

|                             | 3.6 V (LCD C                   | OFF)                   | 1.3 μA (Typ.) |

|                             | 3.6 V (LCD C                   | N, Vc1 standard)       | 3.0 μA (Typ.) |

|                             | 3.6 V (LCD C                   | N, Vc2 standard)       | 2.5 μA (Typ.) |

|                             | During operation (32 kHz cry   | ctal oscillation)      |               |

|                             | 3.6 V (LCD C                   | OFF)                   | 3.0 μA (Typ.) |

|                             | During HALT (60 kHz CR osc     | cillation)             |               |

|                             | 3.6 V (LCD C                   | OFF)                   | 3.5 μA (Typ.) |

|                             | 3.6 V (LCD C                   | N, VC1 standard)       | 6.2 μA (Typ.) |

|                             |                                | N, Vc2 standard)       | 4.6 μA (Typ.) |

|                             | During operation (60 kHz CR    | oscillation)           |               |

|                             | 3.6 V (LCD C                   | OFF)                   | 7.0 μA (Typ.) |

|                             | High-speed operation:          |                        |               |

|                             | During operation (500 kHz C    | R oscillation)         |               |

|                             | 3.6 V (LCD C                   |                        | 90 μA (Typ.)  |

|                             | During operation (1 MHz CR     | oscillation)           |               |

|                             | 3.6 V (LCD C                   | OFF)                   | 200 μA (Typ.) |

|                             | During operation (2 MHz CR     | oscillation)           |               |

|                             | 3.6 V (LCD C                   |                        | 350 μA (Typ.) |

|                             | During operation (3.58 MHz of  |                        |               |

|                             | 3.6 V (LCD C                   |                        | 500 μA (Typ.) |

|                             | During operation (4 MHz cry    | stal oscillation)      |               |

|                             | 3.6 V (LCD C                   | *                      | 550 μA (Typ.) |

| Package                     |                                | -                      |               |

|                             | QFP15-128pin (plastic) or chip | (S1C63408)             |               |

<sup>\*2:</sup> Can be selected with software

circuit current will be added when the reset circuit option is selected.)

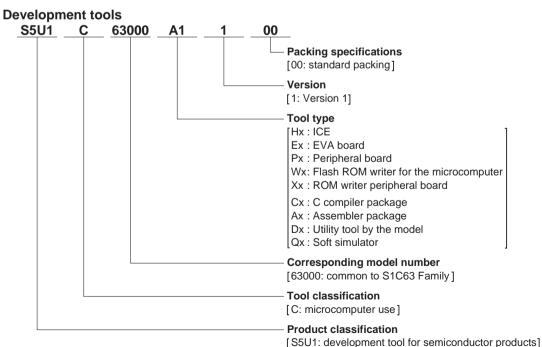

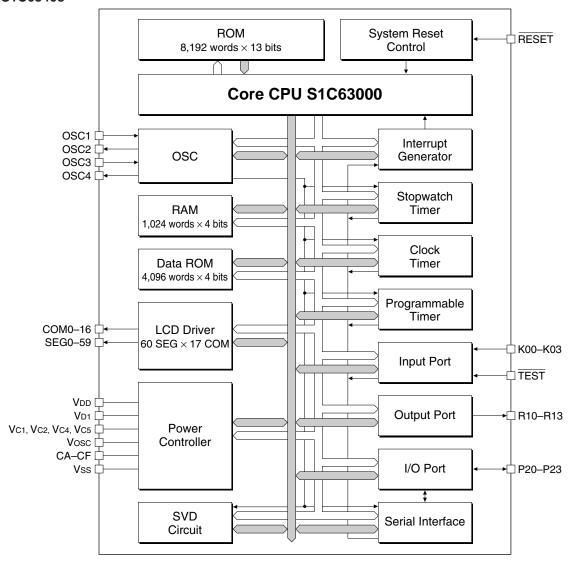

# 1.2 Block Diagram

## S1C63406

Fig. 1.2.1 S1C63406 block diagram

#### S1C63408

Fig. 1.2.2 S1C63408 block diagram

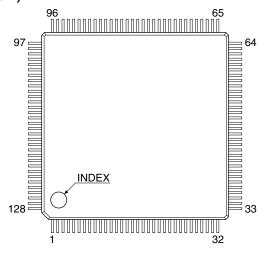

# 1.3 Pin Layout Diagram

# S1C63406 (TQFP15-128pin)

| No. | Pin name | No. | Pin name        | No. | Pin name | No. | Pin name |

|-----|----------|-----|-----------------|-----|----------|-----|----------|

| 1   | N.C.     | 33  | CF              | 65  | N.C.     | 97  | SEG15    |

| 2   | SEG41    | 34  | VC5             | 66  | N.C.     | 98  | SEG16    |

| 3   | SEG42    | 35  | VC4             | 67  | N.C.     | 99  | SEG17    |

| 4   | SEG43    | 36  | Vc2             | 68  | N.C.     | 100 | SEG18    |

| 5   | SEG44    | 37  | VC1             | 69  | COM0     | 101 | SEG19    |

| 6   | SEG45    | 38  | K00             | 70  | COM1     | 102 | SEG20    |

| 7   | SEG46    | 39  | K01             | 71  | COM2     | 103 | SEG21    |

| 8   | SEG47    | 40  | K02             | 72  | COM3     | 104 | SEG22    |

| 9   | SEG48    | 41  | N.C.            | 73  | COM4     | 105 | SEG23    |

| 10  | SEG49    | 42  | N.C.            | 74  | N.C.     | 106 | N.C.     |

| 11  | N.C.     | 43  | K03             | 75  | N.C.     | 107 | N.C.     |

| 12  | N.C.     | 44  | R10             | 76  | N.C.     | 108 | N.C.     |

| 13  | N.C.     | 45  | R11             | 77  | COM5     | 109 | N.C.     |

| 14  | SEG50    | 46  | R12             | 78  | COM6     | 110 | SEG24    |

| 15  | SEG51    | 47  | R13             | 79  | COM7     | 111 | SEG25    |

| 16  | SEG52    | 48  | P20             | 80  | SEG0     | 112 | SEG26    |

| 17  | SEG53    | 49  | P21             | 81  | SEG1     | 113 | SEG27    |

| 18  | SEG54    | 50  | P22             | 82  | SEG2     | 114 | SEG28    |

| 19  | N.C.     | 51  | P23             | 83  | SEG3     | 115 | SEG29    |

| 20  | N.C.     | 52  | N.C.            | 84  | N.C.     | 116 | SEG30    |

| 21  | N.C.     | 53  | N.C.            | 85  | N.C.     | 117 | SEG31    |

| 22  | SEG55    | 54  | N.C.            | 86  | SEG4     | 118 | SEG32    |

| 23  | SEG56    | 55  | Vdd             | 87  | SEG5     | 119 | N.C.     |

| 24  | SEG57    | 56  | V <sub>D1</sub> | 88  | SEG6     | 120 | N.C.     |

| 25  | SEG58    | 57  | OSC4            | 89  | SEG7     | 121 | SEG33    |

| 26  | SEG59    | 58  | OSC3            | 90  | SEG8     | 122 | SEG34    |

| 27  | COM8     | 59  | Vosc            | 91  | SEG9     | 123 | SEG35    |

| 28  | CA       | 60  | OSC2            | 92  | SEG10    | 124 | SEG36    |

| 29  | СВ       | 61  | OSC1            | 93  | SEG11    | 125 | SEG37    |

| 30  | CC       | 62  | Vss             | 94  | SEG12    | 126 | SEG38    |

| 31  | CD       | 63  | RESET           | 95  | SEG13    | 127 | SEG39    |

| 32  | CE       | 64  | TEST            | 96  | SEG14    | 128 | SEG40    |

N.C.: No Connection

5

Fig. 1.3.1 S1C63406 pin layout diagram

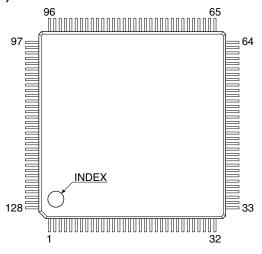

# S1C63408 (QFP15-128pin)

| No. | Pin name |

|-----|----------|-----|----------|-----|----------|-----|----------|

| 1   | N.C.     | 33  | N.C.     | 65  | N.C.     | 97  | N.C.     |

| 2   | N.C.     | 34  | N.C.     | 66  | N.C.     | 98  | N.C.     |

| 3   | N.C.     | 35  | CE       | 67  | COM0     | 99  | SEG19    |

| 4   | SEG46    | 36  | CF       | 68  | COM1     | 100 | N.C.     |

| 5   | SEG47    | 37  | Vc5      | 69  | COM2     | 101 | SEG20    |

| 6   | SEG48    | 38  | VC4      | 70  | N.C.     | 102 | SEG21    |

| 7   | SEG49    | 39  | Vc2      | 71  | COM3     | 103 | SEG22    |

| 8   | SEG50    | 40  | Vc1      | 72  | COM4     | 104 | SEG23    |

| 9   | SEG51    | 41  | K00      | 73  | COM5     | 105 | SEG24    |

| 10  | SEG52    | 42  | K01      | 74  | COM6     | 106 | SEG25    |

| 11  | SEG53    | 43  | K02      | 75  | COM7     | 107 | SEG26    |

| 12  | SEG54    | 44  | K03      | 76  | SEG0     | 108 | SEG27    |

| 13  | SEG55    | 45  | R10      | 77  | SEG1     | 109 | SEG28    |

| 14  | SEG56    | 46  | R11      | 78  | SEG2     | 110 | SEG29    |

| 15  | SEG57    | 47  | R12      | 79  | SEG3     | 111 | SEG30    |

| 16  | SEG58    | 48  | R13      | 80  | SEG4     | 112 | SEG31    |

| 17  | SEG59    | 49  | P20      | 81  | SEG5     | 113 | SEG32    |

| 18  | COM8     | 50  | P21      | 82  | SEG6     | 114 | SEG33    |

| 19  | COM9     | 51  | P22      | 83  | SEG7     | 115 | SEG34    |

| 20  | COM10    | 52  | P23      | 84  | SEG8     | 116 | SEG35    |

| 21  | COM11    | 53  | Vdd      | 85  | SEG9     | 117 | SEG36    |

| 22  | COM12    | 54  | VD1      | 86  | SEG10    | 118 | SEG37    |

| 23  | COM13    | 55  | OSC4     | 87  | SEG11    | 119 | SEG38    |

| 24  | COM14    | 56  | OSC3     | 88  | SEG12    | 120 | SEG39    |

| 25  | COM15    | 57  | Vosc     | 89  | SEG13    | 121 | SEG40    |

| 26  | COM16    | 58  | OSC2     | 90  | SEG14    | 122 | SEG41    |

| 27  | CA       | 59  | OSC1     | 91  | SEG15    | 123 | SEG42    |

| 28  | СВ       | 60  | Vss      | 92  | SEG16    | 124 | SEG43    |

| 29  | CC       | 61  | RESET    | 93  | SEG17    | 125 | SEG44    |

| 30  | CD       | 62  | TEST     | 94  | N.C.     | 126 | SEG45    |

| 31  | N.C.     | 63  | N.C.     | 95  | SEG18    | 127 | N.C.     |

| 32  | N.C.     | 64  | N.C.     | 96  | N.C.     | 128 | N.C.     |

N.C.: No Connection

Fig. 1.3.2 S1C63408 pin layout diagram

# 1.4 Pin Description

# S1C63406

Table 1.4.1 S1C63406 pin description

| Pin name           | Pin No.            | In/Out | Function                                                                   |

|--------------------|--------------------|--------|----------------------------------------------------------------------------|

| V <sub>DD</sub>    | 55                 | _      | Power (+) supply pin                                                       |

| Vss                | 62                 | _      | Power (–) supply pin                                                       |

| V <sub>D1</sub>    | 56                 | _      | Internal logic system regulated voltage output pin                         |

| Vosc               | 59                 | _      | Oscillation system regulated voltage output pin                            |

| VC1, VC2, VC4, VC5 | 37, 36, 35, 34     | _      | LCD system power supply pins (1/4 bias)                                    |

| CA-CF              | 28-33              | _      | LCD system boosting/reducing capacitor connecting pins                     |

| OSC1               | 61                 | I      | Crystal or CR oscillation input pin (selected by mask option)              |

| OSC2               | 60                 | О      | Crystal or CR oscillation output pin (selected by mask option)             |

| OSC3               | 58                 | I      | Crystal, ceramic or CR oscillation input pin (selected by mask option)     |

| OSC4               | 57                 | О      | Crystal, ceramic or CR oscillation output pin (selected by mask option)    |

| K00-K02            | 38-40              | I      | Input port pins                                                            |

| K03                | 43                 | I      | Input port pin or EVIN signal input pin (selected by software)             |

| R10, R11           | 44, 45             | О      | Output port pins                                                           |

| R12                | 46                 | О      | Output port pin or TOUT signal output pin (selected by software)           |

| R13                | 47                 | О      | Output port pin or FOUT signal output pin (selected by software)           |

| P20                | 48                 | I/O    | I/O port pins or serial I/F data input pin (selected by software)          |

| P21                | 49                 | I/O    | I/O port pins or serial I/F data output pin (selected by software)         |

| P22                | 50                 | I/O    | I/O port pins or serial I/F clock input/output pin (selected by software)  |

| P23                | 51                 | I/O    | I/O port pins or serial I/F ready signal output pin (selected by software) |

| COM0-COM8          | 69-73, 77-79, 27   | О      | LCD common output pin                                                      |

| SEG0-SEG59         | 80-83, 86-105,     | О      | LCD segment output pin                                                     |

|                    | 110-118, 121-128,  |        |                                                                            |

|                    | 2-10, 14-18, 22-26 |        |                                                                            |

| RESET              | 63                 | I      | Initial reset input pin                                                    |

| TEST               | 64                 | I      | Testing input pin                                                          |

# S1C63408

Table 1.4.2 S1C63408 pin description

| Pin name           | Pin No.             | In/Out | Function                                                                   |

|--------------------|---------------------|--------|----------------------------------------------------------------------------|

| Vdd                | 53                  | _      | Power (+) supply pin                                                       |

| Vss                | 60                  | _      | Power (–) supply pin                                                       |

| V <sub>D1</sub>    | 54                  | _      | Internal logic system regulated voltage output pin                         |

| Vosc               | 57                  | _      | Oscillation system regulated voltage output pin                            |

| VC1, VC2, VC4, VC5 | 40, 39, 38, 37      | _      | LCD system power supply pins (1/4 bias)                                    |

| CA-CF              | 27–30, 35, 36       | _      | LCD system boosting/reducing capacitor connecting pins                     |

| OSC1               | 59                  | I      | Crystal or CR oscillation input pin (selected by mask option)              |

| OSC2               | 58                  | О      | Crystal or CR oscillation output pin (selected by mask option)             |

| OSC3               | 56                  | I      | Crystal, ceramic or CR oscillation input pin (selected by mask option)     |

| OSC4               | 55                  | О      | Crystal, ceramic or CR oscillation output pin (selected by mask option)    |

| K00-K02            | 41–43               | I      | Input port pins                                                            |

| K03                | 44                  | I      | Input port pin or EVIN signal input pin (selected by software)             |

| R10, R11           | 45, 46              | О      | Output port pins                                                           |

| R12                | 47                  | О      | Output port pin or TOUT signal output pin (selected by software)           |

| R13                | 48                  | 0      | Output port pin or FOUT signal output pin (selected by software)           |

| P20                | 49                  | I/O    | I/O port pins or serial I/F data input pin (selected by software)          |

| P21                | 50                  | I/O    | I/O port pins or serial I/F data output pin (selected by software)         |

| P22                | 51                  | I/O    | I/O port pins or serial I/F clock input/output pin (selected by software)  |

| P23                | 52                  | I/O    | I/O port pins or serial I/F ready signal output pin (selected by software) |

| COM0-COM16         | 67–69, 71–75, 18–26 | 0      | LCD common output pin                                                      |

| SEG0-SEG59         | 76–93, 95, 99,      | 0      | LCD segment output pin                                                     |

|                    | 101–126, 4–17       |        |                                                                            |

| RESET              | 61                  | I      | Initial reset input pin                                                    |

| TEST               | 62                  | I      | Testing input pin                                                          |

# 1.5 Mask Option

Mask options shown below are provided for the S1C63406/408. Several hardware specifications are prepared in each mask option, and one of them can be selected according to the application. The function option generator winfog, that has been prepared as the development software tool of S1C63406/408, is used for this selection. Mask pattern of the IC is finally generated based on the data created by the winfog. Refer to the "S5U1C63000A Manual" for the winfog.

#### <Mask Option List>

The following is the option list for the S1C63406/408.

Multiple selections are available in each option item as indicated in the option list. Using "4 Peripheral Circuits and Operation" as reference, select the spcifications that meet the target system and check the appropriate box. Be sure to record the spcifications for unused functions too, according to the instructions provied.

| 1. OSC1 SY                                      | "STEM CLOCK  □ 1. Crystal (32.768 kHz)  □ 2. CR (60 kHz)                                                       |                                                                                               |

|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| 2. OSC3 SY                                      | STEM CLOCK  ☐ 1. CR ☐ 2. Ceramic (3.58 MHz) ☐ 3. Crystal (4 MHz)                                               |                                                                                               |

| 3. RESET C                                      | EIRCUIT  ☐ 1. Use (1.8 V) ☐ 2. Use (1.6 V) ☐ 3. Use (1.4 V) ☐ 4. Not Use                                       |                                                                                               |

| 4. MULTIPL                                      | E KEY ENTRY RESET C  ☐ 1. Not Use ☐ 2. Use (K00, K01, K02, K0 ☐ 3. Use (K00, K01, K02) ☐ 4. Use (K00, K01)     |                                                                                               |

| 5. MULTIPL                                      | E KEY ENTRY RESET T<br>☐ 1. Not Use<br>☐ 2. Use                                                                | IME AUTHORIZE                                                                                 |

| 6. INPUT PO<br>• K00<br>• K01<br>• K02<br>• K03 | ORT PULL UP RESISTO<br>☐ 1. With Resistor<br>☐ 1. With Resistor<br>☐ 1. With Resistor<br>☐ 1. With Resistor    | R  2. Gate Direct                 |

| 7. OUTPUT  • R10  • R11  • R12  • R13           | PORT OUTPUT SPECIF  1. Complementary  1. Complementary  1. Complementary  1. Complementary  1. Complementary   | ICATION  2. Nch-OpenDrain 2. Nch-OpenDrain 2. Nch-OpenDrain 2. Nch-OpenDrain 2. Nch-OpenDrain |

| 8. I/O PORT                                     | OUTPUT SPECIFICATION  1. Complementary  1. Complementary  1. Complementary  1. Complementary  1. Complementary | ON  □ 2. Nch-OpenDrain □ 2. Nch-OpenDrain □ 2. Nch-OpenDrain □ 2. Nch-OpenDrain               |

#### <Outline of Mask Option>

#### (1) OSC1 oscillation circuit

Crystal or CR oscillation can be selected as the OSC1 oscillation circuit.

Refer to Section 4.3.2, "OSC1 oscillation circuit", for details.

#### (2) OSC3 oscillation circuit

Crystal, ceramic or CR oscillation can be selected as the OSC3 oscillation circuit.

Select item 3 when using a crystal oscillator or item 2 when using a ceramic oscillator. The frequencies in parentheses are recommended typical values. Refer to Section 4.3.3, "OSC3 oscillation circuit", for details.

#### (3) Internal reset circuit

This mask option selects whether the internal reset circuit is used or not. Select a minimum supply voltage according to the oscillation frequency when this circuit is used. Refer to Section 2.2.3, "Internal reset circuit", for details.

#### (4) External reset by simultaneous LOW input to the I/O port (K00–K03)

This function resets the IC when several keys are pressed simultaneously. The mask option is used to select whether this function is used or not. Further when the function is used, a combination of the input terminals (K00-K03), which are connected to the keys to be pressed simultaneously, can be selected. Refer to Section 2.2.2, "Simultaneous low input to terminals K00-K03", for details.

#### (5) Time authorize circuit for the simultaneous LOW input reset function

When using the external reset function (shown in 4 above), using the time authorize circuit or not can be selected by mask option. The reset function works only when the input time of simultaneous LOW is more than the rule time if the time authorize circuit is being used.

Refer to Section 2.2.2, "Simultaneous low input to terminals K00-K03", for details.

#### (6) Input port pull-up resistor

The mask option is used to select whether the pull-up resistor is supplemented to the input ports or not. It is possible to select for each bit of the input ports.

Refer to Section 4.4.2, "Mask option", for details.

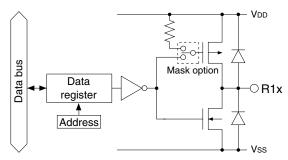

#### (7) Output specification of the output port

Either complementary output or N-channel open drain output can be selected as the output specification for the output ports. The selection is done in 1-bit units.

Refer to Section 4.5.2, "Mask option", for details.

#### (8) Output specification of the I/O ports

For the output specification when the  $\rm I/O$  ports are in the output mode, either complementary output or N-channel open drain output can be selected in 1-bit units.

Refer to Section 4.6.2, "Mask option", for details.

# CHAPTER 2 POWER SUPPLY AND INITIAL RESET

# 2.1 Power Supply

The S1C63406/408 operating power voltage is as follows:

Table 2.1.1 Operating power voltage

| OSC1 clock      | OSC3 clock                            | Operating power voltage | CPU operating voltage (VD1)   |

|-----------------|---------------------------------------|-------------------------|-------------------------------|

|                 | Not use                               | 1.3 V-3.6 V             | 1.1 V                         |

| Max. 80 kHz     | Max. 700 kHz (CR)                     | 1.4 V-3.6 V             | 1.1 V / 1.3 V                 |

| (crystal or CR) | Max. 2.2 MHz (CR)                     | 1.6 V-3.6 V             | 1.1 V / 1.3 V / 1.5 V         |

|                 | Max. 4.2 MHz (crystal, ceramic or CR) | 1.8 V-3.6 V             | 1.1 V / 1.3 V / 1.5 V / 1.7 V |

(When VC1 standard is selected)

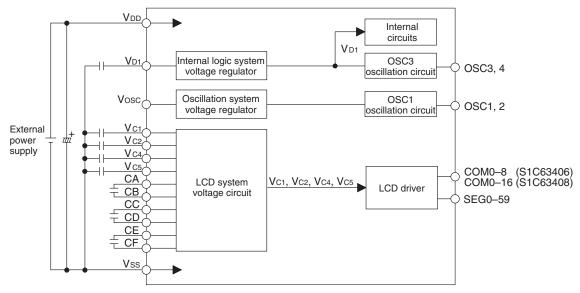

The S1C63406/408 operates by applying a single power supply within the above range between VDD and Vss. The S1C63406/408 itself generates the voltage necessary for all the internal circuits by the built-in power supply circuits shown in Table 2.1.2.

Table 2.1.2 Power supply circuits

| Circuit                                | Power supply circuit                    | Output voltage     |

|----------------------------------------|-----------------------------------------|--------------------|

| OSC1 oscillation circuit               | Oscillation system voltage regulator    | Vosc               |

| OSC3 oscillation and internal circuits | Internal logic system voltage regulator | V <sub>D1</sub>    |

| LCD driver                             | LCD system voltage circuit              | Vc1, Vc2, Vc4, Vc5 |

Notes: • Do not drive external loads with the output voltage from the internal power supply circuits.

• See Chapter 7, "Electrical Characteristics", for voltage values and drive capability.

Fig. 2.1.1 Configuration of power supply

# 2.1.1 Voltage <VD1> for internal circuits

VDI is the voltage for the OSC3 oscillation circuit and the internal logic circuits, and is generated by the internal logic system voltage regulator.

The S1C63406/408 is designed with twin clock specification; it has two types of oscillation circuits OSC1 and OSC3 built-in. Use OSC1 clock for normal operation, and switch it to OSC3 by the software when high-speed operation is necessary. When switching the clock, the operating voltage VD1 must be switched by the software to stabilize the operation of the oscillation circuit and internal circuits.

The internal logic system voltage regulator can output the following four types of VD1 voltage. It should be set at the value according to the oscillation circuit and oscillation frequency by the software.

V<sub>D1</sub> = 1.1 V for low-power operation (when OSC3 oscillation is OFF)

VD1 = 1.3 V for high-speed operation (when Max. 700 kHz OSC3 CR oscillation is ON)

VD1 = 1.5 V for high-speed operation (when Max. 2.2 MHz OSC3 CR oscillation is ON)

V<sub>D1</sub> = 1.7 V for high-speed operation (when Max. 4.2 MHz OSC3 crystal/ceramic/CR oscillation is ON)

Refer to Section 4.3, "Oscillation Circuit", for the VD1 switching procedure.

# 2.1.2 Voltage <Vosc> for OSC1 oscillation circuit

Vosc is the voltage for the OSC1 oscillation circuit and is generated by the oscillation system voltage regulator for stabilizing the oscillation.

# 2.1.3 Voltage < VC1, VC2, VC4, VC5> for LCD driving

VC1, VC2, VC4 and VC5 are the LCD drive voltages generated by the LCD system voltage circuit. These four output voltages can only be supplied to the externally expanded LCD driver.

The LCD system voltage circuit generates VC1 or VC2 with the voltage regulator built-in, and generates three other voltages by boosting or reducing the voltage of VC1 or VC2. Table 2.1.3.1 shows the VC1, VC2, VC4 and VC5 voltage values and boost/reduce status.

|                   | 0 0             |                   |

|-------------------|-----------------|-------------------|

| LCD drive voltage | VDD = 1.3-3.6 V | VDD = 2.5-3.6 V   |

| Vc1 (0.975-1.2 V) | Vc1 (standard)  | 1/2 × Vc2         |

| Vc2 (1.950-2.4 V) | 2 × Vc1         | Vc2 (standard)    |

| Vc4 (2.925-3.6 V) | 3 × Vc1         | 3/2 × Vc2         |

| Vc5 (3.900-4.8 V) | 4 × Vc1         | $2 \times V_{C2}$ |

Table 2.1.3.1 LCD drive voltage when generated internally

Note: The LCD drive voltage can be adjusted by the software (see Section 4.7.5). Values in the above table are typical values.

Either the VC1 or VC2 used for the standard is selected according to the supply voltage by the software. The VC2 standard improves the display quality and reduces current consumption, however, the power supply voltage VDD must be 2.5 V or more.

Refer to Section 4.7, "LCD Driver", for control of the LCD drive voltage.

## 2.2 Initial Reset

To initialize the S1C63406/408 circuits, initial reset must be executed. There are three ways of doing this.

- (1) External initial reset by the RESET terminal

- (2) External initial reset by simultaneous low input to terminals K00-K03 (mask option)

- (3) Internal initial reset by the reset circuit (mask option)

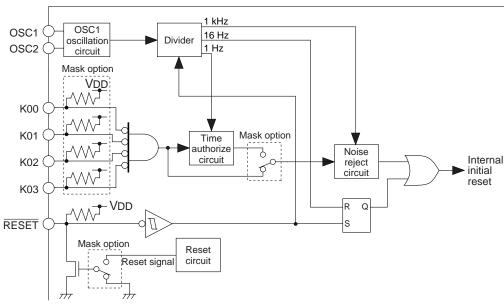

When the power is turned on, be sure to initialize using the reset function. Figure 2.2.1 shows the configuration of the initial reset circuit.

Fig. 2.2.1 Configuration of initial reset circuit

## 2.2.1 Reset terminal ( $\overline{RESET}$ )

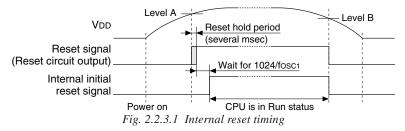

Initial reset can be executed externally by setting the reset terminal to a low level (VSS). After that the initial reset is released by setting the reset terminal to a high level (VDD) and the CPU starts operation. The reset input signal is maintained by the RS latch and becomes the internal initial reset signal. The RS latch is designed to be released by a 16 Hz signal (high) that is divided by the OSC1 clock. Therefore in normal operation, a maximum of 1024/fosc1 seconds (32 msec when fosc1 is 32.768 kHz) is needed until the internal initial reset is released after the reset terminal goes to high level. Be sure to maintain a reset input of 0.1 msec or more.

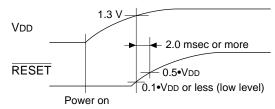

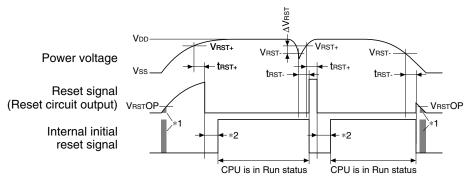

However, when turning the power on, the reset terminal should be set at a low level as in the timing shown in Figure 2.2.1.1.

Fig. 2.2.1.1 Initial reset at power on

The reset terminal should be set to 0.1 • VDD or less (low level) until the supply voltage becomes 1.3 V or more.

After that, a level of 0.5 • VDD or less should be maintained more than 2.0 msec.

#### 2.2.2 Simultaneous low input to terminals K00-K03

Another way of executing initial reset externally is to input a low signal simultaneously to the input ports (K00–K03) selected with the mask option.

Since this initial reset passes through the noise reject circuit, maintain the specified input terminals at low level for at least 1.5 msec (when the oscillation frequency fosc1 is 32.768 kHz) during normal operation. The noise reject circuit does not operate immediately after turning the power on until the oscillation circuit starts oscillating. Therefore, maintain the specified input terminals at low level for at least 1.5 msec (when the oscillation frequency fosc1 is 32.768 kHz) after oscillation starts.

Table 2.2.2.1 shows the combinations of input ports (K00–K03) that can be selected with the mask option.

Table 2.2.2.1 Combinations of input ports

| ı | -1 | 3.T             |

|---|----|-----------------|

|   | 1  | Not use         |

|   | 2  | K00*K01*K02*K03 |

|   | 3  | K00*K01*K02     |

|   | 4  | K00*K01         |

When, for instance, mask option 2 (K00\*K01\*K02\*K03) is selected, initial reset is executed when the signals input to the four ports K00-K03 are all low at the same time. When 3 or 4 is selected, the initial reset is done when a key entry including a combination of selected ports is made.

Further, the time authorize circuit can be selected with the mask option. The time authorize circuit checks the input time of the simultaneous low input and performs initial reset if that time is the defined time (1 to 2 sec) or more. If using this function, make sure that the specified port terminals do not go low at the same time during ordinary operation.

#### 2.2.3 Internal reset circuit

The S1C63406/408 has a built-in reset circuit that can be configured by mask option. This reset circuit provides a system reset function when the power is instantaneously interrupted or drops as well as a power-on reset function that is useful when the power is turned on.

Table 2.2.3.1 Reset circuit options

| 1 | Use 1.8 V |

|---|-----------|

| 2 | Use 1.6 V |

| 3 | Use 1.4 V |

| 4 | Not use   |

When "Use" is selected by mask option, the reset circuit outputs a reset signal after turning the power on until the voltage level on the VDD terminal reaches the reset-release level. It also outputs a reset signal when the power downs below the reset level. Refer to Chapter 7, "Electrical Characteristics", for detailed reset timing chart.

The reset signal is maintained by the RS latch and becomes the internal

initial reset signal. The RS latch is designed to be released by a 16 Hz signal (high) that is divided by the OSC1 clock. Therefore in normal operation, a maximum of 1024/fosc1 seconds (32 msec when fosc1 = 32.768 kHz) is needed until the internal initial reset is released after the reset signal goes to high level.

A voltage level (1.8, 1.6 or 1.4 V) must be selected according to the minimum operating voltage (see Table 2.1.1) when this circuit is used. This selection presets the reset-release level (Level A) and reset level (Level B) to the reset circuit. There is a 40 mV (Typ.) of hysteresis between Levels A and B. See Chapter 7, "Electrical Characteristics", for the preset levels.

Note that the power-on reset circuit increases current consumption. In particular, current consumption in reset status will be greatly increased. See Chapter 7, "Electrical Characteristics", for details. When the "Not Use" option is selected, this circuit does not output a reset signal at power on and down.

- Notes: When using the reset circuit, be sure to connect a capacitor (0.01 µF is recommended) to the reset terminal in order to operate it properly. In this case, to avoid a large current flow in the circuit, do not fix the reset terminal at high level.

- When the internal reset circuit is used, it is not necessary to perform initial resetting using the reset terminal.

# 2.2.4 Internal register at initial resetting

Initial reset initializes the CPU as shown in Table 2.2.4.1.

The registers and flags which are not initialized by initial reset should be initialized in the program if necessary.

In particular, the stack pointers SP1 and SP2 must be set as a pair because all the interrupts including NMI are masked after initial reset until both the SP1 and SP2 stack pointers are set with software.

When data is written to the EXT register, the E flag is set and the following instruction will be executed in the extended addressing mode. If an instruction which does not permit extended operation is used as the following instruction, the operation is not guaranteed. Therefore, do not write data to the EXT register for initialization only.

Refer to the "S1C63000 Core CPU Manual" for extended addressing and usable instructions.

| CPU core               |        |                |               |  |  |  |  |  |  |

|------------------------|--------|----------------|---------------|--|--|--|--|--|--|

| Name                   | Symbol | Number of bits | Setting value |  |  |  |  |  |  |

| Data register A        | A      | 4              | Undefined     |  |  |  |  |  |  |

| Data register B        | В      | 4              | Undefined     |  |  |  |  |  |  |

| Extension register EXT | EXT    | 8              | Undefined     |  |  |  |  |  |  |

| Index register X       | X      | 16             | Undefined     |  |  |  |  |  |  |

| Index register Y       | Y      | 16             | Undefined     |  |  |  |  |  |  |

| Program counter        | PC     | 16             | 0110H         |  |  |  |  |  |  |

| Stack pointer SP1      | SP1    | 8              | Undefined     |  |  |  |  |  |  |

| Stack pointer SP2      | SP2    | 8              | Undefined     |  |  |  |  |  |  |

| Zero flag              | Z      | 1              | Undefined     |  |  |  |  |  |  |

| Carry flag             | C      | 1              | Undefined     |  |  |  |  |  |  |

| Interrupt flag         | I      | 1              | 0             |  |  |  |  |  |  |

| Extension flag         | E      | 1              | 0             |  |  |  |  |  |  |

| Queue register         | Q      | 16             | Undefined     |  |  |  |  |  |  |

Table 2.2.4.1 Initial values

| Peripheral circuits              |   |           |  |  |  |  |  |  |

|----------------------------------|---|-----------|--|--|--|--|--|--|

| Name Number of bits Setting valu |   |           |  |  |  |  |  |  |

| RAM                              | 4 | Undefined |  |  |  |  |  |  |

| Display memory                   | 4 | Undefined |  |  |  |  |  |  |

| Other pheripheral circuits       | - | *         |  |  |  |  |  |  |

\* See Section 4.1, "Memory Map".

# 2.2.5 Terminal settings at initial resetting

The output port (R) terminals and I/O port (P) terminals are shared with special output terminals and input/output terminals of the serial interface. These functions are selected by the software. At initial reset, these terminals are set to the general purpose output port terminals and I/O port terminals. Set them according to the system in the initial routine. In addition, take care of the initial status of output terminals when designing a system.

Table 2.2.5.1 shows the list of the shared terminal settings.

| Terminal | Terminal status              | Specia | loutput | Serial I/F |         |         |  |

|----------|------------------------------|--------|---------|------------|---------|---------|--|

| name     | at initial reset             | TOUT   | FOUT    | Master     | Slave   | Async.  |  |

| R10      | R10 (High level output)      |        |         |            |         |         |  |

| R11      | R11 (High level output)      |        |         |            |         |         |  |

| R12      | R12 (High level output)      | TOUT   |         |            |         |         |  |

| R13      | R13 (High level output)      |        | FOUT    |            |         |         |  |

| P20      | P20 (Input mode & Pulled-up) |        |         | SIN(I)     | SIN(I)  | SIN(I)  |  |

| P21      | P21 (Input mode & Pulled-up) |        |         | SOUT(O)    | SOUT(O) | SOUT(O) |  |

| P22      | P22 (Input mode & Pulled-up) |        |         | SCLK(O)    | SCLK(I) |         |  |

| P23      | P23 (Input mode & Pulled-up) |        |         |            | SRDY(O) |         |  |

Table 2.2.5.1 List of shared terminal settings

For setting procedure of the functions, see explanations for each of the peripheral circuits.

# 2.3 Test Terminal ( $\overline{TEST}$ )

This is the terminal used for the factory inspection of the IC. During normal operation, connect the  $\overline{\text{TEST}}$  terminal to VDD.

# CHAPTER 3 CPU, ROM, RAM

## 3.1 *CPU*

The S1C63406/408 has a 4-bit core CPU S1C63000 built-in as its CPU part.

Refer to the "S1C63000 Core CPU Manual" for the S1C63000.

The S1C63406/408 supports the SLEEP function.

## 3.2 Code ROM

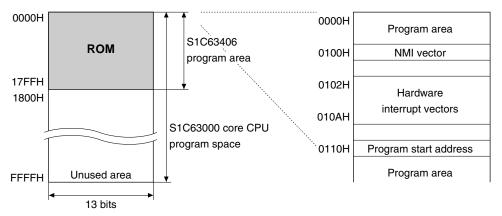

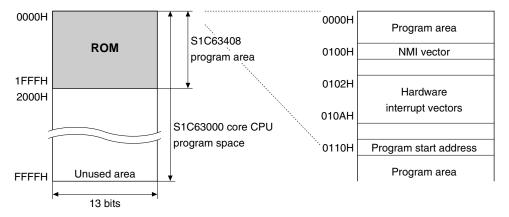

The built-in code ROM is a mask ROM for loading programs. The S1C63406 has a built-in 6,144 steps  $\times$  13 bits of code ROM. The S1C63408 has a built-in 8,192 steps  $\times$  13 bits of code ROM.

The core CPU can linearly access the program space up to step FFFFH from step 0000H, however, the program areas of the S1C63406 and S1C63408 are step 0000H to step 17FFH and step 0000H to step 1FFFH, respectively. The program start address after initial reset is assigned to step 0110H. The non-maskable interrupt (NMI) vector and hardware interrupt vectors are allocated to step 0100H and steps 0102H–010AH, respectively.

#### S1C63406

#### S1C63408

Fig. 3.2.1 Configuration of code ROM

#### 3.3 RAM

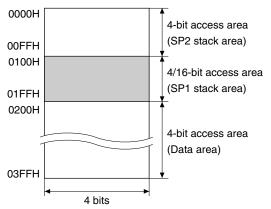

The RAM is a data memory for storing various kinds of data, and has a capacity of 1,024 words  $\times$  4 bits. The RAM area is assigned to addresses 0000H to 03FFH on the data memory map. Addresses 0100H to 01FFH are 4-bit/16-bit data accessible areas and in other areas it is only possible to access 4-bit data. When programming, keep the following points in mind.

- (1) Part of the RAM area is used as a stack area for subroutine call and register evacuation, so pay attention not to overlap the data area and stack area.

- (2) The S1C63000 core CPU handles the stack using the stack pointer for 4-bit data (SP2) and the stack pointer for 16-bit data (SP1).

- 16-bit data are accessed in stack handling by SP1, therefore, this stack area should be allocated to the area where 4-bit/16-bit access is possible (0100H to 01FFH). The stack pointers SP1 and SP2 change cyclically within their respective range: the range of SP1 is 0000H to 03FFH and the range of SP2 is 0000H to 00FFH. Therefore, pay attention to the SP1 value because it may be set to 0200H or more exceeding the 4-bit/16-bit accessible range in the S1C63406/408 or it may be set to 00FFH or less. Memory accesses except for stack operations by SP1 are 4-bit data access.

- After initial reset, all the interrupts including NMI are masked until both the stack pointers SP1 and SP2 are set by software. Further, if either SP1 or SP2 is re-set when both are set already, the interrupts including NMI are masked again until the other is re-set. Therefore, the settings of SP1 and SP2 must be done as a pair.

- (3) Subroutine calls use 4 words (for PC evacuation) in the stack area for 16-bit data (SP1). Interrupts use 4 words (for PC evacuation) in the stack area for 16-bit data (SP1) and 1 word (for F register evacuation) in the stack area for 4-bit data.

Fig. 3.3.1 Configuration of data RAM

#### 3.4 Data ROM

The data ROM is a mask ROM for loading various static data such as a character generator, and the data can be read using the same data memory access instructions as the RAM.

The S1C63406 has a built-in 3,072 words  $\times$  4 bits of data ROM and it is assigned to addresses 8000H to 8BFFH on the data memory map.

The S1C63408 has a built-in 4,096 words  $\times$  4 bits of data ROM and it is assigned to addresses 8000H to 8FFFH on the data memory map.

# CHAPTER 4 PERIPHERAL CIRCUITS AND OPERATION

The peripheral circuits of S1C63406/408 (timer, I/O, etc.) are interfaced with the CPU in the memory mapped I/O method. Thus, all the peripheral circuits can be controlled by accessing the I/O memory on the memory map using the memory operation instructions. The following sections explain the detailed operation of each peripheral circuit.

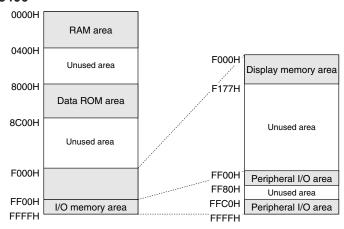

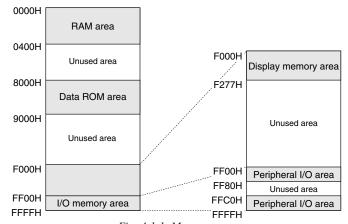

# 4.1 Memory Map

The S1C63406 data memory consists of 1,024-word RAM, 3,072-word data ROM, 540-bit display memory and 50-word peripheral I/O memory.

The S1C63408 data memory consists of 1,024-word RAM, 4,096-word data ROM, 1,020-bit display memory and 50-word peripheral I/O memory.

Figure 4.1.1 shows the overall memory map of the S1C63406/408, and Tables 4.1.1(a)–(d) the peripheral circuits' (I/O space) memory maps.

#### S1C63406

#### S1C63408

Fig. 4.1.1 Memory map

Note: Memory is not implemented in unused areas within the memory map. Further, some non-implementation areas and unused (access prohibition) areas exist in the display memory area and the peripheral I/O area. If the program that accesses these areas is generated, its operation cannot be guaranteed. Refer to Section 4.7.4, "Display memory", for the display memory, and the I/O memory maps shown in Tables 4.1.1 (a)–(d) for the peripheral I/O area.

Table 4.1.1 (a) I/O memory map (FF00H-FF4AH)

| Address   Common      |         |         |         |             | 1001         | 1.1.1   | (4) 1/ | O mem  | ory ma  | p (FF00H-FF4AH)                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|-------------|--------------|---------|--------|--------|---------|-----------------------------------------------------------------------------------|

| FF00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Address |         |         |             |              |         |        |        |         | Comment                                                                           |

| FF60H   FF60   |         | D3      | D2      | D1          | D0           | -       |        |        | _       |                                                                                   |

| FF04H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         | CI KCHG | oscc    | VDC1        | VDC0         |         | -      |        |         |                                                                                   |

| FF48H   SVDS3   SVDS2   SVDS1   SVDS3   SVDS2   SVDS3   SVDS2   SVDS3   SVDS   | FF00H   |         |         |             |              | { I     | -      | On     | Off     |                                                                                   |

| FF64H   FF64   |         |         | R       | w           |              |         | -      |        |         |                                                                                   |

| SVDS3   SVDS2   SVDS1   SVDS0   SVDS2   SVDS2   SVDS2   SVDS2   SVDS2   SVDS3   SVDS2   SVDS3   SVD3   SVD3   SVDS3   SVD3      |         |         | In/VV   |             |              | VDC0    | 0      |        |         |                                                                                   |

| FF64H   FF64   |         | SNDS3   | SNDSS   | SVDS1       | SYDSU        | SVDS3   | 0      |        |         |                                                                                   |

| FF48H   FF48   | FENAH   | 37033   | 31032   | 34031       | 37030        | SVDS2   | 0      |        |         |                                                                                   |

| FF69H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 110411  |         | В       | ΛΑ/         |              | SVDS1   | 0      |        |         |                                                                                   |

| FF68H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |         | Π/      | VV          |              | SVDS0   | 0      |        |         |                                                                                   |

| FF69H   FF69H   FOUTE   FOF02   FOF01   FOF02   FOF02   FOF02   FOF02   FOF02   FOF03   FOF0   |         | _       | _       | CVDDT       | CVDON        | 0 *3    | _ *2   |        |         | Unused                                                                            |

| FF42H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | FEOGLI  | "       | U       | 20001       | SVDON        | 0 *3    | _ *2   |        |         | Unused                                                                            |