# Radiation hard 16-Bit ParallelError Detection & Correction

DS3595-5.0 January 2000

Replaces June 1999 version, DS3595-4.0

The 54HSC/T630 is a 16-bit parallel Error Detection and Correction circuit. It uses a modified Hamming code to generate a 6-bit check word from each 16-bit data word. The check word is stored with the data word during a memory write cycle. During a memory read cycle a 22-bit word is taken from memory and checked for errors.

Single bit errors in data words are flagged and corrected. Single bit errors in check words are flagged but not corrected. The position of the incorrect bit is pinpointed, in both cases, by the 6-bit error syndrome code which is output during the error correction cycle.

Two bit errors are flagged but not corrected. Any combination of two bit errors occurring within the 22-bit word read from memory, (ie two errors in the 16-bit data word, two bits in the 16-bit check word or one error in each) will be correctly identified.

The gross errors of all bits, low or high, will be detected.

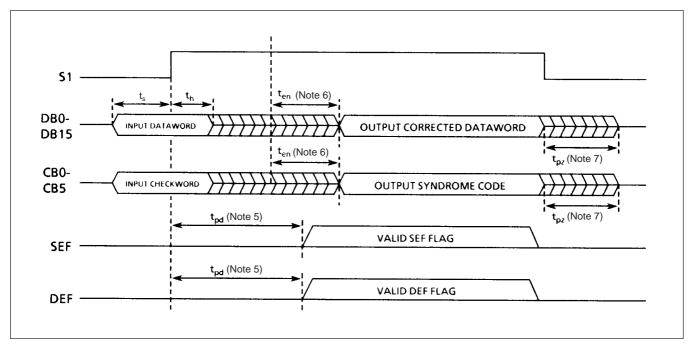

The control signals S1 and S0 select the function to be performed by the EDAC They control the generation of check words and the latching and correction of data (see table 1) When errors are detected, flags are placed on outputs SEF and DEF (see table 2).

# SO FUNCTION SELECTOR FLAG ENABLE CHECK MASK DATA ENABLE LATCH DATA ERROR GENERATOR CHECK WORD CB(5:0) FLAG ENABLE FLAG ENABLE FLAG ENABLE FLAG ENABLE

Figure 1: Block Diagram

# **FEATURES**

■ Radiation Hard:

Dose Rate Upset Exceeding 3x10<sup>10</sup> Rad(Si)/sec Total Dose for Functionality Upto 1x10<sup>6</sup> Rad(Si)

- High SEU Immunity, Latch Up Free

- CMOS-SOS Technology

- All Inputs and Outputs Fully TTL Compatible (54HST630) or CMOS Compatible (54HSC630)

- Low Power

- Detects and Corrects Single-Bit Errors

- Detects and Flags Dual-Bit Errors

- High Speed:

Write Cycle - Generates Checkword In 40ns Typical

Read Cycle - Flags Errors In 20ns Typical

# 54HSC/T630

|       | Control |      |                                               |                             |                      | Error Flag | s       |

|-------|---------|------|-----------------------------------------------|-----------------------------|----------------------|------------|---------|

| Cycle | S1      | S0   | EDAC Function                                 | Data UO                     | Checkword            | SEF        | DEF     |

| WRITE | Low     | Low  | Generates Checkword                           | Input Data                  | Output Checkword     | Low        | Low     |

| READ  | Low     | High | Read Data BCheckword                          | Input Data                  | Input Checkword      | Low        | Low     |

| READ  | High    | High | Latch & Flag Error                            | Latch Data                  | Latch Checkword      | Enabled    | Enabled |

| READ  | High    | Low  | Correct Data Word &<br>Generate Syndrome Bits | Output<br>Corrected<br>Data | Output Syndrome Bits | Enabled    | Enabled |

Table 1: Control Functions

| Total Nu    | mber of Errors  | Error | Flags | Data Correction |  |  |

|-------------|-----------------|-------|-------|-----------------|--|--|

| 16-bit Data | 6-bit Checkword | SEF   | DEF   |                 |  |  |

| 0           | 0               | Low   | Low   | Not Applicable  |  |  |

| 1           | 0               | High  | Low   | Correction      |  |  |

| 0           | 1               | High  | Low   | Correction      |  |  |

| 1           | 1               | High  | High  | Interrupt       |  |  |

| 2           | 0               | High  | High  | Interrupt       |  |  |

| 0           | 2               | High  | High  | Interrupt       |  |  |

Table 2: Error Functions

#### **ERROR DETECTION & CORRECTION**

During a memory write cycle, six check bits (CBO-CB5) are generated by eight-input parity generators using the data bits defined in Table 3. During a memory read cycle, the 6-bit checkword is retrieved along with the actual data.

Error detection is accomplished as the 6-bit checkword and the 16-bit data word from memory are applied to internal parity generators/checkers. If the parity of all six groupings of data and check bits are correct, it is assumed that no error has occurred and both error flags will be low. It should be noted that the sense of two of the check bits, bits CBO and CB1, is inverted to ensure that the gross-error condition of all lows and all highs is detected.

If the parity of one or more of the check groups is incorrect, an error has occurred and the proper error flag or flags will be set high. Any single error in the 16bit data word will change the sense of exactly three bits of the 6-bit checkword. Any single error in the 6bit checkword changes the sense of only that one bit. In either case, the single error flag will be set high while the dual error flag will remain low.

Any two-bit error will change the sense of an even number of check bits. The two-bit error is not correctable since the parity tree can only identify singlebit errors. Both error flags are set high when any two-bit error is detected.

Three or more simultaneous bit errors cause the EDAC to transmit that no error, a correctable error, or an uncorrectable error has occurred and hence produce erroneous results in all three cases.

Error correction is accomplished by identifying the bad bit and inverting it. Identification of the erroneous bit is achieved by comparing the 16-bit word and 6-bit checkword from memory with the new checkword with one (checkword error) or three (data word error) inverted bits.

As the corrected word is made available on the data word I/O port, the checkword I/O port presents a 6-bit syndrome error code. This syndrome code can be used to identify the corrupted bit in memory (see Table 4. overleaf).

| Ole a all accord |   | 16-bit Data Word |   |   |   |   |   |   |   |   |    |    |    |    |    |    |

|------------------|---|------------------|---|---|---|---|---|---|---|---|----|----|----|----|----|----|

| Checkword<br>Bit | 0 | 1                | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

| CB0              | Х | Х                |   | Х | Х |   |   |   | Х | Х | Х  |    |    | Х  |    |    |

| CB1              | Х |                  | Х | Х |   | Х | Х |   | Х |   |    | Х  |    |    | Χ  |    |

| CB2              |   | Х                | Х |   | Χ | X |   | X |   | X |    |    | X  |    |    | X  |

| CB3              | Х | Х                | Х |   |   |   | Х | Х |   |   | Х  | Х  | Х  |    |    |    |

| CB4              |   |                  |   | Х | Χ | Х | Х | Х |   |   |    |    |    | Χ  | Χ  | Х  |

| CB5              |   |                  |   |   |   |   |   |   | X | X | Х  | Х  | Х  | Х  | Χ  | Х  |

The six check bits are partly bits derived from the matrix of data bits as indicated by 'X' for each bit.

Table 3: Check Word Generation

| Syndrome      |     | Error Location |     |     |     |     |     |     |     |     |      |      |      |      |      |      |     |     |     |     |     |     |             |

|---------------|-----|----------------|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-------------|

| Error<br>Code | DB0 | DB1            | DB2 | DB3 | DB4 | DB5 | DB6 | DB7 | DB8 | DB9 | DB10 | DB11 | DB12 | DB13 | DB14 | DB15 | СВО | CB1 | CB2 | СВЗ | СВ4 | CB5 | No<br>Error |

| CB0           | L   | L              | Н   | L   | L   | Н   | Н   | Н   | L   | L   | L    | Н    | Н    | L    | Н    | Н    | L   | Н   | Н   | Н   | Н   | Н   | Н           |

| CB1           | L   | Н              | L   | L   | Н   | L   | L   | Н   | L   | Н   | Н    | L    | Н    | Н    | L    | Н    | Н   | L   | Н   | Н   | Н   | Н   | Н           |

| CB2           | Н   | L              | L   | Н   | L   | L   | Н   | L   | Н   | L   | Н    | Н    | L    | Н    | Н    | L    | Н   | Н   | L   | Н   | Н   | Н   | Н           |

| CB3           | L   | L              | L   | Н   | Н   | Н   | L   | L   | Н   | Н   | L    | L    | L    | Н    | Н    | Н    | Н   | Н   | Н   | L   | Н   | Н   | Н           |

| CB4           | Н   | Н              | Н   | L   | L   | L   | L   | L   | Н   | Н   | Н    | Н    | Н    | L    | L    | L    | Н   | Н   | Н   | Н   | L   | Н   | Н           |

| CB5           | Н   | Н              | Н   | Н   | Н   | Н   | Н   | Н   | L   | L   | L    | L    | L    | L    | L    | L    | Н   | Н   | Н   | Н   | Н   | L   | Н           |

Table 4: Error Syndrome Codes

# **APPLICATIONS**

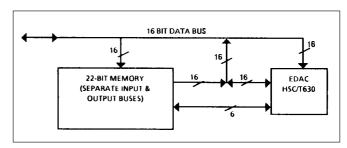

Although many semiconductor memories have separate input and output pins, it is possible to design the error detection and correction function using a single EDAC. EDAC data and check bit pins function as inputs or outputs dependent upon the state of control signals S0 and S1. It becomes necessary to use wired AND logic, with fairly complex timing system, to control the EDAC and data bus. This scheme becomes difficult to implement both in terms of board layout and timing. System performance is also adversely affected, See Figure 2.

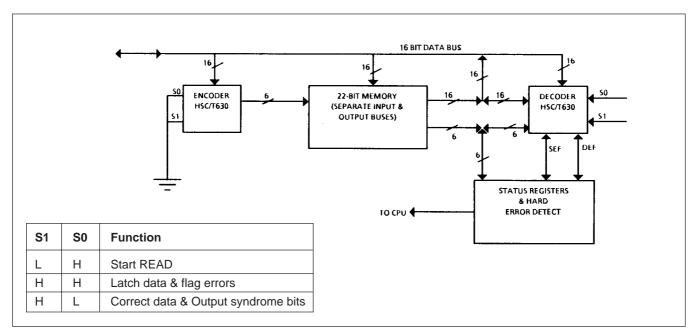

Optimised systems can be implemented using two EDAC's in parallel, One of the units is used strictly as an encoder during the memory write cycle. Both controls S0 and SI are grounded, The encoder chip will generate the 6-bit check word for memory storage along with the 16-bit data.

The second of the two EDAC's will be used as a decoder during the memory read cycle. This decoder chip requires timing pulses for correct operation. Control S1 is set low and S0 high as the memory read cycle begins. After the memory output data is valid, the control S1 input is moved from the low to a high. This low-to-high transition latches the 22-bit word from memory into internal registers of this second EDAC and enables the two error flags. If no error occurs, the CPU can accept the 16-bit word directly from memory. If a single error has occurred, the CPU must move the control SO input from the high to a low to output corrected data and the error syndrome bits. Any dual error should be an interrupt condition.

In most applications, status registers will be used to keep tabs on error flags and error syndrome bits. If repeated patterns of error flags and syndrome bits occur, the CPU will be able to recognize these symptoms as a "hard" error. The syndrome bits can be used to pinpoint the faulty memory chip, See Figure 3.

Figure 2: Error Detection and Correction Using a Single EDAC Unit

# 54HSC/T630

Figure 3: Error Detection and Correction Using Two EDAC Units

# **DEFINITION OF SUBGROUPS**

| Subgroup | Definition                                               |

|----------|----------------------------------------------------------|

| 1        | Static characteristics specified in Table 6 at +25°C     |

| 2        | Static characteristics specified in Table 6 at +125°C    |

| 3        | Static characteristics specified in Table 6 at -55°C     |

| 9        | Switching characteristics specified in Table 7 at +25°C  |

| 10       | Switching characteristics specified in Table 7 at +125°C |

| 11       | Switching characteristics specified in Table 7 at -55°C  |

|          |                                                          |

# DC CHARACTERISTICS AND RATINGS

| Parameter               | Min                  | Max                  | Units |

|-------------------------|----------------------|----------------------|-------|

| Supply Voltage          | -0.5                 | 7                    | V     |

| Input Voltage           | V <sub>SS</sub> -0.3 | V <sub>DD</sub> +0.3 | V     |

| Current Through Any Pin | -20                  | +20                  | mA    |

| Operating Temperature   | -55                  | 125                  | °C    |

| Storage Temperature     | -65                  | 150                  | °C    |

Table 5: Absolute Maximum Ratings

**Note:** Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these conditions, or at any other condition above those indicated in the operations section of this specification, is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

|                  |                          |                                                                                            | Total do             |     |     |       |

|------------------|--------------------------|--------------------------------------------------------------------------------------------|----------------------|-----|-----|-------|

| Symbol           | Parameter                | Conditions                                                                                 | Min                  | Тур | Max | Units |

| V <sub>DD</sub>  | Supply Voltage           | -                                                                                          | 4.5                  | 5.0 | 5.5 | V     |

| V <sub>IH1</sub> | TTL Input High Voltage   | -                                                                                          | 2.0                  | -   | -   | V     |

| V <sub>IL1</sub> | TTL Input Low Voltage    | -                                                                                          | -                    | -   | 0.8 | V     |

| V <sub>IH2</sub> | CMOS Input High Voltage  | -                                                                                          | 3.5                  | -   | -   | V     |

| V <sub>IL2</sub> | CMOS Input Low Voltage   | -                                                                                          | -                    | -   | 1.5 | V     |

| V <sub>OH1</sub> | TTL Output High Voltage  | $I_{OH} = -4mA$                                                                            | 2.4                  | -   | -   | V     |

| V <sub>OL1</sub> | TTL Output Low Voltage   | $I_{OL} = 12$ mA (CB or DB),<br>$I_{OL} = 4$ mA (SEF or DEF)                               | -                    | -   | 0.4 | V     |

| V <sub>OH2</sub> | CMOS Output High Voltage | $I_{OH} = -4mA$                                                                            | V <sub>DD</sub> -0.5 | -   | -   | V     |

| V <sub>OL2</sub> | CMOS Output Low Voltage  | $I_{OL} = 12$ mA (CB or DB),<br>$I_{OL} = 4$ mA (SEF or DEF)                               | -                    | -   | 0.5 | V     |

| I <sub>1L</sub>  | Input Low Current        | $V_{DD} = 5.5$ , $V_{IN} = V_{SS}$                                                         | -                    | -   | -10 | μΑ    |

| I <sub>1H</sub>  | Input High Current       | $V_{DD} = 5.5, V_{IN} = V_{DD}$                                                            | -                    | -   | 50  | μΑ    |

| I <sub>2L</sub>  | IO Low Current           | $V_{DD} = 5.5$ , $V_{IN} = V_{SS}$                                                         | -                    | -   | -50 | μΑ    |

| I <sub>2H</sub>  | IO High Current          | $V_{DD} = 5.5, V_{IN} = V_{DD}$                                                            | -                    | -   | 50  | μΑ    |

| I <sub>DD</sub>  | Power Supply Current     | V <sub>DD</sub> = Max, S0 & S1 at<br>5.5V, All CB & DB pins<br>grounded, DEF & SEF<br>open | -                    | -   | 1   | mA    |

$V_{DD} = 5V \pm 10\%$ , over full operating temperature range.

Parameters at higher radiation levels available on request.

Table 6: Electrical Characteristics

# **AC ELECTRICAL CHARACTERISTICS**

| Parameter                                                                  | From<br>(Input) | To<br>(Output) | Min. | Max. | Units | Conditions (HST) | Conditions (HSC)                  |

|----------------------------------------------------------------------------|-----------------|----------------|------|------|-------|------------------|-----------------------------------|

| t <sub>PLH</sub> Propogation delay time, low-to-high-level output (Note 4) | DB              | СВ             | -    | 58   | ns    | S0 = 0V, S1 = 0V | S0 = 0V, S1 = 0V                  |

| t <sub>PLH</sub> Propogation delay time, low-to-high-level output (Note 4) | DB              | СВ             | -    | 58   | ns    | S0 = 0V, S1 = 0V | S0 = 0V, S1 = 0V                  |

| t <sub>PLH</sub> Propogation delay time, low-to-high-level output (Note 5) | S1 ↑            | DEF            | -    | 29   | ns    | S0 = 3V          | $S0 = V_{DD}-1V$                  |

| t <sub>PLH</sub> Propogation delay time, low-to-high-level output (Note 5) | S1 ↑            | SEF            | -    | 29   | ns    | S0 = 3V          | $S0 = V_{DD}-1V$                  |

| t <sub>PZH</sub> Output enable time to high level (Note 6)                 | S0 ↓            | CB, DB         | -    | 40   | ns    | S1 = 3V (fig. 5) | $S1 = V_{DD}-1V \text{ (fig. 5)}$ |

| t <sub>PZL</sub> Output enable time to low level (Note 6)                  | S0              | CB, DB         | -    | 45   | ns    | S1 = 3V (fig. 4) | $S1 = V_{DD}-1V \text{ (fig. 4)}$ |

| t <sub>PHZ</sub> Output disable time to high level (Note 7)                | S0 ↑            | CB, DB         | -    | 45   | ns    | S1 = 3V (fig. 5) | $S1 = V_{DD}-1V \text{ (fig. 5)}$ |

| t <sub>PLZ</sub> Output disable time to low level (Note 7)                 | S0 ↑            | CB, DB         | -    | 65   | ns    | S1 = 3V (fig. 4) | $S1 = V_{DD}-1V$ (fig. 4)         |

| t <sub>S</sub> Set-up time to S1 >                                         | CB, DB          | -              | 30   | -    | ns    | -                | -                                 |

| t <sub>H</sub> Hold time after S1 >                                        | CB, DB          | -              | 15   | -    | ns    | -                | -                                 |

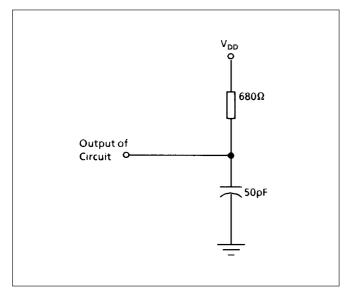

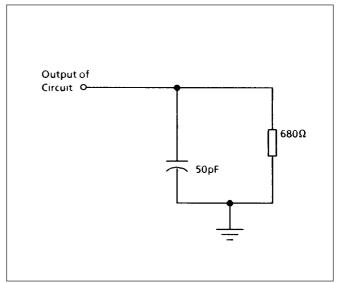

<sup>1.</sup>  $V_{DD}$  = 5V ±10% and CL = 50pF, over full operating temperature and total dose = 300K Rad(Si) 2. Input Pulse  $V_{SS}$  to 3.0 Volts.(TTL),  $V_{DD}$  -1V (CMOS).

Table 7: AC Electrical Characteristics

Mil-Std-883, method 5005, subgroups 1, 2, 3

<sup>3.</sup> Times Measurement Reference Level 1.5 Volts.

<sup>4.</sup> These parameters describe the time intervals taken to generate the check word during the memory write cycle.

<sup>5.</sup> These parameters describe the time intervals taken to flag errors during memory read cycle.

<sup>6.</sup> These parameters describe the time intervals taken to correct and output the data word and to generate and output the syndrome error code during the memory read cycle.

<sup>7.</sup> These parameters describe the time intervals taken to disable the CB & DB buses in preparation for a new data word during the memory read cycle.

<sup>8.</sup> Mil-Std-883, method 5005, subgroups 9, 10, 11

<sup>9.</sup> Parameters at higher radiation levels available on request.

# 54HSC/T630

Figure 4: Output Load Circuit

Figure 5: Output Load Circuit

Figure 6: Read, Flag and Correct, Made Switching Waveforms

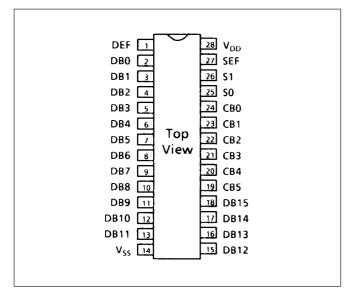

#### **PIN ASSIGNMENTS**

DEF 28 ] v<sub>DD</sub> SEF DB0 **S**1 DB1 26 **S**0 DB2 4 DB3 24 CB0 CB1 DB4 Top 6 23 CB2 D85 View 22 CB3 DB6 21 DB7 9 20 CB4 10 ] CB5 DB8 L 19 DB9 11 18 **DB15** ] DB14 DB10 [ 12 17 DB11 13 16 DB13  $V_{SS}$ 14 ] DB12

Figure 7: 28-Lead Ceramic DIL (Solder Seal)

- Package Style C

Figure 8: 28-Lead Flatpack (Solder Seal) - Package Style F

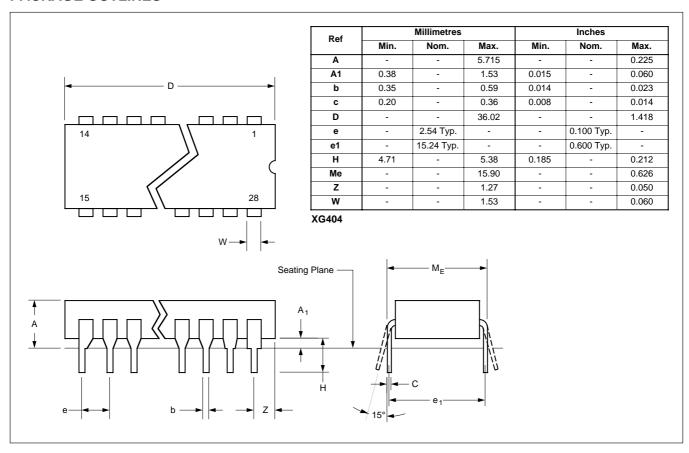

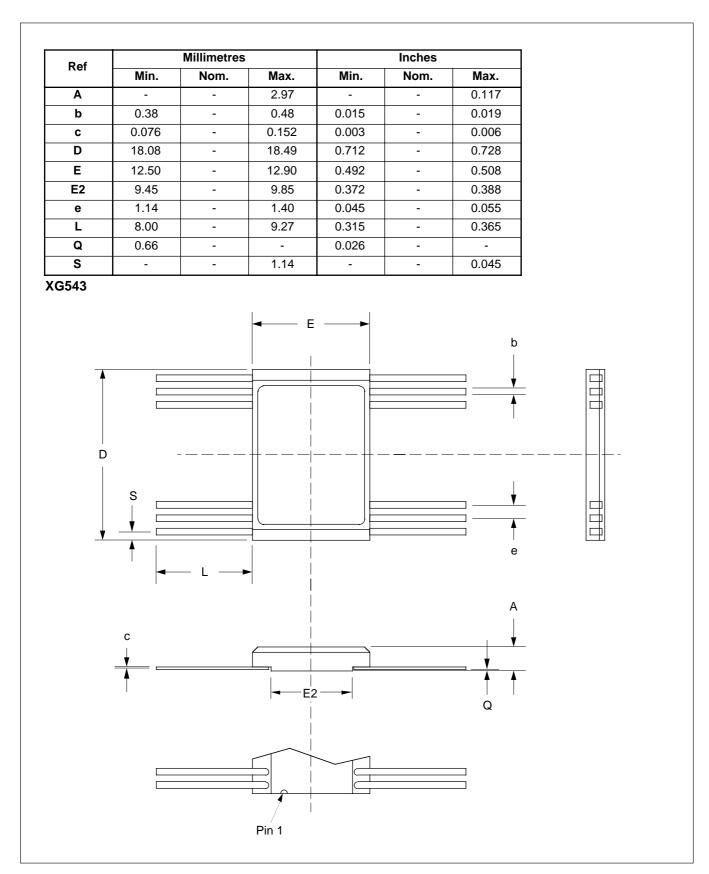

# **PACKAGE OUTLINES**

Figure 9: 28-Lead Ceramic DIL (Solder Seal) - Package Style C

Figure 10: 28-Lead Ceramic Flatpack (Solder Seal) - Package Style F

#### RADIATION TOLERANCE

#### **Total Dose Radiation Testing**

For product procured to guaranteed total dose radiation levels, each wafer lot will be approved when all sample devices from each lot pass the total dose radiation test.

The sample devices will be subjected to the total dose radiation level (Cobalt-60 Source), defined by the ordering code, and must continue to meet the electrical parameters specified in the data sheet. Electrical tests, pre and post irradiation, will be read and recorded.

GEC Plessey Semiconductors can provide radiation testing compliant with Mil-Std-883 method 1019 lonizing Radiation (total dose) test.

| Total Dose (Function to specification)*      | 3x10 <sup>5</sup> Rad(Si)             |

|----------------------------------------------|---------------------------------------|

| Transient Upset (Stored data loss)           | 5x10 <sup>10</sup> Rad(Si)/sec        |

| Transient Upset (Survivability)              | >1x10 <sup>12</sup> Rad(Si)/sec       |

| Neutron Hardness (Function to specification) | >1x10 <sup>15</sup> n/cm <sup>2</sup> |

| Single Event Upset**                         | <1x10 <sup>-10</sup> Errors/bit day   |

| Latch Up                                     | Not possible                          |

<sup>\*</sup> Other total dose radiation levels available on request

Figure 11: Radiation Hardness Parameters

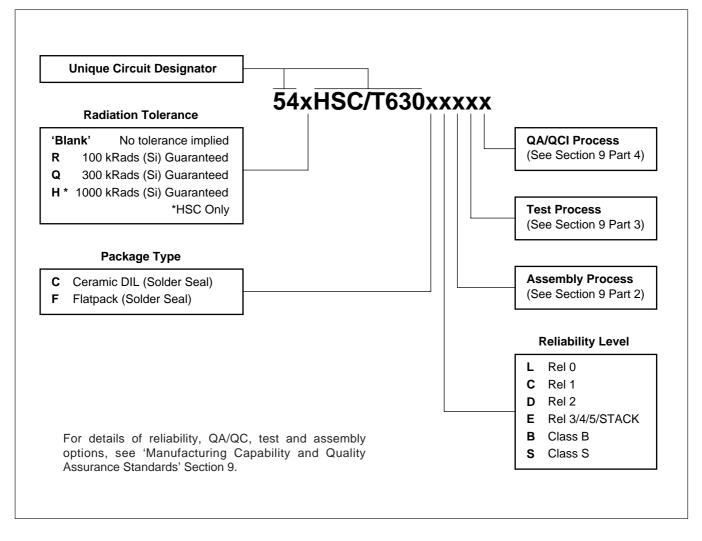

# ORDERING INFORMATION

<sup>\*\*</sup> Worst case galactic cosmic ray upset - interplanetary/high altitude orbit

## http://www.dynexsemi.com

e-mail: power\_solutions@dynexsemi.com

HEADQUARTERS OPERATIONS

DYNEX SEMICONDUCTOR LTD

Doddington Road, Lincoln. Lincolnshire. LN6 3LF. United Kingdom. Tel: 00-44-(0)1522-500500

Fax: 00-44-(0)1522-500550

#### DYNEX POWER INC.

Unit 7 - 58 Antares Drive, Nepean, Ontario, Canada K2E 7W6. Tel: 613.723.7035

Fax: 613.723.1518

Toll Free: 1.888.33.DYNEX (39639)

CUSTOMER SERVICE CENTRES

France, Benelux, Italy and Spain Tel: +33 (0)1 69 18 90 00. Fax: +33 (0)1 64 46 54 50

North America Tel: 011-800-5554-5554. Fax: 011-800-5444-5444

UK, Germany, Scandinavia & Rest Of World Tel: +44 (0)1522 500500. Fax: +44 (0)1522 500020

SALES OFFICES

France, Benelux, Italy and Spain Tel: +33 (0)1 69 18 90 00. Fax: +33 (0)1 64 46 54 50

Germany Tel: 07351 827723

North America Tel: (613) 723-7035. Fax: (613) 723-1518. Toll Free: 1.888.33.DYNEX (39639) /

Tel: (831) 440-1988. Fax: (831) 440-1989 / Tel: (949) 733-3005. Fax: (949) 733-2986.

**UK, Germany, Scandinavia & Rest Of World** Tel: +44 (0)1522 500500. Fax: +44 (0)1522 500020 These offices are supported by Representatives and Distributors in many countries world-wide.

© Dynex Semiconductor 2000 Publication No. DSxxxx-y Issue No. x.x January 2000 TECHNICAL DOCUMENTATION – NOT FOR RESALE. PRINTED IN UNITED KINGDOM

## Datasheet Annotations:

Dynex Semiconductor annotate datasheets in the top right hard corner of the front page, to indicate product status. The annotations are as follows:-

Target Information: This is the most tentative form of information and represents a very preliminary specification. No actual design work on the product has been started.

Preliminary Information: The product is in design and development. The datasheet represents the product as it is understood but details may change.

Advance Information: The product design is complete and final characterisation for volume production is well in hand.

No Annotation: The product parameters are fixed and the product is available to datasheet specification.

This publication is issued to provide information only which (unless agreed by the Company in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. The Company reserves the right to alter without prior notice the specification, design or price of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to the Company's conditions of sale, which are available on request.

All brand names and product names used in this publication are trademarks, registered trademarks or trade names of their respective owners