### Parallel EEPROMs Compiler

### Preliminary

United To Excel

### **Features**

- Flexible Architecture

- 16-16K words

- Max 64K bits

- Support Data Bus width 4-128 bits in 4 bit increments

- Fast Read Access Time - 100ns

- Fast Self-Timed Byte Write Cycle

- 1ms

- Internal Address and Data Latches

- Internal Control Timer

- Automatic Clear Before Write

- Fast Self-Timed Write All

- Automatic Clear Before Write

- Direct Microprocessor Control

READY/BUSY

- General Description

The EEPROM Compiler will generate low-power, high-performance Electrically Erasable and Programmable Read Only Memory with easy to use features. The device is manufactured with ICT's reliable nonvolatile CMOS technology.

### Figure 1 Pin Configurations

| Pin Name      | Function            |

|---------------|---------------------|

| A0 - A13*     | Addresses           |

| CE            | Chip Enable         |

| ŌE            | Output Enable       |

| WE            | Write Enable        |

| I/O0 - I/O31* | Data Inputs/Outputs |

| RDY/BUSY      | Ready/Busy Output   |

| ALLEN         | Write All Enable    |

| RESET         | RESET Input         |

\* number of addresses and I/O's are determined by user specified architecture

- 3.3V ± 10% Supply

- Low Power - 5 mA Active Current - 10 µA CMOS Standby Current

- High Reliability

- Endurance: 10<sup>5</sup> Cycles - Data Retention: 10 Years

- Direct Microprocessor Control

Asynchronous clear

- Independent output enables

- Commercial and Industrial Temperature Ranges

- Advanced Double Poly Triple Metal Embedded EEPROM Process

The EEPROM Compiler is accessed like a static RAM for the read or write cycles without the need of external components. During a byte write, the address and data are latched internally, freeing the microprocessor address and data bus for other operations. Following the initiation of a write cycle, the device will go to a busy state and automatically clear and write the latched data using an internal control timer. The device includes a method for detecting the end of a write cycle, level detection of RDY/BUSY. Once the end of a write cycle has been detected, a new access for a read or a write can begin.

The CMOS technology offers fast access times of 100 ns at low power dissipation. When the chip is deselected the standby current is less than 10  $\mu A.$

Integrated Circuit Technology Corp. 2123 Ringwood Avenue San Jose, CA 95131 ◆ Tel:(408) 434-0678 ◆ Fax:(408) 434-0688 ◆ http://www.ictpld.com

United Microelectronics Corporation

No. 10, Innovation Rd. I, Science-Based Industrial Park, Hsin-Chu City, Taiwan, R.O.C. 🔶 Tel: 886-3578-2258 🔶 Fax: 886-3578-0472 🔶 http://www.umc.com.tw

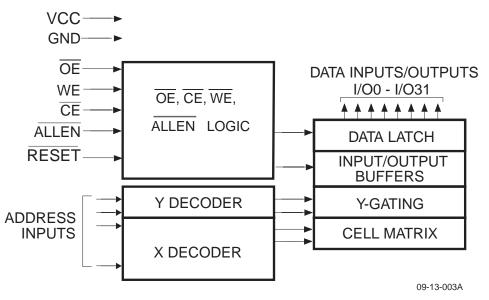

### BLOCK DIAGRAM

### **Device Operation**

**READ:** The EEPROM is accessed like a Static RAM. When  $\overline{CE}$  and  $\overline{OE}$  are low and  $\overline{WE}$  is high, the data stored at the memory location determined by the address pins is asserted on the <u>outputs</u>. The outputs are put in a high impedance state whenever  $\overline{CE}$  or  $\overline{OE}$  is high. This dual line control gives designers increased flexibility in preventing bus contention.

**BYTE WRITE:** Writing data into the EEPROM is similar to writing into a Static RAM. A low pulse on the WE or CE input with ALLEN and OE high and CE or WE low (respectively) initiates a byte write. The address location is latched on the last falling edge of WE (or CE); the new data is latched on the first rising edge. Internally, the device performs a self-clear before write. Once a byte write has been started, it will automatically time itself to completion.

**READY/BUSY:** READY/BUSY output can be used to detect the end of a write cycle. RDY/BUSY is actively pulled low during the write cycle and is released at the completion of the write.

**WRITE PROTECTION:** Inadvertent writes to the device are protected against by holding any one of  $\overrightarrow{CE}$  high,  $\overrightarrow{RESET}$  low or  $\overrightarrow{WE}$  high inhibits byte write cycles.

See the operating modes table for NORMAL, ERASE ALL, WRITE ALL operation.

Write ALL: Writing data into the EEPROM is similar to writing into a Static RAM. A low pulse on the WE or CE input with ALLEN low and OE high and CE or WE low (respectively) initiates a WRITE ALL. Internally, the device performs a selfclear before write. Once a WRITE ALL has been started, it will automatically time itself to completion.

## DC and AC Operating Range

| EEPROM             |            |              |  |  |

|--------------------|------------|--------------|--|--|

| Operating          | Commercial | 0°C - 70°C   |  |  |

| Temperature (Case) | Industrial | -40°C - 85°C |  |  |

| Supply Voltage     |            | 3.3V ± 10%   |  |  |

## **Operating Modes**

| MODE                  | CE              | ŌĒ               | WE              | I/O              | ALLEN           | RESET           |

|-----------------------|-----------------|------------------|-----------------|------------------|-----------------|-----------------|

| Read                  | V <sub>IL</sub> | V <sub>IL</sub>  | V <sub>IH</sub> | D <sub>OUT</sub> | Х               | V <sub>IH</sub> |

| Write <sup>(2)</sup>  | V <sub>IL</sub> | V <sub>IH</sub>  | V <sub>IL</sub> | D <sub>IN</sub>  | V <sub>IH</sub> | V <sub>IH</sub> |

| Standby/Write Inhibit | V <sub>IH</sub> | X <sup>(1)</sup> | Х               | High Z           | Х               | V <sub>IH</sub> |

| Write Inhibit         | Х               | Х                | V <sub>IH</sub> |                  | Х               | Х               |

| Write Inhibit         | Х               | Х                | Х               |                  | Х               | V <sub>IL</sub> |

| Output Disable        | Х               | V <sub>IH</sub>  | Х               | High Z           | Х               | V <sub>IH</sub> |

| WRAL                  | V <sub>IL</sub> | V <sub>IH</sub>  | V <sub>IL</sub> | High Z           | V <sub>IL</sub> | V <sub>IH</sub> |

Notes:

1. X can be  $V_{\text{IL}}$  or  $V_{\text{IH.}}$

2. Refer to AC Programming Waveforms.

## **DC Characteristics**

| Symbol           | Parameter                            | Condition                                                                         |      | Min | Мах | Units |

|------------------|--------------------------------------|-----------------------------------------------------------------------------------|------|-----|-----|-------|

| ILI              | Input Load Current                   | $V_{IN} = 0V$ to $V_{CC} + 1V$                                                    |      |     | 10  | μA    |

| I <sub>LO</sub>  | Output Leakage Current               | $V_{I/O} = 0V$ to $V_{CC}$                                                        |      |     | 10  | μΑ    |

| I <sub>SB1</sub> | V <sub>CC</sub> Standby Current CMOS | $\overline{\text{CE}}$ = V <sub>CC</sub> - 0.3V to V <sub>CC</sub> + 1.0V         |      |     | 10  | μΑ    |

|                  |                                      | _                                                                                 | Com. |     | 2   | mA    |

| I <sub>SB2</sub> | V <sub>CC</sub> Standby Current TTL  | $CE = 2.0V$ to $V_{CC} + 1.0V$                                                    | Ind. |     | 3   | mA    |

| I <sub>CC</sub>  | V <sub>CC</sub> Active Current AC    | $\frac{f = 5 \text{ MH}_{Z}; \text{ I}_{OUT} = 0 \text{ mA}}{CE} = \text{V}_{IL}$ | Com. |     | 5   | mA    |

|                  |                                      |                                                                                   | Ind. |     | 5   | mA    |

| V <sub>IL</sub>  | Input Low Voltage                    |                                                                                   |      |     | 0.6 | V     |

| V <sub>IH</sub>  | Input High Voltage                   |                                                                                   |      | 2.0 |     | V     |

| V <sub>OL</sub>  | Output Low Voltage                   | I <sub>OL</sub> =600μA                                                            |      |     | 0.4 | V     |

| V <sub>OH</sub>  | Output High Voltage                  | I <sub>OH</sub> = -600μA                                                          |      | 2.0 |     | V     |

### **AC Read Characteristics**

|                                   |                                                              | EEP | EEPROM |       |

|-----------------------------------|--------------------------------------------------------------|-----|--------|-------|

| Symbol                            | Parameter                                                    | Min | Max    | Units |

| T <sub>ACC</sub>                  | Address to Output Delay                                      |     | 100    | ns    |

| T <sub>CE</sub> <sup>(1)</sup>    | CE to Output Delay                                           |     | 100    | ns    |

| T <sub>OE</sub> <sup>(2)</sup>    | OE to Output Delay                                           | 10  | 70     | ns    |

| T <sub>DF</sub> <sup>(3)(4)</sup> | CE or OE High to Output Float                                | 0   | 50     | ns    |

| Т <sub>ОН</sub>                   | Output Hold from OE, CE or Address, whichever occurred first | 0   |        | ns    |

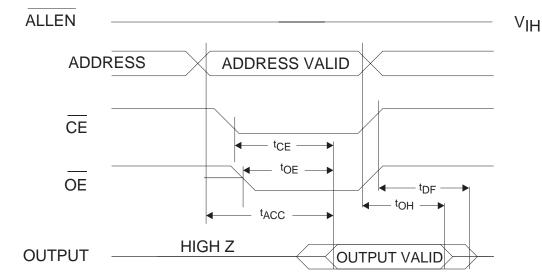

## AC Read Waveforms (1)(2)(3)(4)

- Notes: 1.  $\overline{CE}$  may be delayed up to  $t_{ACC}$   $t_{CE}$  after the address transition without impact on  $t_{ACC}$ .

- 2.  $\overline{OE}$  may be delayed up to  $t_{CE} t_{OE}$  after the falling edge of  $\overline{CE}$  without impact on  $t_{CE}$  or by  $t_{ACC} t_{OE}$  after an address change without impact on  $t_{ACC}$ .

- 3.  $t_{DF}$  is specified from  $\overline{OE}$  or  $\overline{CE}$  whichever occurs first (C<sub>L</sub> = 5 pF).

- 4. This parameter is characterized and is not 100% tested.

09-13-004A

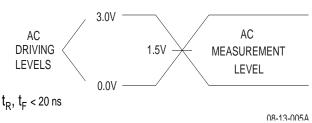

# Input Test Waveforms and Measurement Level

4

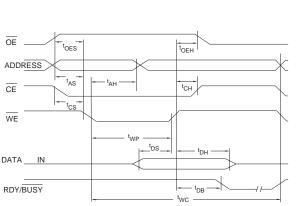

### **AC Write Characteristics**

| Symbol                             | Parameter                                                                                      | Min | Туре | Max  | Units |

|------------------------------------|------------------------------------------------------------------------------------------------|-----|------|------|-------|

| t <sub>AS</sub> , t <sub>OES</sub> | Address, OE Set-up Time                                                                        | 10  |      |      | ns    |

| t <sub>AH</sub>                    | Address Hold Time                                                                              | 50  |      |      | ns    |

| t <sub>WP</sub>                    | Write Pulse Width (WE or CE)                                                                   | 100 |      | 1000 | ns    |

| t <sub>DS</sub>                    | Data Set-up Time                                                                               | 50  |      |      | ns    |

| t <sub>DH</sub> , T <sub>OEH</sub> | Data, OE Hold Time                                                                             | 10  |      |      | ns    |

| t <sub>CS</sub> , t <sub>CH</sub>  | $\overline{CE}$ to $\overline{WE}$ and $\overline{WE}$ to $\overline{CE}$ Set-up and Hold Time | 0   |      |      | ns    |

| t <sub>DB</sub>                    | Time to Device Busy                                                                            |     |      | 50   | ns    |

| t <sub>WC</sub>                    | Write Cycle Time                                                                               |     | 0.5  | 1.0  | ms    |

| T <sub>WCALL</sub>                 | Write All Cycle Time                                                                           |     | 5    | 10   | ms    |

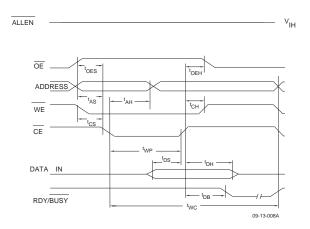

### AC Write Waveforms

WE Controlled

ALLEN

- V<sub>IH</sub>

#### $\overline{\text{CE}}$ Controlled

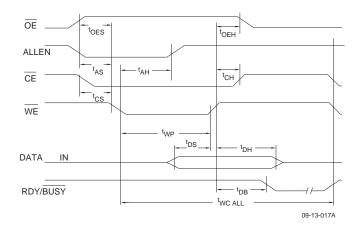

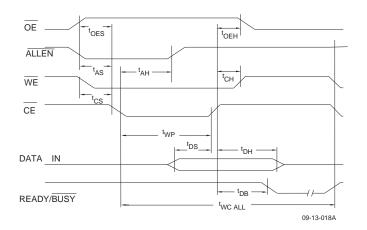

# Write All Waveforms

WE Controlled

CE Controlled

### Integrated Circuit Technology Corp.

2123 Ringwood Avenue San Jose, CA 95131

Tel:(408) 434-0678 Fax:(408) 434-0688 http://www.ictpld.com

# United Microelectronics Corporation UMC Group

No. 10, Innovation Rd. I, Science-Based Industrial Park, Hsin-Chu City, Taiwan, R.O.C.

Tel: 886-3578-2258 Fax: 886-3578-0472 http://www.umc.com.tw