### **Features**

- Very Low Power Design (≈ 50 mW)

- Single IF Concept

- 2-bit ADC on Chip

- Small QFN Package (28 Pins)

- . Highly Integrated, Few External Components

- UHF6 Technology

Electrostatic sensitive device.

Observe precautions for handling.

### **Description**

With the growing importance of mobile communication, location awareness is a key feature for more and more products and services. Due to its small size and minimal power consumption, the GPS front-end IC ATR0600 is an ideal solution for mobile applications and navigation systems.

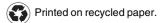

Figure 1. Block Diagram

# **GPS**Front-end IC

### **ATR0600**

### **Preliminary**

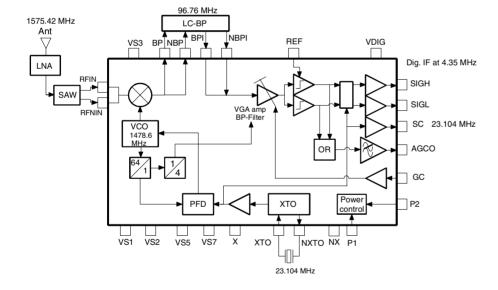

### **Pin Configuration**

Figure 2. Pinning QFN28

### **Pin Description**

| Pin | Symbol | Type | Function                                                                       | Protection Level |  |  |

|-----|--------|------|--------------------------------------------------------------------------------|------------------|--|--|

| 1   | AGCO   | 0    | Signal level output                                                            | ESD3             |  |  |

| 2   | NX     | OB   | Complementary to X                                                             | ESD3             |  |  |

| 3   | VS7    | Р    | ECL - blocks supply                                                            | ESD2             |  |  |

| 4   | NXTO   | IB   | Complementary to XTO                                                           | ESD3             |  |  |

| 5   | XTO    | IB   | Quartz input                                                                   | ESD3             |  |  |

| 6   | VS5    | Р    | XTO supply                                                                     | ESD2             |  |  |

| 7   | Х      | OB   | Quartz intermediate output                                                     | ESD3             |  |  |

| 8   | n.c.   | -    | Not connected                                                                  | _                |  |  |

| 9   | P2     | I    | Power-up quartz oscillator                                                     | ESD3             |  |  |

| 10  | P1     | Ĺ    | Power-up RF part                                                               | ESD3             |  |  |

| 11  | VS3    | Р    | Reference supply                                                               | ESD2             |  |  |

| 12  | RFIN   | IB   | RF input 1.575 GHz                                                             | ESD3             |  |  |

| 13  | RFNIN  | IB   | Complementary to RFIN                                                          | ESD3             |  |  |

| 14  | n.c.   | -    | Not connected                                                                  | -                |  |  |

| 15  | BP     | IB   | Open-collector output of mixer                                                 | ESD3             |  |  |

| 16  | NBP    | IB   | Complementary to BP                                                            | ESD3             |  |  |

| 17  | BPI    | IB   | IF - filter input                                                              | ESD3             |  |  |

| 18  | NBPI   | IB   | Complementary to BPI                                                           | ESD3             |  |  |

| 19  | VS1    | Р    | VCO + mixer + VGA supply                                                       | ESD2             |  |  |

| 20  | n.c.   | -    | Not connected                                                                  | -                |  |  |

| 21  | n.c.   | -    | Not connected                                                                  | -                |  |  |

| 22  | GC     | I    | Gain control input                                                             | ESD3             |  |  |

| 23  | VS2    | Р    | Subsampling unit supply                                                        | ESD2             |  |  |

| 24  | REF    | 0    | Defining low threshold voltage                                                 | ESD3             |  |  |

| 25  | SIGL   | 0    | Digital interface subsampled output high threshold voltage refered to REF1     | ESD3             |  |  |

| 26  | SIGH   | 0    | Digital interface subsampled output low threshold voltage refered to REF2 ESD3 |                  |  |  |

| 27  | VDIG   | Р    | Digital interface supply voltage 1.8 V                                         | ESD2             |  |  |

| 28  | SC     | 0    | Digital interface clock output ESD3                                            |                  |  |  |

# Functional Description

The specification of GPS receivers for personal mobile applications strongly differs from stand-alone GPS receiver specifications. One reason is the presence of strong blocking signals from mobile transmitters which might cause unacceptable levels of degradation in the carrier-to-noise ratio of a GPS system if not sufficiently suppressed. The other reason is the requirements for very low power consumption.

The ATR0600 GPS receiver IC has been especially designed for GPS applications in mobile phones. From this system point of view, it incorporates highest isolation between GPS and cellular antennas, as well as low power consumption. The ATR0600 contains a low-power single IF design and integrates a complete frequency synthesizer. It is fully functional over a supply-voltage range of 2.7 V to 3.3 V and is housed in a 28-pin QLN package.

The GPS receiver's input signal is a Direct Sequence Spread Spectrum (DSSS) signal at 1575.42 MHz with a 1.023 Mbps Bi-Phase-Shift-Keying (BPSK) modulated spreading code. As the input signal power at the antenna is approximately -140 dBm, the desired signal is below the thermal noise floor.

### **LNA/Mixer Stage**

The ATR0600 receives the L1 GPS signal via an external LNA. The LNA bandwidth should be as narrow as possible to avoid interferences from out-of-band signals (especially from those of the 1800 GSM band).

Combined with the antenna the LNA provides a first filtering of the GPS signal. The LNA in addition should have a power shutdown feature. The shutdown signal will be generated inside the digital section of the GPS receiver. The output of the LNA drives an external SAW filter, which provides the image rejection for the mixer and the isolation of the 1800-MHz GSM band. The output of the SAW filter drives a highly linear mixer which down-converts the GPS signal to an IF of 97.76 MHz.

### **IF Stage**

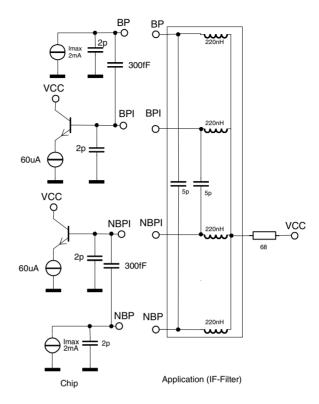

The mixer directly drives an external LC-bandpath filter. In order to provide the ultimate selectivity of the GPS frequency before the A/D conversion of the receiver part, the signal path of the ATR0600 combines an external filter and a second integrated filter. We recommend to design the external filter as a 2-pole filter with quality factor Q > 25.

### **VGA Amplifier Stage**

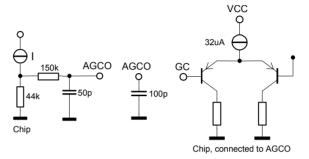

The output of the LC-filter drives an on-chip Variable Gain-Controlled amplifier (VGA) which is combined with an integrated IF-bandpath filter to perform additional filtering of GSM jamming signals. The AGC stage provides the additional gain needed to optimally load the signal range of the following analog/digital converter. The AGC control loop can be selected either on-chip close loop or open loop mode. Connecting the AGC\_OUT output directly to the AGC\_CNTRL input activates the internal control loop.

In that case, the VGA control signal is passed to the VGA via an integrated buffer stage including all necessary filtering (low-pass filter). The external control loop is closed by the baseband IC ATR0620.

#### A/D Converter Stage

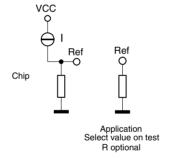

The output of the VGA drives the integrated 1.5-bit analog-to-digital converter stage, which comprises two comparators and two output drivers in order to provide sign and magnitude output bits to the baseband IC ATR0620. The comparator LOW- and HIGH-thresholds (in Figure 1 on page 1 for SIGH and SIGL) are adjustable via external resistor. The OR gate closes the internal AGC control loop.

## Power Save Setting Stage

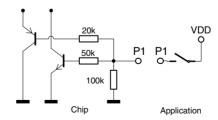

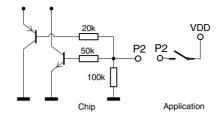

The integrated power-control stage is controlled by the baseband IC ATR0620 via P1 and P2. The input signals control the shutdown of the reference crystal oscillator (P2) or the shutdown of the whole RF section (P1).

### **Absolute Maximum Ratings**

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Parameters                | Symbol           | Value       | Unit |  |

|---------------------------|------------------|-------------|------|--|

| Supply voltage            | V <sub>S</sub>   | 3.7         | V    |  |

| Input voltage             | V <sub>in</sub>  | 3.7         | V    |  |

| Junction temperature      | T <sub>j</sub>   | 125         | °C   |  |

| Storage temperature range | T <sub>stg</sub> | -40 to +125 | °C   |  |

### **Thermal Resistance**

| Parameters       | Symbol     | Value | Unit |

|------------------|------------|-------|------|

| Junction ambient | $R_{thJA}$ | 125   | K/W  |

### **Recommended Operating Conditions**

| Parameters                                   | Symbol                 | Value       | Unit |

|----------------------------------------------|------------------------|-------------|------|

| Supply voltage                               | V <sub>S</sub>         | 2.7 to 3.3  | V    |

| Temperature range                            | Temp                   | -40 to +85  | °C   |

| Input frequency                              | f <sub>in, mixer</sub> | 1575.42     | MHz  |

| Reference frequency                          | f <sub>ref</sub>       | 23.104      | MHz  |

| External IF filter (see Figure 13 on page 9) |                        |             |      |

| Supply voltage digital interface, pin 27     | V <sub>DD</sub>        | 1.65 to 2.0 | V    |

### **Electrical Characteristics**

| No. | Parameters                       | Test Conditions                                               | Pin                           | Symbol             | Min. | Тур. | Max. | Unit | Type* |

|-----|----------------------------------|---------------------------------------------------------------|-------------------------------|--------------------|------|------|------|------|-------|

| 1   | Common                           |                                                               |                               |                    |      |      |      |      |       |

| 1.1 | Supply current                   | P1 = P2 = VPU <sub>on</sub>                                   | 3, 6,<br>11,<br>19, 23        | I <sub>S</sub>     |      | 18   |      | mA   | Α     |

| 1.2 | Supply current XTO               | P1 = VPU <sub>off</sub><br>P2 = VPU <sub>on</sub>             | 6                             | I <sub>XTO</sub>   |      | 2    |      | mA   | А     |

| 1.3 | Supply current digital interface | P1 = P2 = VPU <sub>on</sub>                                   | 27                            | I <sub>DD</sub>    |      | 250  |      | μΑ   | А     |

| 1.4 | Supply current (power down)      | P1 = P2 = VPUoff                                              | 3, 6,<br>11,<br>19,<br>23, 27 | I <sub>S, pd</sub> |      |      | 20   | μΑ   | A     |

| 1.5 | Total gain                       | RFIN, RNIN matched, to 50 $\Omega$ , $V_{GC} = 2.2 \text{ V}$ | 1                             | G                  |      | 95   |      | dB   | В     |

| 1.6 | Noise figure                     |                                                               |                               | N <sub>F</sub>     |      |      | 6.9  | dB   | С     |

<sup>\*)</sup> Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

### **Electrical Characteristics (Continued)**

| No. | Parameters                            | Test Conditions                                    | Pin    | Symbol                                         | Min. | Тур.                     | Max. | Unit         | Type*  |

|-----|---------------------------------------|----------------------------------------------------|--------|------------------------------------------------|------|--------------------------|------|--------------|--------|

| 2   | Mixer and 1st IF-filter               |                                                    | *      |                                                |      | •                        |      | *            |        |

| 2.1 | Output frequency                      | f <sub>ref</sub> = 23.104 MHz                      | 15, 16 | f <sub>IF</sub>                                |      | 96.76                    |      | MHz          | В      |

| 2.2 | Input impedance                       | f <sub>ref</sub> = 1575 MHz                        | 12, 13 | Z <sub>in, IF</sub>                            |      | 13 - j80                 |      | Ω            | С      |

| 3   | VGA and 2 <sup>nd</sup> IF-filter     |                                                    |        |                                                |      |                          |      |              |        |

| 3.1 | Bandpass center frequency             | f <sub>ref</sub> = 23.104 MHz                      |        | f <sub>in, VGA</sub>                           |      | 96.76                    |      | MHz          |        |

| 3.2 | Minimum gain                          | V <sub>GC</sub> = 1.0 V                            |        | G <sub>VGA, min</sub>                          |      | 0                        |      | dB           | D      |

| 3.3 | Maximum gain                          | V <sub>GC</sub> = 2.2 V                            |        | G <sub>VGA, max</sub>                          |      | 75                       |      | dB           | D      |

| 3.4 | Control-voltage sensitivity           | V <sub>GC</sub> = 2.2 V<br>V <sub>GC</sub> = 1.0 V |        | N <sub>vga, min</sub><br>N <sub>vga, max</sub> |      | 6.6<br>150               |      | dB/V<br>dB/V | D<br>D |

| 3.5 | Gain-control output cut-off frequency | Without external load                              |        | F <sub>agc_out</sub>                           |      | 100                      |      | kHz          | D      |

| 3.6 | Gain-control output voltage           | at 50 pF load                                      | 1      | V <sub>agc_out</sub>                           | 1.0  |                          | 2.2  | V            | В      |

| 4   | Reference Oscillator                  |                                                    |        |                                                |      |                          | 11   | "            |        |

| 4.1 | XTO phase noise at 100 Hz             |                                                    | 28     | P <sub>n100</sub>                              |      | -80                      |      | dBc/Hz       | С      |

| 4.2 | XTO phase noise at 1 kHz              |                                                    | 28     | P <sub>n1k</sub>                               |      | -100                     |      | dBc/Hz       | С      |

| 5   | Clock and Data Drive                  | r                                                  |        |                                                |      |                          |      |              |        |

| 5.1 | Clock driver frequency                |                                                    | 28     | f <sub>clk</sub>                               |      | 23.104                   |      | MHz          | Α      |

| 5.2 | Clock output level                    | C <sub>load</sub> = 10 pF                          | 28     | V <sub>clkhigh</sub>                           |      | 0.8 ×<br>V <sub>DD</sub> |      | V            | B, C   |

| 5.3 | Clock output level                    | C <sub>load</sub> = 10 pF                          | 28     | V <sub>clklow</sub>                            |      | 0.2 ×<br>V <sub>DD</sub> |      | V            | С      |

| 5.4 | Data output level                     | C <sub>load</sub> = 10 pF                          | 25, 26 | V <sub>datahigh</sub>                          |      | $0.8 \times V_{DD}$      |      | V            | С      |

| 5.5 | Data output level                     | C <sub>load</sub> = 10 pF                          | 25, 26 | V <sub>datalow</sub>                           |      | 0.2 ×<br>V <sub>DD</sub> |      | V            | С      |

| 6   | Power-up, Pins P1 and                 | P2                                                 |        |                                                |      |                          |      | ,            |        |

| 6.1 | Power-on voltage level on             |                                                    | 9, 10  | VPU <sub>on</sub>                              | 0.9  |                          |      | V            | С      |

| 6.2 | Power-on voltage level off            |                                                    | 9, 10  | VPU <sub>off</sub>                             |      |                          | 0.3  | V            | С      |

| 6.3 | Power-on delay time                   |                                                    | 9, 10  | TPU <sub>on, off</sub>                         |      |                          | 6    | μs           | С      |

|     | - 0                                   | 1                                                  |        |                                                |      | 1                        |      | 1            |        |

<sup>\*)</sup> Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

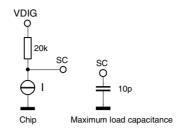

### Interface Description Figure 3. Clock Interface

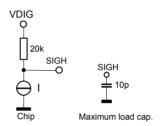

Figure 4. SIGH Interface

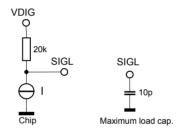

Figure 5. SIGL Interface

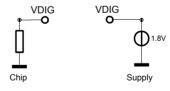

Figure 6. Supply VDIGI Interface

Figure 7. Power Control Interface P1

Figure 8. Power Control Interface P2

Figure 9. Automatic Gain-control Interface

Figure 10. A/D Reference Level-control Interface Ref

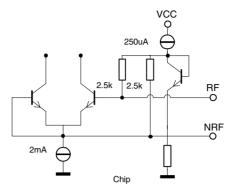

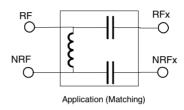

Figure 11. Mixer Input Interface

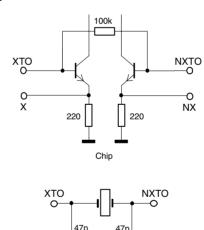

Figure 12. XTO Interface

68p

NX

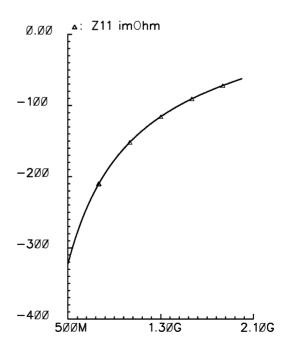

Figure 13. IF-filter Interface

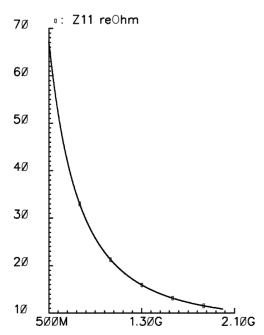

Figure 14. Mixer Input Impedance at RF-NRF

S-Parameter Response

### **Ordering Information**

| Extended Type Number | Package     | Remarks          |  |  |

|----------------------|-------------|------------------|--|--|

| ATR0600-PJQ          | QFN28 - 5x5 | Taped and reeled |  |  |

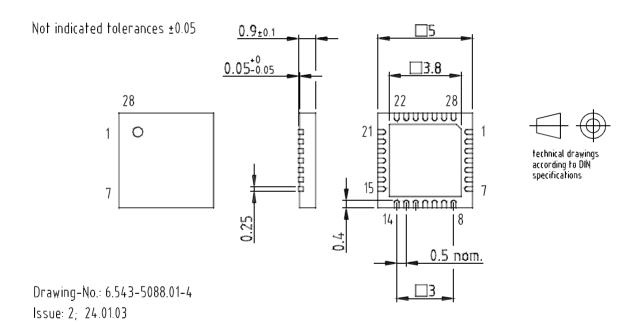

### **Package Information**

Package: QFN 28 – 5x5 Exposed pad 3.8x3.8

(acc. JEDEC OUTLINE No. MO-220)

Dimensions in mm

#### **Atmel Corporation**

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

### **Regional Headquarters**

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland

Tel: (41) 26-426-5555 Fax: (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong

Tel: (852) 2721-9778 Fax: (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan

Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Atmel Operations**

#### Memoru

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

#### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18

Fax: (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00 Fax: (33) 4-42-53-60-01

1150 East Chevenne Mtn. Blvd. Colorado Springs, CO 80906, USA

Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland

Tel: (44) 1355-803-000 Fax: (44) 1355-242-743

#### RF/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany Tel: (49) 71-31-67-0 Fax: (49) 71-31-67-2340

1150 East Chevenne Mtn. Blvd. Colorado Springs, CO 80906, USA

Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Biometrics/Imaging/Hi-Rel MPU/ High Speed Converters/RF Datacom

Avenue de Rochepleine **BP 123**

38521 Saint-Egreve Cedex, France

Tel: (33) 4-76-58-30-00 Fax: (33) 4-76-58-34-80

Literature Requests www.atmel.com/literature

Disclaimer: Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

### © Atmel Corporation 2003. All rights reserved.

Atmel® and combinations thereof are the registered trademarks of Atmel Corporation or its subsidiaries.

Other terms and product names may be the trademarks of others.