# VFP10<sup>™</sup> Vector Floating-point Coprocessor

**Technical Reference Manual**

Copyright © 2001 ARM Limited. All rights reserved. ARM DDI 0178B

# VFP10<sup>™</sup> Vector Floating-point Coprocessor Technical Reference Manual

Copyright © 2001 ARM Limited. All rights reserved.

#### **Release Information**

Change history

| Date         | Issue | Change                                                                     |

|--------------|-------|----------------------------------------------------------------------------|

| 22 May, 2001 | А     | First release                                                              |

| 24 May, 2001 | В     | Second release, addition of FPINST and FPINST2 <reg> field addresses</reg> |

#### **Proprietary Notice**

Words and logos marked with  ${}^{\otimes}$  or  ${}^{\sim}$  are registered trademarks or trademarks owned by ARM Limited, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM Limited shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

#### **Confidentiality Status**

This document is Open Access. This document has no restriction on distribution.

#### **Product Status**

The information in this document is final (information on a developed product).

#### Web Address

http://www.arm.com

# Contents VFP10 Vector Floating-point Coprocessor Technical Reference Manual

|           | Prefa | ace                                                  |      |

|-----------|-------|------------------------------------------------------|------|

|           |       | About this document                                  |      |

|           |       | Further reading                                      | xii  |

|           |       | Feedback                                             |      |

| Chapter 1 | Intro | duction                                              |      |

|           | 1.1   | About the VFP10 coprocessor                          | 1-2  |

|           | 1.2   | Coprocessor interface                                | 1-4  |

|           | 1.3   | The VFP10 coprocessor pipeline                       | 1-5  |

|           | 1.4   | Modes of operation                                   |      |

|           | 1.5   | Short vector instructions                            | 1-15 |

|           | 1.6   | Parallel execution of instructions                   | 1-16 |

|           | 1.7   | VFP10 coprocessor treatment of branch instructions . | 1-17 |

|           | 1.8   | Writing optimal VFP10 coprocessor code               |      |

|           | 1.9   | Clocking                                             |      |

|           | 1.10  | Testing                                              |      |

|           | 1.11  | Modifications from VFP10 coprocessor (Rev 0)         | 1-21 |

| Chapter 2 | VFP1  | 0 Register File                                      |      |

|           | 2.1   | About the register file                              |      |

|           | 2.2        | Register file internal formats                               | 2-3  |

|-----------|------------|--------------------------------------------------------------|------|

|           | 2.3        | Decoding the register file                                   |      |

|           | 2.4        | Loading operands from ARM registers                          |      |

|           | 2.5        | Maintaining consistency in register precisions               |      |

|           | 2.6        | Data transfer between memory and VFP10 coprocessor registers |      |

|           | 2.7        | Access to register banks in CDP operations                   |      |

| Chapter 3 | VFP1       | 0 Programmer's Model                                         |      |

| •         | 3.1        | About the programmer's model                                 | 3-2  |

|           | 3.2        | Compliance with IEEE-754                                     |      |

|           | 3.3        | ARM v5TE coprocessor extensions                              |      |

|           | 3.4        | Summary of VFP coprocessor system control registers          |      |

|           | 3.5        | FPSCR register                                               |      |

| Chapter 4 | Instr      | uction Execution in the VFP10 Coprocessor                    |      |

| -         | 4.1        | About instruction execution in the VFP10 coprocessor         | 4-2  |

|           | 4.2        | Serializing instructions                                     |      |

|           | 4.3        | Interrupting VFP10 coprocessor instructions                  | 4-5  |

|           | 4.4        | Forwarding                                                   | 4-6  |

|           | 4.5        | Hazard and resource stall conditions                         |      |

|           | 4.6        | Parallel execution of operations                             | 4-21 |

|           | 4.7        | Execution timing                                             | 4-23 |

| Chapter 5 | Exce       | ption Handling                                               |      |

|           | 5.1        | About exception processing                                   | 5-2  |

|           | 5.2        | Support code                                                 | 5-3  |

|           | 5.3        | Illegal instructions                                         | 5-6  |

|           | 5.4        | Determination of the trigger instruction                     | 5-7  |

|           | 5.5        | Input subnormal                                              | 5-12 |

|           | 5.6        | Invalid operation                                            | 5-13 |

|           | 5.7        | Division by zero                                             | 5-16 |

|           | 5.8        | Overflow                                                     | 5-17 |

|           | 5.9        | Underflow                                                    | 5-19 |

|           | 5.10       | Inexact result                                               | 5-21 |

|           | 5.11       | Input exceptions                                             | 5-22 |

|           | 5.12       | Arithmetic exceptions                                        | 5-23 |

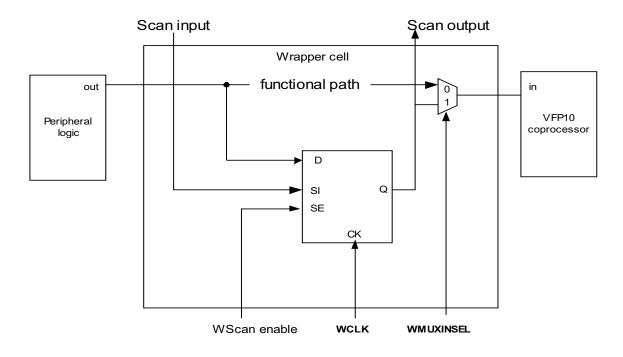

| Chapter 6 | Desi       | gn for Test                                                  |      |

| -         | 6.1        | About DFT                                                    | 6-2  |

|           | 6.2        | VFP10 DFT                                                    | 6-3  |

|           | 6.3        | VFP10 Core                                                   | 6-4  |

|           | ~ 4        | VFP10 test wrapper                                           | 6-6  |

|           | 6.4        |                                                              |      |

|           | 6.4<br>6.5 | VFP10 clocking                                               |      |

|           | -          |                                                              | 6-10 |

# Glossary

# List of Tables VFP10 Vector Floating-point Coprocessor Technical Reference Manual

|            | Change history                                                            |        |

|------------|---------------------------------------------------------------------------|--------|

| Table 2-1  | MCR transfers                                                             | 2-7    |

| Table 2-2  | MRC transfers                                                             | 2-7    |

| Table 2-3  | MCRR transfers                                                            | 2-8    |

| Table 2-4  | MRRC transfers                                                            | 2-8    |

| Table 2-5  | Single-precision data memory images and byte addresses                    | . 2-10 |

| Table 2-6  | Double-precision data memory images and byte addresses                    | . 2-11 |

| Table 2-7  | Register bank description                                                 | . 2-12 |

| Table 2-8  | Single-precision three-operand register usage                             | . 2-15 |

| Table 2-9  | Single-precision two-operand register usage                               | . 2-16 |

| Table 2-10 | Double-precision three-operand register usage                             | . 2-16 |

| Table 2-11 | Double-precision two-operand register usage                               | . 2-16 |

| Table 3-1  | Default NaN values                                                        | 3-6    |

| Table 3-2  | Access to control registers                                               | . 3-17 |

| Table 3-3  | FPEXC bit field descriptions                                              |        |

| Table 3-4  | Vector iteration count bit values                                         |        |

| Table 3-5  | FPSID bit fields                                                          |        |

| Table 3-6  | Vector length/stride combinations                                         | . 3-25 |

| Table 3-7  | Exception status and control bits                                         | . 3-26 |

| Table 4-1  | Single-precision source register locking and clearing in non-RunFast mode | . 4-12 |

| Table 4-2  | Double-precision source register locking and clearing in non-RunFast mode | . 4-12 |

| Table 4-3  | Single-precision source register locking and clearing in RunFast mode   | 4-13  |

|------------|-------------------------------------------------------------------------|-------|

| Table 4-4  | Double-precision source register locking and clearing in RunFast mode   | 4-13  |

| Table 4-5  | Instruction cycles for example 1                                        | 4-14  |

| Table 4-6  | Instruction cycles for example 2                                        | 4-15  |

| Table 4-7  | Instruction cycles for short vector MULS example                        | 4-16  |

| Table 4-8  | Instruction cycles for short vector FMULS example                       | 4-16  |

| Table 4-9  | Instruction cycles for example in Run Fast mode                         | 4-17  |

| Table 4-10 | Instruction cycles for vector MULS example                              | 4-18  |

| Table 4-11 | Instruction cycles for example 2                                        |       |

| Table 4-12 | Pipeline stages for load multiple, vector MULS, scalar FADDS            | 4-20  |

| Table 4-13 | Parallel execution in three pipelines                                   |       |

| Table 4-14 | Throughput and latency cycle timings for VFP10 CDP operations           | 4-23  |

| Table 5-1  | Possible IEEE 754 invalid operation exceptions                          | 5-13  |

| Table 5-2  | Default results for positive invalid inputs                             | 5-15  |

| Table 5-3  | Overflow result                                                         | 5-18  |

| Table 5-4  | LSA and USA determination                                               | 5-23  |

| Table 5-5  | USA and LSA values and conditions                                       | 5-24  |

| Table 5-6  | FMUL family bounce and exceptional thresholds                           | 5-26  |

| Table 5-7  | FDIV bounce and exceptional thresholds                                  | 5-27  |

| Table 5-8  | FCVTSD bounce conditions                                                | 5-28  |

| Table 5-9  | SP Float-to-integer bounce thresholds and stored results                | 5-30  |

| Table 5-10 | DP Float-to-integer bounce thresholds and stored results                | 5-32  |

| Table 6-1  | Scan chain configuration                                                | . 6-4 |

| Table 6-2  | Internal scan chain configuration                                       | . 6-5 |

| Table 6-3  | Wrapper cell control and observation configurations                     | . 6-9 |

| Table 6-4  | VFP10 macrocell test ports                                              | 6-11  |

| Table 6-5  | VFP10 test signals during core scan test                                | 6-12  |

| Table 6-6  | VFP10 coprocessor test signals in functional mode                       | 6-13  |

| Table 6-7  | VFP10 test pins in VFP10 coprocessor external test wrapper mode         | 6-13  |

| Table G-8  | Register banks in single-precision and double-precision registers Gloss | ary-4 |

# List of Figures VFP10 Vector Floating-point Coprocessor Technical Reference Manual

| Figure 1-1 | FMAC pipeline                               |      |

|------------|---------------------------------------------|------|

| Figure 1-2 | Divide and square root pipeline             | 1-8  |

| Figure 1-3 | Load/Store pipeline                         |      |

| Figure 2-1 | Integer format                              | 2-3  |

| Figure 2-2 | Single-precision data format                | 2-4  |

| Figure 2-3 | Register data formats                       | 2-4  |

| Figure 2-4 | Register file format                        | 2-6  |

| Figure 3-1 | FMDRR bit fields                            | 3-11 |

| Figure 3-2 | FMRRD bit fields                            | 3-12 |

| Figure 3-3 | FMSRR bit fields                            | 3-13 |

| Figure 3-4 | FMRRS bit fields                            | 3-15 |

| Figure 3-5 | FPEXC register format                       | 3-19 |

| Figure 3-6 | FPSID register format                       | 3-21 |

| Figure 3-7 | User status and control bit fields summary  | 3-23 |

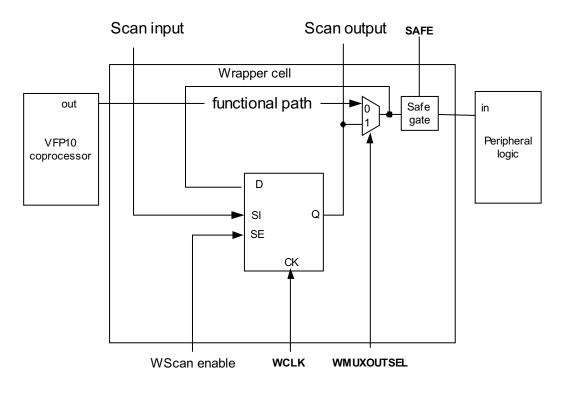

| Figure 6-1 | Dedicated input wrapper cell                | 6-6  |

| Figure 6-2 | Dedicated output wrapper cell               | 6-7  |

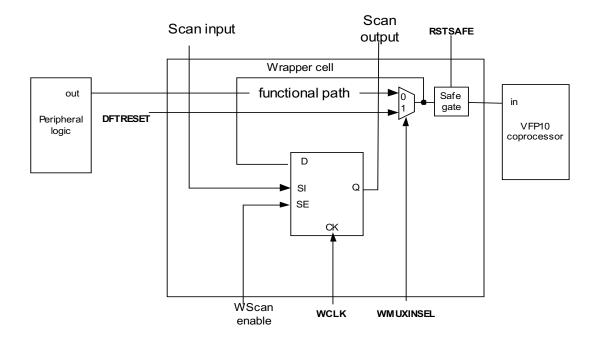

| Figure 6-3 | Reset dedicated wrapper cell                | 6-8  |

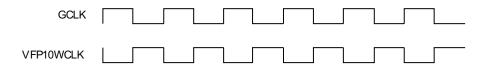

| Figure 6-4 | VFP10 production scan mode clocking         |      |

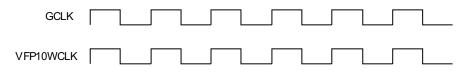

| Figure 6-5 | VFP10 serial core test clocking requirement | 6-10 |

List of Figures

# Preface

This preface introduces the VFP10<sup>TM</sup> (Rev1) Vector Floating-point Coprocessor and its reference documentation. It contains the following sections:

- About this document on page x

- Further reading on page xii

- *Feedback* on page xiii.

### About this document

This document is the technical reference manual for the VFP10 coprocessor (Rev1).

#### Intended audience

This document has been written for experienced hardware and software engineers who are familiar with the ARM10 Thumb Family architecture and are conversant with IEEE 754 and its conventions for dealing with floating-point arithmetic. We recommend reading the relevant sections of the *ARM Architecture Reference Manual* before reading this manual.

#### Using this manual

This document is organized into the following chapters:

#### Chapter 1 Introduction

Read this chapter for an overview of the VFP10 coprocessor pipelines, modes of operation and a summary of the differences between this revision and the previous revision.

#### Chapter 2 VFP10 Register File

Read this chapter for a description of the VFP10 coprocessor register file.

#### Chapter 3 VFP10 Programmer's Model

Read this chapter for details of the programmer's model and VFP10 coprocessor registers.

#### Chapter 4 Instruction Execution in the VFP10 Coprocessor

Read this chapter for details of instruction execution in VFP10 coprocessor.

#### Chapter 5 Exception Handling

Read this chapter for a description of VFP10 coprocessor exception handling.

#### Chapter 6 Design for Test

Read this chapter for a description of VFP10 coprocessor design for test features.

## **Typographical conventions**

The following typographical conventions are used in this book:

| bold               | Highlights interface elements, such as menu names and buttons. Also used for terms in descriptive lists, where appropriate.                    |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| italic             | Highlights important notes, introduces special terminology, denotes internal cross-references, and citations.                                  |

| typewriter         | Denotes text that can be entered at the keyboard, such as commands, file<br>and program names, and source code.                                |

| <u>type</u> writer | Denotes a permitted abbreviation for a command or option. The<br>underlined text can be entered instead of the full command or option<br>name. |

| typewriter italic  |                                                                                                                                                |

|                    | Denotes arguments to commands and functions where the argument is to                                                                           |

be replaced by a specific value.

#### typewriter bold

Denotes language keywords when used outside example code and ARM processor signal names.

# **Further reading**

This section lists publications by ARM Limited, and by third parties.

ARM periodically provides updates and corrections to its documentation. See http://www.arm.com for current errata sheets and addenda.

See also the ARM Frequently Asked Questions list at: http://www.arm.com/DevSupp/Sales+Support/faq

### **ARM** publications

This document contains information that is specific to the VFP10 Vector Floating-point Coprocessor (Rev 1). Refer to the following documents for other relevant information:

- ARM Architecture Reference Manual (ARM DUI 0100) Revision D or later

- *AFS Firmware Suite Version 1.3 Reference Guide* (ARM DUI 0102).

- ARM1020E Technical Reference Manual (ARM DDI 0177)

- ARM10200E Test Chip Implementation Guide (ARM DXI 0106).

### **Other publications**

This manual makes extensive use of the terminology and conventions of:

• ANSI/IEEE Std 754-1985, IEEE Standard for Binary Floating-point Arithmetic.

# Feedback

ARM Limited welcomes feedback both on the VFP10 Vector Floating-point Coprocessor (Rev1), and on the documentation.

### Feedback on the VFP10 Vector Floating-point Coprocessor (Rev1)

If you have any comments or suggestions about this product, please contact your supplier giving:

- the product name

- a concise explanation of your comments.

### Feedback on this document

If you have any comments about this document, please send email to errata@arm.com giving:

- the document title

- the document number

- the page number(s) to which your comments refer

- a concise explanation of your comments.

General suggestions for additions and improvements are also welcome.

Preface

# Chapter 1 Introduction

This chapter introduces the VFP10 Vector Floating-point Coprocessor. It contains the following sections:

- About the VFP10 coprocessor on page 1-2

- Coprocessor interface on page 1-4

- The VFP10 coprocessor pipeline on page 1-5

- *Modes of operation* on page 1-12

- Short vector instructions on page 1-15

- *Parallel execution of instructions* on page 1-16

- VFP10 coprocessor treatment of branch instructions on page 1-17

- Writing optimal VFP10 coprocessor code on page 1-18

- *Clocking* on page 1-19

- *Testing* on page 1-20

- *Modifications from VFP10 coprocessor (Rev 0)* on page 1-21.

# 1.1 About the VFP10 coprocessor

The ARM VFP10 Floating-point Coprocessor is the first implementation of the *Vector Floating-point Architecture* (VFPv2). It provides IEEE 754-compliant, low-cost floating-point computation for applications where high-performance graphics processing or signal processing capabilities are required.

The VFP10 coprocessor is optimized for:

- high data transfer bandwidth through 64-bit split load and store buses

- fast hardware execution of a high percentage of operations on normalized data resulting in higher overall performance while providing full IEEE 754 support when required

- parallel divide and square-root operations in parallel with other arithmetic operations to reduce the impact of long latency operations

- full IEEE 754 compatibility in RunFast mode without support code assistance, providing determinable run-time calculations for all input data

- low power consumption, small die size and reduced kernel code.

The VFP10 coprocessor is a high-performance, low-power ARM enhanced numeric coprocessor macrocell that provides high throughput IEEE 754-compatible operations. Designed to be incorporated with the ARM10 family of cores, the VFP10 coprocessor provides full support of single-precision and double-precision addition, subtraction, multiplication, division, and multiply with accumulate operations. Conversions between floating-point data formats and ARM integer word format are provided, with special operations to perform the conversion in *Round-To-Zero* (RZ) rounding for high-level language support.

The VFP10 coprocessor delivers high performance in general purpose applications, such as Java, and an excellent performance-power-area solution for embedded applications.

—— Note ———

This document is intended to be read in conjunction with the Vector Floating-point Architecture section of the *ARM Architecture Reference Manual*. Only VFP10-specific implementation issues are described in this book.

#### 1.1.1 Applications

The VFP10 coprocessor is built with full-scan for high coverage testability. Advanced power-saving support is incorporated to take advantage of the power-saving modes of the ARM1020E macrocell. The VFP10 coprocessor provides high-performance, low-cost floating-point computation particularly suitable for a wide spectrum of applications such as:

- personal digital assistants and smartphones for graphics, voice and user interfaces, Java interpretation, and *Just In Time* (JIT) compilation

- games machines for high-resolution three-dimensional graphics and digital audio

- printers and *Multi-Function Peripheral* (MFP) controllers for high-definition color rendering requiring high data memory bandwidth

- network controllers for high data bandwidth between network ports and for data compression

- set-top boxes for digital audio and digital video and three-dimensional user interfaces

- automotive applications for engine management and power train computations.

# 1.2 Coprocessor interface

The VFP10 coprocessor is designed to be integrated with an ARM10 family device through a general-purpose ARM1020E coprocessor interface. This interface is further defined in the *ARM1020E Technical Reference Manual*.

The VFP10 coprocessor uses coprocessor ID numbers 10 and 11, mainly for single-precision and double-precision operations, respectively. In some cases, such as mixed precision operations, the coprocessor ID represents the destination precision. In a system containing a VFP10 coprocessor, these coprocessor ID numbers must not be used by another coprocessor.

For the VFP10 coprocessor to operate at the maximum frequency specified, the coprocessor interface between the ARM1020E and the VFP10 coprocessor must be implemented with care to minimize the physical distance between the ARM1020E device and the VFP10 coprocessor, and to make the interconnect wires as short as possible. See the *ARM1020E Implementation Guide* for more information.

# 1.3 The VFP10 coprocessor pipeline

The VFP10 coprocessor comprises three separate pipelines:

- the multiply-accumulate pipeline (FMAC)

- the *Divide and square root* pipeline (DS).

- the *Load/Store* pipeline (LS)

These are each capable of operating independently of the other pipelines and in parallel with them. Each of the three pipelines share the first two pipeline stages, Issue and Decode. These two stages and the first cycle of the Execute stage of each pipeline remains in lockstep with the ARM pipeline stage but effectively one cycle behind the ARM pipeline. When the ARM is in the Decode stage for a particular VFP instruction, the VFP10 coprocessor is in the Issue stage for the same instruction. This lockstep mechanism maintains in-order issue between the ARM processor and the VFP10 coprocessor.

The three pipelines are capable of operating in parallel, enabling more than 1 instruction to be completed per cycle. Instructions issued to the FMAC pipeline can complete out of order with respect to load and store operations and divide or square root operations. This out-of-order completion might be visible to the user in the case of an exception generated by a short vector FMAC or DS operation, with a load or store operation initiated before the exception was detected. The destination registers or memory of the load or store operation will reflect the completion of a transfer while the destination registers of the exceptional FMAC or DS operation will retain their values before the operation was initiated. This is described in more detail in *Parallel execution of operations* on page 4-21.

The pipeline supports single-cycle throughput for all single-precision operations (excluding divide and square root) and most double-precision operations. Double-precision multiply and multiply-accumulate operations have a two-cycle throughput. The LS pipeline is capable of supplying two single-precision operands or one double-precision operand per cycle, balancing the data transfer capability with the operand requirements.

### 1.3.1 The FMAC pipeline

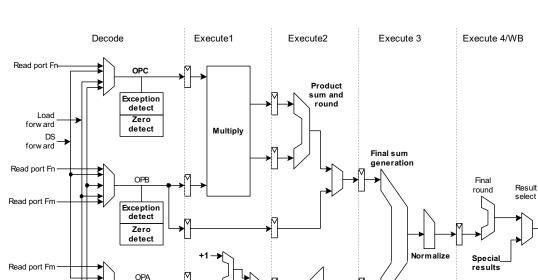

The FMAC pipeline is shown in Figure 1-1.

Figure 1-1 FMAC pipeline

FMAC Writeback

path

#### 1.3.2 FMAC pipeline execution

Read port Fd

To Register File

The FMAC pipeline executes the following instructions:

Exception detect

Zero

detect

- FSUB Subtraction.

- FMUL, FNMUL Multiply.

- FMAC, FNMAC, FMSC, FNMSC

Multiply-accumulate.

A operand

inversion and

negation

Align

- FABS Absolute value.

- FNEG Negation.

- FUITO, FTOUI Unsigned integer conversion.

- FSITO, FTOSI Signed integer conversion.

FTOUIZ, FTOSIZ

Floating-point to integer conversion with forced RZ rounding mode.

FCMP, FCMPE, FCMPZ, FCMPEZ

Comparison.

FCVTSD, FCVTDS

Format conversion.

FCPY Copy register.

See Execution timing on page 4-23 for cycle counts.

The FMAC family of instructions (FMAC, FNMAC, FMSC, and FNMSC) perform a chained multiply and accumulate operation. The product is computed, rounded to the specified rounding mode and destination precision, and checked for exceptions before the accumulate operation is performed. The accumulate operation is also rounded to the specified rounding mode and destination precision, and checked for exceptions. The final result is identical to the equivalent sequence of operations executed in sequence. Exception processing and status reporting also reflect the independence of the components of the chained operations.

As an example, the FMAC instruction performs a chained multiply-add operation with the following sequence of operations:

- 1. The product of the operands in the Fn and Fm registers are multiplied.

- 2. The product is rounded to the current rounding mode and destination precision and checked for exceptions.

- 3. The result is summed with the operand in the Fd register.

- 4. The sum is rounded to the current rounding mode and destination precision and checked for exceptions. If no exception conditions that require support code are present, the result is written to the Fd register.

For example, the instruction FMACS S0, S1, S2 returns the same result as: FMULS TEMP, S1, S2 FADDS S0, S1, TEMP

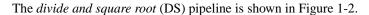

#### 1.3.3 Divide and square root pipeline

#### Figure 1-2 Divide and square root pipeline

The divide and square root pipeline executes the following instructions:

| FDIV  | Division |

|-------|----------|

| FCODT | C        |

FSQRT Square root

The VFP10 coprocessor executes divide and square root functions for both single-precision and double-precision operands with all IEEE 754 rounding modes supported. The DS unit uses a shared radix-4 algorithm that provides a good balance between speed and chip area. The DS operations have a latency of 17 cycles for single-precision operations and 31 cycles for double-precision operations. The throughput is 14 cycles for single-precision operations and 28 cycles for double-precision operations.

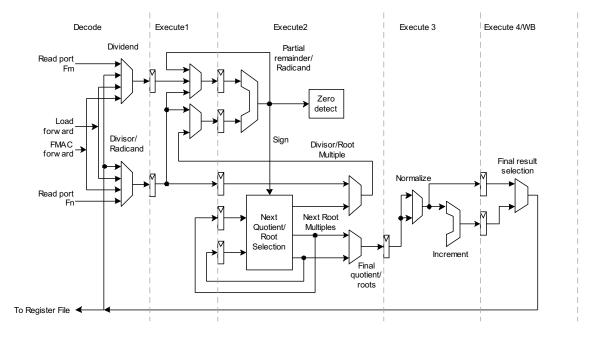

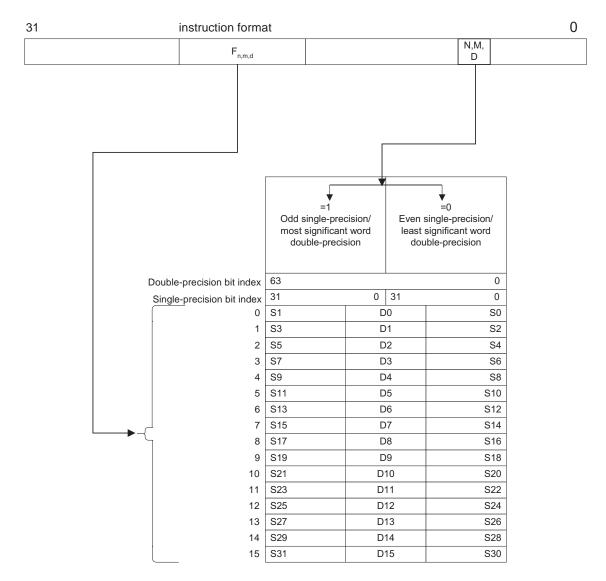

#### 1.3.4 Load/store pipeline

The LS pipeline handles all of the instructions that involve data transfer to and from the ARM1020E macrocell, including loads (LDC) and (LDM), stores (STC) and (STM), moves to coprocessor register (MCR) and (MRCC), and moves from coprocessor register (MRC) and MRRC). It remains synchronized with the ARM1020E macrocell LS pipeline for the duration of the instruction.

Data written to the ARM1020E macrocell is read from the VFP10 coprocessor register file in the Decode (D) stage and transferred to the ARM1020E macrocell in the same cycle, and is latched on the ARM1020E macrocell Execute/Memory cycle boundary. The transfer is made on a dedicated 64-bit store data bus between all coprocessors and the ARM1020E macrocell.

Load data is written to the VFP10 coprocessor on a dedicated 64-bit load bus between the ARM1020E macrocell and all coprocessors. Data is received by the VFP10 coprocessor on the Memory (M)/Writeback (W) boundary. Data is written to the register file in the Writeback stage, and available for forwarding to CDP operations in the same cycle. Figure 1-3 on page 1-10 shows the LS pipeline.

#### 1.3.5 Load/Store operations

The load/store pipeline executes the following instructions:

| FLD  | Load a single data value, either single-precision, double-precision, or 32-bit integer from memory to the VFP10 coprocessor register file.    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| FLDM | Load up to 32 single-precision or integer data values or 16 double-precision data values from memory to the VFP10 coprocessor register file.  |

| FST  | Store a single data value, either single-precision, double-precision, or 32-bit integer from the VFP10 coprocessor register file to memory.   |

| FSTM | Store up to 32 single-precision or integer data values or 16 double-precision data values from the VFP10 coprocessor register file to memory. |

| FMSR  | Transfer a single-precision or integer data value from a VFP10 coprocessor single-precision register to an ARM1020E macrocell register.        |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------|

| FMDHR | Transfer the upper-half of a double-precision data value from a VFP10 coprocessor double-precision register to an ARM1020E macrocell register. |

| FMDLR | Transfer the lower-half of a double-precision data value from a VFP10 coprocessor double-precision register to an ARM1020E macrocell register. |

| FMRS  | Transfer a single-precision or integer data value from an ARM1020E macrocell register to a VFP10 coprocessor single-precision register.        |

| FMRDH | Transfer the upper-half of a double-precision data value from a VFP10 coprocessor double-precision register.                                   |

| FMRDL | Transfer the lower-half of a double-precision data value from an ARM1020E macrocell register to a VFP10 coprocessor double-precision register. |

| FMDRR | Transfer two ARM1020E macrocell registers to a double-precision register in the VFP10 coprocessor.                                             |

| FMRRD | Transfer a double-precision register in the VFP10 coprocessor to two ARM1020E macrocell registers.                                             |

| FMRRS | Transfer a pair of consecutively-numbered registers in the VFP10 coprocessor to two ARM1020E macrocell registers.                              |

| FMXR  | Transfer an ARM1020E macrocell register value to a VFP10 coprocessor control register.                                                         |

| FMRX  | Transfer a VFP10 coprocessor control register to an ARM1020E macrocell register value.                                                         |

# 1.4 Modes of operation

The VFP10 coprocessor provides full IEEE 754 compatibility through a combination of hardware and software. Some of the rare cases in the IEEE 754 can require significant additional compute time to resolve correctly according to the requirements of the IEEE 754 specification. For instance, the VFP10 coprocessor does not process subnormal inputs directly. To provide correct handling of input subnormal according to the IEEE 754 specification, a trap is made to support code to process the operation. Using the support code for processing this operation can require hundreds of cycles. In some applications this is unavoidable, as compliance with the IEEE 754 specification is essential to proper operation of the program. In many other applications, especially in the embedded space, strict compliance to the IEEE 754 is unnecessary, while determinable runtime, low interrupt latency, and low power are of more importance. The VFP10 coprocessor provides both:

- the full compliance mode, referred to as non-RunFast, described in *Non-RunFast mode* on page 1-12

- limited compliance mode, referred to as RunFast, described in *RunFast Mode* on page 1-13.

#### 1.4.1 Non-RunFast mode

When the VFP10 coprocessor is not in RunFast mode, all operations that cannot be processed according to the IEEE 754 specification utilize support code for assistance. The operations requiring support code are:

- any CDP operation involving a subnormal input when FTZ mode (FPSCR[24]) is not enabled

- any CDP operation involving a NaN input when DN mode (FPSCR[25]) is not enabled

- any CDP operation that has the potential of generating an underflow condition

- any CDP operation when the *Inexact Exception Enable* (IXE) bit is set

- any CDP operation when overflow is possible and the *Overflow Exception Enable* (OFE) FPSCR[10]) is set

- any CDP operation that involves an invalid combination as the result of a product overflow and the *Invalid Exception Enable* (IOE, FPSCR[8]) is set.

The VFP10 coprocessor properly signals valid exception conditions according to the IEEE 754 specification. The support code is utilized to determine the nature of the exception, whether processing is required to perform preliminary computation for an exception handler, and to call an installed exception handler or signal the termination of the process.

*Arithmetic exceptions* on page 5-23 describes in greater detail the conditions under which the VFP10 coprocessor traps to support code.

### 1.4.2 RunFast Mode

Although we refer to the behavior of the VFP10 coprocessor as being in *RunFast Mode*, RunFast is not a mode that is set specifically, but the behavior of the VFP10 coprocessor when the FTZ (Flush-to-Zero Mode, FPSCR[24]) and DN (Default NaN Mode, FPSCR[25]) bits are set, and all exception enable bits are clear, that is, no exceptions are enabled in the FPSCR bits [15], [12:8].

Specifically, in Run Fast mode the VFP10 coprocessor:

- processes an input subnormal operand and a tiny result before rounding as a positive zero

- processes an input NaN as a default NaN

- returns the IEEE specified default result for operations that overflow, operations which are considered as invalid, and for divide-by-zero cases, fully in hardware and without additional latency

- processes all operations in hardware without trapping to support code.

In the FTZ mode, the VFP10 coprocessor treats a subnormal input as a positive zero for computation. An operation that is determined to underflow the range of the destination precision before rounding returns a positive zero.

Two flags are available to provide visibility into the VFP10 coprocessor in FTZ mode

- the IDC bit in the FPSCR (FPSCR[7]) is set in a sticky manner to indicate the presence of a flushed input in the computations executed since this bit was last cleared

- the UFC bit in the FPSCR (FPSCR[11]) is set in a sticky manner to indicate the presence of a flushed result in the computations executed since this bit was last cleared.

These two bits provide visibility to the programmer of the behavior of the code in the presence of very small inputs or results.

The *Default NaN* (DN) mode specifies that the result of any operation that involves either input NaNs or generated a NaN result returns the default NaN. Propagation of the fraction bits is maintained only by FABS, FNEG, and FCPY operations, all other CDP operations ignore any information in the fraction bits of an input NaN.

RunFast mode enables the programmer to write code for the VFP10 coprocessor that runs in determinable time, regardless of the characteristics of the input data, without requiring the support code for assistance completing any operation. Within RunFast mode no user exception traps are available, although exception status bits in the FPSCR will be correct according to the IEEE754 for Inexact, Overflow, Invalid operation, and Divide-by-zero. The Underflow exception status bit has been modified for FTZ mode. All these bits are set by an exceptional condition and can only by cleared by a write to the FPSCR. See *Invalid operation* on page 5-13 and following for more detail on these exceptions.

Specifically, in Run Fast mode the VFP10 coprocessor:

- processes an input subnormal operand as a positive zero

- processes an input NaN as a default NaN

- returns the IEEE specified default result for operations that overflow, operations which are considered as invalid, and for divide-by-zero cases, fully in hardware and without additional latency.

# 1.5 Short vector instructions

The VFPv2 architecture provides a mechanism for execution of *short vectors* of up to 8 operations on single-precision data and up to 4 operations for double-precision data. Short vectors are most useful in graphics and signal-processing applications. They contribute to smaller code size, faster execution by supporting parallel operations, most notably multiple transfers, and simplify the generation of high data throughput algorithms.

Short vector operations issue the individual operations specified in the instruction in a serial fashion. A short vector does not begin execution until all the source registers are available and all destination registers are not the target of another operation (to eliminate write-after-write hazards).

See Chapter 4 Instruction Execution in the VFP10 Coprocessor for more information on instruction execution.

# **1.6** Parallel execution of instructions

The VFP10 coprocessor provides the ability to execute several floating-point operations in parallel, while the ARM1020E macrocell is executing ARM instructions. While a short vector operation will execute for a number of cycles in the VFP10 coprocessor, it will appear to the ARM1020E macrocell as a single-cycle instruction and be retired in the ARM1020E macrocell before it completes execution in the VFP10 coprocessor.

The three pipelines are designed to operate independently of one another once initial processing is completed. This makes it possible to issue a short vector operation and a load or store multiple operation in the next cycle, and have both executing at the same time, provided no data hazards exist between the two instructions. With this mechanism, algorithms which can be double-buffered can be written to hide much of the time to transfer data to and from the VFP10 coprocessor under the arithmetic operations, resulting in a significant improvement in performance.

The separate divide and square root pipeline allows for operations, both data transfer and CDPs (provided they are not to the DS pipeline) to execute in parallel with the divide. The DS block has a dedicated write port to the register file, and no special care is needed when executing operations in parallel with divide or square root instructions. This is only true for scalar divides; short vector divides will still support the parallel data transfer operations to execute in parallel in the LS pipeline, but the FMAC pipeline will be unavailable until the final iteration of the short vector divide or square root has completed the initial execute cycle. This is described further in *Parallel execution of operations* on page 4-21.

# 1.7 VFP10 coprocessor treatment of branch instructions

The VFP10 coprocessor does not directly provide branch instructions. Instead, the result of a floating-point compare instruction can be stored in the ARM condition code flags by loading the FPSCR register to the program counter using the FMSTAT instruction. This enables the ARM branch instructions and conditional execution capabilities to be used for executing conditional floating-point code. See section C5 of the *ARM Architecture Reference Manual* for information on the use of ARM conditional execution to test IEEE 754 predicates.

In many cases, in which full IEEE 754 comparisons are not needed, simple comparisons of single-precision data, such as comparisons to zero, or to a constant, can be done using a FMRS transfer and the ARM CMP and CMN instructions. This method is faster in many cases than using a FCMP followed by an FMSTAT instruction. For more information See *Compliance with IEEE-754* on page 3-4.

# 1.8 Writing optimal VFP10 coprocessor code

These guidelines provide significant performance increases for VFP10 coprocessor code:

- Schedule most scalar operations immediately following each other, provided there is no read-after-write hazard. Scalar double-precision multiply or multiply-accumulate instructions, or short vector instructions of length greater than 1, must be followed by either a single ARM or load/store instruction instead of an arithmetic FMAC VFP10 coprocessor instruction.

- Avoid short vector divides and square roots. The VFP10 coprocessor FMAC and DS pipelines are unavailable until the final iteration of the short vector divide or square root is issued from the D stage. If the short vector divide or square root can be separated, other VFP10 coprocessor instructions can be issued in the cycles immediately following the divide or square root. See Example 4-21 on page 4-22 for more information on parallel execution.

- The best performance for data-intensive applications requires double-buffering looped short vector instructions. The vector banks can be divided in half to provide two independent working areas. Arithmetic operations on one half of the bank must be followed by loads or stores to the other bank to take advantage of the simultaneous execution of data transfer operations with the arithmetic instructions.

- The first VFP10 coprocessor instruction following a branch mispredict is serialized and waits for all VFP10 coprocessor instructions prior to the branch to complete. Avoid placing long load/store instructions or divide/square-root instructions before branches that are not predicted correctly a high percentage of the time.

- Moves to and from control registers are serializing. Avoid placing these in loops or time-critical code.

- In non-RunFast mode, avoid reading source operands in the next cycle (this generates a read-after-read hazard).

- Avoid using FCMPZ/FCMPEZ if fully compliant IEEE 754 comparisons are not required. The use of an FMRS instruction with an ARM CMP or CMN may be faster for simple comparisons.

# 1.9 Clocking

The VFP10 coprocessor is a fully static design, with a single clock input **GCLK** that can be stopped indefinitely without loss of state. **GCLK** has the same timing requirements as the ARM1020E **GCLK** and is in phase with it. The VFP **GCLK** must be implemented to avoid excessive skew between the ARM1020E **GCLK** clock to preserve signal integrity and timing on the coprocessor interface. Refer to *ARM1020E Technical Reference Manual* for more information on the coprocessor interface.

The clock generation within the VFP10 coprocessor is tightly integrated with the test functionality. Please see the next section on testing for more information on the impact on the clocking by the test logic.

# 1.10 Testing

The VFP10 coprocessor is a fully-scanned design, with full boundary scan capability allowing for independent testing. See Chapter 5 *Design for Test* for more information on testing.

# 1.11 Modifications from VFP10 coprocessor (Rev 0)

The VFP10 coprocessor described in this Technical Reference Manual is the second revision of the VFP10 coprocessor design. The first revision, VFP10 coprocessor (Rev 0), was designed as a prototype and not intended for product integration. Significant enhancements have been made to the VFP10 coprocessor as a result of continued development of the ARM floating-point products. These differences are as follows:

- 64-bit transfer instructions, implementations of the V5TE MCRR and MRRC operations, are included in the VFP10 coprocessor Rev1. These instructions transfer two ARM registers to and from a double-precision or two contiguous single-precision registers in the VFP10 coprocessor. These instructions are described in *ARM v5TE coprocessor extensions* on page 3-11.

- The DS is separate from the primary execution pipeline (FMAC) pipeline, enabling parallel execution of instructions in the FMAC pipeline with a divide or square root in the DS pipeline. Full hazard detection and register interlocking between the two pipelines is handled completely by hardware. This is discussed further in *Parallel execution of operations* on page 4-21.

- Conditions under which an instruction requires support code intervention have been significantly reduced. The VFP10 coprocessor (Rev 0) requires support code to process arithmetic operations involving infinities or which could potentially overflow, and divide-by-zero cases. The VFP10 coprocessor (Rev1) handles infinity inputs, overflow conditions, and divide-by-zero cases according to the IEEE 754 for the case of the exception not enabled. Support code is utilized for any arithmetic operation for which overflow is possible when the overflow trap is enabled. This is discussed further in Chapter 5 *Exception Handling*.

- The VFP10 coprocessor (Rev1) introduces a new mode which simplifies and significantly increases the performance for programs that use NaNs but do not require propagation of the fraction bits of the NaN. This mode, referred to as Default NaN (DN) mode, when enabled causes the VFP10 coprocessor (Rev 1) to process any arithmetic operation involving a NaN in accordance with the IEEE 754 specification. Any arithmetic operation involving a quiet NaN returns the default NaN without trapping to support code. Any arithmetic operation involving a signaling NaN will set the Invalid Operation Exception status bit, and, if the Invalid Operation exception is enabled, a trap is taken and the user trap handler is called. This is described further in *IEEE-754 implementation choices* on page 3-4.

- A further enhancement is made to the performance of high data throughput code when the code is capable of executing in FTZ mode and Default NaN mode, and when no exceptions are enabled. This condition, referred to as RunFast mode, enables the VFP10 coprocessor to remove certain hazard conditions which are

related to the pipeline, namely between short vector operations and loads involving the short vector source registers. In VFP10 coprocessor (Rev 0) the load operation would be required to stall until the scoreboard locks on the source registers were removed by each iteration of the short vector operation. This requirement was present to preserve the source registers in the event of an exception detected on one of the short vector iterations. When executing in RunFast mode the source registers are not required to be preserved, and the load does not stall. This is discussed further in *RunFast Mode* on page 1-13, and in *Hazard and resource stall conditions* on page 4-11.

- A new exception is introduced in Rev1 which identifies cases of an input subnormal when in Flush-to-zero mode. The VFP10 (Rev 0) coprocessor did not report the instance of a subnormal input when flushed to zero in FTZ mode. The new exception status flag is called IDC. A corresponding enable, IDE, allows for trapping on this case to a user trap handler. This is discussed further in *Input subnormal* on page 5-12.

- The functionality of the UFC bit is modified in FTZ mode to identify the flushing of a tiny result. The exception does not cause a trap even if UFE is enabled. This is discussed further in *Underflow* on page 5-19.

- The VFP10 coprocessor Rev0 was implemented in a fully-synthesized methodology, while the Rev1 is a semi-custom design. The VFP10 coprocessor (Rev1) supports full scan testing, with boundary scan for isolation of the VFP10 coprocessor from other modules for testing purposes.

# Chapter 2 VFP10 Register File

This chapter describes implementation-specific features of the VFP10 coprocessor that are useful to programmers. It contains the following sections:

- About the register file on page 2-2

- *Register file internal formats* on page 2-3

- Decoding the register file on page 2-5

- Loading operands from ARM registers on page 2-7

- Maintaining consistency in register precisions on page 2-9

- Data transfer between memory and VFP10 coprocessor registers on page 2-10

- Access to register banks in CDP operations on page 2-12.

# 2.1 About the register file

The ARM VFP10 coprocessor uses a register file that contains thirty-two 32-bit registers organized in four banks. Each register can be used to store:

- a single-precision data item

- a single integer data item.

Alternatively, a consecutive pair of registers  $(R_{(even+1)}, R_{(even)})$  can be used to store a double-precision item. The registers in the VFP10 coprocessor can also be used as secondary data storage by a non floating-point application, because no modification of the data is performed on a load or store operation.

The register file addressing is circular within each of the banks for most operations. Load and store operations do not circulate, allowing for multiple banks, up to the entire register file, to be loaded or stored in a single instruction. Short vector operations obey certain rules specifying in what conditions the registers in the argument list specify circular buffers or scalar registers. The LEN and STRIDE fields within the FPSCR specify the number of operations performed by the short vector instructions. Further information and examples are in the ARM *Architecture Reference Manual*, Section C5. The banked approach to the register file supports the use of circular buffers by short vector instructions for applications requiring high data throughput, such as filtering and graphics transforms.

# 2.2 Register file internal formats

The VFPv2 architecture provides the option of an internal data format that is different from some or all of the external formats. For the VFP10 coprocessor, data in the register file possesses the same format as data in memory. No modification to the format is performed by a load or store operation for single-precision, double-precision, or integer data. It is the responsibility of the programmer to be aware of the data type in each register. Hardware does not perform any checking of the agreement between data type in the source registers and the data type expected by the instruction. Hardware always interprets the data according to the precision contained in the instruction. It is recommended that for context saving and restoring VFP data registers you use the FLDMX/FSTMX instructions for compatibility with future implementations.

Attempting to access a register that has not been initialized or loaded with valid data is UNPREDICTABLE. A means to detect access to an uninitialized register is to load all registers with signaling NaNs in the precision of the initial access of the register and enable the invalid exception to detect access to an uninitialized register.

## 2.2.1 Integer data format

The VFP10 coprocessor supports signed and unsigned 32-bit integers. Signed integers are treated as two's complement values. Figure 2-1 shows the integer format for signed and unsigned integers.

31 0 Integer

#### Figure 2-1 Integer format

No modification to the data is implicit in a load, store, or transfer operation on integer data. The format of integer data within the register file is identical to the format in memory or in an ARM general-purpose register.

## 2.2.2 Single-precision data format

The single-precision data format used in the VFP10 coprocessor is defined in the ANSI/IEEE Std 754-1985, IEEE Standard for Binary Floating-point Arithmetic. Refer to this for details about:

- the exponent bias

- special formats

- numerical ranges.

Figure 2-2 shows the single-precision bit fields.

| 31 | 30 23    | 3 22                               | 0 |

|----|----------|------------------------------------|---|

| s  | Exponent | Mantissa (no explicit integer bit) |   |

#### Figure 2-2 Single-precision data format

Single-precision data format comprises:

- the sign bit, [bit 31]

- the exponent, bits [30:23]

- the mantissa with no explicit integer bit, bits [22:0].

#### 2.2.3 Double-precision data format

The double-precision data format used in the VFP10 coprocessor is defined in the IEEE 754 specification. Refer to this for details about:

- the exponent bias

- special formats

- numerical ranges.

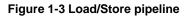

Double-precision format comprises the *Most Significant Word* (MSW) and the *Least Significant Word* (LSW). Figure 2-3 shows the bit fields of the two words in double-precision format.

#### Figure 2-3 Register data formats

MSW comprises:

- the sign bit, bit 31 of the MSW

- the exponent, bits [30:20]

- the mantissa upper 20 bits with no explicit integer bit, bits [19:0].

LSW comprises the mantissa lower 32 bits.

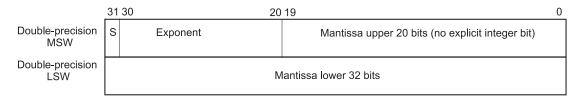

# 2.3 Decoding the register file

Register file access involves the most significant four bits of the register number in the instruction word. For operations involving double-precision operands or destinations, the M, N, and D bit corresponding to a double-precision access must be zero. For single-precision and integer accesses the most significant four bits is in the Fx bit positions (where x is, m, n, or d) and the least significant bit in the M, N, or D bits respectively for each instruction format. Figure 2-4 on page 2-6 shows the register file encoding. See the *ARM Architecture Reference Manual* for instruction formats and the position of these bits.

## Figure 2-4 Register file format

# 2.4 Loading operands from ARM registers

Floating-point data can be transferred between ARM registers and VFP10 coprocessor registers using the MCR, MRC, MCRR, and MRCC coprocessor data transfer instructions. Single-precision and integer data can be transferred to the ARM1020E macrocell and manipulated in a single ARM register, while double-precision data requires two ARM registers. No exceptions are possible on these transfer instructions.

MCR and MRC instructions transfer 32-bit quantities between ARM and VFP10 coprocessor registers. Table 2-1 describes MCR transfersr.

#### Table 2-1 MCR transfers

| Instruction | Operation           | Description                                                                                     |

|-------------|---------------------|-------------------------------------------------------------------------------------------------|

| FMXR        | VFP System Reg = Rd | System register transfer.<br>Register may be any of FPSID, FPSCR,<br>FPEXC, FPINST, or FPINST2. |

| FMDLR       | Dn[31:0] = Rd       | Transfer of the lower half of a double-precision data item.                                     |

| FMDHR       | Dn[63:32] = Rd      | Transfer of the upper half of a double-precision data item.                                     |

| FMSR        | Sn = Rd             | Transfer of a single-precision or integer data item.                                            |

Table 2-2 describes MRC transfers.

#### Table 2-2 MRC transfers

| Instruction | Operation           | Description                                                                                     |

|-------------|---------------------|-------------------------------------------------------------------------------------------------|

| FMRX        | Rd = VFP System Reg | System register transfer.<br>Register may be any of FPSID, FPSCR,<br>FPEXC, FPINST, or FPINST2. |

| FMRDL       | Rd = Dn[31:0]       | Transfer of the lower half of a double-precision data item.                                     |

| FMRDH       | Rd = Dn[63:32]      | Transfer of the upper half of a double-precision data item.                                     |

| FMRS        | Rd = Sn             | Transfer of a single-precision or integer data item.                                            |

MCRR and MRRC instructions transfer 64-bit quantities between ARM and VFP10 coprocessor registers. Table 2-3 describes MCRR transfers.

#### Table 2-3 MCRR transfers

| Instruction | Operation                                   | Description                                                                                                          |

|-------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| FMDRR       | Dm[lower half ] = Rd<br>Dm = [upper half]Rn | Transfer the concatenation of Rn:Rd to VFP double-precision register Dm.                                             |

| FMSRR       | Sm = Rd<br>Sm+1 = Rn                        | Transfer the pair of ARM registers {Rn, Rd}<br>to a contiguous pair of VFP single-precision<br>registers {Sm+1, Sm}. |

Table 2-4 describes MRRC transfers

## Table 2-4 MRRC transfers

| Instruction | Operation                                  | Description                                                                                                          |

|-------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| FMRRD       | Rd = Dm[lower half]<br>Rn = Dm[upper half] | Transfer the VFP double-precision register<br>Dm to the concatenation of Rn:Rd.                                      |

| FMRRS       | Rd = Sm $Rn = Sm+1$                        | Transfer the contiguous pair of VFP<br>single-precision registers {Sm+1, Sm} to a<br>pair of ARM registers {Rn, Rd}. |

# 2.5 Maintaining consistency in register precisions

The VFP10 coprocessor register file stores single-precision, double-precision, and integer data in the same registers. For example, D6 occupies the same registers as S12 and S13. The usable format of the register or registers is a function of the last load or arithmetic instruction that wrote to the register or registers.

The hardware does not do any checking of the register contents to enforce consistent use of the current register format with the precision of the current operation. Inconsistent use of the registers is possible but UNPREDICTABLE. The data is interpreted by the hardware in the format required by the instruction regardless of the latest store or write operation to the register. It is the task of the compiler or programmer to maintain consistency in register usage.

# 2.6 Data transfer between memory and VFP10 coprocessor registers

The format for accessing data stored in memory is determined by the CP15 control register B bit. The ARM1020E macrocell supports both little-endian and big-endian access formats in memory.

The ARM1020E macrocell stores 32-bit words in memory with the LSB in the lowest byte of memory regardless of the endianness selected. For a store of a single-precision data value the LSB bits are located at the target address with the lower two bits of the address set to 00. The MSB is at the target address with the lower two bits set to 11. To load the single-precision data to an ARM register or to a VFP10 coprocessor register you must set the lower two bits of the target address to 00.

For single-precision data, Table 2-5 on page 2-10 shows the data storage in memory and the address access to each byte in both little-endian and big-endian access modes. In the examples in Table 2-5 on page 2-10 and Table 2-6 on page 2-11 the target address is 0x4000000.

| Single-precision data bytes | Address in<br>memory | Little-endian<br>byte address | Big-endian byte<br>address |

|-----------------------------|----------------------|-------------------------------|----------------------------|

| MSB<br>Bits[31:24]          | 0x40000003           | 0x40000003                    | 0x40000000                 |

| Bits[23:16]                 | 0x40000002           | 0x40000002                    | 0x40000001                 |

| Bits[15:8]                  | 0x40000001           | 0x40000001                    | 0x40000002                 |

| LSB<br>Bits[7:0]            | 0x40000000           | 0x40000000                    | 0x40000003                 |

#### Table 2-5 Single-precision data memory images and byte addresses

For double-precision data, the location of the two words that comprise the data are stored in different locations for little-endian and big-endian data access formats. Table 2-6 shows the data storage in memory and the address to access each byte in little-endian and big-endian access modes.

| Double-                 | Little-endian        | Little-endian |                      |              |

|-------------------------|----------------------|---------------|----------------------|--------------|

| precision<br>data bytes | Address in<br>memory | Byte address  | Address in<br>memory | Byte address |

| MSB<br>Bits[63:56]      | 0x40000007           | 0x40000007    | 0x40000003           | 0x40000000   |

| Bits[55:48]             | 0x40000006           | 0x40000006    | 0x40000002           | 0x40000001   |

| Bits[47:40]             | 0x40000005           | 0x40000005    | 0x40000001           | 0x40000002   |

| Bits[39:32]             | 0x40000004           | 0x40000004    | 0x40000000           | 0x40000003   |

| Bits[31:24]             | 0x40000003           | 0x40000003    | 0x40000007           | 0x40000004   |

| Bits[23:16]             | 0x40000002           | 0x40000002    | 0x40000006           | 0x40000005   |

| Bits[15:08]             | 0x40000001           | 0x40000001    | 0x40000005           | 0x40000006   |

| LSB<br>Bits[7:0]        | 0x40000000           | 0x40000000    | 0x40000004           | 0x40000007   |

Table 2-6 Double-precision data memory images and byte addresses

The memory image for the data is identical for both little-endian and big-endian within word data items. The hardware performs the transformations of the address to provide both little-endian and big-endian addressing to the programmer.

# 2.7 Access to register banks in CDP operations

The register file is especially suited for short vector operations. You can use four banks of registers in a circular fashion to facilitate signal processing and matrix operations. For details of this refer to the *ARM Architecture Reference Manual*.

## 2.7.1 About register banks

The register file is divided into 4 banks with 8 registers in each bank for single-precision operations and 4 registers per bank for double-precision operations. The banks are accessed in a circular manner by CDP instructions. Load and store multiple instructions do not access the registers in a circular manner but will treat the register file as a linearly ordered structure.

Table 2-7 shows how the register banks are defined.

| Bank | Single-precision registers in bank | Double-precision registers in bank |  |

|------|------------------------------------|------------------------------------|--|

| 0    | S0-S7                              | D0-D3                              |  |

| 1    | S8-S15                             | D4-D7                              |  |

| 2    | S16-S23                            | D8-D11                             |  |

| 3    | S24-S31                            | D12-D15                            |  |

Table 2-7 Register bank description

A short vector CDP operation that has a source or destination vector crossing a bank boundary accesses the registers within the bank as if the last register in the bank was followed in a linear order by the first register in the bank.

Example 2-1 on page 2-12 shows a short vector operation crossing bank boundaries.

#### Example 2-1 Register access example

| For instance, the add ope<br>FADDS S11, S22, S31                 | eration:                                                                                                                                                                                                      |

|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| if treated as a vector or manner:                                | f length 6, would access the registers in the following                                                                                                                                                       |

| FADDS S11, S22, S31<br>FADDS S12, S23, S24                       | ; the first iteration<br>; the second iteration. The second source vector has<br>; wrapped around and is accessing the first register in<br>; the 4th bank                                                    |

| FADDS S13, S16, S25                                              | ; the third iteration. The first source vector has<br>; wrapped around and is accessing the first register in<br>; the 3rd bank                                                                               |

| FADDS S14, S17, S26<br>FADDS S15, S18, S27<br>FADDS S8, S19, S28 | <pre>; the fourth iteration<br/>; the fifth iteration<br/>; the sixth and last iteration The destination vector<br/>; has wrapped around and is writing to the first;<br/>; register in the second bank</pre> |

## 2.7.2 Operations using register banks

The register file organization supports four types of operations described in the following sections:

- Scalar-only operations on page 2-13

- Vector-only operations on page 2-14

- Vector-only operation with scalar source on page 2-14

- Scalar operations in short vector mode on page 2-15.

See *FPSCR register* on page 3-23 for details of LEN and STRIDE fields and the FPSCR.

## Scalar-only operations

An operation is a scalar-only operation if the operands are treated as scalars and the result is a scalar. There are two ways to perform a scalar-only operation:

• Setting the LEN field of the *Floating-Point Status and Control Register* (FPSCR) to 0 selects a vector length of 1. For example, if LEN = 0, then the following operation:

FADDS S12, S21, S22

results in the sum of the single-precision values in S21 and S22 being written to S12.

• If the LEN field of the FPSCR is not 0, the operation is scalar-only if the destination register is in bank 0. For example, regardless of the value of LEN, the following operation:

FADDD D2, D5, D14

results in the sum of the double-precision values in D5 and D14 being written to D2. No other operation will be performed by this instruction even though the LEN field value is nonzero. *Scalar operations in short vector mode* on page 2-15 shows an example where scalar and short vector operations are intermixed.

Some operations can only operate on scalar data regardless of the value of the LEN field or destination register bank number. These operations are:

- compare instructions FCMP, FCMPZ, FCMPE, and FCMPEZ

- integer conversion instructions FTOUI, FTOUIZ, FTOSI, FTOSIZ, FUITO, and FSITO

- precision conversion instructions FCVTDS and FCVTSD.

## **Vector-only operations**

Vector-only operations require the LEN field to be nonzero, and the destination and Fm registers not in bank 0.

For example, if LEN = 3 (an effective vector length of 4) and STRIDE = 0 (for a vector stride of one) the following instruction:

FMACS S16, S0, S8

results in the following operations being performed as an atomic operation:

FMACS S16, S0, S8 FMACS S17, S1, S9 FMACS S18, S2, S10 FMACS S19, S3, S11.

## Vector-only operation with scalar source

The VFPv2 architecture enables a vector to be operated on by a scalar operand. The destination must be a vector (not in bank 0) and the Fm operand must be in bank 0.

For example, if LEN = 1 (an effective vector length of 2) and STRIDE = 0 (for a vector stride of one) the following operation:

FMULD D12, D8, D2

results in the following scalar operations being performed as an atomic operation:

FMULD D12, D8, D2 FMULD D13, D9, D2.

This effectively scales the two entry vectors (D8, D9) by the value in D2 and writes the new vector to D12 and D13.

## Scalar operations in short vector mode

You can intermix scalar and short vector operations by carefully selecting the source and destination registers. Combining the second method of performing scalar-only operations with nonscalar operation means that it is not necessary to change the LEN field to 0 from a nonzero value to perform scalar operations.

For example, if LEN = 1 for a vector length of 2 and STRIDE = 0 (for a vector stride of one), then the following instructions:

FABSD D4, D8 FADDS S0, S0, S31 FMULS S24, S26, S1

results in the following operations being performed:

FABSD D4, D8;a vector double-precision ABS operationFABSD D5, D9;on registers (D8, D9) to (D4, D5)FADDS S0, S0,S31 ;a scalar increment of S0 by S31FMULS S24,S26,S1 ;a vector(S26, S27) scaled by S1FMULS S25,S27,S1 ;and written to (S24, S25)

Table 2-8 to Table 2-11 on page 2-16 summarize the four types of operations possible in the VFPv2 architecture. *Any* refers to the availability of all registers in the precision for the specified operand. The VFP10 coprocessor supports all these operations in hardware. *S* refers to a scalar register only with a single register on each of the Fd, Fn, and Fm operands. *V* refers to a vector register with multiple registers for Fd and Fn, and possibly also for Fm. Table 2-8 describes single-precision three-operand register usage.

| LEN field | Fd   | Fn  | Fm   | Operation type                     |

|-----------|------|-----|------|------------------------------------|

| 0         | Any  | Any | Any  | S = S  op  S  or  S = S  op  S * S |

| Non-0     | 0-7  | Any | Any  | S = S  op  S  or  S = S  op  S * S |

| Non-0     | 8-31 | Any | 0-7  | V = V  op  S  or  V = V  op  V * S |

| Non-0     | 8-31 | Any | 8-31 | V = V  op  V  or  V = V  op  V * V |

Table 2-8 Single-precision three-operand register usage

Table 2-9 describes single-precision two-operand register usage.

| LEN<br>field | Fd   | Fm   | Operation<br>type |

|--------------|------|------|-------------------|

| 0            | Any  | Any  | S = op S          |

| Non-0        | 0-7  | Any  | S = op S          |

| Non-0        | 8-31 | 0-7  | V= op S           |

| Non-0        | 8-31 | 8-31 | V= op V           |

Table 2-9 Single-precision two-operand register usage

Table 2-10 describes double-precision three-operand register usage.

Table 2-10 Double-precision three-operand register usage

| LEN field | Fd   | Fn  | Fm   | Operation type                     |

|-----------|------|-----|------|------------------------------------|

| 0         | Any  | Any | Any  | S = S  op  S  or  S = S  op  S * S |

| Non-0     | 0-3  | Any | Any  | S = S  op  S  or  S = S  op  S * S |

| Non-0     | 4-15 | Any | 0-3  | V = V  op  S  or  V = V  op  V * S |

| Non-0     | 4-15 | Any | 4-15 | V = V  op  V  or  V = V  op  V * V |

Table 2-10 describes double-precision two-operand register usage.

#### Table 2-11 Double-precision two-operand register usage

| LEN<br>field | Fd   | Fm   | Operation<br>type                       |

|--------------|------|------|-----------------------------------------|

| 0            | Any  | Any  | $\mathbf{S} = \mathbf{op} \ \mathbf{S}$ |

| Non-0        | 0-3  | Any  | $\mathbf{S} = \mathbf{op} \ \mathbf{S}$ |

| Non-0        | 4-15 | 0-3  | V= op S                                 |

| Non-0        | 4-15 | 4-15 | V= op V                                 |

# Chapter 3 VFP10 Programmer's Model

This chapter describes implementation-specific features of the VFP10 coprocessor that are useful to programmers. It contains the following sections:

- *About the programmer's model* on page 3-2

- *Compliance with IEEE-754* on page 3-4

- ARM v5TE coprocessor extensions on page 3-11

- Summary of VFP coprocessor system control registers on page 3-17

- FPSCR register on page 3-23.

# 3.1 About the programmer's model

This section gives a general introduction to the VFP10 coprocessor implementation of the VFPv2 floating-point architecture.

#### ARM Architecture Reference Manual deals with Architecture aspects of VFPv1.

VFP10 implements all the instructions and modes of the VFPv2 architecture. The VFPv2 adds the following features and enhancements to the VFPv1 architecture:

- The ARM v5TE instruction set, which includes MRRC and MCRR 64-bit ARM to coprocessor transfer instructions. These instructions allow the transfer of a double-precision register, or two consecutively numbered single-precision registers, to or from a pair of ARM registers. See *Loading operands from ARM registers* on page 2-7 for syntax and usage of VFP MRRC and MCRR instructions.

- The Default NaN operating mode. In this mode, any operation that involves one or more NaNs as operands produces the default NaN as a result, rather than return the NaN or one of the NaNs involved in the operation. This mode is compatible with the IEEE-754 specification but not with current industry handling of NaNs.

- Addition of the subnormal Input exception flag (IDC). This flag is set whenever an operation has as an operand a subnormal value. It remains set until cleared through a write to the FPSCR. A separate trap enable bit is also added (IDE). When set, the VFP10 coprocessor traps to the UNDEFINED trap upon an assertion of IDC.

- Modification of the functionality of the UFC bit when FTZ modes are enabled. In this mode, the UFC bit is set whenever a result is below the threshold for normal numbers before rounding, and is flushed to zero. UFC remains set until cleared through a write to the FPSCR. The underflow trap enable bit, UFE, does not cause a trap to the UNDEFINED trap handler on an assertion of UFC.

- Modification of the invalid trap functionality when FTZ and DN modes are enabled. In this mode, the IOC bit is set on any operation that would normally have asserted IOC with the exception of certain cases of floating-point to integer conversions. If the conversion is performed in a rounding mode other than round-to-zero (truncate), and the result overflows the destination integer format due to rounding, IOC does not cause a trap to be taken if IOE is enabled, but does set the IOC bit. If IOE is set and a floating-point to integer conversion overflows the destination integer format before rounding, IOC is set, and the VFP10 coprocessor does trap to the UNDEFINED trap handler.

• Modification of the functionality of the IXC bit in FTZ mode. In the VFPv1 architecture specification the IXC bit was set when an input or result was flushed to zero. In VFPv2 the IDC and UFC bits provide this information. See *Inexact result* on page 5-21 for more information.

# 3.2 Compliance with IEEE-754

This section introduces issues connected with IEEE-754 compliance:

- why compliance is important

- hardware and software components

- software-based components and their availability.

## 3.2.1 An IEEE-754-compliant implementation