# ARM1026EJ-S

Revision: r0p2

### **Technical Reference Manual**

#### ARM1026EJ-S

#### **Technical Reference Manual**

Copyright © 2003 ARM Limited. All rights reserved.

#### **Release Information**

#### Change history

| Date               | Issue | Change                                                  |

|--------------------|-------|---------------------------------------------------------|

| 24 September, 2002 | A     | First release.                                          |

| 20 December, 2002  | В     | Second release. Updated for ARM1026EJ-S r0p1 processor. |

| 20 June, 2003      | C     | Third release. Updated for ARM1026EJ-S r0p2 processor.  |

#### **Proprietary Notice**

Words and logos marked with  $^{\circ}$  or  $^{\circ}$  are registered trademarks or trademarks of ARM Limited in the EU and other countries, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM Limited in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM Limited shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

#### **Confidentiality Status**

This document is Open Access. It has no restriction on distribution.

#### **Product Status**

The information in this document is final (information on a developed product).

#### Web Address

http://www.arm.com

# Contents

# **ARM1026EJ-S Technical Reference Manual**

|           | Prefa |                                 |       |

|-----------|-------|---------------------------------|-------|

|           |       | About this document             | xviii |

|           |       | Feedback                        | xxiv  |

| Chapter 1 | Intro | oduction                        |       |

| -         | 1.1   | About the processor             | 1-2   |

|           | 1.2   | Components of the processor     |       |

|           | 1.3   | Silicon revision information    | 1-10  |

| Chapter 2 | Integ | ger Core                        |       |

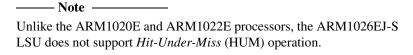

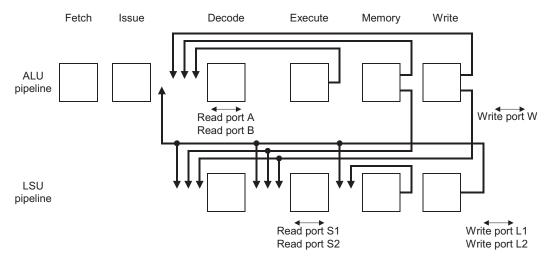

| -         | 2.1   | About the integer core          | 2-2   |

|           | 2.2   | Pipeline                        | 2-4   |

|           | 2.3   | Prefetch unit                   | 2-6   |

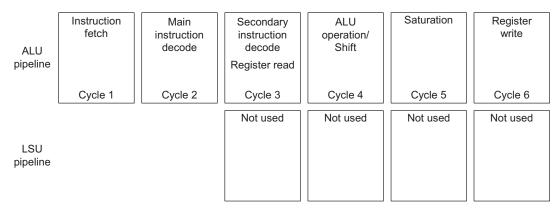

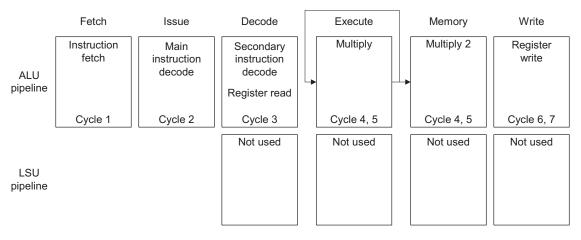

|           | 2.4   | Typical ALU/multiply operations | 2-7   |

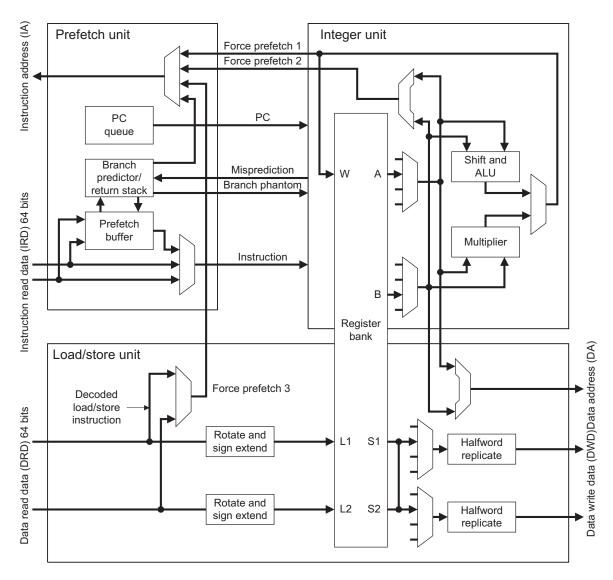

|           | 2.5   | Load/store unit                 |       |

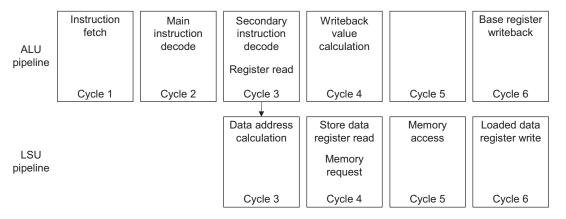

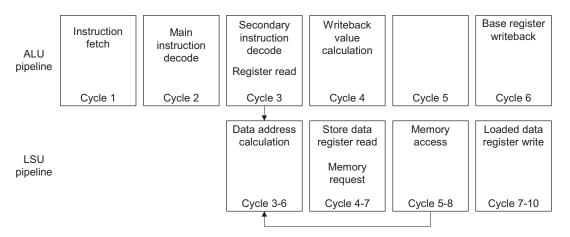

|           | 2.6   | Typical load/store operations   | 2-9   |

| Chapter 3 | Programmer's Model |                                                     |      |  |

|-----------|--------------------|-----------------------------------------------------|------|--|

|           | 3.1                | About the programmer's model                        | 3-2  |  |

|           | 3.2                | Program status registers                            | 3-3  |  |

|           | 3.3                | About the CP15 system control coprocessor registers | 3-5  |  |

|           | 3.4                | CP15 register descriptions                          | 3-9  |  |

|           | 3.5                | CP15 instruction summary                            | 3-70 |  |

| Chapter 4 | Cloc               | king and Reset Timing                               |      |  |

| •         | 4.1                | About clock and reset signals                       | 4-2  |  |

|           | 4.2                | Clock interfaces                                    |      |  |

|           | 4.3                | Reset                                               | 4-4  |  |

| Chapter 5 | Prefe              | etch Unit                                           |      |  |

| •         | 5.1                | About the prefetch unit                             | 5-2  |  |

|           | 5.2                | Branch prediction activity                          |      |  |

|           | 5.3                | Branch instruction cycle summary                    |      |  |

|           | 5.4                | Instruction memory barriers                         |      |  |

| Chapter 6 | Bus                | Interface                                           |      |  |

| •         | 6.1                | About the bus interface                             | 6-2  |  |

|           | 6.2                | Bus transfer characteristics                        |      |  |

|           | 6.3                | Bus transfer cycle timing                           |      |  |

|           | 6.4                | Topology                                            |      |  |

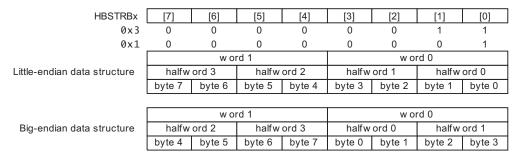

|           | 6.5                | Endianness of BIU transfers                         | 6-24 |  |

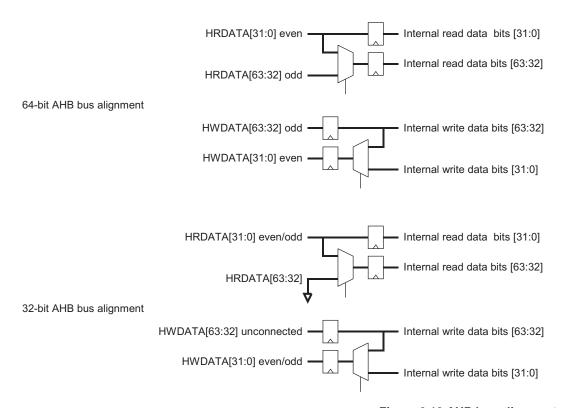

|           | 6.6                | 64-bit and 32-bit AHB data buses                    | 6-25 |  |

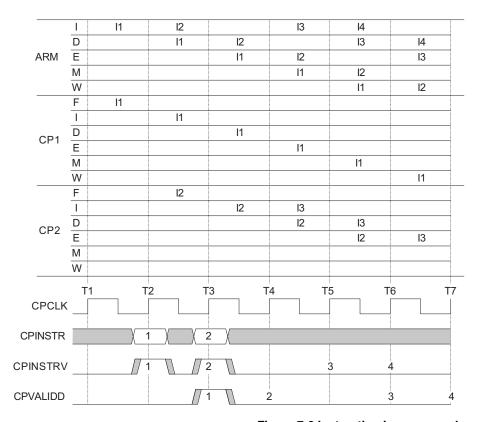

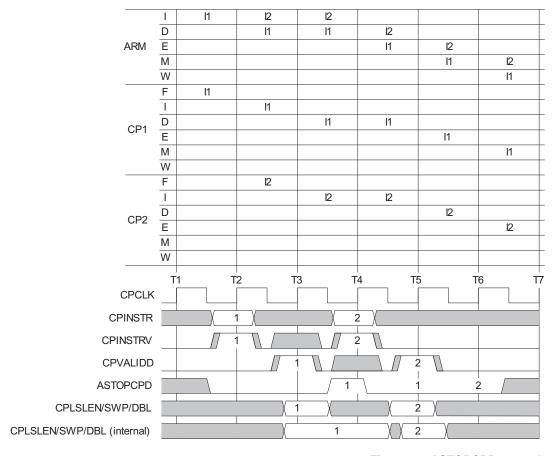

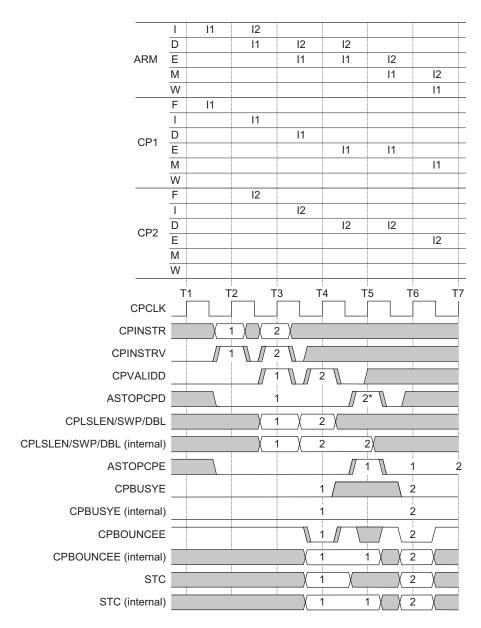

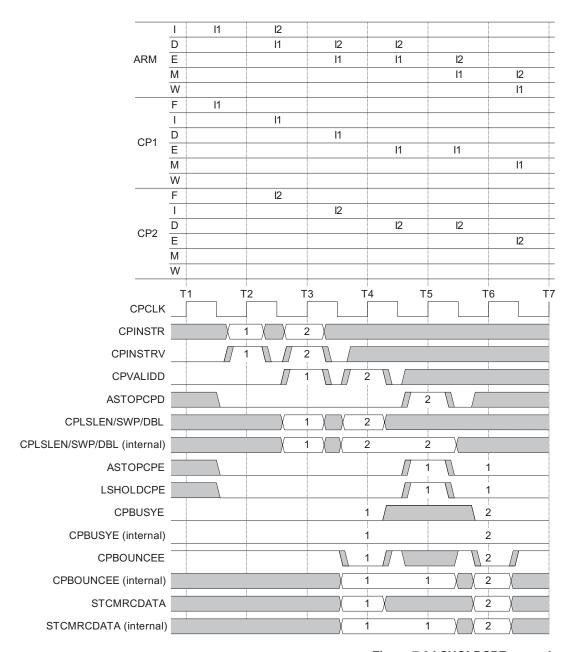

| Chapter 7 | Copr               | rocessor Interface                                  |      |  |

| •         | 7.1                | About the coprocessor interface                     | 7-2  |  |

|           | 7.2                | Coprocessor interface signals                       |      |  |

|           | 7.3                | Design considerations                               |      |  |

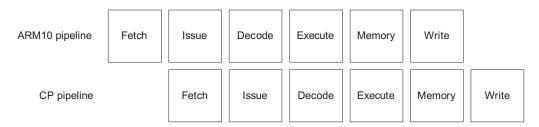

|           | 7.4                | Parallel execution                                  |      |  |

|           | 7.5                | Rules for the interface                             | 7-9  |  |

|           | 7.6                | Pipeline signal assertion                           | 7-10 |  |

|           | 7.7                | Instruction issue                                   |      |  |

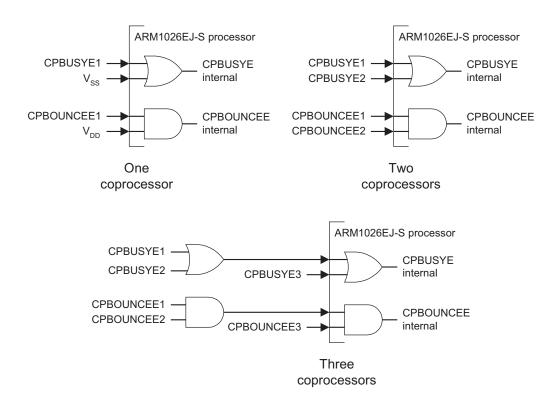

|           | 7.8                | Hold signals                                        | 7-21 |  |

|           | 7.9                | Instruction cancelation                             |      |  |

|           | 7.10               | Bounced instructions                                | 7-47 |  |

|           | 7.11               | Data buses                                          | 7-53 |  |

| 8.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Chapter 8  | Debu  | g                                            |       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------|----------------------------------------------|-------|

| 8.2   Register descriptions   8-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -          | 8.1   | About the debug unit                         | 8-2   |

| 8.4   Halt mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            | 8.2   |                                              |       |

| 8.5   Monitor mode   8-22     8.6   Values in the link register after exceptions   8-24     8.7   Comms channel   8-25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            | 8.3   | Software lockout function                    | 8-18  |

| 8.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            | 8.4   | Halt mode                                    | 8-19  |

| Record                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            | 8.5   | Monitor mode                                 | 8-22  |

| Chapter 9         Debug Test Access Port           9.1         Debug test access port and halt mode         9-2           9.2         DBGTAP instructions         9-4           9.3         Scan chain descriptions         9-7           Chapter 10         Memory Management Unit           10.1         About the MMU         10-2           10.2         MMU software-accessible registers         10-6           10.3         Address translation         10-8           10.4         MMU memory access control         10-26           10.5         MMU cachable and bufferable information         10-28           10.6         MMU and pending write buffer         10-29           10.7         Fault checking sequence         10-30           10.8         Fault priority         10-33           10.9         MMU aborts and external aborts         10-34           10.10         Memory Protection Unit         11-2           11.1         About the MPU         11-2           11.2         MPU software-accessible registers         11-3           11.3         Configuring the MPU         11-5           11.4         Overlapping protection regions         11-8           11.5         Fault priority                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            | 8.6   | Values in the link register after exceptions | 8-24  |

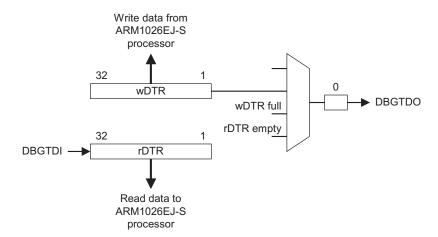

| 9.1   Debug test access port and halt mode   9-2   9.2   DBGTAP instructions   9-4   9-3   Scan chain descriptions   9-4   9-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            | 8.7   | Comms channel                                | 8-25  |

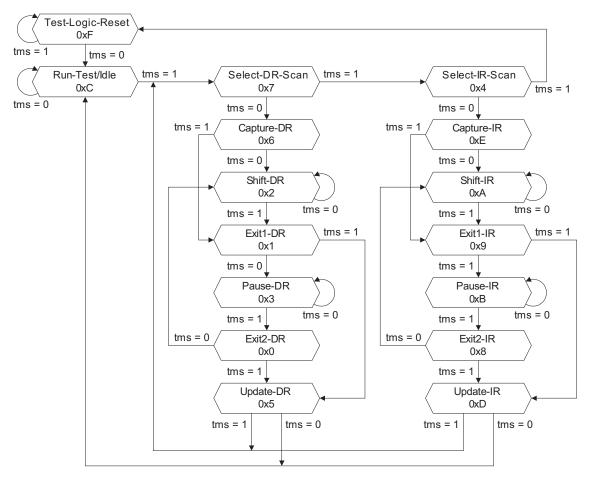

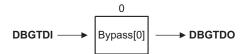

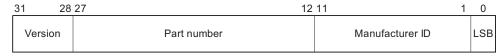

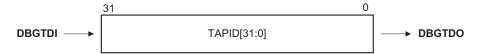

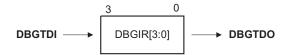

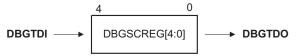

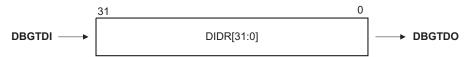

| 9.2 DBGTAP instructions   9-4   9.3 Scan chain descriptions   9-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Chapter 9  | Debu  | g Test Access Port                           |       |

| 9.3   Scan chain descriptions   9-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            | 9.1   | Debug test access port and halt mode         | 9-2   |

| Chapter 10         Memory Management Unit           10.1         About the MMU         10-2           10.2         MMU software-accessible registers         10-6           10.3         Address translation         10-8           10.4         MMU memory access control         10-26           10.5         MMU achable and bufferable information         10-28           10.6         MMU and pending write buffer         10-29           10.7         Fault checking sequence         10-30           10.8         Fault priority         10-33           10.9         MMU aborts and external aborts         10-34           10.10         Memory parity         10-35           Chapter 11         Memory Protection Unit           11.1         About the MPU         11-2           11.2         MPU software-accessible registers         11-3           11.3         Configuring the MPU         11-5           11.4         Overlapping protection regions         11-8           11.5         Fault priority         11-8           11.5         Fault priority         11-9           11.6         MPU aborts and external aborts         11-10           Chapter 12           Cac                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            | 9.2   | DBGTAP instructions                          | 9-4   |

| 10.1   About the MMU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            | 9.3   | Scan chain descriptions                      | 9-7   |

| 10.2 MMU software-accessible registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Chapter 10 | Memo  | ory Management Unit                          |       |

| 10.3   Address translation   10-8   10-4   MMU memory access control   10-26   10-5   MMU cachable and bufferable information   10-28   10-6   MMU and pending write buffer   10-29   10-7   Fault checking sequence   10-30   10.8   Fault priority   10-33   10.9   MMU aborts and external aborts   10-34   10.10   Memory parity   10-35      Chapter 11   Memory Protection Unit   11.1   About the MPU   11-2   11.2   MPU software-accessible registers   11-3   11.3   Configuring the MPU   11-5   11.4   Overlapping protection regions   11-8   11.5   Fault priority   11-9   11.6   MPU aborts and external aborts   11-10      Chapter 12   Caches   12-2   12.2   Enabling the caches   12-3   12.3   Cache and TCM access priorities   12-6   12.4   Cache MVA and set/way formats   12-7   12.5   Cache size support   12-9   12.6   Cache support for external aborts   12-10   12.7   Castout functionality, DCache only   12-11   12.8   Cache support for MBIST   12-13   12-13   12-9   Cache memory parity   12-13   12-13   12-9   12-9   Cache memory parity   12-13   12-13   12-13   12-9   12-9   Cache memory parity   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13   12-13    |            | 10.1  | About the MMU                                | 10-2  |

| 10.4 MMU memory access control   10-26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            | 10.2  | MMU software-accessible registers            | 10-6  |

| 10.5 MMU cachable and bufferable information   10-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            | 10.3  | Address translation                          | 10-8  |

| 10.6 MMU and pending write buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            | 10.4  | MMU memory access control                    | 10-26 |

| 10.7   Fault checking sequence   10-30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            | 10.5  | MMU cachable and bufferable information      | 10-28 |

| 10.8   Fault priority   10-33   10.9   MMU aborts and external aborts   10-34   10.10   Memory parity   10-35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            | 10.6  | MMU and pending write buffer                 | 10-29 |

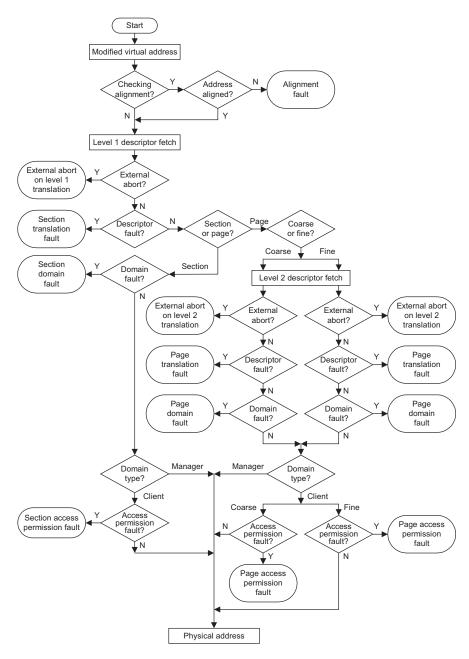

| 10.9   MMU aborts and external aborts   10-34   10.10   Memory parity   10-35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            | 10.7  | Fault checking sequence                      | 10-30 |

| The image is a content of the image is a c |            | 10.8  | ·                                            |       |

| Chapter 11         Memory Protection Unit           11.1         About the MPU         11-2           11.2         MPU software-accessible registers         11-3           11.3         Configuring the MPU         11-5           11.4         Overlapping protection regions         11-8           11.5         Fault priority         11-9           11.6         MPU aborts and external aborts         11-10           Chapter 12         Caches           12.1         About the caches         12-2           12.2         Enabling the caches         12-3           12.3         Cache and TCM access priorities         12-3           12.4         Cache MVA and set/way formats         12-7           12.5         Cache size support         12-9           12.6         Cache support for external aborts         12-10           12.7         Castout functionality, DCache only         12-11           12.8         Cache support for MBIST         12-12           12.9         Cache memory parity         12-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            | 10.9  |                                              |       |

| 11.1       About the MPU       11-2         11.2       MPU software-accessible registers       11-3         11.3       Configuring the MPU       11-5         11.4       Overlapping protection regions       11-8         11.5       Fault priority       11-9         11.6       MPU aborts and external aborts       11-10         Chapter 12         Caches       12-2         12.1       About the caches       12-3         12.2       Enabling the caches       12-3         12.3       Cache and TCM access priorities       12-6         12.4       Cache MVA and set/way formats       12-7         12.5       Cache size support       12-9         12.6       Cache support for external aborts       12-10         12.7       Castout functionality, DCache only       12-11         12.8       Cache support for MBIST       12-12         12.9       Cache memory parity       12-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            | 10.10 | Memory parity                                | 10-35 |

| 11.2       MPU software-accessible registers       11-3         11.3       Configuring the MPU       11-5         11.4       Overlapping protection regions       11-8         11.5       Fault priority       11-9         11.6       MPU aborts and external aborts       11-10         Chapter 12         Caches       12-2         12.1       About the caches       12-3         12.2       Enabling the caches       12-3         12.3       Cache and TCM access priorities       12-6         12.4       Cache MVA and set/way formats       12-7         12.5       Cache size support       12-9         12.6       Cache support for external aborts       12-10         12.7       Castout functionality, DCache only       12-11         12.8       Cache support for MBIST       12-12         12.9       Cache memory parity       12-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Chapter 11 | Memo  | ory Protection Unit                          |       |

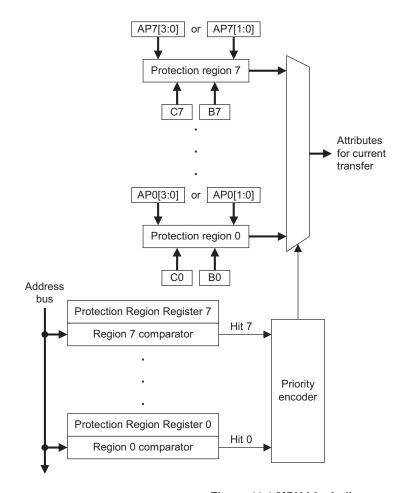

| 11.3       Configuring the MPU       11-5         11.4       Overlapping protection regions       11-8         11.5       Fault priority       11-9         11.6       MPU aborts and external aborts       11-10         Chapter 12         Caches         12.1       About the caches       12-2         12.2       Enabling the caches       12-3         12.3       Cache and TCM access priorities       12-6         12.4       Cache MVA and set/way formats       12-7         12.5       Cache size support       12-9         12.6       Cache support for external aborts       12-10         12.7       Castout functionality, DCache only       12-11         12.8       Cache support for MBIST       12-12         12.9       Cache memory parity       12-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            | 11.1  | About the MPU                                | 11-2  |

| 11.4       Overlapping protection regions       11-8         11.5       Fault priority       11-9         11.6       MPU aborts and external aborts       11-10         Chapter 12         Caches         12.1       About the caches       12-2         12.2       Enabling the caches       12-3         12.3       Cache and TCM access priorities       12-6         12.4       Cache MVA and set/way formats       12-7         12.5       Cache size support       12-9         12.6       Cache support for external aborts       12-10         12.7       Castout functionality, DCache only       12-11         12.8       Cache support for MBIST       12-12         12.9       Cache memory parity       12-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            | 11.2  | MPU software-accessible registers            | 11-3  |

| 11.5       Fault priority       11-9         11.6       MPU aborts and external aborts       11-10         Chapter 12         Caches         12.1       About the caches       12-2         12.2       Enabling the caches       12-3         12.3       Cache and TCM access priorities       12-6         12.4       Cache MVA and set/way formats       12-7         12.5       Cache size support       12-9         12.6       Cache support for external aborts       12-10         12.7       Castout functionality, DCache only       12-11         12.8       Cache support for MBIST       12-12         12.9       Cache memory parity       12-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            | 11.3  | Configuring the MPU                          | 11-5  |

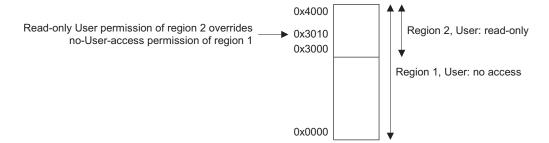

| 11.6       MPU aborts and external aborts       11-10         Chapter 12       Caches         12.1       About the caches       12-2         12.2       Enabling the caches       12-3         12.3       Cache and TCM access priorities       12-6         12.4       Cache MVA and set/way formats       12-7         12.5       Cache size support       12-9         12.6       Cache support for external aborts       12-10         12.7       Castout functionality, DCache only       12-11         12.8       Cache support for MBIST       12-12         12.9       Cache memory parity       12-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            | 11.4  | Overlapping protection regions               | 11-8  |

| Chapter 12         Caches           12.1         About the caches         12-2           12.2         Enabling the caches         12-3           12.3         Cache and TCM access priorities         12-6           12.4         Cache MVA and set/way formats         12-7           12.5         Cache size support         12-9           12.6         Cache support for external aborts         12-10           12.7         Castout functionality, DCache only         12-11           12.8         Cache support for MBIST         12-12           12.9         Cache memory parity         12-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            | 11.5  | Fault priority                               | 11-9  |

| 12.1       About the caches       12-2         12.2       Enabling the caches       12-3         12.3       Cache and TCM access priorities       12-6         12.4       Cache MVA and set/way formats       12-7         12.5       Cache size support       12-9         12.6       Cache support for external aborts       12-10         12.7       Castout functionality, DCache only       12-11         12.8       Cache support for MBIST       12-12         12.9       Cache memory parity       12-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            | 11.6  | MPU aborts and external aborts               | 11-10 |

| 12.2       Enabling the caches       12-3         12.3       Cache and TCM access priorities       12-6         12.4       Cache MVA and set/way formats       12-7         12.5       Cache size support       12-9         12.6       Cache support for external aborts       12-10         12.7       Castout functionality, DCache only       12-11         12.8       Cache support for MBIST       12-12         12.9       Cache memory parity       12-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Chapter 12 | Cach  | es                                           |       |

| 12.3       Cache and TCM access priorities       12-6         12.4       Cache MVA and set/way formats       12-7         12.5       Cache size support       12-9         12.6       Cache support for external aborts       12-10         12.7       Castout functionality, DCache only       12-11         12.8       Cache support for MBIST       12-12         12.9       Cache memory parity       12-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            | 12.1  | About the caches                             | 12-2  |

| 12.4       Cache MVA and set/way formats       12-7         12.5       Cache size support       12-9         12.6       Cache support for external aborts       12-10         12.7       Castout functionality, DCache only       12-11         12.8       Cache support for MBIST       12-12         12.9       Cache memory parity       12-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            | 12.2  | Enabling the caches                          | 12-3  |

| 12.5       Cache size support       12-9         12.6       Cache support for external aborts       12-10         12.7       Castout functionality, DCache only       12-11         12.8       Cache support for MBIST       12-12         12.9       Cache memory parity       12-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            | 12.3  |                                              |       |