S3053

#### **FEATURES**

- Supports 2.5 Gbit/sec data rates

- Fully differential for minimum jitter accumulation

- TTL select

- High speed  $50\Omega$  source terminated outputs

- 0.84 W typical power dissipation

- 3.3 V power supply

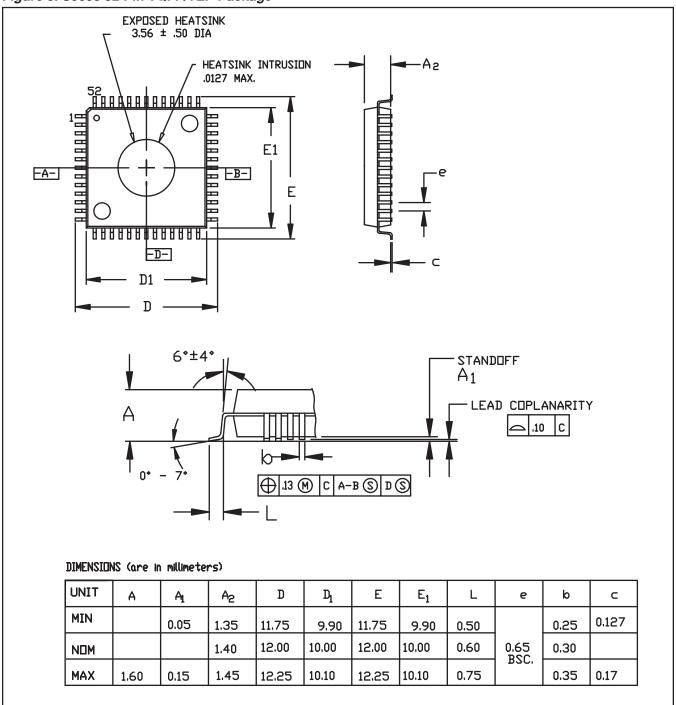

- 52 Pin TQFP/TEP

#### **GENERAL DESCRIPTION**

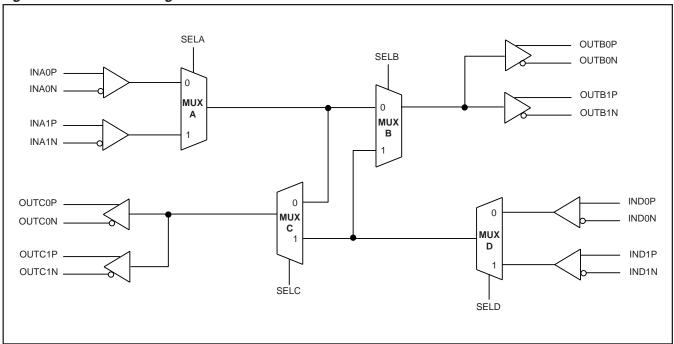

The S3053 is a high performance quad mux with fan out buffers. It is designed to minimize jitter accumulation by providing a high bandwidth fully differential signal path. It can be used to switch OC-48 data signals in Dense Wavelength Division Multiplexer designs and other high speed serial switch designs.

The chip is designed using four 2:1 multiplexers. It can be used to fan out and/or multiplex high speed clock and data signals. The S3053 is compatible with the AMCC OC-48 clock recovery, MUX/DEMUX and Crosspoint Switch products. This allows signal integrity to be maintained throughout the system design.

The primary AC parameter of importance is the deterministic jitter or data eye degradation inserted by the crosspoint. The design minimizes jitter accumulation by using high bandwidth, low skew fully differential circuits. This provides for symmetric rise and fall delays as well as noise rejection.

Figure 1. S3053 Block Diagram

Table 1. Truth Table

| SELA | SELB | SELC | SELD | OUTB | OUTC |

|------|------|------|------|------|------|

| 0    | 0    | 0    | 0    | INA0 | INA0 |

| 0    | 0    | 0    | 1    | INA0 | INA0 |

| 0    | 0    | 1    | 0    | INA0 | IND0 |

| 0    | 0    | 1    | 1    | INA0 | IND1 |

| 0    | 1    | 0    | 0    | IND0 | INA0 |

| 0    | 1    | 0    | 1    | IND1 | INA0 |

| 0    | 1    | 1    | 0    | IND0 | IND0 |

| 0    | 1    | 1    | 1    | IND1 | IND1 |

| 1    | 0    | 0    | 0    | INA1 | INA1 |

| 1    | 0    | 0    | 1    | INA1 | INA1 |

| 1    | 0    | 1    | 0    | INA1 | IND0 |

| 1    | 0    | 1    | 1    | INA1 | IND1 |

| 1    | 1    | 0    | 0    | IND0 | INA1 |

| 1    | 1    | 0    | 1    | IND1 | INA1 |

| 1    | 1    | 1    | 0    | IND0 | IND0 |

| 1    | 1    | 1    | 1    | IND1 | IND1 |

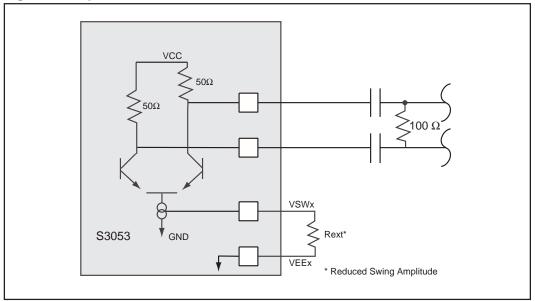

#### **Programable Swing Control**

An external resistor can be connected across adjacent pins, VSWx to VEEx, where x is B0, B1, C0 and C1. This will result in a decreased Vswing for the specified output and a decrease in chip power dissipation. For example, if a 700 Ohm resistor is used, the Vswing will decrease from its full scale swing of approximately 570mV to 250mV and that specific output will draw approximately 13mA less. All four outputs can be independently set. If no external resistor is used, the output swing will default to its full scale value. See Figure 7.

The 700 Ohm value is only used as an example. The power concious user could use as small a resistor value as the application can handle.

INA0,1 IND0,1 OUTB0,1 OUTC0,1

Figure 2. Timing Waveforms

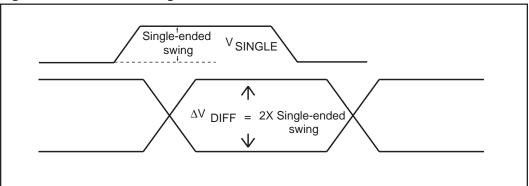

Figure 3. Differential Voltage

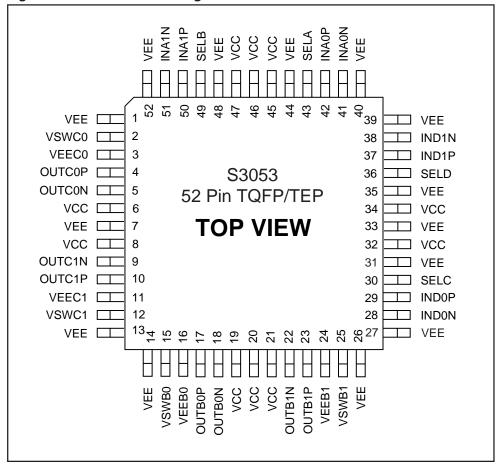

Table 2. Pin Assignment and Descriptions

| Pin Name                             | Level                             | I/O | Pin#                                                                    | Description                                                                  |

|--------------------------------------|-----------------------------------|-----|-------------------------------------------------------------------------|------------------------------------------------------------------------------|

| INAOP<br>INAON<br>INA1P<br>INA1N     | Int.<br>Biased<br>Diff.<br>LVPECL | ı   | 42<br>41<br>50<br>51                                                    | Differential inputs to the multiplexer.                                      |

| IND0P<br>IND0N<br>IND1P<br>IND1N     | Int.<br>Biased<br>Diff.<br>LVPECL | I   | 29<br>28<br>37<br>38                                                    | Differential inputs to the multiplexer.                                      |

| SELA<br>SELD                         | LVTTL                             | I   | 43<br>36                                                                | A Low selects IN0. When High, this signal selects IN1.                       |

| OUTB0P<br>OUTB0N<br>OUTB1P<br>OUTB1N | Diff.<br>CML                      | 0   | 17<br>18<br>23<br>22                                                    | Serial output from Mux B.                                                    |

| OUTC0P<br>OUTC0N<br>OUTC1P<br>OUTC1N | Diff.<br>CML                      | 0   | 4<br>5<br>10<br>9                                                       | Serial output from Mux C.                                                    |

| SELB<br>SELC                         | LVTTL                             | I   | 49<br>30                                                                | A Low selects Mux A output. When High, this signal selects the Mux D output. |

| VCC                                  |                                   |     | 6, 8, 19,<br>20, 21,<br>32, 34,<br>45, 46,<br>47,                       | Power Supply. 3.3V nominal.                                                  |

| VSWB0<br>VSWB1<br>VSWC0<br>VSWC1     | Analog                            | 1   | 15<br>25<br>2<br>12                                                     | Voltage Swing Control pin.                                                   |

| VEE                                  |                                   |     | 1, 7, 13,<br>14, 26,<br>27, 31,<br>33, 35,<br>39, 40,<br>44, 48,<br>52, | Ground.                                                                      |

| VEEB0<br>VEEB1<br>VEEC0<br>VEEC1     | Output<br>GND                     |     | 16<br>24<br>3<br>11                                                     | Ground for B0, B1, C0, C1.                                                   |

Figure 4. S3053 Pinout Package

Figure 5. S3053 52 Pin TQFP/TEP Package

Table 3. Thermal Management

| Device | Power | ⊝ja Still Air | ⊝jc Still Air |

|--------|-------|---------------|---------------|

| S3053  | 1.1W  | 42° C/W       | 2.2° C/W      |

Table 4. AC Characteristics (Over recommended operating conditions.)

| Parameter      | Description                               | Min | Тур | Max | Units | Conditions                           |

|----------------|-------------------------------------------|-----|-----|-----|-------|--------------------------------------|

| T <sub>R</sub> | Serial Data rise time. (OUT0, OUT1).      |     |     | 175 | ps    | 20% to 80% tested on a sample basis. |

| T <sub>F</sub> | Serial Data fall time.<br>(OUT0, OUT1).   |     |     | 150 | ps    | (100Ω line-to-line.)                 |

| T1             | Flow through propagation delay IN to OUT. |     |     | 2.0 | ns    | 100 $\Omega$ load line-to-line.      |

| $R_J$          | Random jitter                             |     | 2   | 4   | ps    |                                      |

| D <sub>J</sub> | Deterministic jitter                      |     | 20  |     | ps    |                                      |

#### Table 5. LVTTL Input DC Characteristics (Over recommended operating conditions.)

| Parameter            | Description                  | Min  | Тур | Max | Units | Conditions             |

|----------------------|------------------------------|------|-----|-----|-------|------------------------|

| V <sub>IH(ITL)</sub> | Input HIGH voltage (SEL-TTL) | 2.0  |     | VCC | V     |                        |

| V <sub>IL(ITL)</sub> | Input LOW voltage (SEL-TTL)  | 0    |     | 0.8 | V     |                        |

| I <sub>IH(ITL)</sub> | Input HIGH current (SEL-TTL) |      |     | 50  | μA    | V <sub>IN</sub> = 2.4V |

| I <sub>IL(ITL)</sub> | Input LOW current (SEL-TTL)  | -500 |     | -50 | μΑ    | V <sub>IN</sub> = 0.5V |

#### Table 6. CML Output DC Characteristics

| Parameter                    | Description                                      | Min          | Тур | Max          | Units | Conditions                                              |

|------------------------------|--------------------------------------------------|--------------|-----|--------------|-------|---------------------------------------------------------|

| V <sub>OL</sub>              | CML Output LOW Voltage                           | Vcc<br>-1.0  |     | Vcc<br>-0.55 | V     | 100 $\Omega$ line-to-line.                              |

| V <sub>OH</sub>              | CML Output HIGH Voltage                          | Vcc<br>-0.35 |     | Vcc<br>-0.10 | V     | 100 $\Omega$ line-to-line.                              |

| $\Delta V_{	ext{OUTDIFF}}$   | CML Serial Output Differential Voltage Swing     | 900          |     | 1460         | mV    | 100 $\Omega$ line-to-line. See Figure 3. Rext = open.   |

| $\Delta V_{	ext{OUTSINGLE}}$ | CML Serial Output Single-<br>ended Voltage Swing | 450          |     | 730          | mV    | 100 $\Omega$ line-to-line. See Figure 3. Rext =ch open. |

#### Table 7. Internally Biased LVPECL Input DC Characteristics

| Parameters                   | Description                              | Min | Тур | Max  | Units | Conditions    |

|------------------------------|------------------------------------------|-----|-----|------|-------|---------------|

| $\Delta V_{INDIFF}$          | Min. Differential Input Voltage<br>Swing | 300 |     | 1200 | mV    | See Figure 3. |

| $\Delta V_{\text{INSINGLE}}$ | Min. Single-ended Input<br>Voltage Swing | 150 |     | 600  | mV    | See Figure 3. |

| R <sub>DIFF</sub>            | Differential Input Resistance            | 80  | 100 | 120  | Ω     |               |

Table 8. Absolute Maximum Ratings1

| Parameter                                     | Min  | Тур | Max                  | Units |

|-----------------------------------------------|------|-----|----------------------|-------|

| Power Supply Voltage (V <sub>CC</sub> )       | -0.5 |     | +4                   | V     |

| PECL DC Input Voltage (V <sub>INP</sub> )     | -0.5 |     | V <sub>CC</sub> +0.5 | V     |

| TTL DC Input Voltage (V <sub>INP</sub> )      | -0.5 |     | V <sub>CC</sub> +0.5 | V     |

| Case Temperature Under Bias (T <sub>C</sub> ) | -55  |     | 125                  | C°    |

| Junction Temperature Under Bias               | -55  |     | 150                  | C°    |

| Storage Temperature (T <sub>STG</sub> )       | -65  |     | 150                  | C°    |

| Static Discharge Voltage                      |      | 500 |                      | V     |

<sup>1.</sup> CAUTION: Stresses listed under "Absolute Maximum Ratings" may be applied to devices one at a time without causing permanent damage. Functionality at or above the values listed is not implied. Exposure to these values for extended periods may affect device reliability.

Table 9. Recommended Operating Conditions 1

| Parameter                          | Min       | Тур | Max  | Units |

|------------------------------------|-----------|-----|------|-------|

| Ambient Temperature Under Bias     | -40       |     | 85   | °C    |

| Junction Temperature Under Bias    | -40       |     | +130 | °C    |

| Voltage on VCC with respect to GND | 3.13      | 3.3 | 3.47 | V     |

| Voltage on any LVPECL Input Pin    | Vcc<br>-2 |     | Vcc  | V     |

| ICC Supply Current                 |           | 260 | 330  | mA    |

AMCC guarantees the functional and parametric operation of the part under "Recommended Operating Conditions" (except where specifically noted in the AC and DC Parametric tables).

#### **Input Structures**

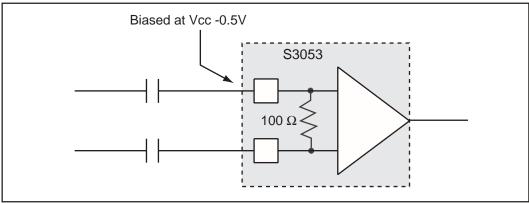

Two input structures exist in this part; TTL and High Speed, Differential Inputs. The LVTTL Inputs will interface with any LVTTL outputs. The High Speed, Differential Inputs can be AC Coupled. Therefore, the High Speed, differential Input buffers are biased at Vcc -0.5V. Refer to Figure 6 for High Speed Differential Input termination.

Figure 6. Input Termination

Figure 7. Output Termination

#### Ordering Information

| Oracining innormation |                      |                                     |                                        |

|-----------------------|----------------------|-------------------------------------|----------------------------------------|

| PREFIX                | DEVICE               | PACKAGE                             | GRADE                                  |

| S- Integrated Circuit | 3053                 | TT – 52 TQFP/TEP                    | (blank) – Commercial<br>I – Industrial |

|                       |                      |                                     |                                        |

|                       | X XXXX Prefix Device | <u>XX</u> <u>X</u><br>Package Grade |                                        |

# Applied Micro Circuits Corporation • 6290 Sequence Dr., San Diego, CA 92121 Phone: (619) 450-9333 • (800) 755-2622 • Fax: (619) 450-9885 http://www.amcc.com

AMCC reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

AMCC does not assume any liability arising out of the application or use of any product or circuit described herein, neither does it convey any license under its patent rights nor the rights of others.

AMCC reserves the right to ship devices of higher grade in place of those of lower grade.

AMCC SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

AMCC is a registered trademark of Applied Micro Circuits Corporation.

Copyright ® 1999 Applied Micro Circuits Corporation