## microelectronics group

## T7698 Quad T1/E1 Line Interface and Octal T1/E1 Monitor

## Features

- Integrated quad T1/E1 line interface and octal T1/ E1 receive frame monitor with HDLC processor provides system QoS capabilities.

- Hardware and software reset options.

- 3-state outputs.

- 0.35 µm, low-power CMOS technology.

- Compliant with:

AT&T

CB119 (10/79)

#### Bellcore

TR-54016 (89) TR-TSY-000170 (10/97) TR-TSY-000009 (5/86) GR-499-CORE (12/95) GR-253-CORE (12/95)

#### ANSI

T1.102 (93) T1.231 (93) T1.403 (95)

#### ITU-T

G.703 (88) G.704 (91) G.706 (91) G.732 (88) G.735-9 (88) G.775 (11/94) G.823-4 (3/93) G.826 (11/93) I.431 (3/93)

#### ETSI

TBR 12 (12/93) TBR 13 (1/96)

- -40 °C to +85 °C operating temperature range.

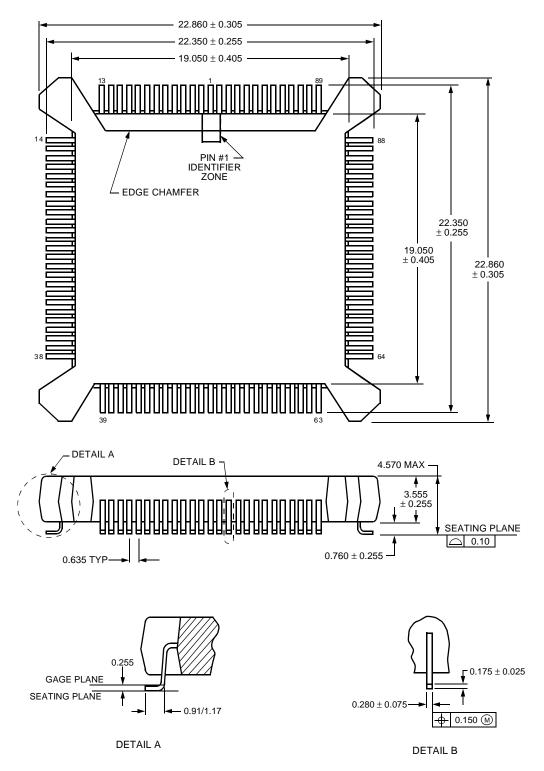

- Fine-pitch (25 mil spacing) surface-mount package, 100-pin BQFP.

#### T1/E1 Line Interface Features

Transmitter includes transmit encoder (B8ZS or HDB3), pulse shaping, and line driver.

- Compatible with the Lucent Technologies Microelectronics Group T7690 line interface.

- Five pulse equalization settings for template compliance at DSX cross connect.

- Receive includes equalization, digital clock and data recovery (immune to false lock), and receive decoder (B8ZS or HDB3).

- CEPT/E1 interference immunity as required by G.703.

- Transmit jitter <0.02 UI.

- Receive generated jitter <0.05 UI.

- Jitter attenuator selectable for use in transmit or receive path. Jitter attenuation characteristics are data pattern independent.

- For use with 100 Ω DS1 twisted-pair, 120 Ω E1 twisted-pair, and 75 Ω E1 coaxial cable.

- Common transformer for transmit/receive.

- Analog LOS alarm for signals less than –18 dB for greater than 1 ms or 10 bit symbol periods to 255 bit symbol periods (selectable).

- Digital LOS alarm for 100 zeros (DS1) or 255 zeros (CEPT).

- Diagnostic loopback modes.

- Ultralow power consumption.

#### T1/E1 Frame Monitor Features

- Framing formats

- DS1 extended superframe (ESF)

- DS1 superframe (SF): D4 (domestic, Japanese);

*SLC*<sup>®</sup>-96; T1DM DDS with FDL access

- Compliant to ITU-CEPT framing recommendation:

- 1. CEPT basic frame format

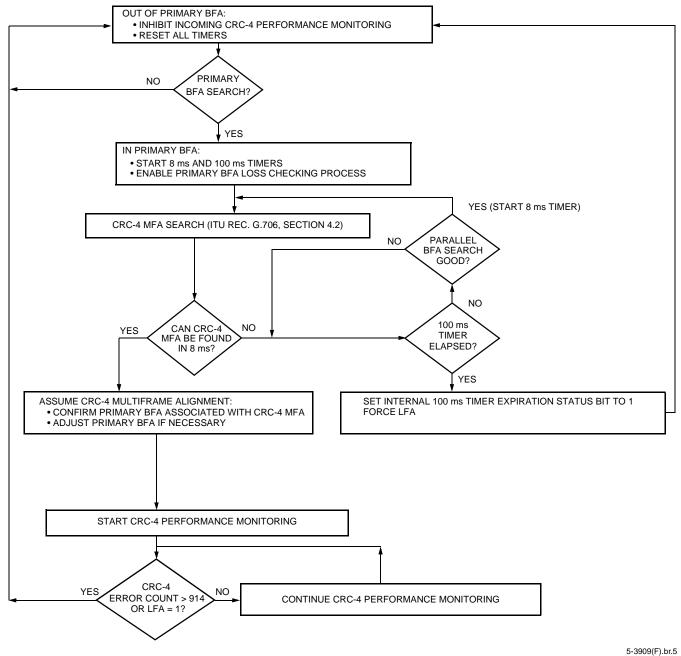

- 2. CEPT with CRC-4 multiframe search algorithm and 100 ms timer

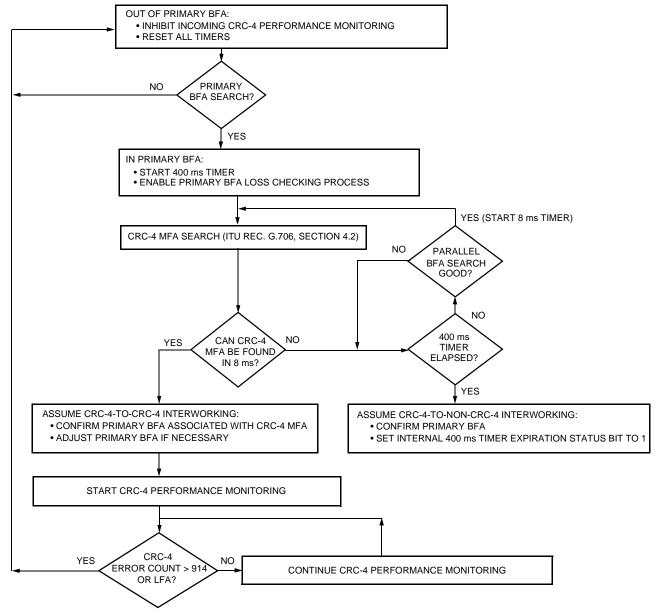

- CEPT with CRC-4 multiframe search algorithm and 400 ms timer for interworking of CRC-4 and non-CRC-4 equipment

- CEPT with loss of frame condition upon detection of ≥915 CRC-4 submultiframe errors out of 1000 CRC-4 submultiframe checks

Page

## **Table of Contents**

#### Contents

| Features                                                               | 1  |

|------------------------------------------------------------------------|----|

| T1/E1 Line Interface Features                                          | 1  |

| T1/E1 Frame Monitor Features                                           | 1  |

| Facility Data Link Features                                            | 8  |

| User-Programmable Microprocessor Interface                             | 8  |

| Applications                                                           | 8  |

| Description                                                            | 8  |

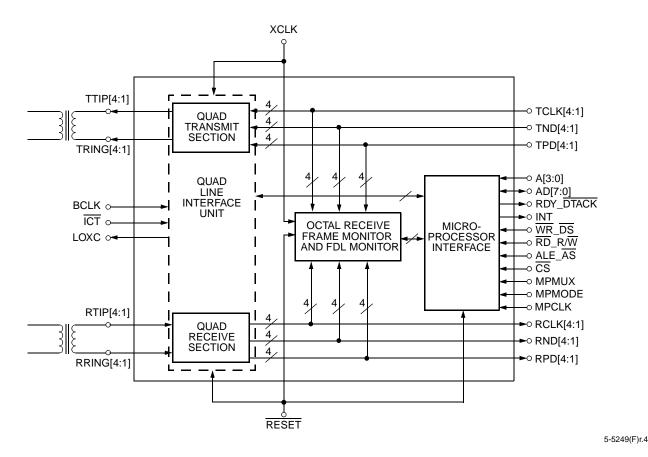

| Block Diagram                                                          | 9  |

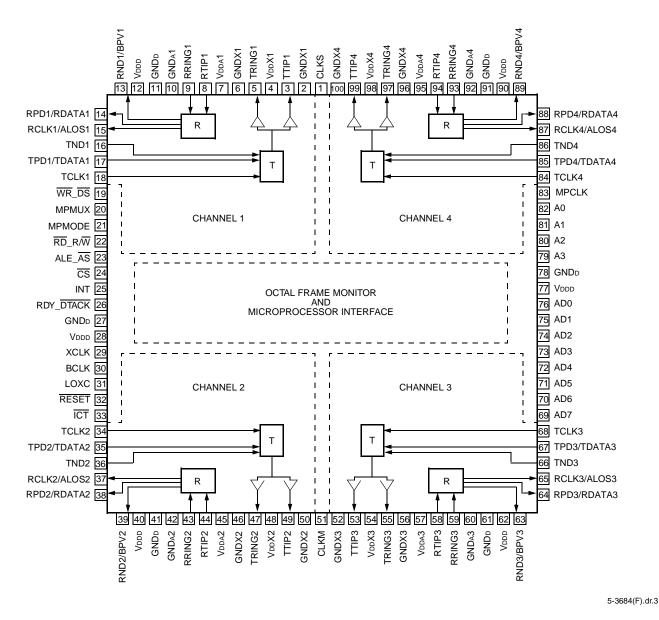

| Pin Information                                                        | 10 |

| T7698 Device Overview                                                  | 15 |

| System Interface Pin Options                                           |    |

| Microprocessor Interface                                               | 16 |

| Overview                                                               | 16 |

| Microprocessor Configuration Modes                                     | 16 |

| Microprocessor Interface Pinout Definitions                            | 17 |

| Microprocessor Clock (MPCLK) Specifications                            | 18 |

| Internal Chip Select Function                                          | 18 |

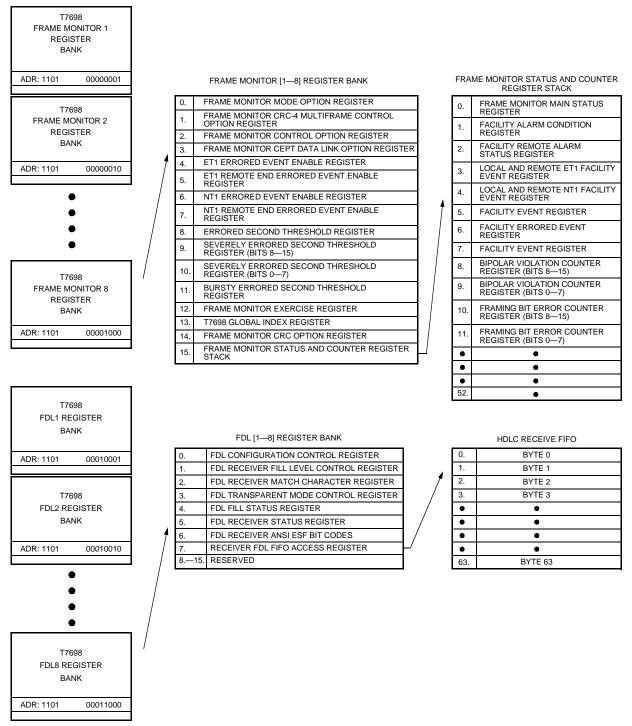

| Microprocessor Interface Register Architecture                         | 19 |

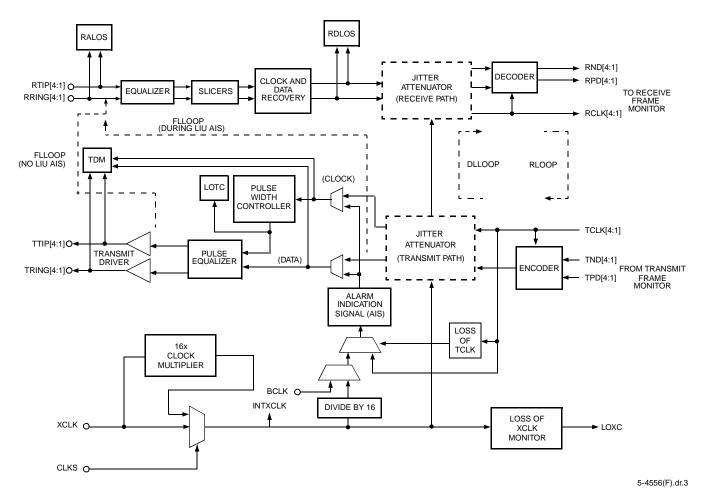

| Line Interface Units                                                   | 22 |

| Line Interface Units: Receive                                          | 23 |

| Data Recovery                                                          |    |

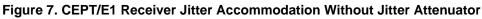

| Jitter Accommodation and Jitter Transfer Without the Jitter Attenuator | 23 |

| Receiver Configuration Modes                                           | 23 |

| Receive Line Interface Configuration Modes                             | 24 |

| DS1 Receiver Specifications                                            | 26 |

| CEPT Receiver Specifications                                           |    |

| Line Interface Units: Transmit                                         | 30 |

| Output Pulse Generation                                                | 30 |

| Jitter                                                                 | 30 |

| Transmitter Configuration Modes                                        |    |

| Transmitter Alarms                                                     |    |

| DS1 Transmitter Pulse Template and Specifications                      |    |

| CEPT Transmitter Pulse Template and Specifications                     |    |

| Line Interface Units: Jitter Attenuator                                |    |

| Generated (Intrinsic) Jitter                                           |    |

| Jitter Transfer Function                                               | 35 |

| Jitter Accommodation                                                   |    |

| Jitter Attenuator Enable                                               |    |

| Line Interface Units: Loopbacks                                        |    |

| Full Local Loopback (FLLOOP)                                           |    |

| Remote Loopback (RLOOP)                                                |    |

| Digital Local Loopback (DLLOOP)                                        |    |

| Line Interface Units: Other Features                                   |    |

| Powerdo <u>wn (P</u> WRDN)                                             |    |

| RESET (RESET, SWRESET)                                                 |    |

| Loss of XCLK Reference Clock (LOXC)                                    |    |

| In-Circuit Testing and Driver High-Impedance State (ICT)               |    |

| LIU Delay Values                                                       |    |

| Line Interface Units: Line Encoding/Decoding                           |    |

| Alternate Mark Inversion (AMI)                                         |    |

| T1-Binary 8 Zero Code Suppression                                      |    |

| High-Density Bipolar of Order 3 (HDB3)                                 | 42 |

## Table of Contents (continued)

## Contents

| Line Interface Units: Quad Line Interface Unit Registers                        |     |

|---------------------------------------------------------------------------------|-----|

| Alarm Registers (0000, 0001)                                                    |     |

| Alarm Mask Registers (0010, 0011)                                               |     |

| Global Control Registers (0100, 0101)                                           |     |

| Channel Configuration and Control Registers (0110-1001, 1011, 1100)             |     |

| Global Index Register (1101)                                                    |     |

| Frame Monitors                                                                  |     |

| Frame Formats                                                                   |     |

| Alarms and Performance Monitoring                                               |     |

| Frame Monitor Register Structure                                                |     |

| Frame Monitor Parameter/Control Registers                                       |     |

| Frame Monitor Status/Counter Registers                                          |     |

| Facility Data Links                                                             |     |

| FDL Features                                                                    |     |

| Facility Data Link Parameter/Status Registers                                   |     |

| XCLK Reference Clock                                                            |     |

| 16x XCLK Reference Clock                                                        |     |

| Primary Line Rate XCLK Reference Clock and Internal Reference Clock Synthesizer |     |

| Power Supply Bypassing                                                          | 99  |

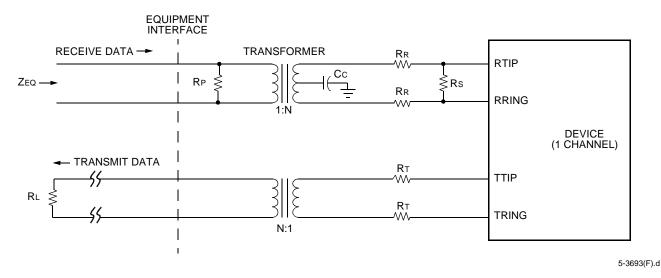

| Line Circuitry                                                                  | 100 |

| Absolute Maximum Ratings                                                        | 101 |

| Handling Precautions                                                            | 101 |

| Operating Conditions                                                            | 101 |

| Power Requirements                                                              | 102 |

| Electrical Characteristics                                                      | 102 |

| Timing Characteristics                                                          | 103 |

| Microprocessor Interface Timing                                                 | 103 |

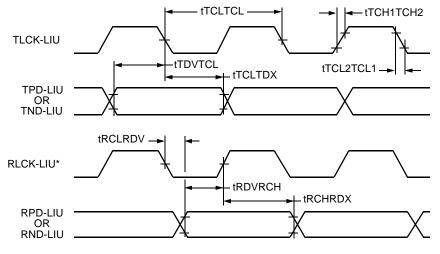

| Data Interface Timing                                                           | 109 |

| Outline Diagram                                                                 | 110 |

| 100-Pin BQFP                                                                    | 110 |

| Ordering Information                                                            | 111 |

| DS98-297T1E1 Replaces DS98-228TIC to Incorporate the Following Updates          | 111 |

Page

Page

## List of Figures

## Figures

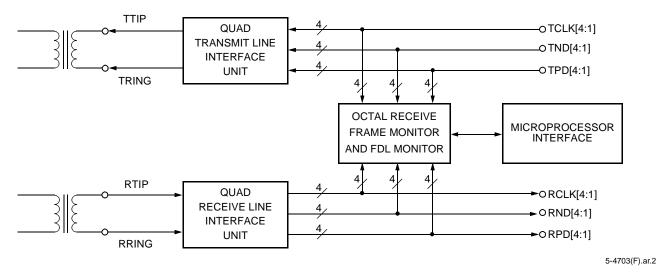

| Figure 1. T7698 Block Diagram                                                                          | 9   |

|--------------------------------------------------------------------------------------------------------|-----|

| Figure 2. T7698 Pin Diagram                                                                            | 10  |

| Figure 3. T7698's Secondary Register Bank Architecture                                                 | 20  |

| Figure 4. Block Diagram of the Quad Line Interface Unit (Single Channel)                               | 22  |

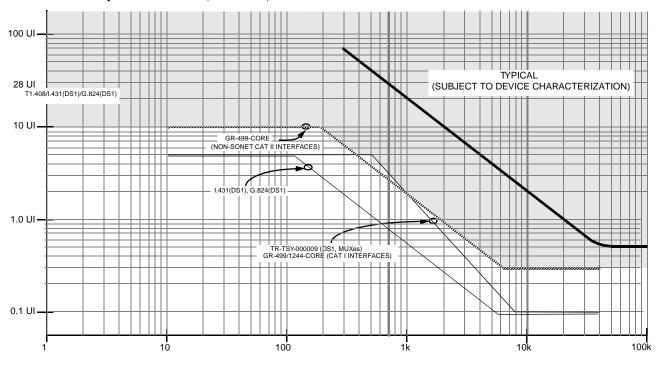

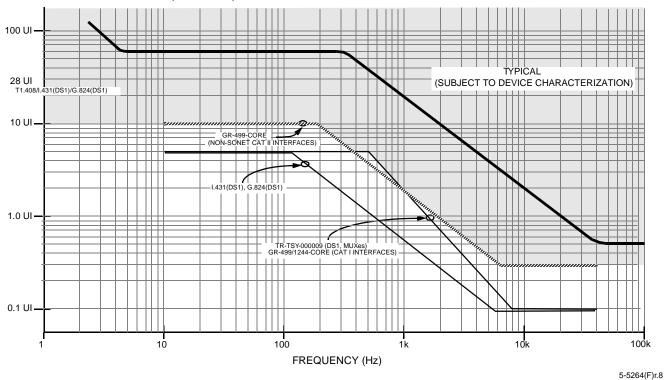

| Figure 5. DS1/T1 Receiver Jitter Accommodation Without Jitter Attenuator                               |     |

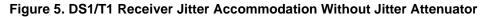

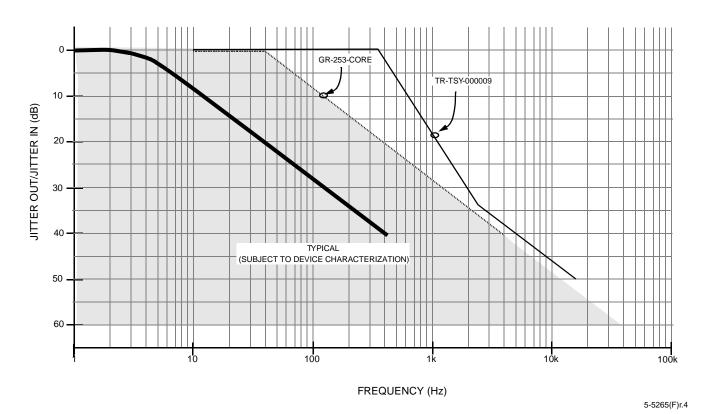

| Figure 6. DS1/T1 Receiver Jitter Transfer Without Jitter Attenuator                                    |     |

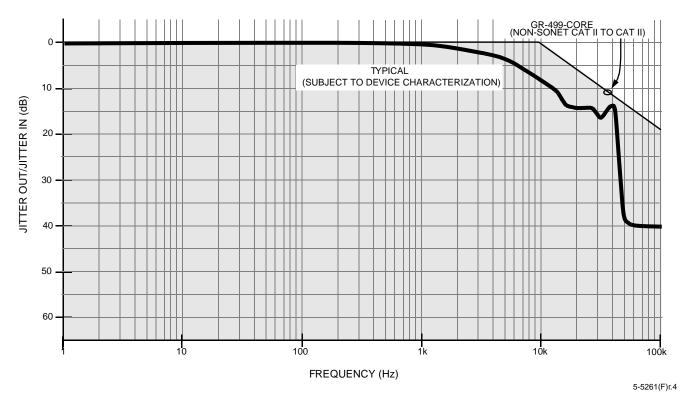

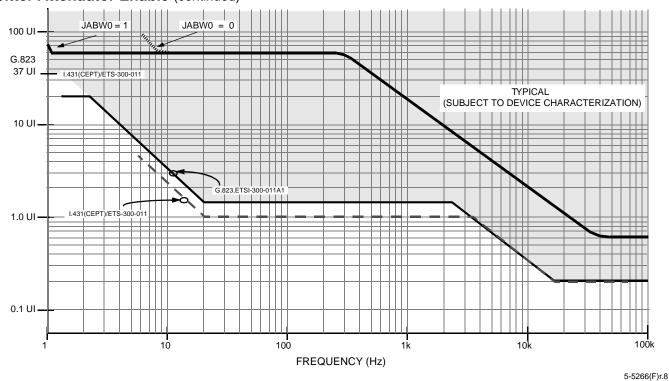

| Figure 7. CEPT/E1 Receiver Jitter Accommodation Without Jitter Attenuator                              | 29  |

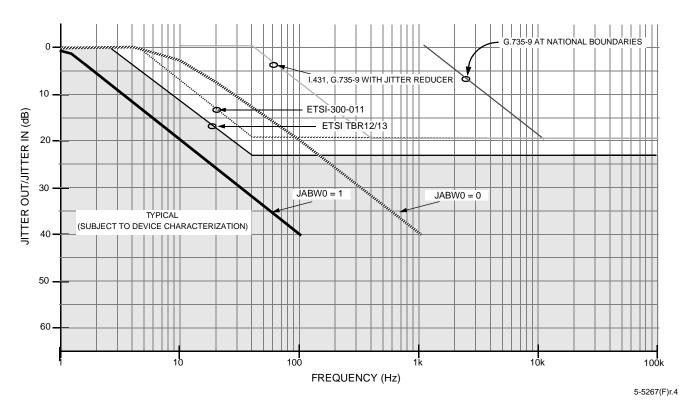

| Figure 8. CEPT/E1 Receiver Jitter Transfer Without Jitter Attenuator                                   |     |

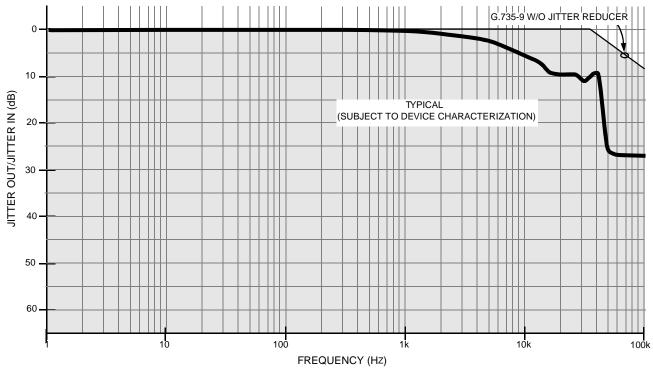

| Figure 9. DSX-1 Isolated Pulse Template                                                                | 32  |

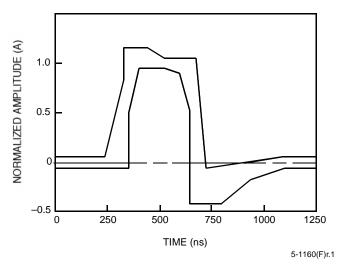

| Figure 10. ITU-T G.703 Pulse Template                                                                  | 33  |

| Figure 11. DS1/T1 Receiver Jitter Accommodation with Jitter Attenuator                                 | 37  |

| Figure 12. DS1/T1 Jitter Transfer of the Jitter Attenuator                                             | 37  |

| Figure 13. CEPT/E1 Receiver Jitter Accommodation with Jitter Attenuator                                |     |

| Figure 14. CEPT/E1 Jitter Transfer of the Jitter Attenuator                                            | 38  |

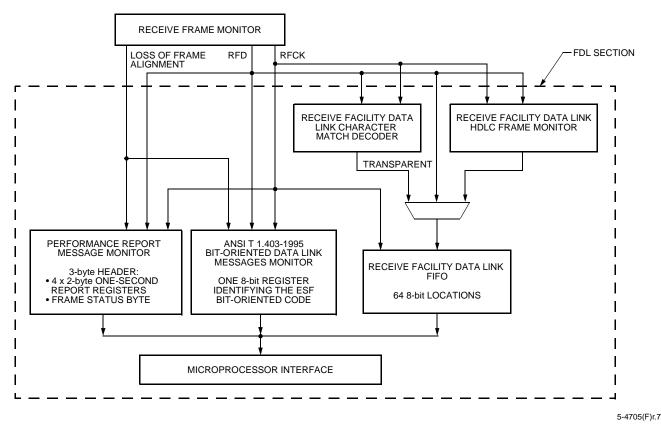

| Figure 15. Block Diagram of the Receive Frame Monitor Section                                          |     |

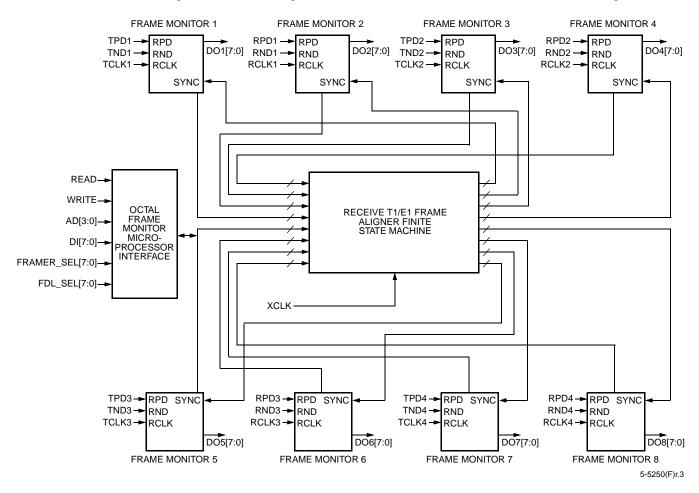

| Figure 16. Block Diagram of the Octal Receive Frame Monitor                                            | 49  |

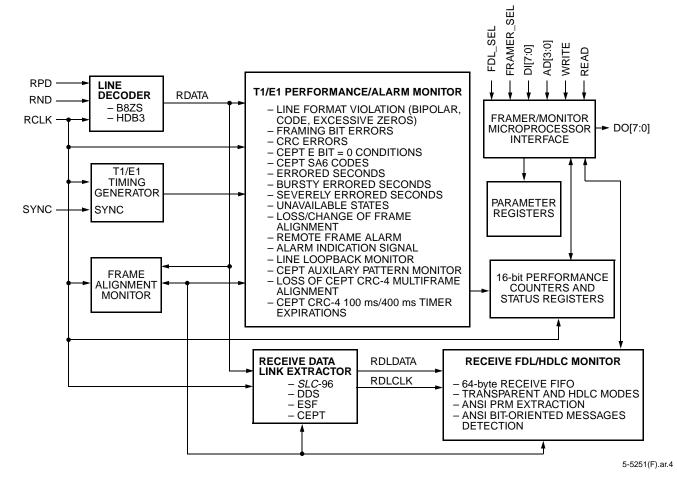

| Figure 17. Block Diagram of the Frame Monitor                                                          |     |

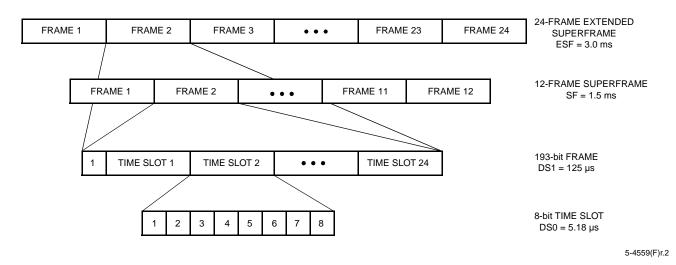

| Figure 18. T1 Frame Structure                                                                          | 51  |

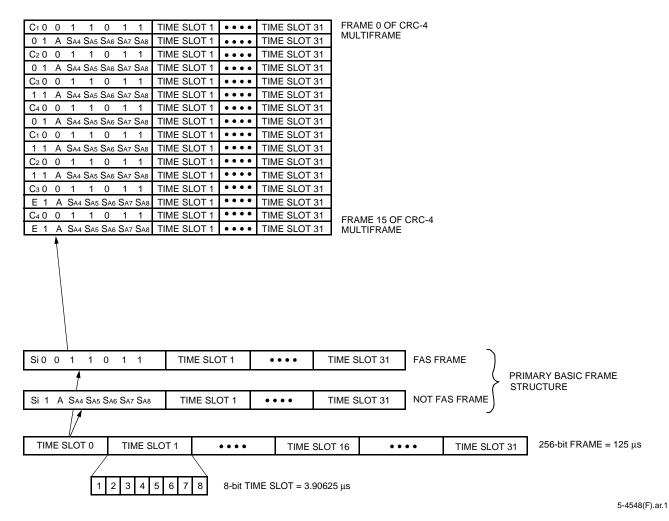

| Figure 19. ITU 2.048 Mbits/s Basic Frame and CRC-4 Multiframe Structures                               | 57  |

| Figure 20. T7698 Receive CRC-4 Multiframe Search Algorithm Using the 100 ms Internal Timer             | 63  |

| Figure 21. CEPT Loss of CRC-4 Multiframe Alignment Recovery Algorithms: T7698 Receive CRC-4 Multiframe | Э   |

| Search Algorithm for Automatic, CRC-4/Non-CRC-4 Equipment Interworking as Defined by ITU               |     |

| (from ITU Rec. G.706, Annex B.2.2 - 1991)                                                              | 65  |

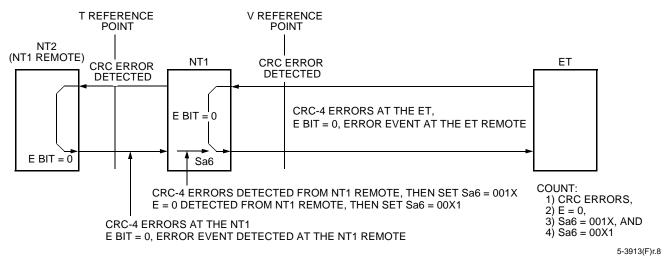

| Figure 22. The T and V Reference Points for a Typical CEPT E1 Application                              | 69  |

| Figure 23. Block Diagram of the Receive Facility Data Link                                             | 90  |

| Figure 24. Line Termination Circuitry                                                                  |     |

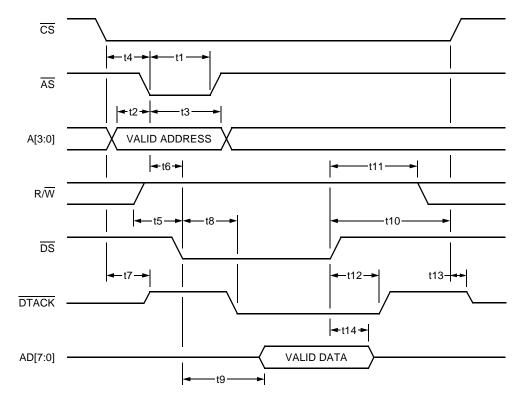

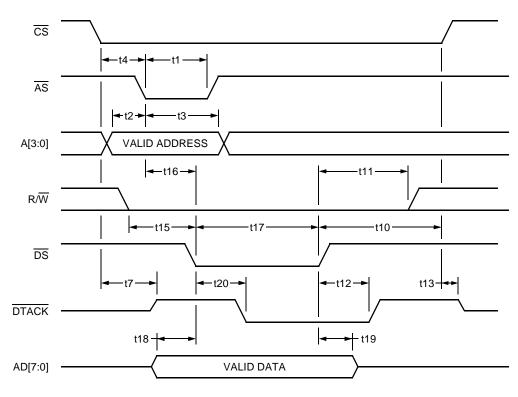

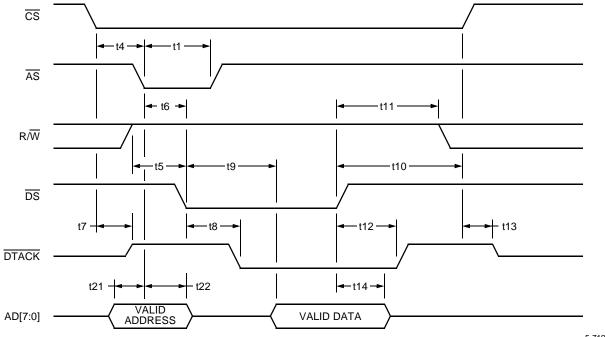

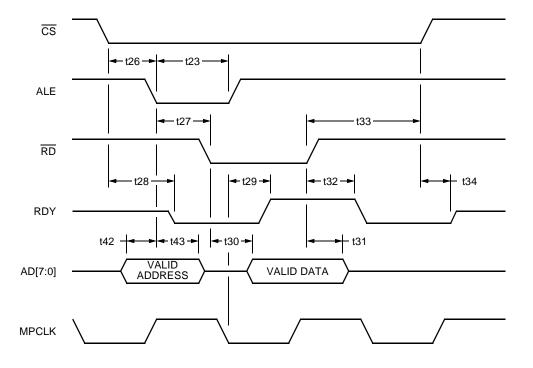

| Figure 25. Mode 1—Read Cycle Timing (MPMODE = 0, MPMUX = 0)                                            |     |

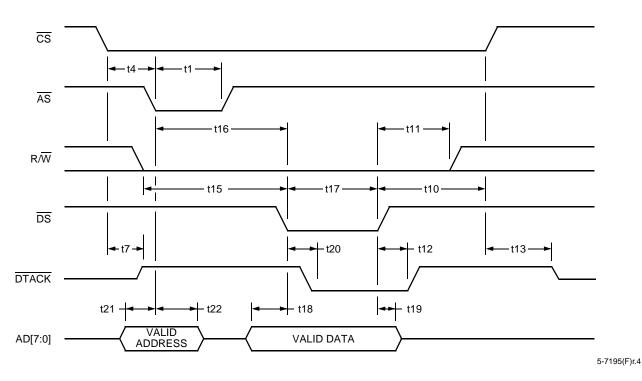

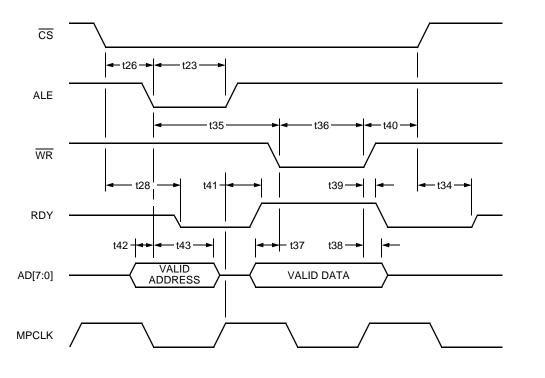

| Figure 26. Mode 1—Write Cycle Timing (MPMODE = 0, MPMUX = 0)                                           | 105 |

| Figure 27. Mode 2—Read Cycle Timing (MPMODE = 0, MPMUX = 1)                                            |     |

| Figure 28. Mode 2—Write Cycle Timing (MPMODE = 0, MPMUX = 1)                                           | 106 |

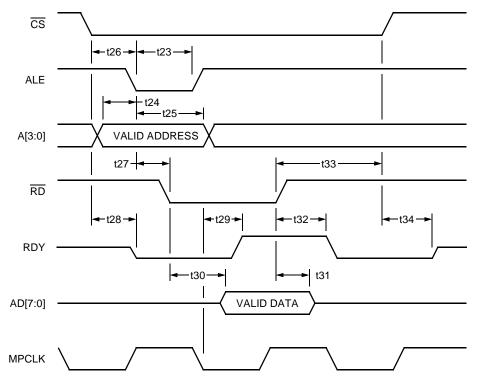

| Figure 29. Mode 3—Read Cycle Timing (MPMODE = 1, MPMUX = 0)                                            | 107 |

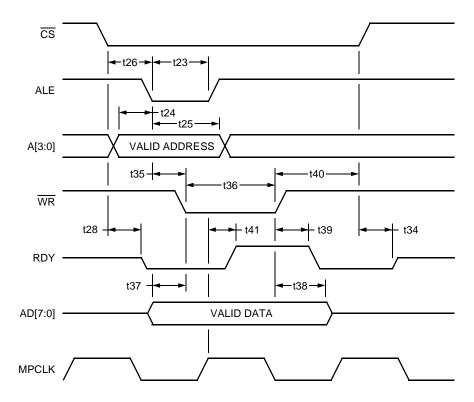

| Figure 30. Mode 3—Write Cycle Timing (MPMODE = 1, MPMUX = 0)                                           | 107 |

| Figure 31. Mode 4—Read Cycle Timing (MPMODE = 1, MPMUX = 1)                                            |     |

| Figure 32. Mode 4—Write Cycle Timing (MPMODE = 1, MPMUX = 1)                                           | 108 |

| Figure 33. Interface Data Timing (ACM = 0)                                                             | 109 |

|                                                                                                        |     |

## List of Tables

#### **Tables**

| Table 1. Pin Descriptions                                                                      | 11 |

|------------------------------------------------------------------------------------------------|----|

| Table 2. System Interface Pin Mapping                                                          | 15 |

| Table 3. Microprocessor Configuration Modes                                                    | 16 |

| Table 4. MODE [1—4] Microprocessor Pin Definitions                                             | 17 |

| Table 5. Microprocessor Input Clock Specifications                                             |    |

| Table 6. Primary (LIU) Register Bank                                                           |    |

| Table 7. Register Map for CODE Bits                                                            |    |

| Table 8. Digital Loss of Signal Standard Select                                                |    |

| Table 9. LOSSD and RCVAIS Control Configurations (Not Valid During Loopback Modes)             | 25 |

| Table 10. DS1 RLIU Specifications                                                              |    |

| Table 11. CEPT RLIU Specifications                                                             | 28 |

| Table 12. Equalizer/Rate Control                                                               |    |

| Table 13. Register Map for CODE Bits                                                           |    |

| Table 14. DSX-1 Pulse Template Corner Points (from CB119)                                      |    |

| Table 15. DS1 Transmitter Specifications                                                       |    |

| Table 16. CEPT Transmitter Specifications                                                      |    |

| Table 17. Loopback Control                                                                     |    |

| Table 18. AMI Encoding                                                                         |    |

| Table 19. DS1 B8ZS Encoding                                                                    |    |

| Table 20. ITU HDB3 Coding and DCPAT Binary Coding                                              |    |

| Table 21. Alarm Registers                                                                      |    |

| Table 22. Alarm Mask Registers                                                                 |    |

| Table 23. Global Control Register (0100)                                                       |    |

| Table 24. Global Control Register (0101)                                                       |    |

| Table 25. Channel Configuration Registers (0110—1001)                                          |    |

| Table 26. Channel Configuration Register (1011)                                                |    |

| Table 27. Control Register (1100)                                                              |    |

| Table 28. Global Index Register                                                                |    |

| Table 29. T-Carrier Hierarchy                                                                  |    |

| Table 30. D4 Superframe Format                                                                 |    |

| Table 31. DDS Channel 24 Format                                                                |    |

| Table 32. Extended Superframe (ESF) Structure                                                  | 54 |

| Table 33. T1 Loss of Frame Alignment Criteria                                                  |    |

| Table 34. T1 Frame Alignment Procedures                                                        |    |

| Table 35. Allocation of Bits 1 to 8 of the FAS Frame and the NOT FAS Frame                     |    |

| Table 36. ITU CRC-4 Multiframe Structure of the T7698                                          | 60 |

| Table 37. Red Alarm Conditions                                                                 | 66 |

| Table 38. Remote Frame Alarm Conditions                                                        | 66 |

| Table 39. Alarm Indication Signal Conditions                                                   |    |

| Table 40. Sa6 Bit Coding Recognized by the T7698 Receive Frame Monitor                         |    |

| Table 41. Sa6 Bit Coding of NT1 Interface Events Recognized by the T7698 Receive Frame Monitor |    |

| Table 42. AUXP Synchronization and Clear Synchronization Process                               |    |

| Table 43. T7698 Event Counters Definition                                                      |    |

| Table 44. T7698 Errored Second Counters Definition                                             | 71 |

| Table 45. T7698 Bursty Errored Second Counters Definition                                      | 72 |

| Table 46. T7698 Severely Errored Second Counters Definition                                    |    |

| Table 47. T7698 Unavailable Second Counter Definition                                          |    |

| Table 48. Frame Monitor Registers                                                              |    |

| Table 49. Framer_PR0 Frame Monitor Mode Bits Decoding                                          |    |

| Table 50. Framer_PR0 Line Code Option Bits Decoding                                            |    |

| Table 51. CEPT CRC-4 Option Bits Decoding                                                      |    |

| Table 52. Frame Monitor Control Option Register (Framer_PR2)                                   |    |

| Table 53. Frame Monitor CEPT Data Link Option Register (Framer_PR3)                            |    |

Page

Page

## List of Tables (continued)

## Tables

| Table 55.       FTI Errored Event Enable Register (Framer_PR5)       76         Table 55.       FTI Errored Event Enable Register (Framer_PR6)       76         Table 56.       NT1 Errored Event Enable Register (Framer_PR7)       76         Table 55.       ETI Remote Ende Register (Framer_PR8)       77         Table 64.       Errored Second Threshold Register (Framer_PR10)       77         Table 65.       ETI Remote Motio Exercise Register (Framer_PR12)       77         Table 64.       Frame Monitor Exercise Register (Framer_PR14)       79         Table 65.       Frame Monitor Exercise Register (Framer_SR1)       79         Table 64.       Frame Monitor Stus/Courter Register (Framer_SR1)       80         Table 64.       Frame Monitor Stus/Courter Register (Framer_SR2)       81         Table 64.       Frame Monitor Stus/Register (Framer_SR2)       81         Table 65.       Frame Monitor Stus/Register (Framer_SR1)       80         Table 64.       Coal and Remote Network Termination-1 Facility Event Register (Framer_SR3)       82         Table 65.       Framing Bit Frow Counter Register (Framer_SR4)       83         Table 71.       Facility Veunt Register (Framer_SR4)       84         Table 72.       Facility Veunt Register (Framer_SR4)       84         Table 73.       Facility Veunt                                                                                                                                                                                                                         |                                                                           | - |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|---|

| Table 56. NT1 Errored Event Enable Register (Framer_PR6)       76         Table 57. NT1 Remote End Errored Event Enable Register (Framer_PR7)       76         Table 58. Errored Second Threshold Register (Framer_PR8)       77         Table 50. BES Threshold Register (Framer_PR1)       77         Table 60. BES Threshold Register (Framer_PR12)       77         Table 61. Frame Monitor Exercise Register (Framer_PR12)       77         Table 63. Frame Monitor Exercise Register (Framer_PR12)       77         Table 64. Frame Monitor Study-Counter Register (Framer_SR0)       80         Table 65. Frame Monitor Study-Counter Register (Framer_SR1)       80         Table 64. Facility Alarn Condition Register (Framer_SR1)       80         Table 64. Local and Remote ET Facility Event Register (Framer_SR3)       81         Table 70. Facility Formed Network Termination -1 Facility Event Register (Framer_SR3)       84         Table 70. Facility Event Register (Framer_SR6)       84         Table 71. Facility Event Register (Framer_SR6)       84         Table 72. Facility Out of Unavailable State Register (Framer_SR7)       85         Table 73. CRC4 Error Counter Register (Framer_SR1)       86         Table 74. Framing Bit Error Counter Register (Framer_SR12)       86         Table 75. CRC4 Error Counter Register (Framer_SR12)       86         Table 76. E-Bit Counter Register (Framer                                                                                                                                     |                                                                           |   |

| Table 57. NT1 Remote End Errored Event Enable Register (Framer_PR8)       76         Table 58. Errored Second Threshold Register (Framer_PR1)       77         Table 56. Errored Second Threshold Register (Framer_PR1)       77         Table 61. Errame Monitor Exercise Register (Framer_PR12)       77         Table 62. Frame Monitor Exercise Register (Framer_PR12)       77         Table 63. Frame Monitor Exercise Register (Framer_PR14)       79         Table 64. Frame Monitor CRC Option Register (Framer_SR1)       80         Table 65. Frame Monitor Main Status Register (Framer_SR2)       80         Table 64. Frame Monitor Status/Counter Register (Framer_SR2)       80         Table 65. Facility Namo Alam Status Register (Framer_SR2)       81         Table 67. Facility Remote Alam Status Register (Framer_SR2)       81         Table 68. Local and Remote Network Termination-1 Facility Event Register (Framer_SR3)       82         Table 70. Facility Event Register (Framer_SR6)       84         Table 71. Facility Event Register (Framer_SR4)       83         Table 73. Bipolar Violation Counter Register (Framer_SR1)       85         Table 74. Framing Bit Error Counter Register (Framer_SR1)       85         Table 75. E-Bit Counter Register (Framer SR10-Framer_SR1)       86         Table 76. E-Bit Counter Register (Framer SR14-Framer_SR1)       86         Table 76. E-Bit Counte                                                                                                                                     |                                                                           |   |

| Table 58. Est S Threshold Register (Framer PR0)       77         Table 50. SES Threshold Register (Framer PR1)       77         Table 60. BES Threshold Register (Framer PR1)       77         Table 61. Frame Monitor Exercise Register (Framer PR12) Bits 5–0       78         Table 62. Frame Monitor Exercise Register (Framer PR12) Bits 5–0       78         Table 63. Frame Monitor Exercise Register (Framer PR12) Bits 5–0       79         Table 64. Frame Monitor Main Status Register (Framer SR1)       80         Table 65. Frame Monitor Main Status Register (Framer SR1)       80         Table 64. Local and Remote ET Facility Event Register (Framer_SR3)       82         Table 64. Local and Remote Network Termination 1–Tacility Event Register (Framer_SR4)       83         Table 70. Facility Event Register (Framer, SR6)       84         Table 71. Facility Event Register (Framer_SR6)       84         Table 72. Facility Cut of Unavailable State Register (Framer_SR7)       85         Table 73. Eipolar Violation Counter Register (Framer_SR10–Framer_SR13)       86         Table 74. Framing Bit Error Counter Register (Framer_SR12–Framer_SR13)       86         Table 75. CRC-4 Errors at NT1 from NT2 Counter Register (Framer_SR2)       87         Table 76. EBI counter Register (Framer_SR2)       87         Table 76. EBI counter Register (Framer SR2)       87         Table 78. EBI C                                                                                                                                     | able 56. NT1 Errored Event Enable Register (Framer_PR6)                   |   |

| Table 59. SES Threshold Register (Framer_PR1)       77         Table 60. BES Threshold Register (Framer_PR12)       77         Table 61. Frame Monitor Exercise Register (Framer PR12) Bits 5–0       78         Table 62. Frame Monitor Exercise Register (Framer PR12) Bits 5–0       78         Table 64. Frame Monitor CRC Option Register (Framer PR14)       79         Table 65. Frame Monitor Main Status Register (Framer SR1)       80         Table 66. Facility Alarm Condition Register (Framer SR2)       81         Table 66. Facility Marm Condition Register (Framer SR2)       81         Table 66. Facility Marm Condition Register (Framer SR2)       81         Table 61. Local and Remote T Facility Event Register (Framer SR3)       82         Table 70. Facility Event Register (Framer SR6)       84         Table 71. Facility Event Register (Framer SR6)       84         Table 72. Facility Out of Unavailable State Register (Framer SR4)       83         Table 73. Epolar Violation Counter Register (Framer SR4)       85         Table 74. Framing Bit Error Counter Register (Framer SR4)       84         Table 75. Epolar Violation Counter Register (Framer SR4)       85         Table 74. Framing Bit Error Counter Register (Framer SR4)       85         Table 75. Ebit Counter Register (Framer SR4)       86         Table 76. E-Bit Counter Register (Framer SR4)       86                                                                                                                                                     | able 57. N11 Remote End Errored Event Enable Register (Framer_PR7)        |   |

| Table 60. BES Threshold Register (Framer_PR12)       77         Table 61. Frame Monitor Exercise Register (Framer_PR12) Bits 5—0       78         Table 62. Frame Monitor Exercise Register (Framer_PR12) Bits 5—0       78         Table 63. Frame Monitor Exercise Register (Framer_PR14)       79         Table 64. Frame Monitor Main Status Register (Framer_SR1)       80         Table 65. Frame Monitor Main Status Register (Framer_SR1)       80         Table 64. Local and Remote ET Facility Event Register (Framer_SR3)       81         Table 64. Local and Remote ET Facility Event Register (Framer_SR3)       82         Table 70. Facility Event Register (Framer_SR6)       84         Table 71. Facility Event Register (Framer_SR6)       84         Table 72. Facility Event Register (Framer_SR6)       84         Table 74. Facility Event Register (Framer_SR7)       85         Table 75. CRC-4 Error Counter Registers (Framer_SR10—Framer_SR13)       86         Table 76. EBI counter Register (Framer_SR14—Framer_SR13)       86         Table 77. CRC-4 Errors at NT1 from NT2 Counter Register (Framer_SR20—Framer_SR21)       87         Table 80. ET But NT1 from NT2 Counter Register (Framer_SR20—Framer_SR21)       87         Table 81. TRT from NT2 Counter Register (Framer_SR20—Framer_SR21)       87         Table 81. ET Errored Seconds Counter Register (Framer_SR20—Framer_SR21)       87                                                                                                                                      |                                                                           |   |

| Table 61. Frame Monitor Exercise Register (Framer_PR12) Bits 5—0.       77         Table 63. Frame Monitor CRC Option Register (Framer_PR14)       79         Table 64. Frame Monitor CRC Option Register (Framer_SR)       79         Table 65. Frame Monitor Status/Counter Register (Framer_SR)       80         Table 66. Facility Alarm Condition Register (Framer_SR2)       81         Table 66. Facility Alarm Condition Register (Framer_SR3)       82         Table 61. Local and Remote FT Facility Event Register (Framer_SR3)       82         Table 62. Local and Remote Network Termination-1 Facility Event Register (Framer_SR4)       83         Table 70. Facility Event Register (Framer_SR5)       84         Table 71. Facility Event Register (Framer_SR5)       84         Table 72. Facility Out of Unavailable State Register (Framer_SR4)       83         Table 73. Bipdar Violation Counter Registers (Framer_SR10—Framer_SR10)       85         Table 74. Framing Bit Error Counter Registers (Framer_SR10—Framer_SR11)       85         Table 75. ERC4 2 Error Counter Registers (Framer_SR10—Framer_SR13)       86         Table 76. E-Bit Counter Register (Framer_SR14—Framer_SR15)       86         Table 78. E Bit at NT1 from NT2 Counter Register (Framer_SR22—Framer_SR23)       87         Table 78. E Bit at NT1 from NT2 Counter Register (Framer_SR24—Framer_SR25)       87         Table 80. ET Errored Seconds Counter Register                                                                                                  |                                                                           |   |

| Table 62. Frame Monitor Exercise Register (Framer_PR14)       79         Table 63. Frame Monitor Status/Counter Register (Framer_SR)       79         Table 64. Frame Monitor Status/Counter Register (Framer_SR0)       80         Table 65. Frame Monitor Status Register (Framer_SR1)       80         Table 66. Local and Remote ET Facility Event Register (Framer_SR2)       81         Table 61. Local and Remote Network Termination-1 Facility Event Register (Framer_SR3)       82         Table 70. Facility Event Register (Framer_SR5)       84         Table 71. Cacility Event Register (Framer_SR6)       84         Table 72. Facility Out of Unavailable State Register (Framer_SR6)       84         Table 73. Bipolar Violation Counter Registers (Framer_SR1)       85         Table 74. Excitity Out of Unavailable State Register (Framer_SR1)       85         Table 75. CRC-4 Error Counter Registers (Framer_SR15)       86         Table 76. E-Bit Counter Register (Framer_SR14—Framer_SR16)       86         Table 77. CRC-4 Errors at NT1 from NT2 Counter Register (Framer_SR24)       87         Table 78. E Bit at NT1 from NT2 Counter Register (Framer_SR22)       87         Table 78. E Bit at NT1 from NT2 Counter Register (Framer_SR24)       87         Table 78. E Bit at NT1 from NT2 Counter Register (Framer_SR24)       87         Table 78. E Bit at NT1 from NT2 Counter Register (Framer_SR24)       87     <                                                                                                                |                                                                           |   |

| Table 63. Frame Monitor CRC Option Register (Framer_SR)       79         Table 64. Frame Monitor Main Status Register (Framer_SR)       79         Table 65. Frame Monitor Main Status Register (Framer_SR)       80         Table 66. Facility Auarn Condition Register (Framer_SR2)       81         Table 68. Local and Remote ET Facility Event Register (Framer_SR3)       82         Table 60. Local and Remote Network Termination-1 Facility Event Register (Framer_SR4)       83         Table 70. Facility Event Register (Framer_SR6)       84         Table 71. Facility Event Register (Framer_SR6)       84         Table 73. Bipolar Violation Counter Registers (Framer_SR7)       85         Table 74. Framing Bit Error Counter Register (Framer_SR10—Framer_SR10)       85         Table 75. CRC-4 Error Counter Register (Framer_SR10—Framer_SR13)       86         Table 76. E-Bit Counter Register (Framer_SR14—Framer_SR15)       86         Table 77. ERC-4 Error Counter Register (Framer_SR20—Framer_SR19)       86         Table 78. E Bit at N11 from N12 Counter Register (Framer_SR20—Framer_SR20)       87         Table 78. E Bit at N11 from N12 Counter Register (Framer_SR20—Framer_SR20)       87         Table 80. ET Bursty Errored Seconds Counter Register (Framer_SR20—Framer_SR20)       87         Table 81. ET Severely Errored Seconds Counter Register (Framer_SR20—Framer_SR20)       87         Table 82. ET-RE Bursty Error                                                                                                  | able 61. Frame Monitor Exercise Register (Framer_PR12)                    |   |

| Table 64. Frame Monitor Status/Counter Register (Framer_SR)       79         Table 65. Frame Monitor Main Status Register (Framer_SR)       80         Table 66. Facility Alarm Condition Register (Framer_SR1)       80         Table 66. Local and Remote Alarm Status Register (Framer_SR3)       82         Table 67. Facility Remote Alarm Status Register (Framer_SR3)       82         Table 67. Facility Event Register (Framer_SR6)       84         Table 70. Facility Event Register (Framer_SR6)       84         Table 71. Facility Cut of Unavailable State Register (Framer_SR7)       85         Table 72. Facility Out of Unavailable State Register (Framer_SR10—Framer_SR1)       85         Table 74. Framing Bit Eror Counter Register (Framer_SR10—Framer_SR13)       86         Table 75. CRC-4 Eror Counter Register (Framer_SR10—Framer_SR13)       86         Table 76. Ebit Counter Register (Framer_SR14—Framer_SR15)       86         Table 77. CRC-4 Erors at NT1 from NT2 Counter Register (Framer_SR20—Framer_SR21)       87         Table 80. ET Bursty Erored Seconds Counter Register (Framer_SR20—Framer_SR23)       87         Table 81. El Severely Erored Seconds Counter Register (Framer_SR20—Framer_SR23)       87         Table 82. ET Unavailable Seconds Counter Register (Framer_SR20—Framer_SR23)       87         Table 83. ET-RE Erored Seconds Counter Register (Framer_SR20—Framer_SR23)       87         Table 84. ET-RE                                                                                                  | able 62. Frame Monitor Exercise Register (Framer_PR12) Bits 5–0           |   |

| Table 65. Frame Monitor Main Status Register (Framer_SR0)       80         Table 67. Facility Alarm Condition Register (Framer_SR1)       80         Table 68. Local and Remote IT Facility Event Register (Framer_SR2)       81         Table 67. Facility Event Register (Framer_SR2)       83         Table 70. Facility Event Register (Framer_SR5)       84         Table 71. Facility Event Register (Framer_SR6)       84         Table 71. Facility Event Register (Framer_SR6)       84         Table 73. Bipolar Violation Counter Registers (Framer_SR7)       85         Table 74. Framing Bit Error Counter Registers (Framer_SR10—Framer_SR1)       85         Table 76. CRC-4 Error Counter Registers (Framer_SR10—Framer_SR13)       86         Table 76. EBit Counter Registers (Framer_SR10—Framer_SR14)       86         Table 77. CRC-4 Error Counter Registers (Framer_SR10—Framer_SR13)       86         Table 78. E Bit at NT1 from NT2 Counter Registers (Framer_SR20—Framer_SR21)       87         Table 80. ET Bursty Errored Seconds Counter Register (Framer_SR20—Framer_SR23)       87         Table 81. ET Severely Errored Seconds Counter Register (Framer_SR20—Framer_SR31)       87         Table 82. ET Unavailable Seconds Counter Register (Framer_SR20—Framer_SR33)       88         Table 83. ET-RE Errored Seconds Counter Register (Framer_SR30—Framer_SR33)       88         Table 84. ET-RE Bursty Errored Seconds Counter Regist                                                                                                  |                                                                           |   |

| Table 66. Facility Alarm Condition Register (Framer_SR1)       80         Table 67. Facility Remote Alarm Status Register (Framer_SR2)       81         Table 68. Local and Remote ET Facility Event Register (Framer_SR3)       82         Table 69. Local and Remote Network Termination-1 Facility Event Register (Framer_SR4)       83         Table 71. Facility Event Register (Framer_SR5)       84         Table 72. Facility Out of Unavailable State Register (Framer_SR7)       85         Table 73. Bipolar Violation Counter Registers (Framer_SR1-Framer_SR9)       85         Table 74. Framing Bit Error Counter Registers (Framer_SR10—Framer_SR1)       86         Table 75. CRC-4 Error Counter Registers (Framer_SR15)       86         Table 76. E-Bit Counter Register (Framer_SR14—Framer_SR16)       86         Table 76. E-Bit Counter Registers (Framer_SR20—Framer_SR19)       86         Table 76. E-Bit Counter Register (Framer_SR20—Framer_SR19)       86         Table 78. ET Errored Seconds Counter Register (Framer_SR20—Framer_SR21)       87         Table 79. ET Eurored Seconds Counter Register (Framer_SR20—Framer_SR23)       87         Table 80. ET Bursty Errored Seconds Counter Register (Framer_SR20—Framer_SR23)       87         Table 81. ET-RE Eurored Seconds Counter Register (Framer_SR20—Framer_SR23)       87         Table 82. ET Unavailable Seconds Counter Register (Framer_SR20—Framer_SR23)       87                                                                                                           |                                                                           |   |

| Table 67. Facility Remote Alarm Status Register (Framer_SR2)       81         Table 68. Local and Remote TF acility Event Register (Framer_SR3)       82         Table 70. Facility Event Register (Framer_SR5)       84         Table 71. Facility Event Register (Framer_SR6)       84         Table 72. Facility Cut of Unavailable State Register (Framer_SR7)       85         Table 73. Bipolar Violation Counter Registers (Framer_SR7)       85         Table 74. Framing Bit Eror Counter Registers (Framer_SR10—Framer_SR1)       85         Table 75. CRC-4 Error Counter Registers (Framer_SR15)       86         Table 76. E-Bit Counter Registers (Framer_SR15)       86         Table 76. E-Bit Counter Registers (Framer_SR16—Framer_SR19)       86         Table 78. E Bit at NT1 from NT2 Counter Registers (Framer_SR20—Framer_SR19)       86         Table 80. ET Errored Seconds Counter Register (Framer_SR20—Framer_SR21)       87         Table 81. ET Severely Errored Seconds Counter Register (Framer_SR20—Framer_SR23)       87         Table 83. ET-RE Errored Seconds Counter Register (Framer_SR20—Framer_SR23)       87         Table 84. ET-RE Bursty Errored Seconds Counter Register (Framer_SR30—Framer_SR23)       87         Table 83. ET-RE Everely Errored Seconds Counter Register (Framer_SR34—Framer_SR31)       87         Table 84. ET-RE Bursty Errored Seconds Counter Register (Framer_SR34—Framer_SR33)       88         Ta                                                                                                  | able 65. Frame Monitor Main Status Register (Framer_SR0)                  |   |

| Table 68. Local and Remote ET Facility Event Register (Framer_SR3)       82         Table 69. Local and Remote Network Termination-1 Facility Event Register (Framer_SR4)       83         Table 71. Facility Evrored Event Register (Framer_SR5)       84         Table 72. Facility Out of Unavailable State Register (Framer_SR7)       85         Table 73. Bipolar Violation Counter Registers (Framer_SR10—Framer_SR9)       85         Table 74. Framing Bit Error Counter Registers (Framer_SR10—Framer_SR13)       86         Table 75. CRC-4 Errors at NT1 from NT2 Counter Registers (Framer_SR15)       86         Table 76. E-Bit Counter Register (Framer_SR14—Framer_SR15)       86         Table 77. CRC-4 Errors at NT1 from NT2 Counter Registers (Framer_SR10—Framer_SR19)       86         Table 78. E Bit at NT1 from NT2 Counter Register (Framer_SR20—Framer_SR21)       87         Table 80. ET Bursty Errored Seconds Counter Register (Framer_SR22—Framer_SR23)       87         Table 81. ET Severely Errored Seconds Counter Register (Framer_SR24—Framer_SR28)       87         Table 82. ET Unavailable Seconds Counter Register (Framer_SR34—Framer_SR31)       87         Table 83. ET-RE Errored Seconds Counter Register (Framer_SR34—Framer_SR33)       88         Table 84. ET-RE Bursty Errored Seconds Counter Register (Framer_SR34—Framer_SR31)       87         Table 85. ET-RE Everely Errored Seconds Counter Register (Framer_SR34—Framer_SR33)       88         Ta                                                               |                                                                           |   |

| Table 69. Local and Remote Network Termination-1 Facility Event Register (Framer_SR4)       83         Table 70. Facility Event Register (Framer_SR5)       84         Table 71. Facility Cort of Unavailable State Register (Framer_SR7)       85         Table 73. Bipolar Violation Counter Registers (Framer_SR3)       85         Table 74. Framing Bit Error Counter Registers (Framer_SR10—Framer_SR1)       85         Table 75. CRC-4 Error Counter Registers (Framer_SR10—Framer_SR13)       86         Table 76. E-Bit Counter Register (Framer_SR14—Framer_SR15)       86         Table 77. CRC-4 Errors at NT1 from NT2 Counter Registers (Framer_SR16)       86         Table 78. E Bit at NT1 from NT2 Counter Registers (Framer_SR16)       86         Table 78. E Bit at NT1 from NT2 Counter Register (Framer_SR16)       87         Table 80. ET Bursty Errored Seconds Counter Register (Framer_SR20—Framer_SR21)       87         Table 80. ET Bursty Errored Seconds Counter Register (Framer_SR24—Framer_SR25)       87         Table 81. ET Severely Errored Seconds Counter Register (Framer_SR34—Framer_SR25)       87         Table 84. ET-RE Bursty Errored Seconds Counter Register (Framer_SR34—Framer_SR33)       88         Table 85. ET-RE Severely Errored Seconds Counter Register (Framer_SR34—Framer_SR35)       88         Table 86. ET-RE Unavailable Seconds Counter Register (Framer_SR34—Framer_SR33)       88         Table 87. NT1 Errored Seconds Counter Register                                                               |                                                                           |   |

| Table 70. Facility Event Register (Framer_SR6)84Table 71. Facility Cut of Unavailable State Register (Framer_SR7)85Table 72. Facility Out of Unavailable State Register (Framer_SR7)85Table 73. Bipolar Violation Counter Registers (Framer_SR8—Framer_SR1)85Table 75. CRC-4 Error Counter Registers (Framer_SR1—Framer_SR13)86Table 75. CRC-4 Error Counter Register (Framer_SR14—Framer_SR15)86Table 75. CRC-4 Error at NT1 from NT2 Counter Registers (Framer_SR16—Framer_SR17)86Table 76. E-Bit Counter Register (Framer_SR14—Framer_SR16)86Table 78. EBit at NT1 from NT2 Counter Registers (Framer_SR21)87Table 80. ET Bursty Errored Seconds Counter Register (Framer_SR24—Framer_SR21)87Table 80. ET Severely Errored Seconds Counter Register (Framer_SR24—Framer_SR23)87Table 82. ET Unavailable Seconds Counter Register (Framer_SR26—Framer_SR27)87Table 83. ET-RE Everely Errored Seconds Counter Register (Framer_SR26—Framer_SR27)87Table 84. ET-RE Bursty Errored Seconds Counter Register (Framer_SR30—Framer_SR33)88Table 85. ET-RE Severely Errored Seconds Counter Register (Framer_SR30—Framer_SR33)88Table 86. ET-RE Unavailable Seconds Counter Register (Framer_SR34—Framer_SR33)88Table 86. ET-RE Unavailable Seconds Counter Register (Framer_SR34—Framer_SR33)88Table 86. ET-RE Unavailable Seconds Counter Register (Framer_SR40—Framer_SR33)88Table 86. ET-RE Everely Errored Seconds Counter Register (Framer_SR40—Framer_SR43)88Table 88. IT1 Eurored Seconds Counter Register (Framer_SR40—Framer_SR43)88Table 88.                            |                                                                           |   |

| Table 71. Facility Errored Event Register (Framer_SR7)84Table 72. Facility Out of Unavailable State Register (Framer_SR7)85Table 73. Bipolar Violation Counter Registers (Framer_SR10—Framer_SR1)85Table 75. CRC-4 Error Counter Register (Framer_SR12—Framer_SR13)86Table 76. ENE Counter Register (Framer_SR14—Framer_SR13)86Table 76. ENE Counter Register (Framer_SR14—Framer_SR13)86Table 76. ENE Counter Register (Framer_SR14—Framer_SR15)86Table 76. ENE Counter Registers (Framer_SR14)86Table 77. CRC-4 Errors at NT1 from NT2 Counter Registers (Framer_SR16—Framer_SR19)86Table 78. E Bit at NT1 from NT2 Counter Register (Framer_SR20—Framer_SR21)87Table 80. ET Bursty Errored Seconds Counter Register (Framer_SR20—Framer_SR23)87Table 80. ET Bursty Errored Seconds Counter Register (Framer_SR20—Framer_SR23)87Table 81. ET Severely Errored Seconds Counter Register (Framer_SR20—Framer_SR27)87Table 82. ET Unavailable Seconds Counter Register (Framer_SR20—Framer_SR27)87Table 83. ET-RE Eurored Seconds Counter Register (Framer_SR30—Framer_SR31)87Table 84. ET-RE Bursty Errored Seconds Counter Register (Framer_SR34—Framer_SR33)88Table 85. ET-RE Unavailable Seconds Counter Register (Framer_SR34—Framer_SR37)88Table 80. NT1 Eurored Seconds Counter Register (Framer_SR34—Framer_SR33)88Table 80. NT1 Severely Errored Seconds Counter Register (Framer_SR40—Framer_SR43)88Table 80. NT1 Severely Errored Seconds Counter Register (Framer_SR40—Framer_SR43)88Table 80. NT1 Severely Errored Seconds Counter Reg                            |                                                                           |   |

| Table 72. Facility Out of Unavailable State Register (Framer_SR7)       85         Table 73. Bipolar Violation Counter Registers (Framer_SR4)—Framer_SR9)       85         Table 74. Framing Bit Error Counter Registers (Framer_SR10—Framer_SR11)       85         Table 75. CRC-4 Error Counter Register (Framer_SR12—Framer_SR13)       86         Table 76. E-Bit Counter Register (Framer_SR12—Framer_SR15)       86         Table 78. E Bit at NT1 from NT2 Counter Registers (Framer_SR16—Framer_SR19)       86         Table 78. E Bit at NT1 from NT2 Counter Registers (Framer_SR20—Framer_SR21)       87         Table 80. ET Bursty Errored Seconds Counter Register (Framer_SR24—Framer_SR23)       87         Table 81. ET Severely Errored Seconds Counter Register (Framer_SR24—Framer_SR29)       87         Table 82. ET Unavailable Seconds Counter Register (Framer_SR26—Framer_SR29)       87         Table 83. ET-RE Errored Seconds Counter Register (Framer_SR30—Framer_SR31)       87         Table 84. ET-RE Bursty Errored Seconds Counter Register (Framer_SR30—Framer_SR33)       88         Table 85. ET-RE Everely Errored Seconds Counter Register (Framer_SR30—Framer_SR33)       88         Table 86. ET-RE Unavailable Seconds Counter Register (Framer_SR30—Framer_SR33)       88         Table 86. NT1 Bursty Errored Seconds Counter Register (Framer_SR40—Framer_SR43)       88         Table 87. NT1 Errored Seconds Counter Register (Framer_SR40—Framer_SR43)       88                                                              |                                                                           |   |

| Table 73. Bipolar Violation Counter Registers (Framer_SR8—Framer_SR9)85Table 74. Framing Bit Error Counter Registers (Framer_SR10—Framer_SR11)85Table 75. CRC-4 Errors Counter Register (Framer_SR14—Framer_SR13)86Table 76. E-Bit Counter Register (Framer_SR14—Framer_SR15)86Table 77. CRC-4 Errors at NT1 from NT2 Counter Registers (Framer_SR16—Framer_SR19)86Table 78. E Bit at NT1 from NT2 Counter Registers (Framer_SR20—Framer_SR19)86Table 79. ET Errored Seconds Counter Register (Framer_SR20—Framer_SR21)87Table 80. ET Bursty Errored Seconds Counter Register (Framer_SR24—Framer_SR23)87Table 81. ET Severely Errored Seconds Counter Register (Framer_SR26—Framer_SR25)87Table 82. ET Unavailable Seconds Counter Register (Framer_SR26—Framer_SR27)87Table 83. ET-RE Errored Seconds Counter Register (Framer_SR26—Framer_SR31)87Table 84. ET-RE Bursty Errored Seconds Counter Register (Framer_SR30—Framer_SR31)87Table 85. ET-RE Severely Errored Seconds Counter Register (Framer_SR34—Framer_SR33)88Table 86. ET-RE Unavailable Seconds Counter Register (Framer_SR34—Framer_SR33)88Table 87. NT1 Errored Seconds Counter Register (Framer_SR40—Framer_SR37)88Table 80. NT1 Severely Errored Seconds Counter Register (Framer_SR40—Framer_SR41)88Table 90. NT1 Unavailable Seconds Counter Register (Framer_SR40—Framer_SR43)88Table 90. NT1 Severely Errored Seconds Counter Register (Framer_SR40—Framer_SR43)88Table 90. NT1 Nexsty Errored Seconds Counter Register (Framer_SR40—Framer_SR43)88Table 90. NT1 Neavailable Seconds Counter Register |                                                                           |   |

| Table 74. Framing Bit Error Counter Register (Framer_SR10—Framer_SR13)       85         Table 75. CRC-4 Error Counter Register (Framer_SR12—Framer_SR15)       86         Table 76. E-Bit Counter Register (Framer_SR14—Framer_SR15)       86         Table 77. CRC-4 Error at NT1 from NT2 Counter Registers (Framer_SR16—Framer_SR19)       86         Table 78. E Bit at NT1 from NT2 Counter Registers (Framer_SR18—Framer_SR19)       86         Table 79. ET Errored Seconds Counter Register (Framer_SR20—Framer_SR21)       87         Table 80. ET Bursty Errored Seconds Counter Register (Framer_SR24—Framer_SR23)       87         Table 81. ET Severely Errored Seconds Counter Register (Framer_SR24—Framer_SR23)       87         Table 82. ET Unavailable Seconds Counter Register (Framer_SR24—Framer_SR23)       87         Table 84. ET-RE Bursty Errored Seconds Counter Register (Framer_SR24—Framer_SR23)       87         Table 85. ET-RE Bursty Errored Seconds Counter Register (Framer_SR34—Framer_SR31)       87         Table 86. ET-RE Severely Errored Seconds Counter Register (Framer_SR34—Framer_SR35)       88         Table 86. ET-RE Unavailable Seconds Counter Register (Framer_SR34—Framer_SR37)       88         Table 80. NT1 Errored Seconds Counter Register (Framer_SR44—Framer_SR39)       88         Table 80. NT1 Errored Seconds Counter Register (Framer_SR44—Framer_SR41)       88         Table 80. NT1 Nurvailable Seconds Counter Register (Framer_SR44—Framer_SR45)       89                                            |                                                                           |   |

| Table 75. CRC-4 Error Counter Register (Framer_SR12—Framer_SR13)86Table 77. CRC-4 Errors at NT1 from NT2 Counter Registers (Framer_SR16—Framer_SR16)86Table 77. CRC-4 Errors at NT1 from NT2 Counter Registers (Framer_SR16—Framer_SR19)86Table 78. E Bit at NT1 from NT2 Counter Registers (Framer_SR20—Framer_SR21)87Table 80. ET Eurored Seconds Counter Register (Framer_SR20—Framer_SR23)87Table 80. ET Severely Errored Seconds Counter Register (Framer_SR24—Framer_SR23)87Table 81. ET Severely Errored Seconds Counter Register (Framer_SR24—Framer_SR25)87Table 82. ET Unavailable Seconds Counter Register (Framer_SR26—Framer_SR29)87Table 83. ET-RE Errored Seconds Counter Register (Framer_SR26—Framer_SR29)87Table 84. ET-RE Bursty Errored Seconds Counter Register (Framer_SR30—Framer_SR31)87Table 85. ET-RE Severely Errored Seconds Counter Register (Framer_SR30—Framer_SR33)88Table 86. ET-RE Unavailable Seconds Counter Register (Framer_SR36—Framer_SR33)88Table 87. NT1 Errored Seconds Counter Register (Framer_SR36—Framer_SR39)88Table 89. NT1 Severely Errored Seconds Counter Register (Framer_SR40—Framer_SR43)88Table 90. NT1 Unavailable Seconds Counter Register (Framer_SR40—Framer_SR43)88Table 93. NT1-RE Eurored Seconds Counter Register (Framer_SR46—Framer_SR43)89Table 93. NT1-RE Evrored Seconds Counter Register (Framer_SR44—Framer_SR43)89Table 94. NT1-RE Unavailable Seconds Counter Register (Framer_SR44—Framer_SR43)89Table 93. NT1-RE Severely Errored Seconds Counter Register (Framer_SR44—Framer_SR45)89Table 94. NT |                                                                           |   |

| Table 76. E-Bit Counter Register (Framer_SR14—Framer_SR15)86Table 77. CRC-4 Errors at NT1 from NT2 Counter Registers (Framer_SR16—Framer_SR19)86Table 78. E Bit at NT1 from NT2 Counter Register (Framer_SR19)86Table 79. ET Errored Seconds Counter Register (Framer_SR20—Framer_SR21)87Table 80. ET Bursty Errored Seconds Counter Register (Framer_SR22—Framer_SR23)87Table 81. ET Severely Errored Seconds Counter Register (Framer_SR26—Framer_SR25)87Table 82. ET Unavailable Seconds Counter Register (Framer_SR26—Framer_SR27)87Table 83. ET-RE Errored Seconds Counter Register (Framer_SR26—Framer_SR29)87Table 84. ET-RE Bursty Errored Seconds Counter Register (Framer_SR30—Framer_SR31)87Table 84. ET-RE Unavailable Seconds Counter Register (Framer_SR30—Framer_SR31)87Table 85. ET-RE Severely Errored Seconds Counter Register (Framer_SR30—Framer_SR33)88Table 86. ET-RE Unavailable Seconds Counter Register (Framer_SR34—Framer_SR35)88Table 88. NT1 Bursty Errored Seconds Counter Register (Framer_SR34)88Table 88. NT1 Bursty Errored Seconds Counter Register (Framer_SR40—Framer_SR43)88Table 90. NT1 Navailable Seconds Counter Register (Framer_SR40—Framer_SR43)88Table 91. NT1-RE Errored Seconds Counter Register (Framer_SR40—Framer_SR43)88Table 92. NT1-RE Severely Errored Seconds Counter Register (Framer_SR40—Framer_SR43)89Table 93. NT1-RE Severely Errored Seconds Counter Register (Framer_SR40—Framer_SR43)89Table 94. NT1-RE Unavailable Seconds Counter Register (Framer_SR40—Framer_SR43)89Table 95. Received NOT FAS TSO RSA a |                                                                           |   |

| Table 77. CRC-4 Errors at NT1 from NT2 Counter Registers (Framer_SR16—Framer_SR17)86Table 78. E Bit at NT1 from NT2 Counter Registers (Framer_SR18—Framer_SR19)86Table 79. ET Errored Seconds Counter Register (Framer_SR20—Framer_SR23)87Table 80. ET Bursty Errored Seconds Counter Register (Framer_SR24—Framer_SR25)87Table 81. ET Severely Errored Seconds Counter Register (Framer_SR24—Framer_SR29)87Table 83. ET-RE Errored Seconds Counter Register (Framer_SR26—Framer_SR29)87Table 84. ET-RE Bursty Errored Seconds Counter Register (Framer_SR30—Framer_SR31)87Table 84. ET-RE Bursty Errored Seconds Counter Register (Framer_SR30—Framer_SR31)87Table 85. ET-RE Severely Errored Seconds Counter Register (Framer_SR30—Framer_SR31)88Table 86. ET-RE Unavailable Seconds Counter Register (Framer_SR34—Framer_SR33)88Table 86. TT I Errored Seconds Counter Register (Framer_SR34—Framer_SR35)88Table 87. NT1 Errored Seconds Counter Register (Framer_SR34—Framer_SR39)88Table 80. NT1 Bursty Errored Seconds Counter Register (Framer_SR40—Framer_SR43)88Table 90. NT1 Unavailable Seconds Counter Register (Framer_SR40—Framer_SR43)88Table 91. NT1-RE Errored Seconds Counter Register (Framer_SR44—Framer_SR45)89Table 92. NT1-RE Bursty Errored Seconds Counter Register (Framer_SR40—Framer_SR45)89Table 93. NT1-RE Errored Seconds Counter Register (Framer_SR46—Framer_SR45)89Table 94. NT1-RE Bursty Errored Seconds Counter Register (Framer_SR45)89Table 93. NT1-RE Severely Errored Seconds Counter Register (Framer_SR45)89Table 94. NT1-RE Burst |                                                                           |   |

| Table 78. E Bit at NT1 from NT2 Counter Registers (Framer_SR18—Framer_SR19)86Table 79. ET Errored Seconds Counter Register (Framer_SR20—Framer_SR21)87Table 80. ET Bursty Errored Seconds Counter Register (Framer_SR24—Framer_SR23)87Table 81. ET Severely Errored Seconds Counter Register (Framer_SR24—Framer_SR25)87Table 83. ET-RE Errored Seconds Counter Register (Framer_SR26—Framer_SR29)87Table 84. ET-RE Bursty Errored Seconds Counter Register (Framer_SR28—Framer_SR29)87Table 85. ET-RE Severely Errored Seconds Counter Register (Framer_SR30—Framer_SR31)87Table 85. ET-RE Unavailable Seconds Counter Register (Framer_SR34—Framer_SR33)88Table 86. ET-RE Unavailable Seconds Counter Register (Framer_SR34—Framer_SR33)88Table 87. NT1 Errored Seconds Counter Register (Framer_SR34—Framer_SR37)88Table 88. NT1 Bursty Errored Seconds Counter Register (Framer_SR40—Framer_SR39)88Table 90. NT1 Unavailable Seconds Counter Register (Framer_SR40—Framer_SR43)88Table 91. NT1-RE Errored Seconds Counter Register (Framer_SR44—Framer_SR45)89Table 92. NT1-RE Eurored Seconds Counter Register (Framer_SR44—Framer_SR45)89Table 93. NT1-RE Everely Errored Seconds Counter Register (Framer_SR44—Framer_SR45)89Table 94. NT1-RE Unavailable Seconds Counter Register (Framer_SR44—Framer_SR45)89Table 95. Received NOT FAS TSO RSA and E Bits Framer_(SR52)89Table 94. NT1-RE Unavailable Seconds Counter Register (Framer_SR48—Framer_SR45)89Table 95. Received NOT FAS TSO RSA and E Bits Framer_(SR52)89Table 96. FDL ANSI Bit Code Status Register ( |                                                                           |   |

| Table 79. ET Errored Seconds Counter Register (Framer_SR20—Framer_SR21)87Table 80. ET Bursty Errored Seconds Counter Register (Framer_SR22—Framer_SR23)87Table 81. ET Severely Errored Seconds Counter Register (Framer_SR24—Framer_SR25)87Table 82. ET Unavailable Seconds Counter Register (Framer_SR26—Framer_SR27)87Table 83. ET-RE Errored Seconds Counter Register (Framer_SR26—Framer_SR29)87Table 84. ET-RE Bursty Errored Seconds Counter Register (Framer_SR30—Framer_SR31)87Table 85. ET-RE Severely Errored Seconds Counter Register (Framer_SR30—Framer_SR33)88Table 86. ET-RE Unavailable Seconds Counter Register (Framer_SR34—Framer_SR35)88Table 87. NT1 Errored Seconds Counter Register (Framer_SR36—Framer_SR37)88Table 89. NT1 Bursty Errored Seconds Counter Register (Framer_SR40—Framer_SR41)88Table 89. NT1 Severely Errored Seconds Counter Register (Framer_SR40—Framer_SR41)88Table 90. NT1 Neverely Errored Seconds Counter Register (Framer_SR40—Framer_SR43)88Table 91. NT1-RE Errored Seconds Counter Register (Framer_SR40—Framer_SR45)89Table 93. NT1-RE Severely Errored Seconds Counter Register (Framer_SR46—Framer_SR45)89Table 94. NT1-RE Unavailable Seconds Counter Register (Framer_SR46—Framer_SR45)89Table 95. Received NOT FAS TSO RSA and E Bits Framer_(SR52)89Table 94. NT1-RE Unavailable Seconds Counter Register (Framer_SR50—Framer_SR47)89Table 95. HDLC Status of Frame Byte92Table 94. HDLC Frame Romat93Table 95. HDLC Status of Frame Byte92Table 94. HDLC Frame Romat93 <td></td> <td></td>                         |                                                                           |   |

| Table 80. ET Bursty Errored Seconds Counter Register (Framer_SR22—Framer_SR23)87Table 81. ET Severely Errored Seconds Counter Register (Framer_SR26—Framer_SR25)87Table 82. ET Unavailable Seconds Counter Register (Framer_SR26—Framer_SR27)87Table 84. ET-RE Bursty Errored Seconds Counter Register (Framer_SR30—Framer_SR31)87Table 85. ET-RE Severely Errored Seconds Counter Register (Framer_SR30—Framer_SR31)87Table 86. ET-RE Unavailable Seconds Counter Register (Framer_SR30—Framer_SR33)88Table 86. ET-RE Unavailable Seconds Counter Register (Framer_SR34—Framer_SR35)88Table 87. NT1 Errored Seconds Counter Register (Framer_SR34—Framer_SR37)88Table 88. NT1 Bursty Errored Seconds Counter Register (Framer_SR30—Framer_SR39)88Table 90. NT1 Unavailable Seconds Counter Register (Framer_SR40—Framer_SR41)88Table 91. NT1-RE Errored Seconds Counter Register (Framer_SR44—Framer_SR45)89Table 93. NT1-RE Bursty Errored Seconds Counter Register (Framer_SR46—Framer_SR45)89Table 94. NT1-RE Unavailable Seconds Counter Register (Framer_SR46—Framer_SR49)89Table 94. NT1-RE Unavailable Seconds Counter Register (Framer_SR46—Framer_SR49)89Table 95. Received NOT FAS TSO RSA and E Bits Framer_(SR52)89Table 96. FDL ANSI Bit Code Status Register (FDL_SR2)91Table 97. Performance Report Message Structure91Table 98. HDLC Status of Frame Byte92Table 99. HDLC Frame Format93Table 90. FDL Receiver Fill Level Control Register (FDL_PR0)95Table 100. Facility Data Link Registers95Table 1                                                       |                                                                           |   |

| Table 81. ET Severely Errored Seconds Counter Register (Framer_SR24—Framer_SR25)87Table 82. ET Unavailable Seconds Counter Register (Framer_SR26—Framer_SR27)87Table 83. ET-RE Errored Seconds Counter Register (Framer_SR26—Framer_SR29)87Table 84. ET-RE Bursty Errored Seconds Counter Register (Framer_SR30—Framer_SR31)87Table 85. ET-RE Severely Errored Seconds Counter Register (Framer_SR32—Framer_SR33)88Table 86. ET-RE Unavailable Seconds Counter Register (Framer_SR34—Framer_SR35)88Table 87. NT1 Errored Seconds Counter Register (Framer_SR34—Framer_SR35)88Table 88. NT1 Bursty Errored Seconds Counter Register (Framer_SR36—Framer_SR39)88Table 89. NT1 Severely Errored Seconds Counter Register (Framer_SR40—Framer_SR41)88Table 90. NT1 Unavailable Seconds Counter Register (Framer_SR40—Framer_SR43)88Table 90. NT1 Re Errored Seconds Counter Register (Framer_SR44—Framer_SR43)88Table 90. NT1-RE Errored Seconds Counter Register (Framer_SR44—Framer_SR43)89Table 93. NT1-RE Bursty Errored Seconds Counter Register (Framer_SR46—Framer_SR47)89Table 94. NT1-RE Unavailable Seconds Counter Register (Framer_SR50)89Table 95. Received NOT FAS TSO RSA and E Bits Framer_(SR52)89Table 95. Received NOT FAS TSO RSA and E Bits Framer_SR5091Table 97. Performance Report Message Structure91Table 98. HDLC Status of Frame Byte92Table 99. HDLC Frame Format93Table 90. FDL Receiver Fill Level Control Register (FDL_PR2)96Table 100. Facility Data Link Registers95Table 101. FDL Recei                                                       |                                                                           |   |

| Table 82. ET Unavailable Seconds Counter Register (Framer_SR26—Framer_SR27)87Table 83. ET-RE Errored Seconds Counter Register (Framer_SR28—Framer_SR30)87Table 84. ET-RE Bursty Errored Seconds Counter Register (Framer_SR30—Framer_SR31)87Table 85. ET-RE Severely Errored Seconds Counter Register (Framer_SR32—Framer_SR33)88Table 86. ET-RE Unavailable Seconds Counter Register (Framer_SR34—Framer_SR35)88Table 86. ET-RE Unavailable Seconds Counter Register (Framer_SR34—Framer_SR35)88Table 88. NT1 Bursty Errored Seconds Counter Register (Framer_SR36—Framer_SR37)88Table 89. NT1 Severely Errored Seconds Counter Register (Framer_SR40—Framer_SR41)88Table 90. NT1 Unavailable Seconds Counter Register (Framer_SR42—Framer_SR43)88Table 91. NT1-RE Eurored Seconds Counter Register (Framer_SR44—Framer_SR45)89Table 92. NT1-RE Bursty Errored Seconds Counter Register (Framer_SR44—Framer_SR45)89Table 93. NT1-RE Severely Errored Seconds Counter Register (Framer_SR46—Framer_SR47)89Table 94. NT1-RE Unavailable Seconds Counter Register (Framer_SR46—Framer_SR49)89Table 95. Received NOT FAS TSO RSA and E Bits Framer_(SR52)89Table 96. FDL ANSI Bit Code Status Register (FDL_SR2)91Table 97. Performance Report Message Structure91Table 98. HDLC Status of Frame Byte92Table 100. Facility Data Link Registers95Table 101. FDL Configuration Control Register (FDL_PR0)95Table 103. FDL Receiver Fill Level Control Register (FDL_PR1)96Table 104. FDL Transparent Mode Control Register (FDL_PR3)96 <td></td> <td></td>                         |                                                                           |   |

| Table 83. ET-RE Errored Seconds Counter Register (Framer_SR28—Framer_SR29)87Table 84. ET-RE Bursty Errored Seconds Counter Register (Framer_SR30—Framer_SR31)87Table 85. ET-RE Severely Errored Seconds Counter Register (Framer_SR32—Framer_SR33)88Table 86. ET-RE Unavailable Seconds Counter Register (Framer_SR34—Framer_SR35)88Table 87. NT1 Errored Seconds Counter Register (Framer_SR36—Framer_SR35)88Table 88. NT1 Bursty Errored Seconds Counter Register (Framer_SR36—Framer_SR39)88Table 89. NT1 Severely Errored Seconds Counter Register (Framer_SR40—Framer_SR49)88Table 90. NT1 Unavailable Seconds Counter Register (Framer_SR40—Framer_SR43)88Table 91. NT1-RE Errored Seconds Counter Register (Framer_SR44—Framer_SR45)89Table 92. NT1-RE Bursty Errored Seconds Counter Register (Framer_SR46—Framer_SR45)89Table 93. NT1-RE Evrored Seconds Counter Register (Framer_SR40—Framer_SR47)89Table 94. NT1-RE Unavailable Seconds Counter Register (Framer_SR40—Framer_SR49)89Table 95. Received NOT FAS TSO RSA and E Bits Framer_(SR52)89Table 96. FDL ANSI Bit Code Status Register (FDL_SR2)91Table 97. Performance Report Message Structure91Table 98. HDLC Status of Frame Byte92Table 99. HDLC Frame Format93Table 100. Facility Data Link Registers95Table 101. FDL Configuration Control Register (FDL_PR0)95Table 103. FDL Receiver Match Character Register (FDL_PR3)96Table 104. FDL Transparent Mode Control Register (FDL_PR3)96Table 105. FDL Fill Status Register (FDL_SR0)97                                                                |                                                                           |   |

| Table 84. ET-RE Bursty Errored Seconds Counter Register (Framer_SR30—Framer_SR31)87Table 85. ET-RE Severely Errored Seconds Counter Register (Framer_SR32—Framer_SR33)88Table 86. ET-RE Unavailable Seconds Counter Register (Framer_SR34—Framer_SR35)88Table 87. NT1 Errored Seconds Counter Register (Framer_SR36—Framer_SR37)88Table 88. NT1 Bursty Errored Seconds Counter Register (Framer_SR36—Framer_SR39)88Table 89. NT1 Severely Errored Seconds Counter Register (Framer_SR40—Framer_SR49)88Table 90. NT1 Unavailable Seconds Counter Register (Framer_SR42—Framer_SR43)88Table 91. NT1-RE Errored Seconds Counter Register (Framer_SR44—Framer_SR43)89Table 92. NT1-RE Bursty Errored Seconds Counter Register (Framer_SR46—Framer_SR47)89Table 93. NT1-RE Severely Errored Seconds Counter Register (Framer_SR46—Framer_SR49)89Table 94. NT1-RE Unavailable Seconds Counter Register (Framer_SR50—Framer_SR49)89Table 95. Received NOT FAS TSO RSA and E Bits Framer_(SR52)89Table 96. FDL ANSI Bit Code Status Register (FDL_SR2)91Table 97. Performance Report Message Structure91Table 98. HDLC Status of Frame Byte92Table 99. HDLC Frame Format93Table 100. Facility Data Link Registers95Table 101. FDL Configuration Control Register (FDL_PR0)95Table 102. FDL Receiver Hill Level Control Register (FDL_PR2)96Table 104. FDL Transparent Mode Control Register (FDL_PR3)96Table 104. FDL Fill Status Register (FDL_SR0)97                                                                                                                                |                                                                           |   |

| Table 85. ET-RE Severely Errored Seconds Counter Register (Framer_SR32—Framer_SR33)88Table 86. ET-RE Unavailable Seconds Counter Register (Framer_SR34—Framer_SR35)88Table 87. NT1 Errored Seconds Counter Register (Framer_SR36—Framer_SR37)88Table 88. NT1 Bursty Errored Seconds Counter Register (Framer_SR36—Framer_SR39)88Table 89. NT1 Severely Errored Seconds Counter Register (Framer_SR40—Framer_SR41)88Table 90. NT1 Unavailable Seconds Counter Register (Framer_SR42—Framer_SR43)88Table 91. NT1-RE Errored Seconds Counter Register (Framer_SR44—Framer_SR43)88Table 92. NT1-RE Bursty Errored Seconds Counter Register (Framer_SR44—Framer_SR45)89Table 93. NT1-RE Severely Errored Seconds Counter Register (Framer_SR46—Framer_SR47)89Table 94. NT1-RE Unavailable Seconds Counter Register (Framer_SR46—Framer_SR49)89Table 95. Received NOT FAS TSO RSA and E Bits Framer_(SR52)89Table 96. FDL ANSI Bit Code Status Register (FDL_SR2)91Table 97. Performance Report Message Structure91Table 98. HDLC Status of Frame Byte92Table 99. HDLC Frame Format93Table 100. Facility Data Link Registers95Table 101. FDL Configuration Control Register (FDL_PR0)95Table 102. FDL Receiver Match Character Register (FDL_PR2)96Table 103. FDL Receiver Match Character Register (FDL_PR3)96Table 104. FDL Transparent Mode Control Register (FDL_PR3)96Table 105. FDL Fill Status Register (FDL_SR0)97                                                                                                                                                          | able 83. ET-RE Errored Seconds Counter Register (Framer_SR28—Framer_SR29) |   |

| Table 86. ET-RE Unavailable Seconds Counter Register (Framer_SR34—Framer_SR35)88Table 87. NT1 Errored Seconds Counter Register (Framer_SR36—Framer_SR37)88Table 88. NT1 Bursty Errored Seconds Counter Register (Framer_SR38—Framer_SR39)88Table 89. NT1 Severely Errored Seconds Counter Register (Framer_SR40—Framer_SR41)88Table 90. NT1 Unavailable Seconds Counter Register (Framer_SR42—Framer_SR43)88Table 91. NT1-RE Errored Seconds Counter Register (Framer_SR42—Framer_SR43)88Table 92. NT1-RE Bursty Errored Seconds Counter Register (Framer_SR46—Framer_SR45)89Table 93. NT1-RE Bursty Errored Seconds Counter Register (Framer_SR46—Framer_SR47)89Table 93. NT1-RE Unavailable Seconds Counter Register (Framer_SR46—Framer_SR49)89Table 94. NT1-RE Unavailable Seconds Counter Register (Framer_SR46—Framer_SR49)89Table 95. Received NOT FAS TSO RSA and E Bits Framer_(SR52)89Table 95. Received NOT FAS TSO RSA and E Bits Framer_(SR52)91Table 96. FDL ANSI Bit Code Status Register (FDL_SR2)91Table 99. HDLC Frame Format93Table 99. HDLC Frame Format93Table 100. Facility Data Link Registers95Table 101. FDL Configuration Control Register (FDL_PR1)96Table 103. FDL Receiver Fill Level Control Register (FDL_PR2)96Table 104. FDL Transparent Mode Control Register (FDL_PR3)96Table 105. FDL Fill Status Register (FDL_SR0)97                                                                                                                                                                                                                    |                                                                           |   |

| Table 87. NT1 Errored Seconds Counter Register (Framer_SR36—Framer_SR37)88Table 88. NT1 Bursty Errored Seconds Counter Register (Framer_SR38—Framer_SR39)88Table 89. NT1 Severely Errored Seconds Counter Register (Framer_SR40—Framer_SR41)88Table 90. NT1 Unavailable Seconds Counter Register (Framer_SR42—Framer_SR43)88Table 91. NT1-RE Errored Seconds Counter Register (Framer_SR44—Framer_SR45)89Table 92. NT1-RE Bursty Errored Seconds Counter Register (Framer_SR44—Framer_SR45)89Table 93. NT1-RE Severely Errored Seconds Counter Register (Framer_SR46—Framer_SR47)89Table 93. NT1-RE Enrored Seconds Counter Register (Framer_SR46—Framer_SR49)89Table 94. NT1-RE Unavailable Seconds Counter Register (Framer_SR50—Framer_SR49)89Table 95. Received NOT FAS TSO RSA and E Bits Framer_(SR52)89Table 96. FDL ANSI Bit Code Status Register (FDL_SR2)91Table 97. Performance Report Message Structure91Table 98. HDLC Status of Frame Byte92Table 100. Facility Data Link Registers95Table 101. FDL Configuration Control Register (FDL_PR0)95Table 102. FDL Receiver Fill Level Control Register (FDL_PR1)96Table 103. FDL Receiver Match Character Register (FDL_PR3)96Table 104. FDL Transparent Mode Control Register (FDL_PR3)96Table 105. FDL Fill Status Register (FDL_SR0)97                                                                                                                                                                                                                                                                            |                                                                           |   |

| Table 88. NT1 Bursty Errored Seconds Counter Register (Framer_SR38—Framer_SR39)88Table 89. NT1 Severely Errored Seconds Counter Register (Framer_SR40—Framer_SR41)88Table 90. NT1 Unavailable Seconds Counter Register (Framer_SR42—Framer_SR43)88Table 91. NT1-RE Errored Seconds Counter Register (Framer_SR44—Framer_SR45)89Table 92. NT1-RE Bursty Errored Seconds Counter Register (Framer_SR46—Framer_SR45)89Table 93. NT1-RE Severely Errored Seconds Counter Register (Framer_SR46—Framer_SR47)89Table 94. NT1-RE Unavailable Seconds Counter Register (Framer_SR50—Framer_SR49)89Table 95. Received NOT FAS TSO RSA and E Bits Framer_(SR52)89Table 96. FDL ANSI Bit Code Status Register (FDL_SR2)91Table 97. Performance Report Message Structure91Table 98. HDLC Status of Frame Byte92Table 100. Facility Data Link Registers95Table 101. FDL Configuration Control Register (FDL_PR0)95Table 102. FDL Receiver Fill Level Control Register (FDL_PR2)96Table 104. FDL Transparent Mode Control Register (FDL_PR3)96Table 105. FDL Fill Status Register (FDL_SR0)97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                           |   |

| Table 89. NT1 Severely Errored Seconds Counter Register (Framer_SR40—Framer_SR41)88Table 90. NT1 Unavailable Seconds Counter Register (Framer_SR42—Framer_SR43)88Table 91. NT1-RE Errored Seconds Counter Register (Framer_SR44—Framer_SR45)89Table 92. NT1-RE Bursty Errored Seconds Counter Register (Framer_SR46—Framer_SR47)89Table 93. NT1-RE Severely Errored Seconds Counter Register (Framer_SR46—Framer_SR47)89Table 94. NT1-RE Unavailable Seconds Counter Register (Framer_SR46—Framer_SR49)89Table 95. Received NOT FAS TSO RSA and E Bits Framer_(SR52)89Table 96. FDL ANSI Bit Code Status Register (FDL_SR2)91Table 97. Performance Report Message Structure91Table 98. HDLC Status of Frame Byte92Table 99. HDLC Frame Format93Table 100. Facility Data Link Registers95Table 101. FDL Configuration Control Register (FDL_PR0)95Table 103. FDL Receiver Fill Level Control Register (FDL_PR1)96Table 104. FDL Transparent Mode Control Register (FDL_PR3)96Table 105. FDL Fill Status Register (FDL_SR0)97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                           |   |