| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: TI380C30A | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

TI380C30A

INTEGRATED TOKEN-RING COMMPROCESSOR

AND PHYSICAL-LAYER INTERFACE

SPWS034 ≠ MARCH 1998

1

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

D

Single-Chip Token-Ring Solution

D

IBM

TM

Token-Ring Network

TM

Compatible

D

Compatible With ISO/IEC IEEE

Std 802.5:1992 Token-Ring Access-Method

and Physical-Layer Specifications

D

Compatible With TI380FPA PacketBlaster

TM

D

Glueless Memory Interface

D

Digital Phase-Locked Loop (PLL)

≠ Precise Control of Bandwidths

≠ Improved Jitter Tolerance

≠ Minimizes Accumulated Phase Slope

D

Phantom Drive for Physical Insertion Onto

Ring

D

Differential Line Receiver With

Level-Dependent Frequency Equalization

D

Low-Impedance Differential Line Driver to

Ease Transmit-Filter Design

D

On-Chip Watchdog Timer

D

Internal Crystal Oscillator for

Reference-Clock Generation

D

Expandable LAN-Subsystem Memory up to

2M Bytes

D

32-Bit Host Address Bus

D

80x8x or 68xxx-Type Bus and Memory

Organization

D

Dual-Port Direct Memory Access (DMA) and

Direct Input/Output Transfers to Host Bus

D

Supports 8- or 16-Bit Pseudo-Direct

Memory Access (PDMA) Operation

D

Electrostatic Discharge (ESD) Protection

Exceeds 2 kV (All Pins)

D

0.8-

µ

m CMOS Technology

D

Token-Ring Features

≠ 16- or 4-Megabit-Per-Second (Mbit/s)

Data Rates

≠ Supports up to 18K-Byte Frame Size

(16 Mbit/s Only)

≠ Supports Universal and Local

Addressing

≠ Early Token-Release Option (16 Mbit/s

Only)

≠ Built-In Real-Time Error Detection

≠ Automatic Frame-Buffer Management

≠ 2-MHz to 33-MHz System-Bus Clock

≠ Slow-Clock Low-Power Mode

D

176-Pin Thin Quad Flat Package

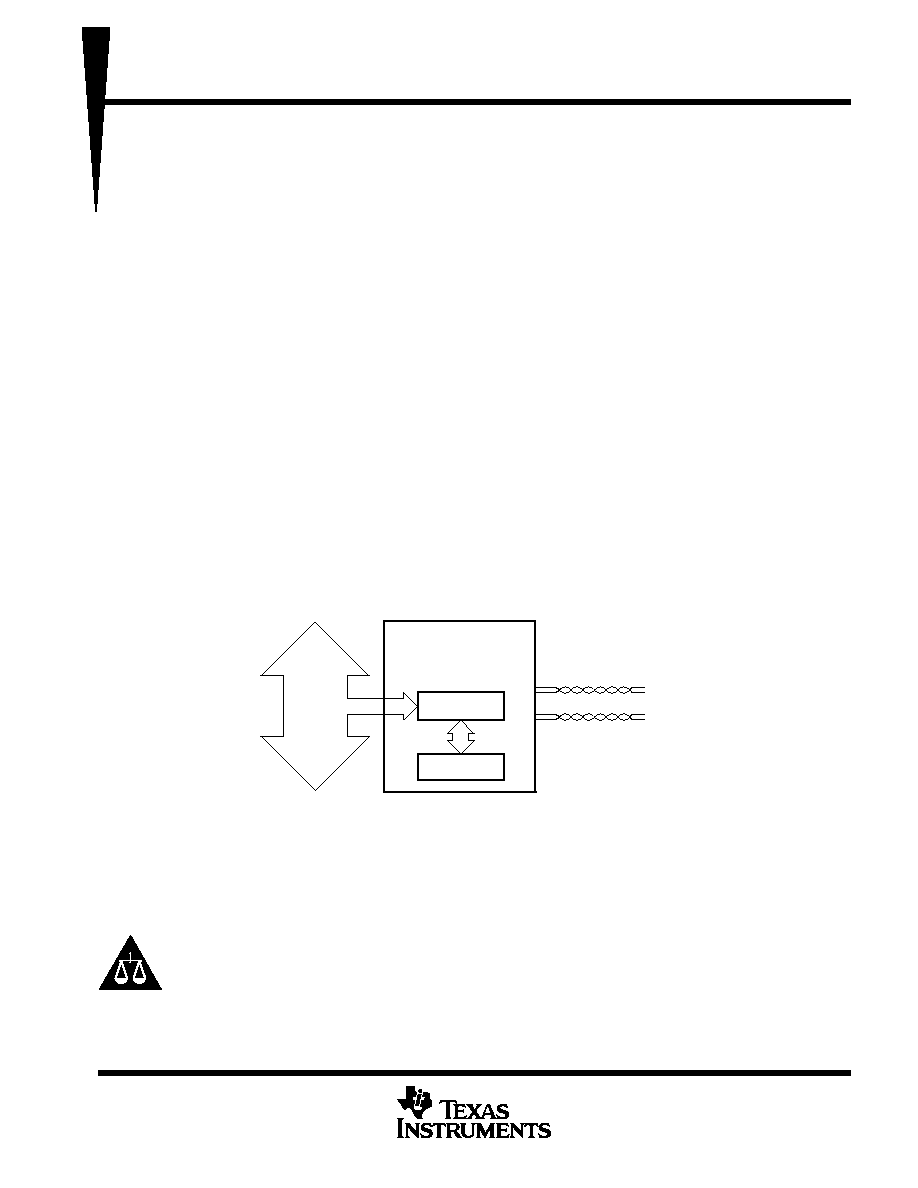

LAN Subsystem

Memory

Transmit

Receive

To

Network

Attached

System

Bus

(2 MHz

to

33 MHz)

TI380C30A

Figure 1. Network-Commprocessor Applications Diagram

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Copyright

©

1998, Texas Instruments Incorporated

Intel is a trademark of Intel Corporation.

IBM and Token-Ring Network are trademarks of International Business Machines Corporation.

Motorola is a trademark of Motorola, Inc.

PacketBlaster and TI are trademarks of Texas Instruments Incorporated.

PAL

Æ

is a registered trademark of Advanced Micro Devices, Inc. Other companies also manufacture programmable array logic devices.

TI380C30A

INTEGRATED TOKEN-RING COMMPROCESSOR

AND PHYSICAL-LAYER INTERFACE

SPWS034 ≠ MARCH 1998

2

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

Table 1. Abbreviations and Acronyms

APS

Accumulated Phase Slope

ASF

Adapter-Support Function

ARI/FCI

Address-Recognize Indicator/Frame-Copied Indicator

BIA

Burn-In Address

CAF

Copy All Frames

CG

Clock Generator

CP

Communications Processor

CPU

Central Processing Unit

CRC

Cyclic Redundancy Check

DIO

Direct Input/Output

DMA

Direct Memory Access

ESD

Electrostatic Discharge

EACO

Enhanced-Address-Copy Option

LLC

Logical Link Control

LSB

Least Significant Bit

MAC

Media-Access Control

Mbit/s

Megabits Per Second

Mbit/s

Megabytes Per Second

MIF

Memory Interface

MIPS

Million Instructions Per Second

MOSFET

Metal Oxide Semiconductor Field-Effect Transistor

MSB

Most Significant Bit

PDMA

Pseudo-Direct Memory Access

PH

Protocol Handler

PHY

Physical-Layer Interface

PLL

Phase-Locked Loop

SIF

System Interface

SIFACL

SIF Adapter Control Register

S/W

Software

TCU

Trunk-Coupling Unit

UNA

Upstream Neighbor Address

TI380C30A

INTEGRATED TOKEN-RING COMMPROCESSOR

AND PHYSICAL-LAYER INTERFACE

SPWS034 ≠ MARCH 1998

3

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

PGF PACKAGE

(TOP VIEW)

XT2

VSSO

XT1

VDDA2

ATEST

VSSA2

IREF

VSSA3

REDY

VDDA3

FRAQ

NSRT

VSSL

VDD

XMATCH

XFAIL

TEST0

TEST1

TEST2

TEST3

TEST4

TEST5

SADH0

SADH1

SADH2

SADH3

SADH4

SADH5

VSS

VDD

VSSC

SADH6

SADH7

SPH

SRD/SUDS

SRDY/SDTACK

SOWN

SDBEN

SBHE/SRNW

SHRQ/SBRQ

SPL

SADL0

SADL1

SADL2

MREF

MAL

MACS

MROMEN

OSC32

OSCIN

TCLK

TMS

TRST

VSSC

VSS

SYNCIN

VDDL

VDD

MDDIR

MAX0

MAX2

MCAS

MW

MRAS

VSSC

VSSL

MOE

MBEN

MADH7

MADH6

MADH5

MADH4

VDD

VSS

MADH3

MADH2

MADH1

MADH0

MAXPH

MBRQ

MBGR

VSS

MAXPL

MADL7

MADL6

MADL5

MADL4

MADL3

MBIAEN

176

45

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

132

131

130

129

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

DD

MRESET

175

46

SSL

MBCLK2

174

47

DDL

MBCLK1

173

48

MADL2

OSCOUT

172

49

MADL1

NSELOUT1

171

50

MADL0

WRAP

170

51

EXTINT3

DR

VR+

169

52

EXTINT2

DR

VR

≠

168

53

EXTINT1

WFL

T

167

54

EXTINT0

NC

166

55

NMI

TDI

165

56

CLKDIV

TDO

164

57

SSC

PXT

AL

163

58

NSELOUT0

RCVR

162

59

PR

TYEN

RCLK

161

60

BTSTRP

V

160

61

SIACK

V

159

62

SRESET

RA

TER

158

63

SRS1

V

157

64

SRS0

NABL

156

65

SRSX

S4

/

1

6

155

66

SCS

PWRDN

154

67

SBRLS

V

153

68

SBBSY

EQ+

152

69

S8

/

SHAL

T

EQ

≠

151

70

SRS2

/

SBERR

V

150

71

DDL

RCV+

149

72

SI

/

M

V

148

73

SINTR

/

SIRQ

RCV≠

147

74

SHLDA

/

SBGR

V

146

75

SDDIR

V

145

76

SRAS

/

SAS

XMT≠

144

77

SWR

/

SLDS

XMT+

143

78

SS

V

142

79

SXAL

PHOUTB

141

80

SALE

V

140

81

SBCLK

PHOUT

A

139

82

SADL7

V

138

83

SADL6

RES

137

84

SADL5

V

136

85

SADL4

NC

135

86

SADL3

V

134

87

DD

V

133

88

SSL

SSC1

SSD

DDD

SSL1

SSA1

DDA1

DDL1

DDX

SSX

SSP

DDP

SSL1

DDL1

DDO

V

V

V

V

V

V

V

V

NC = No internal connection

TI380C30A

INTEGRATED TOKEN-RING COMMPROCESSOR

AND PHYSICAL-LAYER INTERFACE

SPWS034 ≠ MARCH 1998

4

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

description

The TI380C30A is a single-chip token-ring solution, combining the commprocessor and the physical-layer

(PHY) interface onto a single device. The TI380C30A supports 16 Mbit/s and 4 Mbit/s of operation, conforms

to ISO 8802≠5/IEEE Std 802.5≠1992 standards, and has been verified to be completely IBM Token-Ring

Network compatible.

The TI380C30A provides a high degree of integration as it combines the functions of the TI380C25 and the

TI380C60A onto a single chip. Additional information on the PHY section can be found in the TI380C60A data

sheet, literature number SPWS033. With the TI380C30A, only local memory and minimal additional

components such as PAL

Æ

devices and crystal oscillators need to be added to complete the LAN-subsystem

design.

The TI380C30A provides a 32-bit system-memory address reach with a high-speed bus-master direct memory

access (DMA) interface that supports rapid communications with the host system. In addition, the TI380C30A

supports direct I/O and a low-cost 8-bit or 16-bit pseudo-DMA interface that requires only a chip-select to work

directly on an 80x8x 8-bit slave I/O interface. Selectable 80x8x or 68xxx-type host-system bus and memory

organization add to design flexibility.

The TI380C30A supports addressing for up to 2M bytes of local memory. This expanded memory capacity can

improve LAN-subsystem performance by minimizing the frequency of host LAN-subsystem communications

by allowing larger blocks of information to be transferred at one time. The support of large local memory is

important in applications that require large data transfers (such as graphics or database transfers) and in heavily

loaded networks where the extra memory can provide data buffers to store data until it can be processed by

the host.

The proprietary central processing unit (CPU) used in the TI380C30A allows protocol software to be

downloaded into RAM or stored in ROM in the local-memory space. By moving protocols [such as logical link

control (LLC)] to the LAN-subsystem, overall system performance is increased. This is accomplished by

offloading processing from the host-system to the TI380C30A, which also can reduce LAN-subsystem-to-host

communications. As other protocol software is developed, greater differentiation of end products with enhanced

system performance is possible.

The TI380C30A includes hardware counters that provide real-time error detection and automatic frame-buffer

management. These counters control system-bus retries and burst size, and track host- and

LAN-subsystem-buffer status. Previously, these counters were maintained in software. By integrating them into

hardware, software overhead is reduced and LAN-subsystem performance is improved.

The TI380C30A implements a Texas Instruments (TI

TM

)-patented enhanced-address-copy-option (EACO)

interface. This interface supports external address-checking devices, such as the TMS380SRA source-routing

accelerator. The TI380C30A has a 128-word external I/O space in its memory to support external

address-checker devices and other hardware extensions to the TMS380 architecture.

At the PHY, the Manchester-encoded data stream is received and phase-aligned using an on-chip dual-digital

phase-locked loop (PLL). Both the recovered clock and data are passed to the protocol-handling circuits on the

TI380C30A for serial-to-parallel conversion and data processing. On transmit, the TI380C30A buffers the output

from the protocol-handling circuit and drives the media by way of suitable isolation and waveform-shaping

components.

The TI380C30A uses CMOS technology to reduce power consumption to PCMCIA-compatible levels.

Power-management features are incorporated to support Green PC compatibility.

In addition to the PLL, all other functions required to interface to an IEEE Std 802.5 token ring are provided.

These functions include the phantom drive to control the relays within a trunk-coupling unit and wire-fault

detection circuits; an internal-wrap function for self-test; and a watchdog timer to provide fail-safe deinsertion

from the ring in the event of a station, microcode, or commprocessor failure.

TI380C30A

INTEGRATED TOKEN-RING COMMPROCESSOR

AND PHYSICAL-LAYER INTERFACE

SPWS034 ≠ MARCH 1998

5

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

description (continued)

The major blocks of the TI380C30A include the communications processor (CP), the system interface (SIF),

the memory interface (MIF), the protocol handler (PH), the clock generator (CG), the adapter-support function

(ASF), and the PHY, as shown in the functional block diagram.