STPC CONSUMER

2/51

Issue 1.2

s

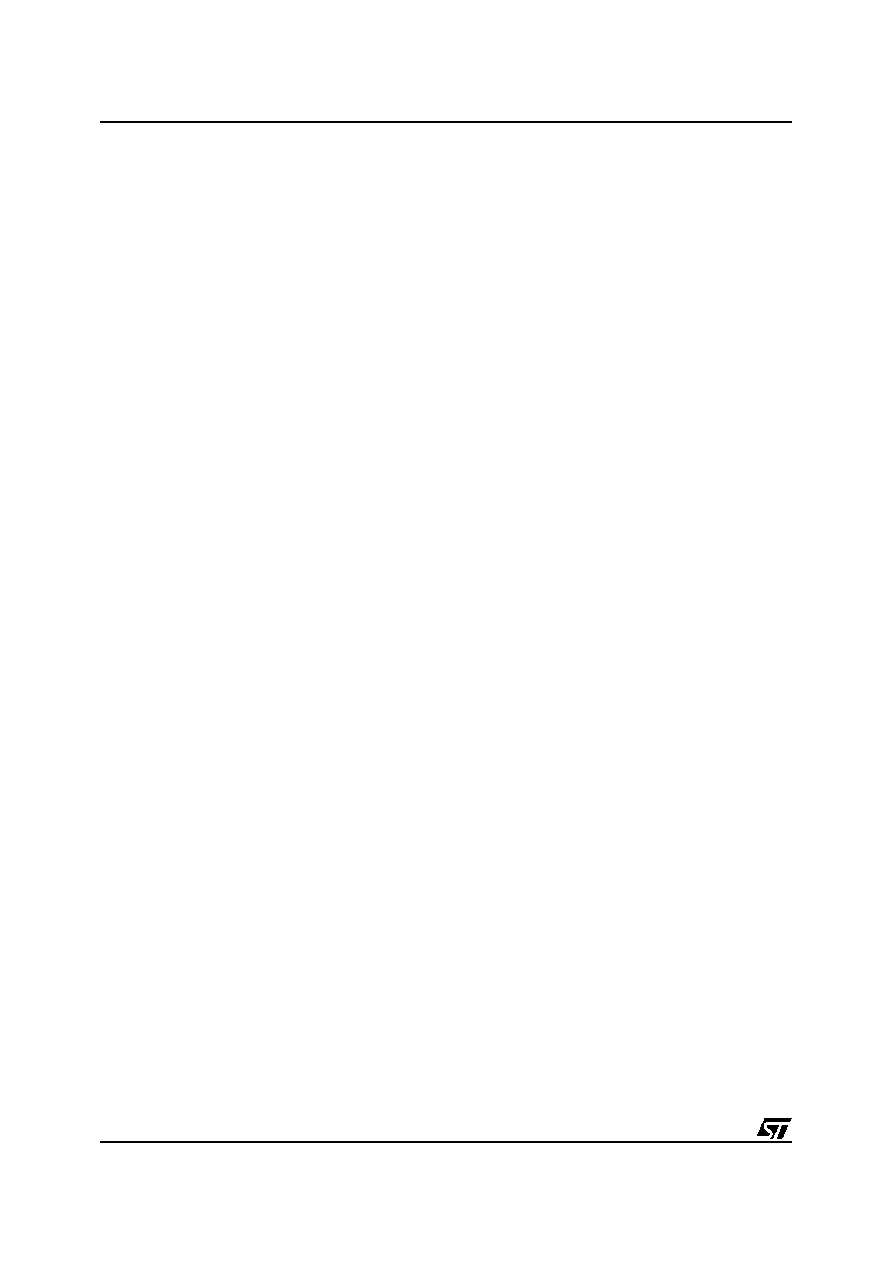

X86 Processor core

s

Fully static 32-bit 5-stage pipeline, x86

processor fully PC compatible.

s

Can access up to 4GBytes of external

memory.

s

8KByte unified instruction and data cache

with write back and write through capability.

s

Parallel processing integral floating point unit,

with automatic power down.

s

Clock core speeds up to of 100 MHz.

s

Fully static design for dynamic clock control.

s

Low power and system management modes.

s

Optimized design for 3.3V operation.

s

DRAM Controller

s

Integrated system memory and graphic frame

memory.

s

Supports up to 128 MBytes system memory

in 4 banks and down to as little as 2Mbytes.

s

Supports 4MB, 8MB, 16MB, 32MB single-

sided and double-sided DRAM SIMMs.

s

Four quad-word write buffers for CPU to

DRAM and PCI to DRAM cycles.

s

Four 4-word read buffers for PCI masters.

s

Supports Fast Page Mode & EDO DRAM.

s

Programmable timing for DRAM parameters

including CAS pulse width, CAS pre-charge

time and RAS to CAS delay.

s

60, 70, 80 & 100ns DRAM speeds.

s

Memory hole between 1 MByte & 8 MByte

supported for PCI/ISA busses.

s

Hidden refresh.

To check if your memory device is supported by

the STPC, please refer to Table 9-3 in the

Programming Manual.

s

Graphics Engine

s

64-bit windows accelerator.

s

Backward compatibility to SVGA standards.

s

Hardware acceleration for text, bitblts,

transparent blts and fills.

s

Up to 64 x 64 bit graphics hardware cursor.

s

Up to 4MB long linear frame buffer.

s

8-, 16-, and 24-bit pixels.

s

Drivers for Windows and other operating

systems.

s

VGA Controller

s

Integrated 135MHz triple RAMDAC allowing

for 1280 x 1024 x 75Hz display.

s

Requires external frequency synthesizer and

reference sources.

s

8-, 16-, 24-bit pixels.

s

Interlaced or non-interlaced output.

s

Video Input port

s

Accepts video inputs in CCIR 601/656 or

ITU-R 601/656, and stream decoding.

s

Optional 2:1 decimator

s

Stores captured video in off setting area of

the onboard frame buffer.

s

Video pass through to the onboard PAL/

NTSC encoder for full screen video images.

s

HSYNC and B/T generation or lock onto

external video timing source.

s

Video Pipeline

s

Two-tap interpolative horizontal filter.

s

Two-tap interpolative vertical filter.

s

Color space conversion (RGB to YUV and

YUV to RGB).

s

Programmable window size.

s

Chroma and color keying for integrated video

overlay.

s

Programmable two tap filter with gamma

correction or three tap flicker filter.

s

Progressive to interlaced scan converter.

s

Digital NTSC/PAL encoder

s

NTSC-M, PAL-M,PAL-B,D,G,H,I,PAL-N easy

programmable video outputs.

s

CCIR601 encoding with programmable color

subcarrier frequencies.

s

Line skip/insert capability

s

Interlaced or non-interlaced operation mode.

s

625 lines/50Hz or 525 lines/60Hz 8 bit

multiplexed CB-Y-CR digital input.

s

CVBS and R,G,B simultaneous analog

outputs through 10-bit DACs.

s

Cross color reduction by specific trap filtering

on luma within CVBS flow.

s

Power down mode available on each DAC.

STPC CONSUMER

3/51

Issue 1.2

s

PCI Controller

s

Fully compliant with PCI 2.1 specification.

s

Integrated PCI arbitration interface. Up to 3

masters can connect directly. External PAL

allows for greater than 3 masters.

s

Translation of PCI cycles to ISA bus.

s

Translation of ISA master initiated cycle to

PCI.

s

Support for burst read/write from PCI master.

s

0.33X and 0.5X CPU clock PCI clock.

s

ISA master/slave Interface

s

Generates the ISA clock from either

14.318MHz oscillator clock or PCI clock

s

Supports programmable extra wait state for

ISA cycles

s

Supports I/O recovery time for back to back

I/O cycles.

s

Fast Gate A20 and Fast reset.

s

Supports the single ROM that C, D, or E.

blocks shares with F block BIOS ROM.

s

Supports flash ROM.

s

Supports ISA hidden refresh.

s

Buffered DMA & ISA master cycles to reduce

bandwidth utilization of the PCI and Host bus.

NSP compliant.

s

IDE Interface

s

Supports PIO

s

Supports up to Mode 5 Timings

s

Transfer Rates to 22 MBytes/sec

s

Supports up to 4 IDE devices

s

Concurrent channel operation (PIO modes) -

4 x 32-Bit Buffer FIFOs per channel

s

Support for PIO mode 3 & 4.

s

Support for 11.1/16.6 MB/s, I/O Channel

Ready PIO data transfers.

s

Individual drive timing for all four IDE devices

s

Supports both legacy & native IDE modes

s

Supports hard drives larger than 528MB

s

Support for CD-ROM and tape peripherals

s

Backward compatibility with IDE (ATA-1).

s

Drivers for Windows and other Operating

Systems

s

Integrated peripheral controller

s

2X8237/AT compatible 7-channel DMA

controller.

s

2X8259/AT compatible interrupt Controller.

16 interrupt inputs - ISA and PCI.

s

Three 8254 compatible Timer/Counters.

s

Co-processor error support logic.

s

Power Management

s

Four power saving modes: On, Doze,

Standby, Suspend.

s

Programmable system activity detector

s

Supports SMM and APM.

s

Supports STOPCLK.

s

Supports IO trap & restart.

s

Independent peripheral time-out timer to

monitor hard disk, serial & parallel ports.

s

Supports RTC, interrupts and DMAs wake-up