DEVICES INCORPORATED

LT4420

Dual 32-Tap Transversal FIR Filter

Advance Information

LOGIC Devices Incorporated

1

Jan. 4, 2002 LDS.4420 C

Communications Products

165 MHz Max Data Rate

330 MHz Max Core Clock Rate

16-bit Data and Coefficients Paths

64-Tap FIR Filter, Cascadable for More Filter Taps

512 User-determined Coefficients Options Per Tap

Multiple Operating Modes: Dual Filter, Single Filter,

32-Bit Data or Coefficient, Double Rate, Auto

Decimate, Asymmetric Coefficient Set Expansion,

and Matrix Multiplication

24- or 48-bit Data Output with User-Defined

Rounding, Limiting, and Selecting

Supports up to 64 Interleaved Data Streams or a

Decimation Factor up to 64:1 for Increasing Filter

Taps

Interleaved Accumulator Capability Adds Increased

Flexibility When Interleaving

Built-in Cascade Ports Allow up to 16 Devices to be

Cascaded Without Any Additional Hardware.

Pre/Post-Modulator Stage with Built-in

User-programmable Direct Digital

Synthesizer (32-bit Accumulator)

Auto Decimation Mode Eliminates the Need

for External Coefficient, Transfer and

Accumulator Controllers

1K Word by 16-bit Capture Buffer. Supports

the Microcontroller in Calculating New

Coefficients in Adaptive Filtering

Microcontroller Interface

2.5 Volt Power Supply

272 BGA Package Ball Pitch 1.27mm

LVCMOS I/O Interface

5V Tolerant I/O

Performs 10 Billion Multiply Accumulates Per

Second

Industrial Temperature Available

The LT4420 is a 165 MHz Dual 16-bit 32-tap Digital Finite Impulse Response (FIR) Filter designed to meet

the filter requirements of tele/data communications and video imaging applications.

This device operates in eight different modes for various applications: Dual Filter, Single Filter, 32-Bit

Data, 32-Bit Coefficient, Double Rate, Auto Decimate, Asymmetric Coefficient Set Expansion, and Matrix

Multiplication.

Designed to take advantage of symmetric coefficient sets, the LT4420 can be configured as a single 64-tap

symmetric FIR filter or a 32-tap asymmetric FIR filter. A 4K-tap symmetric FIR filter may be realized with

a decimation factor of 64:1 utilizing the internal accumulator. When Asymmetric Coefficient Set Expansion

mode is used, a 2K-tap filter can be realized using a coefficient cycling technique; data rate is inversely

proportional to the number of taps. 32-Bit Data or 32-Bit Coefficient Mode will allow the use of either 32-bit

Data/16-bit Coefficients or 16-bit Data/32-bit Coefficients respectively. In addition, the core data rate can

be increased to 330MHz in Double Rate mode. In Auto Decimate mode, the device will self-configure for

the programmed decimation factor and automatically cycle through the pre-programmed coefficient sets;

interleaved Auto Decimation can also be realized.

Interleave/Decimation Registers (I/D Registers) allow up to 64 interleaved data streams to be fed directly

into the device and filtered without being separated externally.

The LT4420 contains on-chip memory to store 512 coefficient sets, 16 Round/Limit/Select Sets, and a

1K word Capture Buffer.

The Capture Buffer, used for calculating coefficient sets for adaptive filtering, allows the microcontroller to

access both input and output data streams without stopping the device.

A unique cascading structure allows for a cascade depth of sixteen devices. Unlimited cascading possible

with additional hardware.

The LT4420 also includes a user controlled Pre/Post-Modulator with a built in DDS and Sine/Cosine ROMs.

FEATURES

DESCRIPTION

DEVICES INCORPORATED

LT4420

Dual 32-Tap Transversal FIR Filter

Advance Information

LOGIC Devices Incorporated

2

Jan. 4, 2002 LDS.4420 C

Communications Products

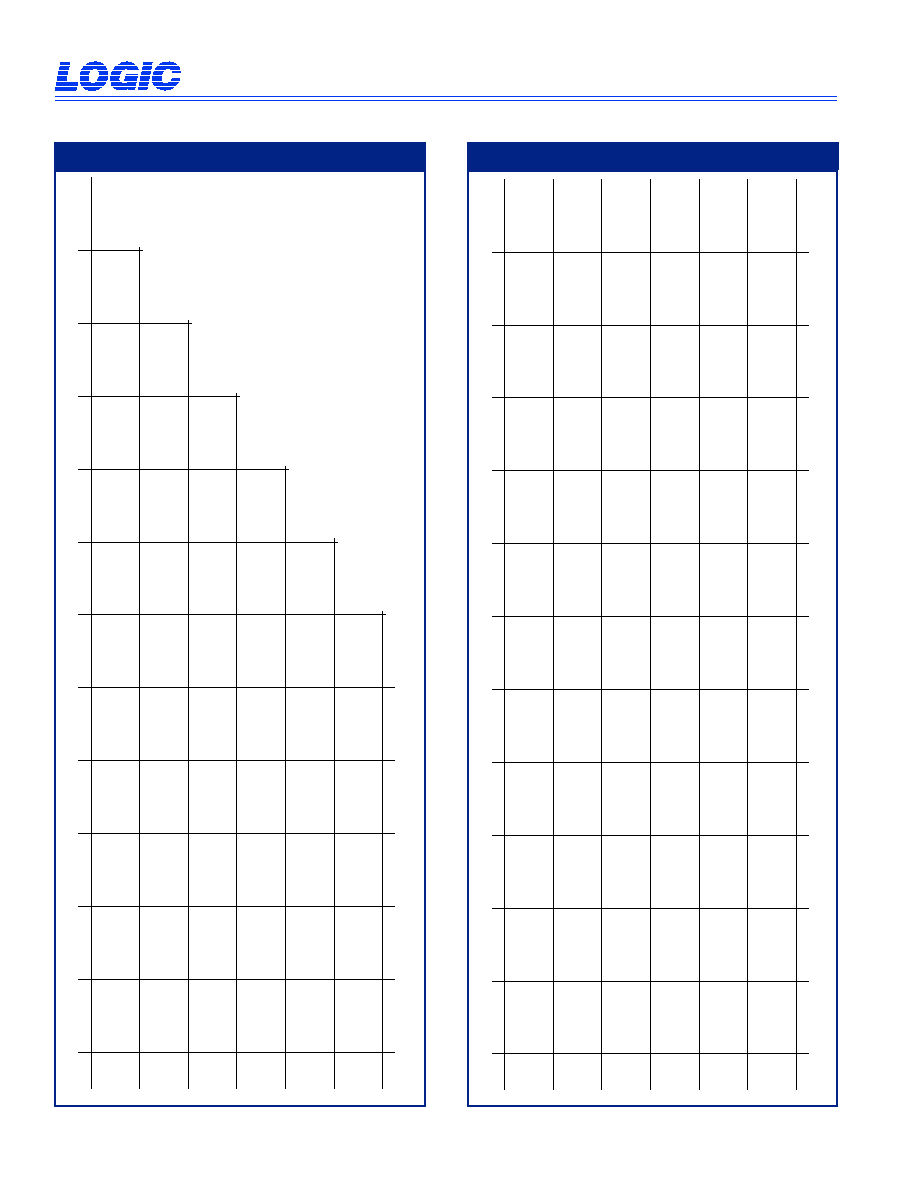

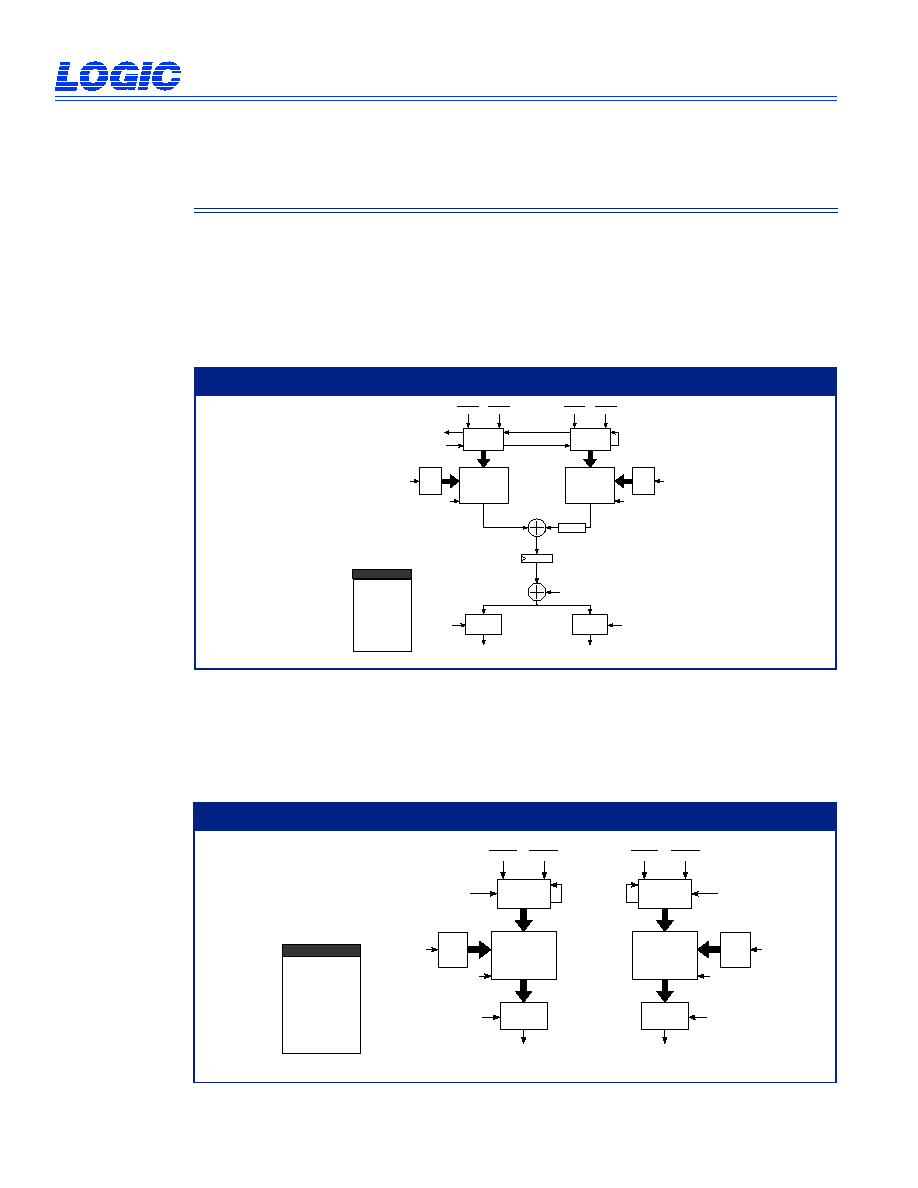

Figure 1. LT4420 Functional Block Diagram

"0

"

BZIF

Sixteen

COEFFICIENT

BANKS

(

5

1

2

s

e

t

s

x

1

6

-

b

i

t

s

/

b

a

n

k

)

DI

N

15-0

Sixteen

I/D

Register Cells

FILTER

A

(Sixteen

17 x 16-Bi

t

Multipliers

)

DAT

A

ALIG

N

AOUT

23-0

CASCADE

COMPENSATIO

N

DELAY

RL

S

CIRCUI

T

RL

S

CIRCUI

T

FILTER

B

(Sixteen

17 x 16-Bi

t

Multipliers

)

ASHEN

CL

K

ATXF

R

BTXF

R

BSHEN

INTERLEAVE

DECIMATION

CONTROL

FLAG LOGI

C

BUL

BOVF

AUL

AOVF

BL

L

AL

L

Sixteen

COEFFICIENT

BANKS

(

5

1

2

s

e

t

s

x

1

6

-

b

i

t

s

/

b

a

n

k

)

ACA

8-0

ACEN

9

BCA

8-0

BCEN

9

DAT

A

15-0

16

ADDR

14-0

15

R/

W

CS

Four

CAPTURE BUFFERs

(1K x 16-bit each)

DI

N

15-0

16

RI

N

15-0

16

AOUT

23-8

16

BI

O

23-8

16

CONFIGURATION/

CONTROL INTERFACE

RI

O

15-0

AACC

APASSA

APASSB

BACC

BPASSA

BPASSB

ARL

S

3-0

4

BRL

S

3-0

4

"0

"

AZIF

RI

N

15-0

CI

O

15-0

16

COE

16

16

24

AOE

BI

O

23

-

0

BOE

24

16

ROE

Modulator

(DDS)

Sixteen

I/D

Register Cells

Modulator

(DDS)

Modulator

(DDS)

Modulator

(DDS)

Resequencer

Resequencer

BSCAL

E

AFLT

BFLT

AMOD

BMOD

ASCAL

E

DEVICES INCORPORATED

LT4420

Dual 32-Tap Transversal FIR Filter

Advance Information

LOGIC Devices Incorporated

3

Jan. 4, 2002 LDS.4420 C

Communications Products

The LT4420 is a Dual 32-Tap Symmetric (16-Tap Asymmetric) Finite Impulse Response (FIR) Filter with

a Modulator Circuit that includes a Direct Digital Synthesizer (DDS). The filter core comprises Filter A

and Filter B. The two filter sides may be internally cascaded to create one 64-Tap Symmetric or one

32-Tap Asymmetric FIR Filter. There are two 16-bit data input ports (DIN15-0 and RIN15-0), two 16-bit I/O

ports (RIO15-0 and CIO15-0), one 24-bit I/O port (BIO23-0), and one dedicated output port (AOUT23-0).

Although the device is generally considered to be a 16-bit device (16-bit data/16-bit coefficient), the

ports may be combined for higher precision (see 32-Bit Data Mode, 32-Bit Coefficient Mode, and Double

Wide Output Mode in the Operating Modes section). All programming of the device is done through the

Configuration Registers via the 16-bit Configuration/Control Interface.

The LT4420 is made up of the following major functional blocks: Filter Cell, I/D Register Cell, Coefficient

Banks, Modulator, Round-Limit-Select Logic, Resequencer, and Microprocessor Control Interface. Other

functional blocks are discussed in the Functional Details section. Due to the high level of programmability,

the Functional Description discusses each functional block in detail.

A Filter Cell is essentially one 16 x 17-bit multiplier. There are sixteen Filter Cells in each filter side;

together there are thirty-two Filter Cells. Each Filter Cell calculates the product of a 17-bit data and a

16-bit coefficient; one 512 x 16-bit Coefficient Bank and two I/D Register Cells feed each Filter Cell (see

Figure 2).

ALU

A

B

ALU

A

B

1-64

1-64

1-64

1-64

DATA

REVERSAL

ALU

A

B

ALU

A

B

1-64

1-64

1-64

1-64

9

xCA

8-0

Coef0

Coef1

16

Coef511

Coef0

Coef1

16

Coef511

33

33

17

35

37

33

33

35

33

33

Coef0

Coef1

16

Coef511

Coef0

Coef1

16

Coef511

Reverse Data Out

Forward Data In

to Accumulator

16

16

16

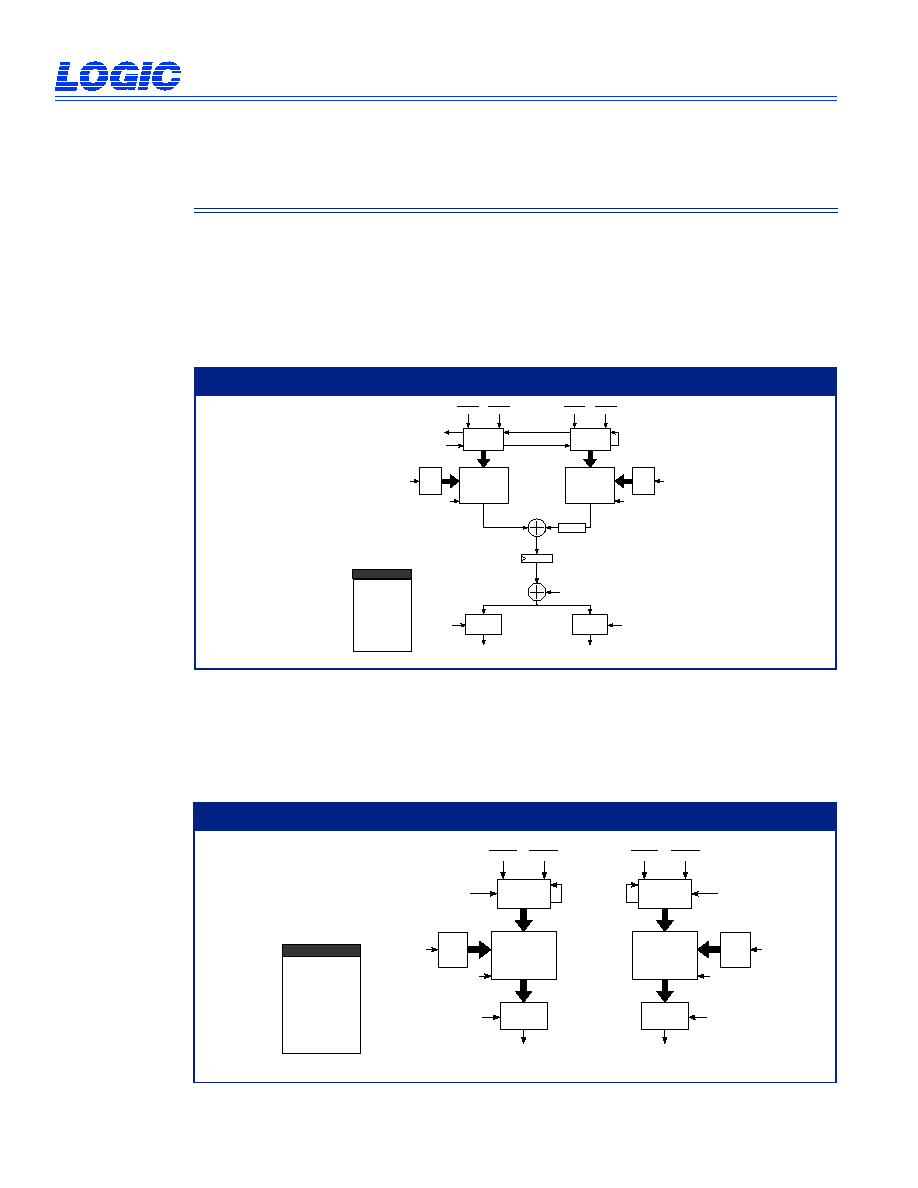

Figure 2. Filter A/B

Functional Description

DEVICES INCORPORATED

LT4420

Dual 32-Tap Transversal FIR Filter

Advance Information

LOGIC Devices Incorporated

4

Jan. 4, 2002 LDS.4420 C

Communications Products

The I/D Register Cell makes possible various filtering techniques. Utilizing the internal ALU and feedback

path, the user may take advantage of symmetric coefficient sets thus doubling the number of taps (see

Figures 15 and 16). The 64-stage pipeline register per I/D Register Cell allows for interleaving up to 64

channels or decimating by a factor of 64.

One Coefficient Bank is provided for each multiplier; there are thirty-two Coefficient Banks total each storing

512 16-bit coefficients. Once the coefficients are loaded and stored, they are addressed through the

ACA

8-0

and BCA

8-0

address buses and can be changed on every cycle to support adaptive, interleaved,

multirate filtering. Coefficient Banks are double buffered and a full coefficient set is bank loaded after the

last coefficient of that set is loaded, thus supporting the ability to update a particular address while it is

in use. A set is considered to be 32 coefficients in Single Filter Mode or 16 coefficients in Dual Filter

Mode. Coefficients are loaded through the Configuration/Control Interface. The Output Circuitry allows for

numerous data routing and control options (see Figure 3).

Functional Description

AACC

A ACCM

"0"

46

46

BACC

46

B ACCM

"0"

BSCALE

ARLS

3-0

BRLS

3-0

4

4

ALIGN

24

BIO

23-0

BOE

from Filter A Core

46

CASCADE

COMPENSATING

DELAY

46

ROUND

LIMIT

SELECT

MODULATOR

ROUND

LIMIT

SELECT

MODULATOR

RESEQUENCER

AOUT

23-0

24

AOE

RESEQUENCER

from Filter B Core

47

AFLT

BFLT

AMOD

BMOD

24

ASCALE

Figure 3. Output Circuitry

DEVICES INCORPORATED

LT4420

Dual 32-Tap Transversal FIR Filter

Advance Information

LOGIC Devices Incorporated

5

Jan. 4, 2002 LDS.4420 C

Communications Products

The Modulator block may be used at either the input or output of the device. The pre- or post-modulators

(demodulators) can apply conventional amplitude modulation (AM), swept AM, phase modulation (PM),

quadrature AM, or frequency modulation (FM) to the data stream at a user-programmed carrier frequency.

They can also demodulate an incoming AM data stream and feed the results to the filter module for post

processing, such as baseband filtering. In conjunction with the filter module, the modulators also support

carrier frequency translation (heterodyning).

If greater input precision is desired, the user may configure the device to accept 32-bit data and 16-bit

coefficients (32-Bit Data Mode) or 32-bit coefficients and 16-bit data (32-Bit Coefficient Mode) while halving

the available number of filter taps. In addition, to compensate for the extra input precision, the output

precision may also be increased from 24 bits to 48 bits (Double Wide Output Mode).

Cascade ports (RIN15-0, RIO15-0, CIO15-0) facilitate the cascading of multiple devices. Access to the

Internal Summer through the BIO23-0 port and a Cascade Delay are provided for cascading up to 15

additional devices without the need for any extra hardware. Thus a 1,024-Tap Symmetric FIR can be

constructed and operated at full rate; a 65,536-Tap Symmetric FIR, when decimating by a factor of 64.

The I/D Register Cells feed the ALU inputs. They allow the device to facilitate interleaving up to 64 channels

and/or decimating by a factor of up to 64, in manual or operate in Auto-decimation Mode. There are 64

I/D Register Cells, thirty-two in the forward path and thirty-two in the reverse path. Each I/D Register Cell

contains a variable length delay of one through 64. This delay is automatically set and is based on the

interleave and decimation factors. Although the device is capable of handling 64 interleaved channels or a

decimation factor of up to 64, both cannot be implemented at the same time. The product of both must be

within 64, thus the limit is written as follows:

(Interleave Factor) x (Decimation Factor) < 64

i.e., (INTLV + 1) x (DECI + 1) < 64

For example, if one channel and no decimation are desired, the I/D Register Cell delay is automatically

set to one. If four channels and no decimation are desired, the I/D Register Cell delay is automatically

set to four. If eight channels and a decimation factor of eight are desired, the I/D Register Cell delay is

automatically set to 64.

Bits 8�13 of Configuration Register 47F3H and 47F4H are used to enter the number of desired channels to

be interleaved for Filter A and Filter B, respectively. If no interleaving is desired, bits 8-13 of the appropriate

Configuration Register must be set to 0. If two channels of interleaving are desired, bits 8-13 must be set to

1 and so on. A maximum of 64 channels may be interleaved.

Bits 0-5 of Configuration Register 47F3H and 47F4H are used to enter a decimation factor for Filter A and

Filter B respectively. If no decimation is desired, bits 0-5 of the appropriate Configuration Register must be

set to 0. If a decimation factor of two is desired, bits 0-5 of the appropriate Configuration Register must be

set to 1 and so on. The maximum decimation factor is 64.

Functional Description

I/D Register Cell

DEVICES INCORPORATED

LT4420

Dual 32-Tap Transversal FIR Filter

Advance Information

LOGIC Devices Incorporated

6

Jan. 4, 2002 LDS.4420 C

Communications Products

The ALUs are part of the I/D Register Cell and allow for doubling the number of taps when coefficients

of symmetry are used by pre-adding data values which are then multiplied by a common coefficient (see

Figure 5 and 6). The ALUs can perform the following operations: A+B, B-A, A+0, B+0. A+B is used

with even-symmetric coefficient sets. B-A is used with odd-symmetric coefficient sets. A+0 and B+0 are

used primarily when implementing interpolation. Bits 2-0 of Configuration Register 47F1H determine the

operation of the ALUs in Filter A. Bits 2-0 of Configuration Register 47F2H determine the operation of the

ALUs in Filter B. Thus, a 64-tap filter may be constructed with the thirty-two multipliers.

Functional Description

ALU

A

B

ALU

A

B

CENTER TAP COE

CENTER TAP - (N+1) COE

1-64

1-64

1-64

1-64

DAT

A

REVERSAL

ALU

A

B

ALU

A

B

CENTER TAP COE

CENTER TAP - (N+1) COE

1-64

1-64

1-64

1-64

DAT

A

REVERSAL

Delay Stage N�1

ALU

A

B

ALU

A

B

CENTER TAP - (N+1) COE

1-64

1-64

1-64

1-64

DAT

A

REVERSAL

EVEN-TAP MODE

ODD-TAP MODE

ODD-TAP INTERLEAVE MODE

2

CENTER TAP COE

2

Delay Stage N

N = DECIMATION FACTOR

1

2

3

4

5

6

7

8

Even-Tap, Even-Symmetric

Coefficient Set

Odd-Tap, Even-Symmetric

Coefficient Set

1

2

3

4

5

6

7

8

Even-Tap, Odd-Symmetric

Coefficient Set

1

2

3

4

5

6

7

Figure 5. Symmetric Coefficient Set Examples

Figure 6. I/D Register Data Paths

ALU

DEVICES INCORPORATED

LT4420

Dual 32-Tap Transversal FIR Filter

Advance Information

LOGIC Devices Incorporated

7

Jan. 4, 2002 LDS.4420 C

Communications Products

The Data Reversal blocks (see Figure 7) handle data resequencing for Data Reversal and Interleaved Data

Reversal, enabling the LT4420 to take advantage of symmetrical coefficients while decimating. The Data

Reversal block can also act as a simple delay RAM for Cascading, Single Filter Mode, and Asymmetric

Coefficient Set Expansion Mode. Data Reversal is enabled by bit 5 of Control Register 47F1H and bit 5 of

Control Register 47F2H for Filter A and Filter B respectively. When Auto-decimation is enabled, all the data

reversal control is handled by the LT4420 once the part is synchronized to the data stream by a falling

edge on xTXFR. When the user chooses to use manual decimation, xTXFR must be pulsed low every

((DECI + 1) x (INTLV + 1)) clock cycles and held low for INTLV + 1 clock cycles. When Data Reversal

is enabled, the functions of these blocks are two LIFOs for each interleaved data channel. While the

LIFO A for the current data channel is being filled, the LIFO B for that same channel is being read out.

The xTXFR signal in this case simply reverses the function of the two LIFOs every ((INT Factor) x (DEC

Factor)) clock cycles.

The coefficient banks store the coefficients, which feed into the multipliers in Filter A and Filter B. There

is a separate bank for each multiplier. Each bank can hold 512 16-bit coefficients. The banks are loaded

through the Configuration/Control Interface and normally directly addressed through the xCA address buses

except when in Auto-Decimation Mode. In Auto-decimation mode, the sequencing of the coefficients is

done automatically with the xCA address acting as a starting offset. Coefficient loading is discussed in the

Configuration/Control Interface section.

The Scale function should be used only in 32-bit Data Mode and 32-bit Coefficient Mode. In all other

modes, Scale should be disabled where it will not affect the data. When bit 3 of Configuration Register

47F0H is HIGH, Scale is enabled. When bit 3 of Configuration Register 47F0H is LOW, Scale is disabled.

The purpose of the Scale Circuitry is to properly scale Filter B's 46-bit data and combine it with Filter A's

46-bit data for a full scale 47-bit result. The Filter B 46-bit data is right shifted by twelve bit positions and

properly sign extended (BSCALE in block diagram) before being added to Filter A's 46-bit data, which is

left-shifted by four bits (ASCALE in block diagram). This shifting provides the proper relative binary weighting

of Filters A and B, while retaining enough format overhead to support 64-fold decimation.

When cascading, the Compensation Delay circuitry properly compensates for the extra delay created

when adding extra devices. This circuitry is a variable length delay which can add a delay of up to 64

to the pipeline, thus compensating for up to fifteen extra devices. When adding one extra device, the

compensating delay will be automatically set to a length of five. When adding two extra devices, the

compensating delay will automatically be set to a length of ten and so on. This is controlled by setting bits

8-11 of Configuration Register 47F0H; this setting will configure the Compensating Delay to properly adjust

to the position of the current LT4420 within the cascade chain.

Functional Description

Coefficient

Banks

Scale

Compensation

Delay

Figure 7. Data Reversal

Data Reversal

DEVICES INCORPORATED

LT4420

Dual 32-Tap Transversal FIR Filter

Advance Information

LOGIC Devices Incorporated

8

Jan. 4, 2002 LDS.4420 C

Communications Products

F

47

F

46

F

45

F

44

F

43

F

42

F

41

F

40

F

39

F

38

F

37

F

36

F

35

F

34

F

33

F

32

F

31

F

30

F

29

F

28

F

27

F

26

F

25

F

24

F

23

F

22

F

21

F

20

F

19

F

18

F

17

F

16

F

15

F

14

F

13

F

12

F

11

F

10

F

09

F

08

F

07

F

06

F

05

F

04

F

03

F

02

F

01

F

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

11000

10111

10110

10101

10100

10011

10010

10001

10000

01111

01110

01101

01100

01011

01010

01001

01000

00111

00110

00101

00100

00011

00010

00001

00000

SLCT

4-0

F

47

F

46

F

45

F

44

F

43

F

42

F

41

F

40

F

39

F

38

F

37

F

36

F

35

F

34

F

33

F

32

F

31

F

30

F

29

F

28

F

27

F

26

F

25

F

24

F

23

F

22

F

21

F

20

F

19

F

18

F

17

F

16

F

15

F

14

F

13

F

12

F

11

F

10

F

09

F

08

F

07

F

06

F

05

F

04

F

03

F

02

F

01

F

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

22

S

21

S

20

S

19

S

18

S

17

S

16

S

15

S

14

S

13

S

12

S

11

S

10

S

09

S

08

S

07

S

06

S

05

S

04

S

03

S

02

S

01

S

00

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

S

23

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

11000

10111

10110

10101

10100

10011

10010

10001

10000

01111

01110

01101

01100

01011

01010

01001

01000

00111

00110

00101

00100

00011

00010

00001

00000

SLCT

4-0

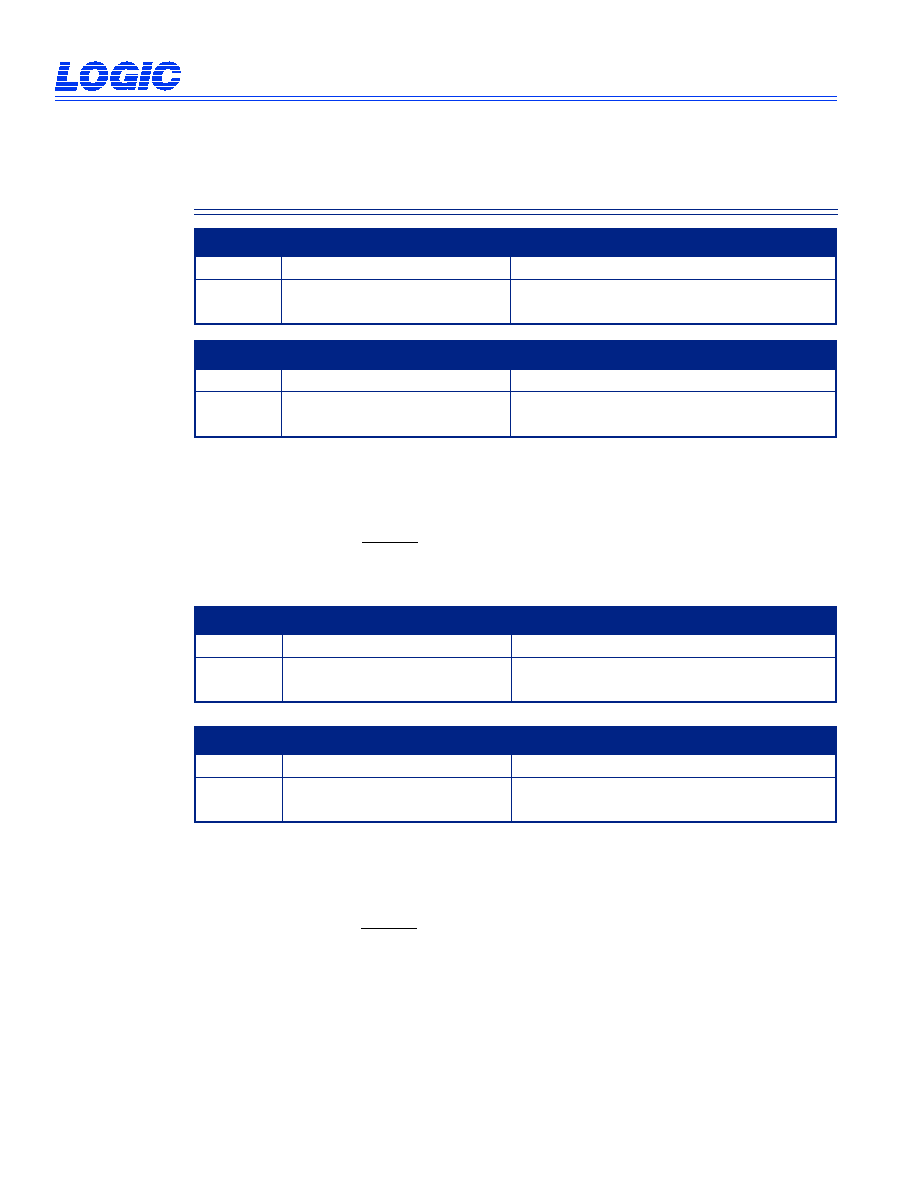

Table 1. Output Select Control

Table 2. Cascade Select Control

DEVICES INCORPORATED

LT4420

Dual 32-Tap Transversal FIR Filter

Advance Information

LOGIC Devices Incorporated

9

Jan. 4, 2002 LDS.4420 C

Communications Products

When cascading, the Align Circuitry is used to properly re-align the 24-bit BIO23-0 input back into the

48-bit filter sum. Filter B's Select Circuitry will no longer be used as discussed in the RLS discussion.

The selected 5-bit Select Register value will determine where the incoming 24-bit cascaded data will be

arranged within the 48-bit range inside the core (see Table 2). The MSB of the 24-bit word will be properly

sign extended to fill the 48-bit space. Anything smaller than the LSB of the 24-bit word will be zero filled

to fill the 48-bit space.

A Round/Limit/Select (RLS) Circuitry (see Figure 8) is provided on both AOUT23-0 and BIO23-0 ports

for programmable output control. Filter A RLS Circuitry is used for the overall filter in Single Filter Mode

operations. Both RLS Circuitry sections are programmable and can each store sixteen round values,

sixteen upper limit values, sixteen lower limit values, and sixteen select (windowing) schemes.

The registers are selected by RLS3-0, where a value of zero would pick the first register (register 0) in all

four sections (round, upper limit, lower limit, and select). Selecting of the registers is appropriately pipeline

delayed to match the data flowing through the output section. For instance, if RLS3-0 is set to a value of

three, round register two will be selected. On the next clock cycle, the sum of round register two and the

core data is then passed through the limit circuit where the value in upper limit register two and lower limit

register two are used for limiting. On the next cycle, the window scheme found in select register two would

then be used to select the appropriate 24 bits of data passed from the limit circuit.

The purpose of the Round Circuitry is to add a 48-bit round or offset value to the 47-bit data being passed

from the core. In the case of Dual Filter Mode operations, there are two separate cores. Sixteen separate

round or offset values can be stored in the sixteen registers. The value of the selected register will then be

added to the 47-bit core data. The sum is then sent to the Limit Circuitry. The round register values are

programmed into the round registers through the Configuration/Control Interface.

Round/Limit/

Select Circuitry

Functional Description

AR0

AR1

48

5

4

ARLS

3-0

RND

LIMIT

48

24

48

FILTER A RLS

DATA IN

47

DATA OUT

48

SELECT

AR15

AS0

AS1

AS15

AUL0

AUL1

AUL15

ALL0

ALL1

ALL15

48

BR0

BR1

48

5

4

BRLS

3-0

FILTER B RLS

48

RND

LIMIT

48

24

48

DATA IN

47

DATA OUT

SELECT

BR15

BS0

BS1

BS15

BUL0

BUL1

BUL15

BLL0

BLL1

BLL15

48

Figure 8. RSL Circuitry

Data Align

DEVICES INCORPORATED

LT4420

Dual 32-Tap Transversal FIR Filter

Advance Information

LOGIC Devices Incorporated

10

Jan. 4, 2002 LDS.4420 C

Communications Products

The purpose of the Limit Circuitry is to prevent the data from either going above or below a specified

range. Sixteen separate upper limit values can be stored in the sixteen upper limit registers. Sixteen

separate lower limit values can be stored in the sixteen lower limit registers. The upper limit value must

be greater than or equal to the lower limit value for the Limit Circuitry to work properly. If the 48-bit data

passed from the Round Circuitry is above the upper limit value, the upper limit value will then be passed

onto the Select Circuitry. If the 48-bit data passed from the Round Circuitry is below the lower limit value,

the lower limit value will then be passed onto the Select Circuitry. If the 48-bit data passed from the Round

Circuitry is within the specified limits, the value will remain untouched and passed onto the Select Circuitry.

The upper and lower limit values are programmed into the upper and lower limit registers through the

Configuration/Control Interface.

The purpose of the Select Circuitry is to pass 24 bits of the 48-bit core data either to the Modulator

or directly to the Resequencer (if the Modulator is bypassed). Any 24-bit window may be selected by

storing and selecting a 5-bit window code programmed into the select registers. The 5-bit window code

is programmed into the select registers through the Configuration/Control Interface. The window code

table is shown in Table 1.

When the selected data are passed from the filter to the modulator, only the 24 most significant bits will

be accepted into the 24 MSBS of the 32-bit phase accumulator. Only the 16 most significant bits will

be accepted by the mixer.

The Resequencer is used to implement various data multiplexing formats for the following:

� data alignment for interleaved decimation

� data alignment for interleaved interpolation

The Reseqencer blocks of the LT4420 re-interleaves interpolated samples and properly spaces interleaved

decimated samples at the output of the LT4420. This block is required only when either decimating

or interpolating interleaved signals. When interpolating the Resequencer can properly resequence 2

interleaved data channels with any integer interpolation factor up to and including 16. For example, lets

say you have 2 interleaved channels interpolated by 2, the normal filter output is as follows:

A1, A2, B1, B2, A3, A4, B3, B4

When RESEN=1, RESEQ=1, and DEPTH=1, for the reseqencer, this is properly resequenced as follows:

A1, B1, A2, B2, A3, B3, A4, B4

When decimating, the reseqencer can properly handle all valid integer interleave/decimation possibilities.

For example, lets say you have 3 interleaved channels decimated by a factor of 2, the filters accumulator

normally outputs data as follows:

A1, B1, C1, C1, C1, C1, A2, B2, C2, C2, C2, C2

where the first data channels comes out every clock cycle while the last data channel is held multiple clock

cycles. In this case, the reseqencer delays each data channel a total of a decimation factor clock cycles.

For this example, the output is as follows:

A1, A1, B1, B1, C1, C1, A2, A2, B2, B2, C2, C2

Round/Limit/

Select Circuitry

Cont'd

Functional Description

Resenquencer

DEVICES INCORPORATED

LT4420

Dual 32-Tap Transversal FIR Filter

Advance Information

LOGIC Devices Incorporated

11

Jan. 4, 2002 LDS.4420 C

Communications Products

A digital modulator circuit, comprising a direct digital synthesizer (DDS) and a multiplier-accumulator, can

be enabled at the input or output of each filter. The following modulation techniques may be implemented:

1. Amplitude Modulation (AM)

2. Swept AM

3. Phase Modulation (PM)

4. Quadrature Amplitude Modulation (QAM)

5. Frequency Modulation (FM)

Each of the LT4420's two modulator modules comprises two cascaded 32-bit phase accumulators, a 16-bit

sinusoidal lookup table, and a mixer (multiplier-accumulator). To effect different types of modulation,

the user can feed various incoming data or programmable constants into the two phase accumulators.

The user also may configure the chip to supply filtered data to the mixer as follows:

DIN -> filter -> modulate -> AOUT

or to post-filter the output of the mixer as follows:

DIN -> modulate -> filter -> AOUT

The upper phase accumulator loop is closed, (i.e., it generates a digitized sawtooth ramp), for conventional

fixed-frequency amplitude modulation (AM), swept-frequency AM (sAM), phase modulation (PM), and 16-,

256-, or other rate quadrature AM (xQAM). The user can periodically reset the accumulation to a known

value by asserting a synchronizing signal. It is open (i.e. it operates as a simple 2-input nonaccumulating

adder), for frequency modulation or compound AM/FM schemes. In sAM, FSC enters this loop to set the

sweep rate, whereas PHI0 + FSC determines the initial frequency of each sweep. In the other modes, FSC

sets carrier frequency and the sum of PHI0 + FSC determines the starting phase of this accumulation.

The lower phase accumulator loop is closed for FM and sAM and open in the other modes. The user can

force the accumulation to a known value by periodically asserting a synchronizing signal. In AM, it adds a

fixed, user-defined phase offset value or two alternating phase offsets. For PM and xQAM, the user can

introduce a filtered or unfiltered (via ports RIO15-0 and CIO15-0) phase modulation data stream here.

For AM, the top accumulator's output restarts at PHI0 + FSC with the arrival of each synchronizing pulse

and increments, modulo 32 bits, by FSC on each enabled data clock cycle. The lower accumulator adds

a constant (a 32-bit concatenation of OFFSET1 and OFFSET2) or two alternating constants (left-justified

OFFSET1 and OFFSET2) to this phase. The lookup table then converts this phase into a sampled

sinusoid. The modulating signal is applied directly to the mixer stage from the chip's main data path, either

before or after the filter, as required by the user. Typical application:

� moduating signal input: DIN

� modulated signal output: AOUT

� carrier frequency: FSC

� initial carrier phase: FSC + PHI0 + OFFSET

Functional Description

Modulator

DEVICES INCORPORATED

LT4420

Dual 32-Tap Transversal FIR Filter

Advance Information

LOGIC Devices Incorporated

12

Jan. 4, 2002 LDS.4420 C

Communications Products

Coherent AM demodulation is simple: bring in the modulated data stream, mix it with the carrier frequency

at the proper phase offset, and low-pass filter the output to remove the spurious (2 x FSC) component.

For noncoherent AM demodulation, one needs to mix the incoming signal with both the sine and cosine

of the carrier, as in the xQAM discussion below, then reconstruct magnitude and phase from the resulting

I and Q components.

For sAM, the top accumulator's output restarts at PHI0 + FSC with the arrival of each synchronizing pulse

and increments, modulo 32 bits, by FSC on each enabled data clock cycle. The lower accumulator also

accumulates, with an initial addend of OFFSET. Again, the modulating signal is applied directly to the

mixer only, either before or after filtering. Typical application:

� moduating signal input: DIN

� modulated signal output: AOUT

� initial carrier frequency: FSC + PHI0

� sweep rate: FSC (typically much smaller than PHI0)

� initial carrier phase: FSC + PHI0 + OFFSET

By programming the CHIRP value via the Configuration/Control Interface, the user can determine the

duration and repetition rate of the sweep.

To generate an xQAM signal with a simple rectangular constellation, the user configures the modulator for

conventional (not swept) AM, but with alternating sine and cosine, rather than steady sine, output from the

lookup table (TBL = 010 instead of 000). By sending I and Q components alternately down the data path,

the user causes the multiplier accumulator in the mixer to generate the following data stream:

I(n) x cos(n)

Q(n) x sin(n) + I(n) x cos(n)

I(n+1) x cos(n+1)

Q(n+1) x sin(n+1) + I(n+1) x cos(n+1)

I(n+2) x cos(n+2)

Q(n+2) x sin(n+2) + I(n+2) x cos(n+2)

In xQAM, the output data rate is one-half of the incoming data component rate. To accommodate twice the

data rate shown, the user can process the I and Q channels separately in the A and B portions of the chip,

and combine the results at the chip's output port.

To demodulate an xQAM signal, the user turns off the accumulation in the mixer and brings in a single

data stream instead of the separate I and Q components shown above. If both halves of the chip are

used to process a single data channel, one will generate I and the other will generate Q, both at the

incoming data rate.

In PM, the user closes the upper accumulator loop to generate the carrier and feeds a filtered or unfiltered

modulating data stream into the lower accumulator. In this application, the amplitude modulation input

into the mixer will generally be a constant or slowly-changing variable (e.g., automatic gain control). The

carrier frequency is dictated by FSC, the initial phase by FSC + PHI0. The modulating data will enter the

chip on DIN and can be filtered either preceding or following modulation. The user can set the constant

or slowly-changing, AGC-controlled amplitude over the RIO15-0 data cascade bus, which is used as an

input in this application.

Functional Description

Modulator Cont'd

DEVICES INCORPORATED

LT4420

Dual 32-Tap Transversal FIR Filter

Advance Information

LOGIC Devices Incorporated

13

Jan. 4, 2002 LDS.4420 C

Communications Products

In FM, the user brings a 32-bit wide modulating signal into RIO15-0 (MSBs) and CIO15-0 (LSBs). FSC,

which is added to this value, determines the center frequency. The upper accumulator acts as a simple

2-input adder, and the lower accumulator loop is closed. The constant or AGC-controlled amplitude is set

by DIN, which can also be varied for a combined AM/FM modulation scheme, if desired. The modulator

can also be programmed to serve as a static gain adjustment stage.

Functional Description

Modulator

Cont'd

Figure 9. Modulator

DEVICES INCORPORATED

LT4420

Dual 32-Tap Transversal FIR Filter

Advance Information

LOGIC Devices Incorporated

14

Jan. 4, 2002 LDS.4420 C

Communications Products

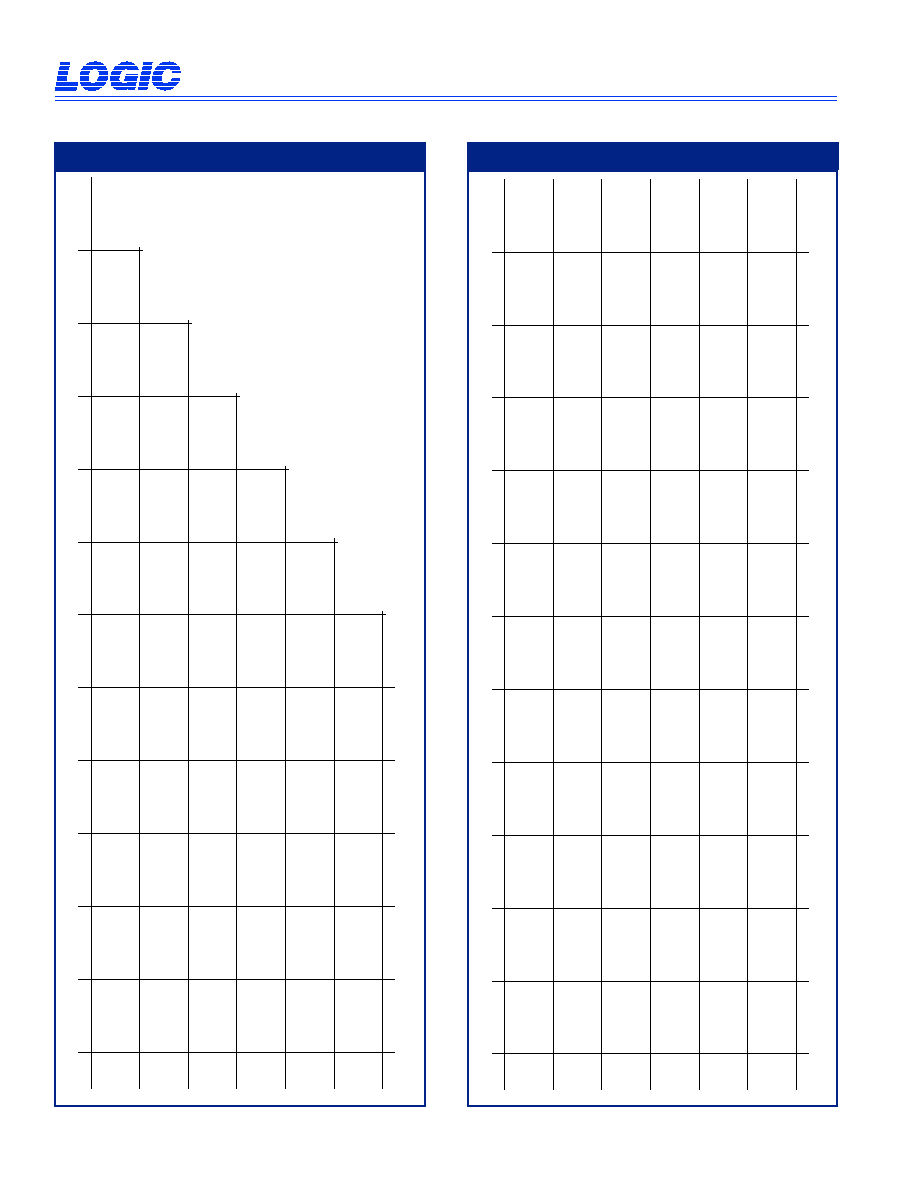

The user can cascade up to 16 devices without any additional hardware. This enables a group of sixteen

LT4420s to compute a single 1,024-Tap Symmetric FIR at full clock rate. If decimation is used, a

65,536-Tap FIR with a decimation of 64 is possible. When cascading, all devices must be in Single Filter

Mode. Cascading is implemented by chaining the LT4420's as follows (see Figure 10):

CIO15-0 of the first device should be connected to DIN15-0 of the next device, to complete the forward

data input path. RIN15-0 of the first device should be connected to RIO15-0 of the next device, to

complete the reverse data input path. BIO23-0 of the first device should be connected to AOUT23-0

of the next device, to combine the filter outputs of the devices. All additional devices are chained in

the same manner.

The last device in the cascade chain should have bit 0 of Configuration Register 47F0H set to 0, and

bits 11-8 of Configuration Register 47F0H set to 0. For all other devices in the cascade chain, bit 0 of

Configuration Register 47F0H must be set to 1. Bit 11-8 of Configuration Register 47F0H counts up as you

count back from the last device in the cascade chain.

Bits 11-8 of Configuration Register 47F0H compensate for the data path delay of the following devices in

the cascade chain. For each additional device in the cascade chain, the latency of the filter is increased

by 8 clock cycles.

For each stage, the partial result is limited to 24 bits. However the 24 bits passed between parts is first run

through the RLS circuitry, then re-aligned in the previous part through the align circuitry. The align circuitry

uses the Filter B select information to realign that result into the current 48 bit partial result. This allows for

very flexible bit growth control across multiple devices.

The LT4420 includes four capture buffers which can be used in calculating adaptive filtering coefficients

or to aid in debugging the root cause of overflow and limiting conditions. There are a total of four 256 x

16-bit memory buffers that collect data from the DIN15-0, RIN15-0, AOUT23-0 and BIO23-0 data paths.

According to their input source, these memories are separated into Filter A and Filter B capture RAM

and controlled individually in pairs with the corresponding configuration register. There are two operation

modes for these capture memories.

The first is Capture on Demand, used for adaptive filtering, where the memory starts to capture data when

a xSYNC signal is received and progresses until the memories are full.

Functional Description

Cascading

DIN

15-0

DOUT

23-0

I/D

REGISTERS

FILTER A

I/D

REGISTERS

FILTER B

CASCADE

COMPENSATION

DELAY

RLS

CIRCUIT

ATXFR

ASHEN

AACC

ARLS

3-0

COEF

BANK

COEF

BANK

ACA

RIO

15-0

BTXFR

BSHEN

BACC

BCA

CIO

15-0

RIN

15-0

BIO

23-0

BRLS

3-0

DATA

ALIGN

DIN

15-0

DOUT

23-0

I/D

REGISTERS

FILTER A

I/D

REGISTERS

FILTER B

RLS

CIRCUIT

ATXFR

ASHEN

AACC

ARLS

3-0

COEF

BANK

COEF

BANK

ACA

RIO

15-0

BTXFR

BSHEN

BACC

BCA

"0"

BSCALE

ASCALE

BSCALE

ASCALE

Figure 10. Cascade Mode-Two Devices

Capture Buffer

DEVICES INCORPORATED

LT4420

Dual 32-Tap Transversal FIR Filter

Advance Information

LOGIC Devices Incorporated

15

Jan. 4, 2002 LDS.4420 C

Communications Products

The second is Capture on-the-Fly, used in debugging where the memory starts to capture data once the

chip is initialized and progresses until one of the status flags (AOVF, BOVF, ALL, AUL, BLL, BUL) is set.

Even though the Capture on-the-Fly stops based on the setting of a flag, the address is realigned in this

mode, so that the earliest data before the halt condition occurred is in the capture buffer at offset zero.

Once the memory is full, a trigger condition occurs that can be monitored by the Configuration/Control

Interface. The memory can then be read if desired. When a memory is read by the Configuration/Control

Interface, it responds to the control bus, which provides the address with a read command. Output data

shall be available at the bus during the same CS cycle.

When either memory is full or a trigger condition occurs, the memory will stop writing data. It also

stores the current status of the overflow and limit flags into the status register for examination by the

Configuration/Control Interface.

The capture memory is always running if it is set to the Capture On-the-Fly Mode and the trigger condition

is never met. To save power, use the capture on demand mode, which exercises the memory only once.

In certain cases, the device can have overflow conditions that will trigger the overflow flags to indicate

that an overflow has occurred. There are six overflow flags pins on the part that will be triggered high

to indicate an overflow. The 46-bit accumulator in Filter A and Filter B can reach saturation, at which

point an overflow condition exists. The event will cause the AOVF or BOVF output flags to be set HIGH

two clock cycles after the overflow.

The AUL and BUL flags work similarly in that they both go HIGH two clock cycles after the data passing

through the limit circuitry is greater than the selected Upper Limit register value.

The ALL and BLL flags work similarly in that they both go HIGH two clock cycles after the data passing

through the limit circuitry is lower than the selected Lower Limit register value.

All flags are dynamically synchronous, thus when a flag is triggered active, it will remain HIGH for one

clock cycle.

Capture Buffer

Cont'd

Flag Logic

Functional Description

DEVICES INCORPORATED

LT4420

Dual 32-Tap Transversal FIR Filter

Advance Information

LOGIC Devices Incorporated

16

Jan. 4, 2002 LDS.4420 C

Communications Products

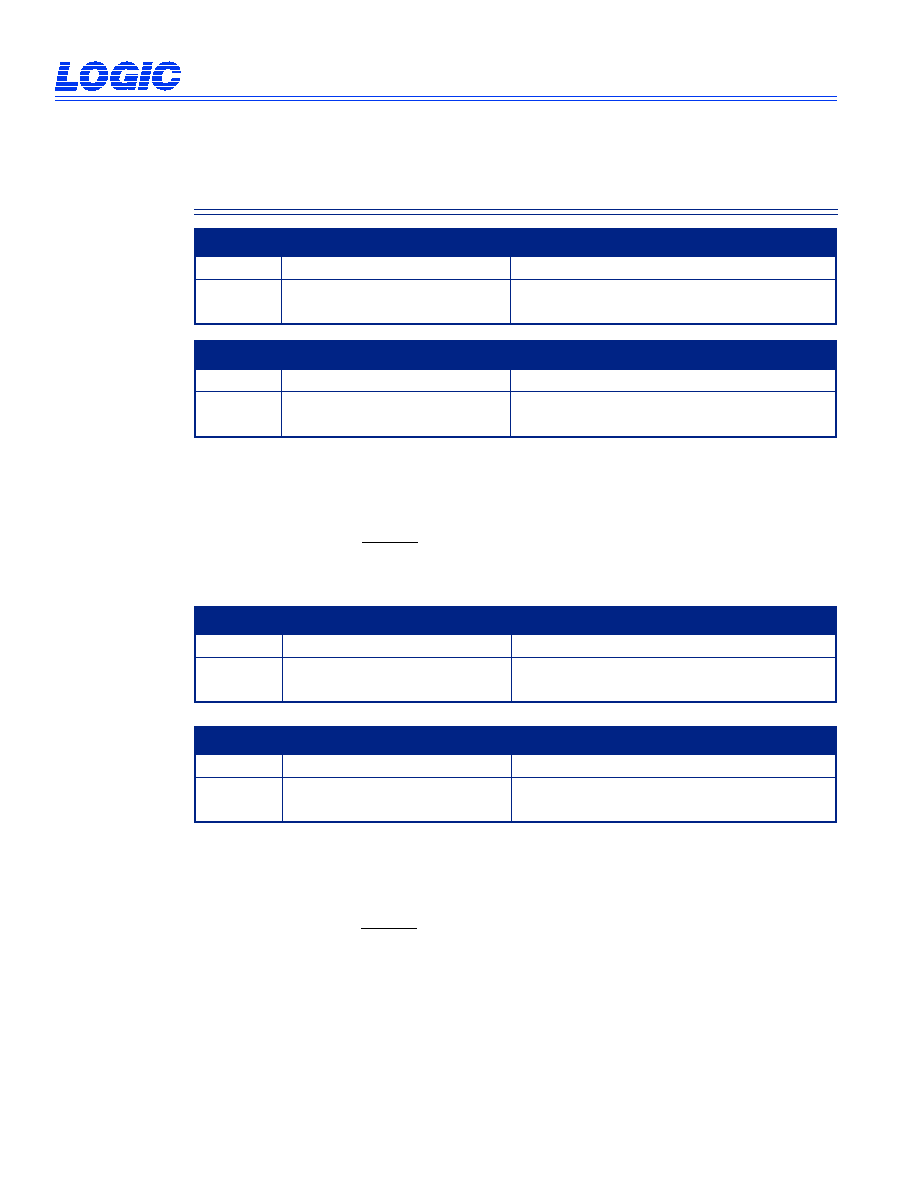

When bit 1 in Configuration Register 47F0H is set LOW, the device is in Single Filter Mode (see Figure 11)

where thirty-two independent multipliers are utilized to construct a 64-tap symmetrical FIR filter or a 32-tap

asymmetrical FIR filter. DIN15-0 is the data input for the filter and AFLT23-0 is the data output for the filter.

Cascade ports (RIN15-0, RIO15-0, CIO15-0) are provided to facilitate the cascading of multiple devices.

Access to the Internal Summer through the BIO24-0 port and a Cascade Delay are provided for cascading

up to 15 additional devices without the need for any extra hardware. Thus a 1,024-Tap Symmetric FIR can

be constructed and operated at full rate; 65,536-Tap Symmetric FIR when decimating by a factor of 64.

When bit 1 in Configuration Register 47F0H is set HIGH, the device is in Dual Filter Mode (see Figure 12),

in which two separate 32-tap symmetric FIRs or two separate 16-tap asymmetric FIRs can be constructed.

DIN15-0 is the data input and DOUT23-0 is the data output for Filter A. Either RIN15-0 or DIN15-0 can be

the data input for filter B, and BIO23-0 is the data output.

Operating Modes

Single Filter

Mode

Figure 11. Single Filter Mode

DIN

15-0

I/D

REGISTERS

FILTER A

I/D

REGISTERS

FILTER B

ATXFR

ASHEN

AACC

COEF

BANK

COEF

BANK

ACA

BTXFR

BSHEN

BACC

BCA

AFLT

23-0

RLS

CIRCUIT

ARLS

3-0

BLFT

23-0

RLS

CIRCUIT

BRLS

3-0

"0"

RIO

15-0

DFSUM

= 1

DBLWIDE = 0

MTX

= 0

FLTR

= 0

BSCALE

= 0

COESEL = x

FLTR

= 0

CASC

= 0

Control Settings

BSCALE

Dual Filter

Mode

Figure 12. Dual Filter Mode

DIN

15-0

I/D

REGISTERS

FILTER A

I/D

REGISTERS

FILTER B

ATXFR

ASHEN

AACC

COEF

BANK

COEF

BANK

ACA

8-0

BTXFR

BSHEN

BACC

BCA

8-0

AFLT

23-0

RLS

CIRCUIT

ARLS

3-0

BFLT

23-0

RLS

CIRCUIT

BRLS

3-0

RIN

15-0

DFSUM

= 0

DBLWIDE = 0

MTX

= 0

FLTR

= 0

BSCALE

= 0

COESEL = x

FLTR

= 1

CASC

= 0

LEGEND

DEVICES INCORPORATED

LT4420

Dual 32-Tap Transversal FIR Filter

Advance Information

LOGIC Devices Incorporated

17

Jan. 4, 2002 LDS.4420 C

Communications Products

When bit 6 in Configuration Register 47F0H is set HIGH, the device is in Auto-decimation Mode. Auto-

decimation works in either Single Filter Mode, dual filter mode, 32-Bit Data Mode, or 32-Bit Coefficient

Mode. In Single Filter Mode, the user should program filters A and B identically. When using Auto-

decimation, the device takes care of coefficient addressing and data routing for a given decimation factor.

ASHEN and BSHEN should be set LOW in this mode. A HIGH to LOW transition of ATXFR and BTXFR

should only be used once to synchronize the device with the start of valid data, after initially loading the

device with configuration/control data. Each additional falling ATXFR or BTXFR will resynchronize the part.

ACA

8-0

and BCA

8-0

will not function as a coefficient address during this mode but rather, it will provide the

starting coefficient addresses for the coefficient addressing sequence. For example, if four coefficient sets

are to be used and ACA

8-0

and BCA

8-0

are set to a value of 3, then coefficient sets 3, 4, 5, and 6 will be

automatically addressed and cycled through.

To determine the number of coefficient sets that will be used, the user must first determine the decimation