| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: E7500 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Intel

Æ

E7500 Chipset

Datasheet

Intel

Æ

E7500 Memory Controller Hub (MCH)

February 2002

Document Number:

290730-001

2

Datasheet

Information in this document is provided in connection with Intel

Æ

products. No license, express or implied, by estoppel or otherwise, to any intellectual

property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability

whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to

fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not

intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for

future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel

Æ

E7500 chipset MCH component may contain design defects or errors known as errata which may cause the product to deviate from

published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained by calling

1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

IIntel, Intel NetBurst and the Intel logo are trademarks or registered trademarks of Intel corporation or its subsidiaries in the United States and other

countries.

*Other names and brands may be claimed as the property of others.

Copyright© 2002, Intel Corporation

Datasheet

3

Contents

1

Introduction

................................................................................................................11

1.1

Glossary of Terms ...............................................................................................11

1.2

Reference Documents.........................................................................................12

1.3

Intel

Æ

E7500 Chipset System Architecture..........................................................12

1.3.1

Intel

Æ

82801CA I/O Controller Hub 3-S (ICH3-S)...................................13

1.3.2

Intel

Æ

82870P2 PCI/PCI-X 64-bit Hub 2 (P64H2)...................................14

1.4

Intel

Æ

E7500 MCH Overview...............................................................................14

1.4.1

Processor System Interface ...................................................................15

1.4.2

Main Memory Interface...........................................................................15

1.4.3

Hub Interface_A (HI_A) ..........................................................................15

1.4.4

Hub Interface_B≠D (HI_B≠D).................................................................16

1.4.5

MCH Clocking ........................................................................................16

1.4.6

SMBus Interface.....................................................................................16

2

Signal Description

...................................................................................................17

2.1

System Bus Interface Signals .............................................................................19

2.2

DDR Channel A Signals ......................................................................................22

2.3

DDR Channel B Signals ......................................................................................23

2.4

Hub Interface_A Signals......................................................................................24

2.5

Hub Interface_B Signals......................................................................................25

2.6

Hub Interface_C Signals .....................................................................................26

2.7

Hub Interface_D Signals .....................................................................................27

2.8

Clocks, Reset, Power, and Miscellaneous Signals .............................................28

2.9

Pin States During and After Reset ......................................................................28

3

Register Description

...............................................................................................31

3.1

Register Terminology ..........................................................................................31

3.2

Platform Configuration.........................................................................................32

3.3

General Routing Configuration Accesses ...........................................................33

3.3.1

Standard PCI Configuration Mechanism ................................................33

3.3.2

Logical PCI Bus 0 Configuration Mechanism .........................................34

3.3.3

Primary PCI Downstream Configuration Mechanism .............................34

3.3.4

HI_B, HI_C, HI_D Bus Configuration Mechanism ..................................34

3.4

Sticky Registers...................................................................................................35

3.5

I/O Mapped Registers .........................................................................................35

3.5.1

CONF_ADDR--Configuration Address Register ...................................35

3.5.2

CONF_DATA--Configuration Data Register..........................................36

3.6

DRAM Controller Registers (Device 0, Function 0).............................................37

3.6.1

VID--Vendor Identification Register (D0:F0) .........................................38

3.6.2

DID--Device Identification Register (D0:F0)..........................................38

3.6.3

PCICMD--PCI Command Register (D0:F0) ..........................................39

3.6.4

PCISTS--PCI Status Register (D0:F0) ..................................................40

3.6.5

RID--Revision Identification Register (D0:F0) .......................................41

3.6.6

SUBC--Sub-Class Code Register (D0:F0) ............................................41

3.6.7

BCC--Base Class Code Register (D0:F0).............................................41

3.6.8

MLT--Master Latency Timer Register (D0:F0) ......................................42

4

Datasheet

3.6.9

HDR--Header Type Register (D0:F0).................................................... 42

3.6.10 SVID--Subsystem Vendor Identification Register (D0:F0) .................... 42

3.6.11 SID--Subsystem Identification Register (D0:F0) ................................... 43

3.6.12 MCHCFG--MCH Configuration Register (D0:F0).................................. 43

3.6.13 MCHCFGNS--MCH Memory Scrub and Initialization Configuration

Register (D0:F0)..................................................................................... 45

3.6.14 FDHC--Fixed DRAM Hole Control Register (D0:F0)............................. 46

3.6.15 PAM[0:6]--Programmable Attribute Map Registers (D0:F0).................. 47

3.6.16 DRB--DRAM Row Boundary Register (D0:F0) ..................................... 49

3.6.17 DRA--DRAM Row Attribute Register (D0:F0) ....................................... 50

3.6.18 DRT--DRAM Timing Register (D0:F0) .................................................. 51

3.6.19 DRC--DRAM Controller Mode Register (D0:F0) ................................... 52

3.6.20 CLOCK_DIS--CK/CK# Disable Register (D0:F0).................................. 53

3.6.21 SMRAM--System Management RAM Control Register (D0:F0) ........... 54

3.6.22 ESMRAMC--Extended System Management RAM Control Register

(D0:F0) ................................................................................................... 55

3.6.23 TOLM--Top of Low Memory Register (D0:F0) ...................................... 56

3.6.24 REMAPBASE--Remap Base Address Register (D0:F0)....................... 56

3.6.25 REMAPLIMIT--Remap Limit Address Register (D0:F0)........................ 57

3.6.26 SKPD--Scratchpad Data Register (D0:F0)............................................ 57

3.6.27 DVNP--Device Not Present Register (D0:F0) ....................................... 58

3.7

DRAM Controller Error Reporting Registers (Device 0, Function 1) ................... 59

3.7.1

VID--Vendor Identification Register (D0:F1) ......................................... 60

3.7.2

DID--Device Identification Register (D0:F1).......................................... 60

3.7.3

PCICMD--PCI Command Register (D0:F1) .......................................... 61

3.7.4

PCISTS--PCI Status Register (D0:F1).................................................. 61

3.7.5

RID--Revision Identification Register (D0:F1) ....................................... 62

3.7.6

SUBC--Sub-Class Code Register (D0:F1) ............................................ 62

3.7.7

BCC--Base Class Code Register (D0:F1)............................................. 63

3.7.8

MLT--Master Latency Timer Register (D0:F1) ...................................... 63

3.7.9

HDR--Header Type (D0:F1) .................................................................. 64

3.7.10 SVID--Subsystem Vendor Identification Register (D0:F1) .................... 65

3.7.11 SID--Subsystem Identification Register (D0:F1) ................................... 65

3.7.12 FERR_GLOBAL--Global Error Register (D0:F1)................................... 66

3.7.13 NERR_GLOBAL--Global Error Register (D0:F1) .................................. 67

3.7.14 HIA_FERR--Hub Interface_A First Error Register (D0:F1) ................... 68

3.7.15 HIA_NERR--Hub Interface_A Next Error Register (D0:F1)................... 69

3.7.16 SCICMD_HIA--SCI Command Register (D0:F1) .................................. 70

3.7.17 SMICMD_HIA--SMI Command Register (D0:F1).................................. 71

3.7.18 SERRCMD_HIA--SERR Command Register (D0:F1) .......................... 72

3.7.19 SYSBUS_FERR--System Bus First Error Register (D0:F1).................. 73

3.7.20 SYSBUS_NERR--System Bus Next Error Register (D0:F1)................. 74

3.7.21 SCICMD_SYSBUS--SCI Command Register (D0:F1).......................... 75

3.7.22 SMICMD_SYSBUS--SMI Command Register (D0:F1) ......................... 76

3.7.23 SERRCMD_SYSBUS--SERR Command Register (D0:F1).................. 77

3.7.24 DRAM_FERR--DRAM First Error Register (D0:F1) .............................. 78

3.7.25 DRAM_NERR--DRAM Next Error Register (D0:F1) ............................. 78

3.7.26 SCICMD_DRAM--SCI Command Register (D0:F1).............................. 79

3.7.27 SMICMD_DRAM--SMI Command Register (D0:F1) ............................. 79

3.7.28 SERRCMD_DRAM--SERR Command Register (D0:F1)...................... 80

Datasheet

5

3.7.29 DRAM_CELOG_ADD--DRAM First Correctable Memory Error

Address Register (D0:F1).......................................................................80

3.7.30 DRAM_UELOG_ADD--DRAM First Uncorrectable Memory Error

Address Register (D0:F1).......................................................................81

3.7.31 DRAM_CELOG_SYNDROME--DRAM First Correctable Memory

Error Register (D0:F1)............................................................................81

3.8

HI_B Virtual PCI-to-PCI Bridge Registers (Device 2, Function 0) .......................82

3.8.1

VID2--Vendor Identification Register (D2:F0) .......................................83

3.8.2

DID2--Device Identification Register (D2:F0)........................................83

3.8.3

PCICMD2--PCI Command Register (D2:F0) ........................................84

3.8.4

PCISTS2--PCI Status Register (D2:F0) ................................................85

3.8.5

RID2--Revision Identification Register (D2:F0) .....................................86

3.8.6

SUBC2--Sub-Class Code Register (D2:F0) ..........................................86

3.8.7

BCC2--Base Class Code Register (D2:F0)...........................................87

3.8.8

MLT2--Master Latency Timer Register (D2:F0) ....................................87

3.8.9

HDR2--Header Type Register (D2:F0)..................................................88

3.8.10 PBUSN2--Primary Bus Number Register (D2:F0) ................................88

3.8.11 BUSN2--Secondary Bus Number Register (D2:F0) ..............................89

3.8.12 SUBUSN2--Subordinate Bus Number Register (D2:F0).......................89

3.8.13 SMLT2--Secondary Bus Master Latency Timer Register (D2:F0) ........90

3.8.14 IOBASE2--I/O Base Address Register (D2:F0).....................................91

3.8.15 IOLIMIT2--I/O Limit Address Register (D2:F0)......................................91

3.8.16 SEC_STS2--Secondary Status Register (D2:F0) .................................92

3.8.17 MBASE2--Memory Base Address Register (D2:F0) .............................93

3.8.18 MLIMIT2--Memory Limit Address Register (D2:F0) ..............................94

3.8.19 PMBASE2--Prefetchable Memory Base Address Register (D2:F0)......95

3.8.20 PMLIMIT2--Prefetchable Memory Limit Address Register (D2:F0).......95

3.8.21 BCTRL2--Bridge Control Register (D2:F0) ...........................................96

3.9

HI_B Virtual PCI-to-PCI Bridge Registers (Device 2, Function 1) .......................97

3.9.1

VID--Vendor Identification Register (D2:F1) .........................................98

3.9.2

DID--Device Identification Register (D2:F1)..........................................98

3.9.3

PCICMD--PCI Command Register (D2:F1) ..........................................99

3.9.4

PCISTS--PCI Status Register (D2:F1) ..................................................99

3.9.5

RID--Revision Identification Register (D2:F1) .....................................100

3.9.6

SUBC--Sub-Class Code Register (D2:F1) ..........................................100

3.9.7

BCC--Base Class Code Register (D2:F1)...........................................101

3.9.8

HDR--Header Type Register (D2:F1)..................................................101

3.9.9

SVID--Subsystem Vendor Identification Register (D2:F1) ..................102

3.9.10 SID--Subsystem Identification Register (D2:F1) .................................102

3.9.11 HIB_FERR--Hub Interface_B First Error Register (D2:F1) .................103

3.9.12 HIB_NERR--Hub Interface_B Next Error Register (D2:F1).................104

3.9.13 SERRCMD2--SERR Command Register (D2:F1) ..............................105

3.9.14 SMICMD2--SMI Command Register (D2:F1)......................................106

3.9.15 SCICMD2--SCI Command Register (D2:F1) ......................................107

3.10

HI_C Virtual PCI-to-PCI Bridge Registers (Device 3, Function 0,1)..................108

3.10.1 DID--Device Identification Register (D3:F0)........................................108

3.10.2 DID--Device Identification Register (D3:F1)........................................108

3.11

HI_D Virtual PCI-to-PCI Bridge Registers (Device 4, Function 0,1)..................109

3.11.1 DID--Device Identification Register (D4:F0)........................................109

3.11.2 DID--Device Identification Register (D4:F1)........................................109

6

Datasheet

4

System Address Map

............................................................................................ 111

4.1

System Memory Spaces ................................................................................... 111

4.1.1

VGA and MDA Memory Spaces........................................................... 113

4.1.2

PAM Memory Spaces .......................................................................... 114

4.1.3

ISA Hole Memory Space...................................................................... 115

4.1.4

I/O APIC Memory Space...................................................................... 115

4.1.5

System Bus Interrupt Memory Space................................................... 115

4.1.6

Device 2 Memory and Prefetchable Memory ....................................... 115

4.1.7

Device 3 Memory and Prefetchable Memory ....................................... 116

4.1.8

Device 4 Memory and Prefetchable Memory ....................................... 116

4.1.9

HI_A Subtractive Decode..................................................................... 116

4.1.10 Main Memory Addresses...................................................................... 116

4.2

I/O Address Space ............................................................................................ 117

4.3

SMM Space....................................................................................................... 117

4.3.1

System Management Mode (SMM) Memory Range............................ 117

4.3.2

TSEG SMM Memory Space................................................................. 118

4.3.3

High SMM Memory Space ................................................................... 118

4.3.4

SMM Space Restrictions...................................................................... 118

4.3.5

SMM Space Definition.......................................................................... 119

4.4

Memory Reclaim Background ........................................................................... 120

4.4.1

Memory Re-Mapping............................................................................ 120

5

Reliability, Availability, Serviceability, Usability, and

Manageability (RASUM)

....................................................................................... 121

5.1

DRAM ECC ....................................................................................................... 121

5.2

DRAM Scrubbing .............................................................................................. 121

5.3

DRAM Auto-Initialization ................................................................................... 121

5.4

SMBus Access .................................................................................................. 121

6

Electrical Characteristics

.................................................................................... 123

6.1

Absolute Maximum Ratings .............................................................................. 123

6.2

Thermal Characteristics .................................................................................... 123

6.3

Power Characteristics ....................................................................................... 124

6.4

I/O Interface Signal Groupings.......................................................................... 125

6.5

DC Characteristics ............................................................................................ 127

7

Ballout and Package Specifications

............................................................... 131

7.1

Ballout ............................................................................................................... 131

7.2

Package Specifications ..................................................................................... 141

7.3

Chipset Interface Trace Length Compensation................................................. 143

7.3.1

MCH System Bus Signal Package Trace Length Data ........................ 144

7.3.1.1 MCH DDR Channel A Signal Package Trace Length Data..... 145

7.3.1.2 MCH DDR Channel B Signal Package Trace Length Data..... 148

7.3.1.3 MCH Hub Interface_A Signal Package Trace Length

Data......................................................................................... 151

7.3.1.4 MCH Hub Interface_B Signal Package Trace Length

Data......................................................................................... 151

7.3.1.5 MCH Hub Interface_C Signal Package Trace Length

Data......................................................................................... 152

7.3.1.6 MCH Hub Interface_D Signal Package Trace Length

Data......................................................................................... 152

Datasheet

7

8

Testability

..................................................................................................................153

8.1

XOR Chains ......................................................................................................154

Figures

1-1

Intel

Æ

E7500 Chipset Platform Block Diagram ....................................................13

2-1

MCH Interface Signals ........................................................................................18

3-1

PAM Registers ....................................................................................................48

4-1

System Address Map ........................................................................................111

4-2

Detailed Extended Memory Range Address Map .............................................112

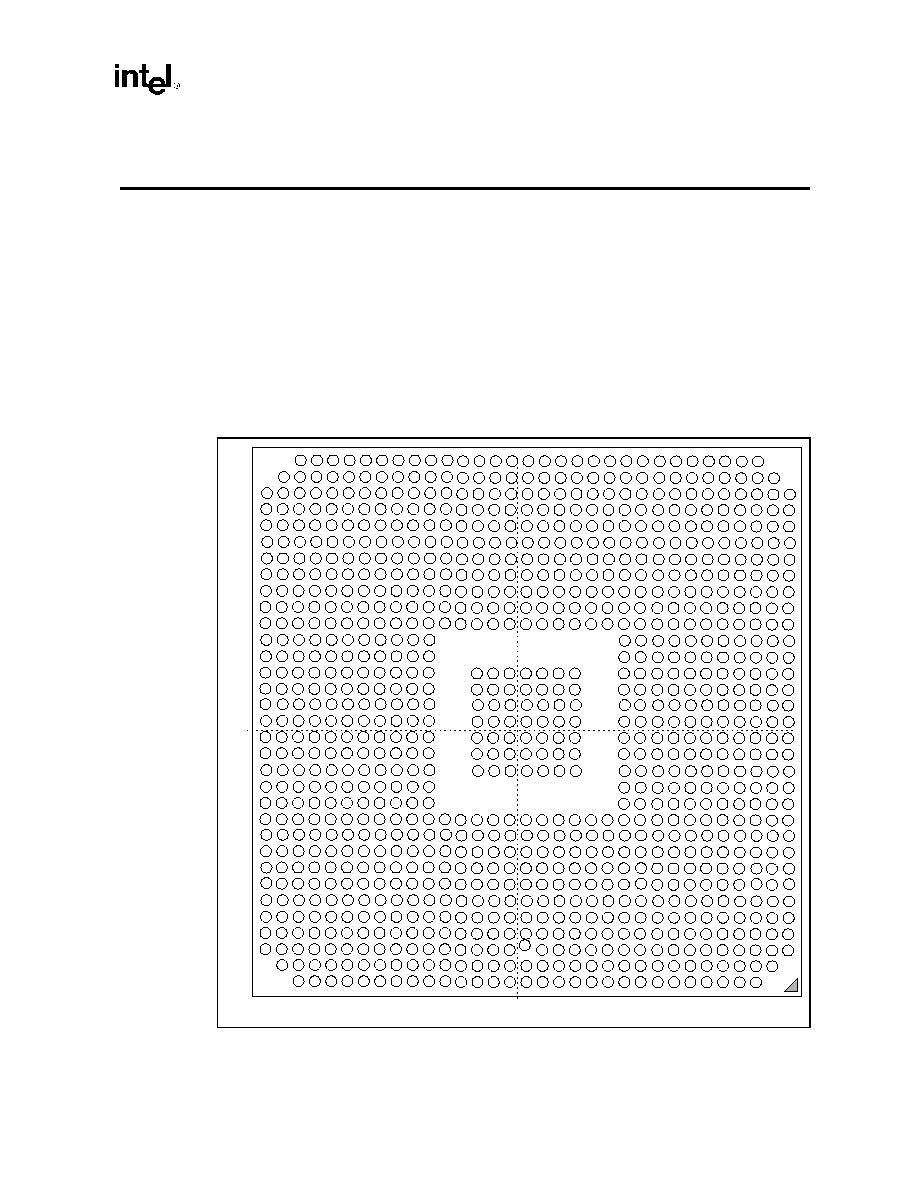

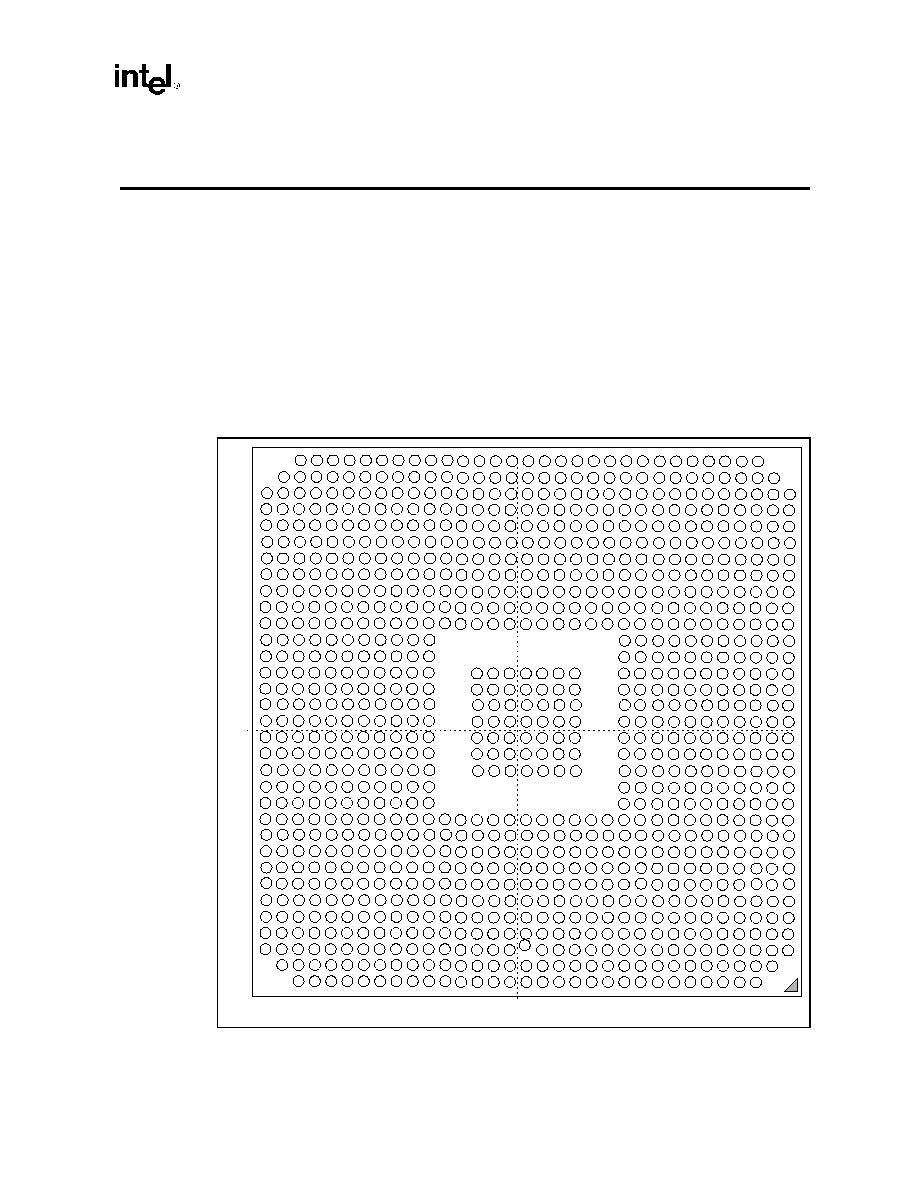

7-1

Intel

Æ

E7500 MCH Ballout (Top View) ..............................................................131

7-2

Intel

Æ

E7500 MCH Ballout (Left Half of Top View) ............................................132

7-3

Intel

Æ

E7500 MCH Ballout (Right Half of Top View)..........................................133

7-4

MCH Package Dimensions (Top View) .............................................................141

7-5

MCH Package Dimensions (Side View) ............................................................142

Tables

1-1

Supported DIMM Configuration...........................................................................15

2-1

System Bus Interface Signals .............................................................................19

2-2

DDR Channel_A Interface Signals ......................................................................22

2-3

DDR Channel_B Interface Signals ......................................................................23

2-4

HI _A Signals.......................................................................................................24

2-5

HI_B Signals........................................................................................................25

2-6

HI_C Signals .......................................................................................................26

2-7

HI_D Signals .......................................................................................................27

2-8

Clocks, Reset, Power, and Miscellaneous Signals .............................................28

3-1

Intel

Æ

E7500 MCH Logical Configuration Resources ..........................................33

3-2

DRAM Controller Register Map (HI_A--D0:F0) ..................................................37

3-3

PAM Associated Attribute Bits.............................................................................48

3-4

DRAM Controller Register Map (HI_A--D0:F1) ..................................................59

3-5

HI_B Virtual PCI-to-PCI Bridge Register Map (HI_A--D2:F0) ............................82

3-6

HI_B Virtual PCI-to-PCI Bridge Register Map (HI_A--D2:F1) ............................97

4-1

SMM Address Range ........................................................................................119

6-1

Absolute Maximum Ratings...............................................................................123

6-2

MCH Package Thermal Resistance ..................................................................123

6-3

Thermal Power Dissipation (VCC1_2 = 1.2 V ±5%)..........................................124

6-4

DC Characteristics Functional Operating Range (VCC1_2 = 1.2 V ±5%).........124

6-5

Signal Groups System Bus Interface ................................................................125

6-6

Signal Groups DDR Interface............................................................................125

6-7

Signal Groups Hub Interface 2.0 (HI_B≠D) .......................................................126

6-8

Signal Groups Hub Interface 1.5 (HI_A)............................................................126

6-9

Signal Groups SMBus .......................................................................................126

6-10

Signal Groups Reset and Miscellaneous ..........................................................126

6-11

Operating Condition Supply Voltage (VCC1_2 = 1.2 V ±5%)............................127

6-12

System Bus Interface (VCC1_2 = 1.2 V ±5%)...................................................127

6-13

DDR Interface (VCC1_2 = 1.2 V ±5%) ..............................................................128

6-14

Hub Interface 2.0 Configured for 50

(VCC1_2 = 1.2 V ±5%).........................129

6-15

Hub Interface 1.5 with Parallel Buffer Mode Configured for 50

(VCC1_2 = 1.2 V ±5%)......................................................................................130

8

Datasheet

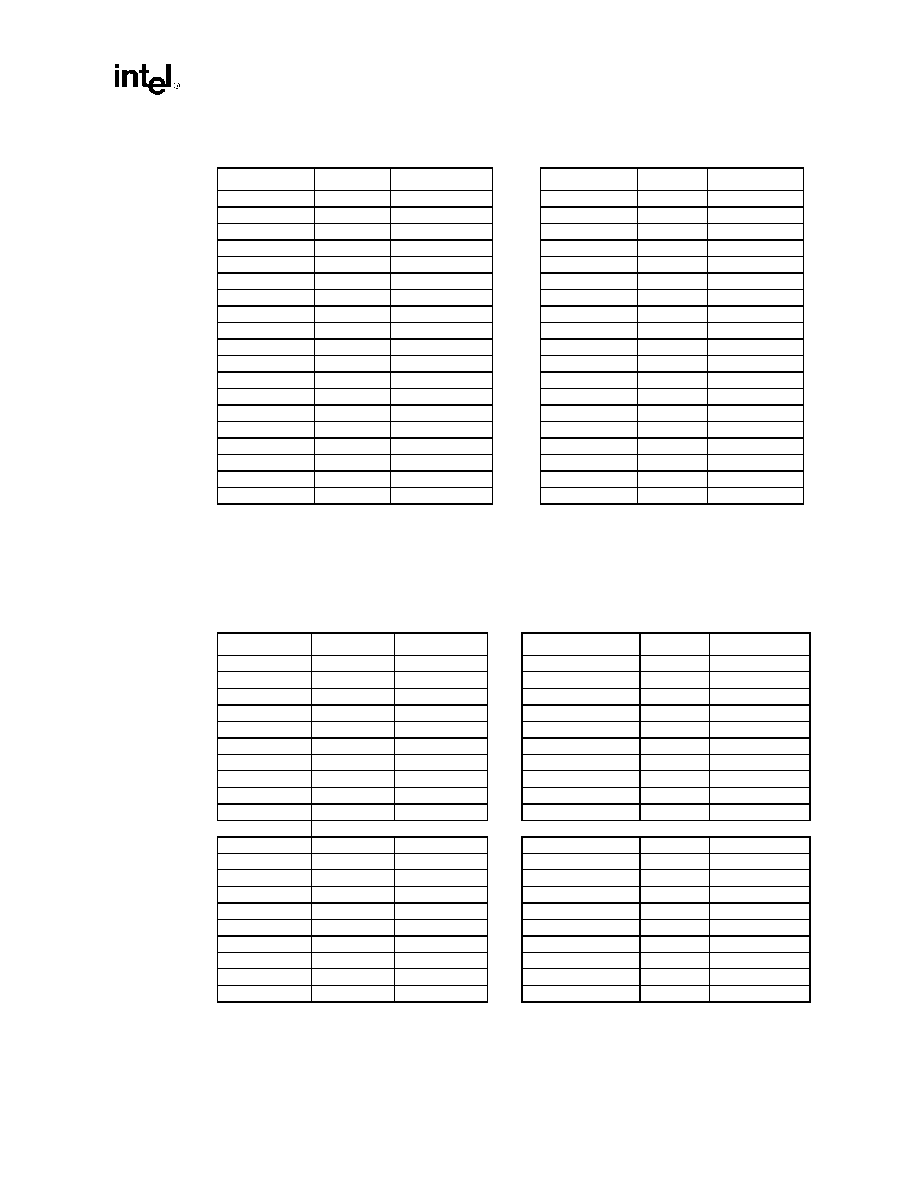

7-1

MCH Signal List ................................................................................................ 134

7-2

Example Normalization Table ........................................................................... 143

7-3

MCH L

PKG

Data for the System Bus ................................................................. 144

7-4

MCH L

PKG

Data for DDR Channel A................................................................. 145

7-5

MCH L

PKG

Data for DDR Channel B................................................................. 148

7-6

MCH L

PKG

Data for Hub Interface_A ................................................................ 151

7-7

MCH L

PKG

Data for Hub Interface_B ................................................................ 151

7-8

MCH L

PKG

Data for Hub Interface_C ................................................................ 152

7-9

MCH L

PKG

Data for Hub Interface_D ................................................................ 152

8-1

XOR Chains ...................................................................................................... 154

Datasheet

9

Revision History

Rev.

Description

Date

-001

Initial Release

February 2002

10

Datasheet

Intel

Æ

E7500 MCH Features

s

Processor/Host Bus Support

--Intel

Æ

XeonTM processor with 512-KB

L2 cache

--400 MHz system bus

(2x address, 4x data)

--Symmetric Multiprocessing Protocol

(SMP) for up to two processors at

400 MT/s

--System bus Dynamic Bus Inversion

(DBI)

--36-bit system bus addressing

--12-deep in-order queue

--AGTL+ bus driver technology with

on-die termination resistors

--Parity protection on system bus data,

address/request, and response signals

s

Memory System

--One 144-bit wide DDR memory port

(with Chipkill* technology ECC)

--Peak memory bandwidth of 3.2 GB/s

--Supports 64 Mb, 128 Mb, 256 Mb,

512 Mb DRAM densities

--Supports a maximum of 16 GB of

memory using (x4) double-sided DIMM

--Supports x72, Registered, ECC DDR

DIMMs (in pairs)

s

Hub Interface_A to Intel

Æ

ICH3-S

--Supports connection to ICH3-S via

hub interface 1.5

--266 MB/s point-to-point hub

interface 1.5 interface to ICH3-S

--Parity protected

--66 MHz base clock running 4x

(533 MB/s) data transfer

--Isochronous support

--Parallel termination mode only

--64-bit addressing on inbound

transactions (maximum 16 GB memory

decode space)

s

Hub Interface_B, Hub Interface_C, and

Hub Interface_D

--Supports connection to Intel

Æ

P64H2 via

HI 2.0

--Each hub interface is an independent

1 GB/s point-to-point 16-bit connection

--ECC protected

--66 MHz base clock running 8x (1 GB/s)

data transfers

--Supports snooped and non-snooped

inbound accesses

--Parallel termination mode

--64-bit inbound addressing

--32-bit outbound addressing supported

for PCI-X

s

PCI / PCI-X

--Supports 33 MHz PCI on ICH3-S

--Supports 33 MHz and 66 MHz PCI on

P64H2

--Supports 66 MHz, 100 MHz or

133 MHz PCI-X on P64H2

s

RASUM

--Supports S4EC/D4ED ECC

--Provides x4 Chipkill technology ECC

support

--Correct any number of errors contained

in a 4-bit nibble

--Detect all errors contained entirely

within two 4-bit nibbles

--Hub Interface_A protected by parity

--Hub Interface_B≠D protected by ECC

--Memory auto-initialization by hardware

implemented to allow main memory to

be initialized with valid ECC

--Memory scrubbing supported

--SMBus target interface access to MCH

error registers

--P64H2 and ICH3-S have SMBus target

interface for access to registers

--ICH3-S master SMBus interface reads

serial presence detect (SPD) on DIMMs

s

Package

--1005-ball, 42.5 mm FC-BGA package

Datasheet

11

Introduction

Introduction

1

The Intel

Æ

E7500 chipset is targeted for the server market, both front-end and general purpose low-

to mid-range. It is intended to be used with the Intel

Æ

XeonTM processor with 512-KB L2 cache.

The E7500 chipset consists of three major components: the Intel

Æ

E7500 Memory Controller Hub

(MCH), the Intel

Æ

I/O Controller Hub 3 (ICH3-S), and the PCI/PCI-X 64-bit Hub 2.0 (P64H2).

The MCH provides the system bus interface, memory controller, hub interface for legacy I/O, and

three high-performance hub interfaces for PCI/PCI-X bus expansion.

This document describes the E7500 Memory Controller Hub (MCH).

Section 1.3, "IntelÆ E7500

Chipset System Architecture" on page 1-12

provides an overview of each of the components of the

E7500 chipset. For details on other components of the chipset, refer to that component's datasheet.

1.1

Glossary of Terms

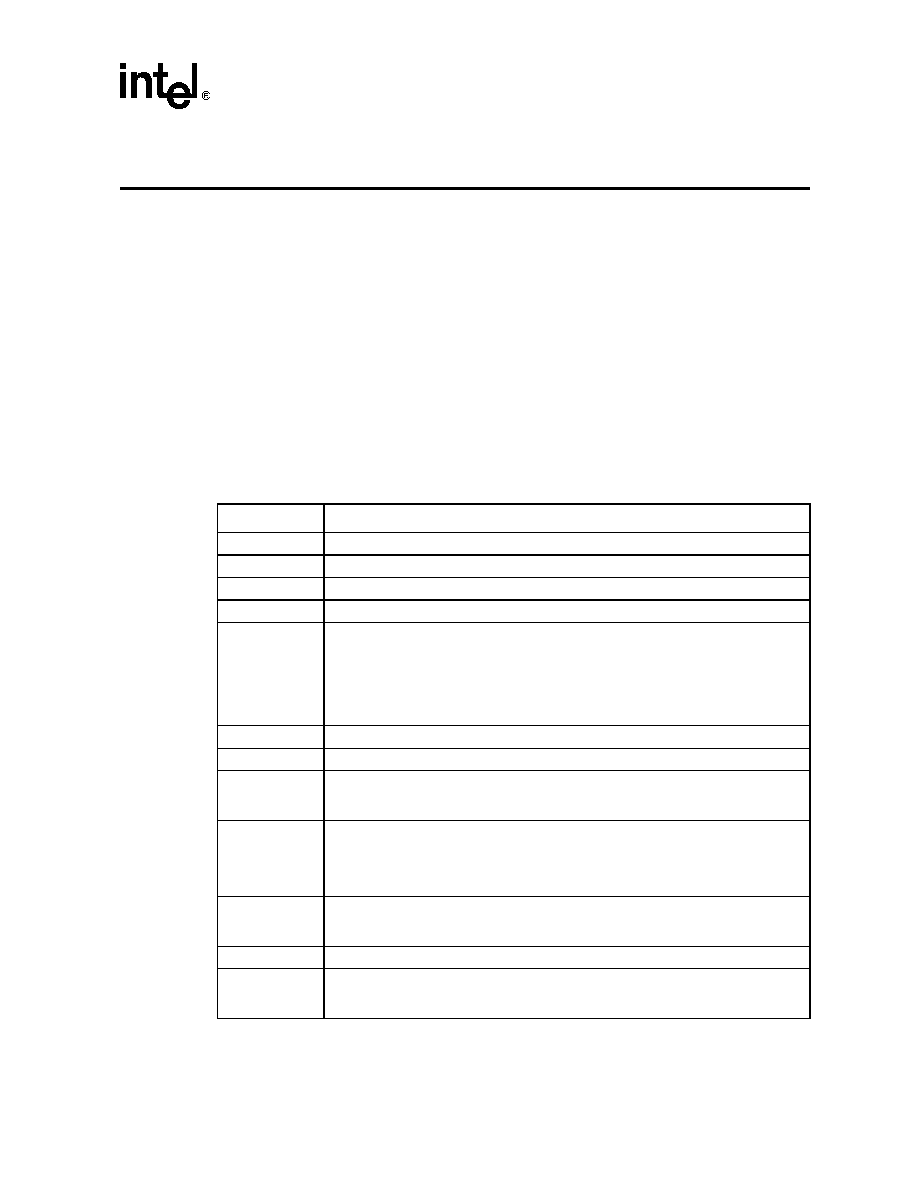

Term

Description

DBI

Dynamic Bus Inversion.

DDR

Double Data Rate memory technology.

DP

Dual Processor.

Full Reset

The term "a full MCH reset" is used in this document when RSTIN# is asserted.

HI

Hub Interface. The proprietary hub interconnect that ties the MCH to the ICH3-S and

P64H2. In this document HI cycles originating from or destined for the primary PCI

interface on the ICH3-S are generally referred to as HI/PCI_A or simply HI_A cycles.

Cycles originating from or destined for any target on the second, third or fourth HI

interfaces are described as HI_B, HI_C, and HI_D cycles respectively. Note that there are

two versions of HI used on the Intel

Æ

E7500 MCH: an 8-bit HI 1.5 protocol is implemented

on HI_A and a 16-bit HI 2.0 protocol is used for the HI_B, HI_C and HI_D.

Host

This term is used synonymously with processor.

IB

Inbound, refers to traffic moving from PCI or other I/O toward DRAM or the system bus.

ICH3-S

The I/O Controller Hub 3-S component that contains the primary PCI interface, LPC

interface, USB, ATA-100, and other legacy functions. It communicates with the MCH over

a proprietary interconnect called the hub interface.

Intel

Æ

XeonTM

processor with

512-KB L2 cache

The processor supported by the Intel

Æ

E7500 chipset. This processor is the second

generation of processors based on the Intel

Æ

NetBurstTM microarchitecture. This

processor delivers performance levels that are significantly higher than previous

generations of IA-32 processors. This processor supports 1-2 processors on a single

system bus and has a 512 KB integrated L2 cache.

MCH

The Memory Controller Hub component that contains the processor interface and DRAM

interface. It communicates with the I/O Controller Hub 3-S (ICH3-S) and P64H2 over a

proprietary interconnect called the Hub Interface (HI).

OB

Outbound, refers to traffic moving from the system bus to PCI or other I/O.

Intel

Æ

P64H2

PCI/PCI-X 64-bit Hub 2.0 component. The Bus Controller Hub component has a 16-bit

hub interconnect 2.0 on its primary side and

two, 64-bit PCI-X bus segments on the

secondary side.

12

Datasheet

Introduction

1.2

Reference Documents

NOTE: Refer to the Intel

Æ

XeonTM Processor with 512-KB L2 Cache and Intel

Æ

E7500 Chipset Platform Design

Guide for an expanded set of reference documents.

1.3

Intel

Æ

E7500 Chipset System Architecture

The E7500 chipset is optimized for the Intel Xeon processor with 512-KB L2 cache. The

architecture of the chipset provides the performance and feature-set required for dual-processor

based severs in the entry-level and mid-range, front-end and general-purpose server market

segments. A new chipset component interconnect, the hub interface 2.0 (HI2.0), is designed into

the E7500 chipset to provide more efficient communication between chipset components for high-

speed I/O. Each HI2.0 provides 1.066 GB/s I/O bandwidth. The E7500 chipset has three HI2.0

connections, delivering 3.2 GB/s bandwidth for high-speed I/O, which can be used for PCI-X. The

system bus, used to connect the processor with the E7500 chipset, utilizes a 400 MT/s transfer rate

for data transfers, delivering a bandwidth of 3.2 GB/s. The E7500 chipset architecture supports a

144-bit wide, 200 MHz Double Data Rate (DDR) memory interface also capable of transferring

data at 3.2 GB/s.

In addition to these performance features, E7500 chipset-based platforms also provide the RASUM

(Reliability, Availability, Serviceability, Usability, and Manageability) features required for entry-

level and mid-range servers. These features include: Chipkill* technology ECC for memory, ECC

for all high-performance I/O, out-of-bound manageability through SMBus target interfaces on all

major components, memory scrubbing and auto-initialization, processor thermal monitoring, and

hot-plug PCI/PCI-X.

Primary PCI or

PCI_A

The physical PCI bus that is driven directly by the ICH3-S component. It supports 5 V,

32-bit, 33 MHz PCI 2.2 compliant components. Communication between PCI_A and the

MCH occurs over HI_A. Note that even though the Primary PCI bus is referred to as

PCI_A it is not PCI Bus #0 from a configuration standpoint.

RASUM

Reliability, Availability, Serviceability, Usability and Manageability.

Document

Document

Number

Intel

Æ

XeonTM Processor with 512 KB L2 Cache and Intel

Æ

E7500 Chipset Platform Design

Guide

298649

Intel

Æ

82801CA I/O Controller Hub 3-S (ICH3-S) Datasheet

290733

Intel

Æ

82870P2 PCI/PCI-X 64-bit Hub 2 (P64H2) Datasheet

290732

Intel

Æ

E7500 Chipset: E7500 Memory Controller Hub (MCH) Thermal and Mechanical

Design Guidelines

298647

Intel

Æ

PCI/PCI-X 64-bit Hub 2 (P64H2) Thermal and Mechanical Design Guidelines

298648

Intel

Æ

82802B/AC Firmware Hub (FWH) Datasheet

290658

Intel

Æ

XeonTM Processor with 512-KB L2 Cache Datasheet

Term

Description

Datasheet

13

Introduction

The E7500 chipset consists of three major components: the Memory Controller Hub (MCH), the

I/O Controller Hub 3-S (ICH3-S), and the PCI/PCI-X 64-bit Hub 2.0 (P64H2). The chipset

components communicate via hub interfaces (HIs). The MCH provides four hub interface

connections: one for the ICH3-S and three for high-speed I/O using P64H2 bridges. The hub

interfaces are point-to-point and therefore only support two agents (the MCH plus one I/O device),

providing connections for up to 3 P64H2 bridges. The P64H2 provides bridging functions between

hub interface_B≠D and the PCI/PCI-X bus. Up to six PCI-X busses are supported. Each PCI-X bus

is 66 MHz, 100 MHz, and 133 MHz PCI-X capable.

Additional platform features supported by the E7500 chipset include four ATA/100 IDE drives,

Low Pin Count interface (LPC), integrated LAN Controller, Audio Codec, and Universal Serial

Bus (USB).

The E7500 chipset is also ACPI compliant and supports Full-on, Stop Grant, Suspend to Disk, and

Soft-off power management states. Through the use of an appropriate LAN device, the E7500

chipset also supports wake-on-LAN* for remote administration and troubleshooting.

1.3.1

Intel

Æ

82801CA I/O Controller Hub 3-S (ICH3-S)

The ICH3-S is a highly-integrated, multi-functional I/O Controller Hub that provides the interface

to the PCI bus and integrates many of the functions needed in today's PC platforms. The MCH and

ICH3-S communicate over a dedicated hub interface. Intel 82801CA ICH3-S functions and

capabilities include:

∑

PCI Local Bus Specification, Revision 2.2-compliant with support for 33 MHz PCI operations.

∑

PCI slots (supports up to 6 Req/Gnt pairs)

∑

ACPI Power Management Logic Support

∑

Enhanced DMA Controller, Interrupt Controller, and Timer Functions

∑

Integrated IDE controller supports Ultra ATA100/66/33

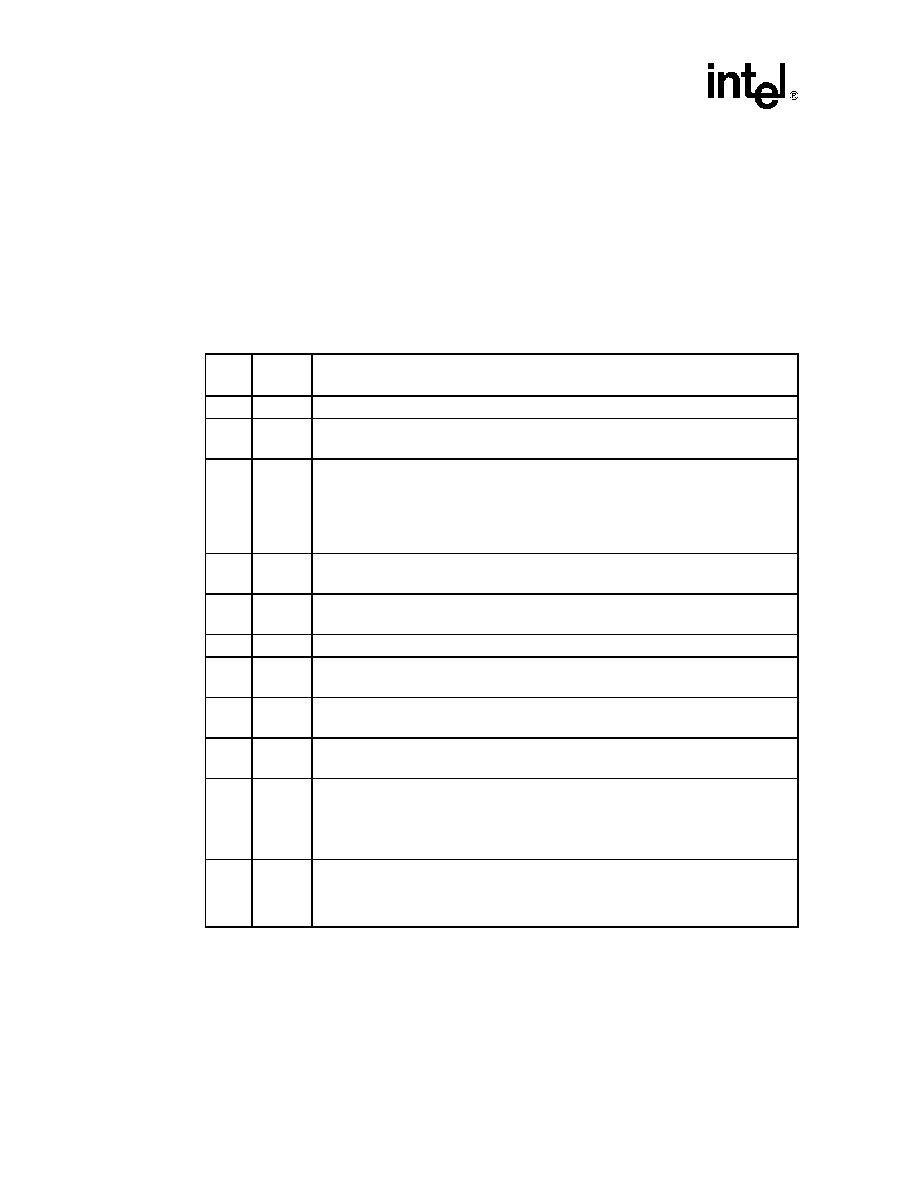

Figure 1-1. Intel

Æ

E7500 Chipset Platform Block Diagram

MCH

Processor

Processor

Main Memory

(16 GB Max)

DDR Channel A

DDR Channel B

200 MHz

Interface

Intel

Æ

P64H2

P64H2

P64H2

Hot Plug

PCI-X

PCI-X

Hot Plug

PCI-X

PCI-X

Hot Plug

PCI-X

PCI-X

Intel

Æ

ICH3-S

16-Bit

HI 2.0

16-Bit

HI 2.0

16-Bit

HI 2.0

USB 1.1

(6 ports)

ATA-100

(4 drives)

AC '97

10/100 LAN

Controller

SMBus 1.1

GPIOs

FWH (1-4)

PCI Bus

8-Bit

HI 1.5

14

Datasheet

Introduction

∑

USB host interface with support for 6 USB ports; 3 UHCI host controllers

∑

Integrated LAN Controller

∑

System Management Bus (SMBus) Specification, Version 1.1 with additional support for I

2

C

devices

∑

Audio Codec '97, Revision 2.2 Specification (a.k.a., AC '97 Component Specification,

Rev. 2.2) Compliant Link for Audio and Telephony codecs (up to 6 channels)

∑

Low Pin Count (LPC) interface

∑

Firmware Hub (FWH) interface support

∑

Alert On LAN* (AOL) and Alert On LAN 2* (AOL2)

1.3.2

Intel

Æ

82870P2 PCI/PCI-X 64-bit Hub 2 (P64H2)

The 82870P2 PCI/PCI-X 64-bit Hub 2 (P64H2) is a peripheral chip that performs PCI bridging

functions between the MCH hub interface and the PCI -X busses. The P64H2 interfaces to the

MCH via a 16-bit hub interface. Each P64H2 has two independent 64-bit PCI bus interfaces that

can be configured to operate in PCI or PCI-X mode. Each PCI bus interface contains an

I/OAPIC with 24 interrupts and a hot-plug controller. Functions and capabilities include:

∑

16-Bit hub interface to MCH

∑

Two PCI bus interfaces

-- PCI Specification, Revision 2.2 compliant

-- PCI-PCI Bridge Specification, Revision 1.1 compliant

-- PCI-X Specification, Revision 1.0 compliant

-- PCI hot plug 1.0 compliant

∑

SMBus interface

∑

Hot-plug controller for each PCI bus segment

∑

I/OAPIC for each PCI bus segment

1.4

Intel

Æ

E7500 MCH Overview

The MCH provides the processor interface, main memory interface, and hub interfaces in an E7500

chipset-based server platform. It supports Intel Xeon processor with 512 KB L2 cache processor.

The MCH is offered in a 1005-ball, 42.5 mm FC-BGA package and has the following

functionality:

∑

Supports single or dual processor configurations at 400 MT/s

∑

AGTL+ host bus with integrated termination supporting 36-bit host addressing

∑

144-bit wide DDR channel supporting 200 MHz dual data rate operation

∑

16 GB DDR DRAM (512 Mb devices) support

∑

8-bit, 66 MHz 4x hub interface A to ICH3-S

∑

Three 16-bit, 66 MHz 8x hub interface

∑

Distributed arbitration for highly concurrent operation

Datasheet

15

Introduction

1.4.1

Processor System Interface

The E7500 MCH is optimized for use with processors based on the Intel

Æ

NetBurstTM

microarchitecture. It supports the following features:

∑

400 MHz system bus (2x address, 4x data)

∑

Symmetric multiprocessing protocol (SMP) for up to two processors at 400 MT/s

∑

System bus dynamic bus inversion (DBI)

∑

36-bit system bus addressing

∑

12-deep in-order queue

∑

AGTL+bus driver technology with on die termination resistors

∑

Parity protection on system bus data, address/ request, and response signals

1.4.2

Main Memory Interface

The MCH directly supports two channels of DDR DRAM operating in lock-step. These channels

are organized to provide minimum latency for the critical segment of data. The MCH DDR

channels run at 200 MHz. The MCH supports 64-Mb, 128-Mb, 256-Mb, or 512-Mb memory

technology. The MCH provides ECC error checking with Chipkill technology, on x4 DIMMS to

ensure DRAM data integrity. The MCH supports x72, registered, ECC DDR DIMMs. The MCH

memory interface supports the following operations:

∑

Provides x4 Chipkill technology ECC support

∑

Corrects any number of errors contained in a 4-bit nibble

∑

Detects all errors contained entirely within two 4-bit nibbles

∑

8 KB≠64 KB page sizes support 64 Mb to 512 Mb DRAM Devices

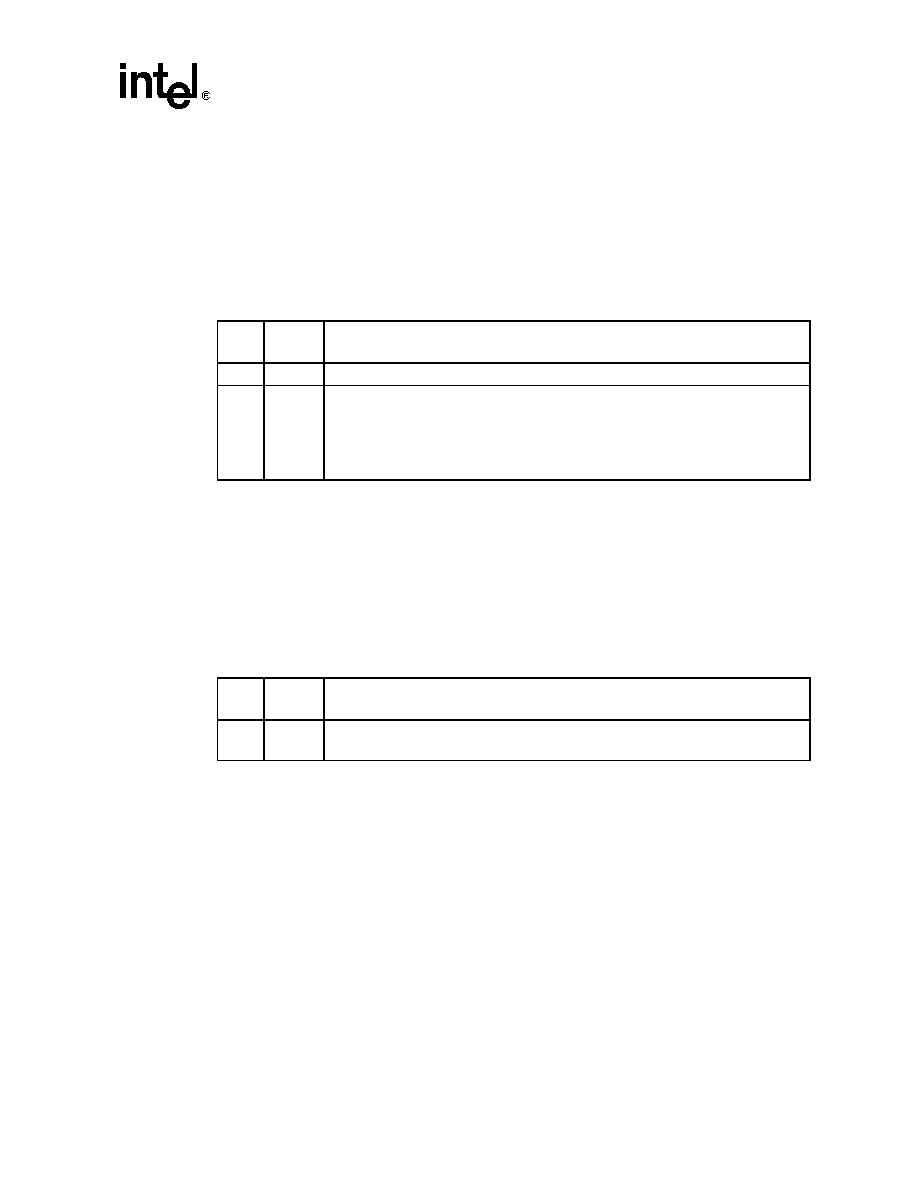

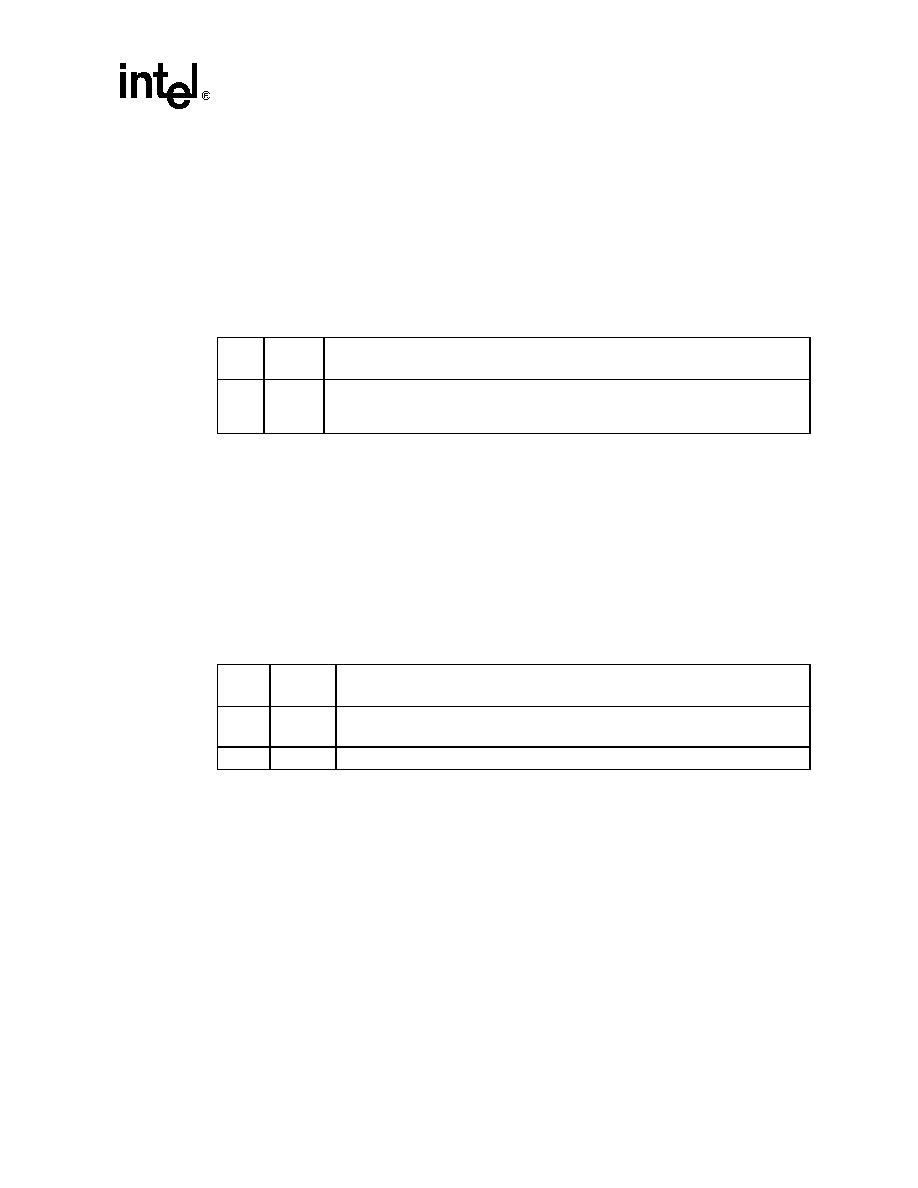

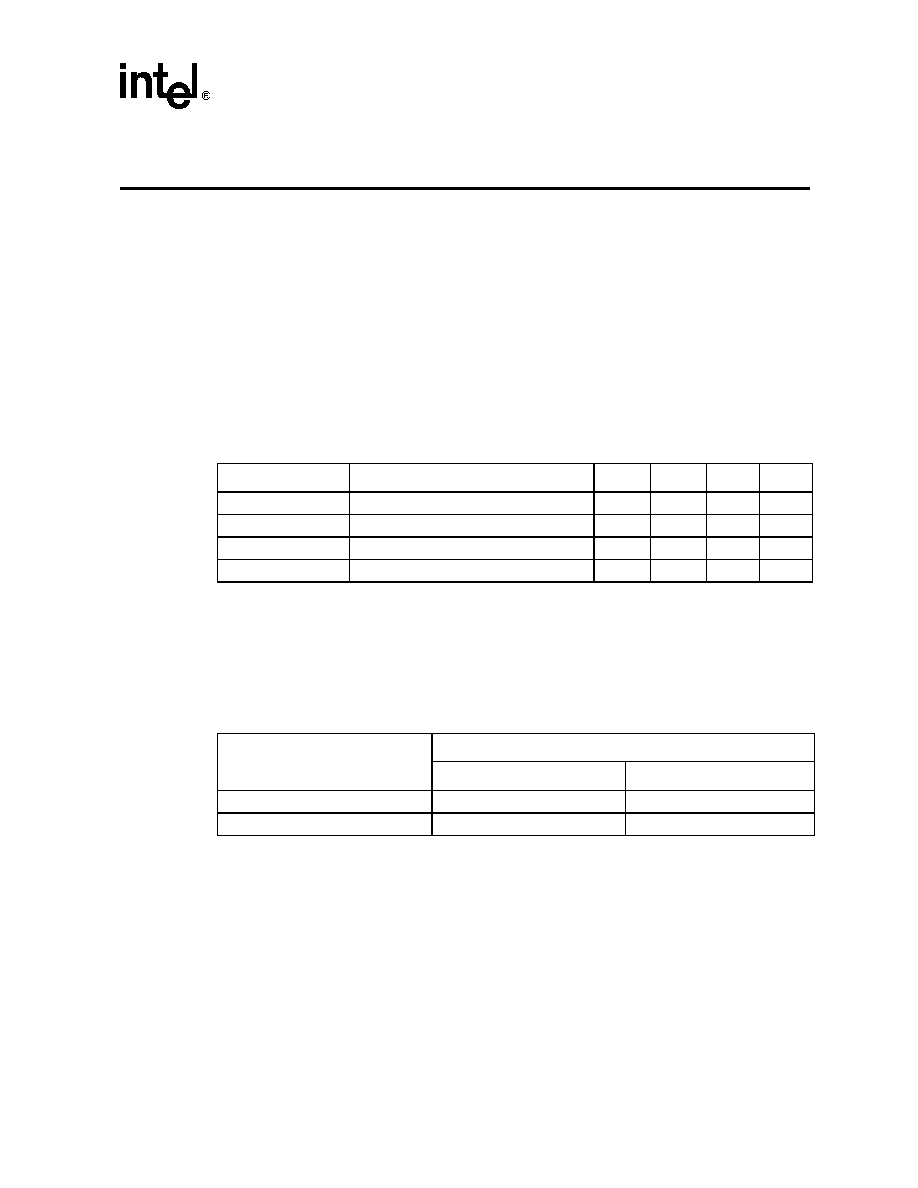

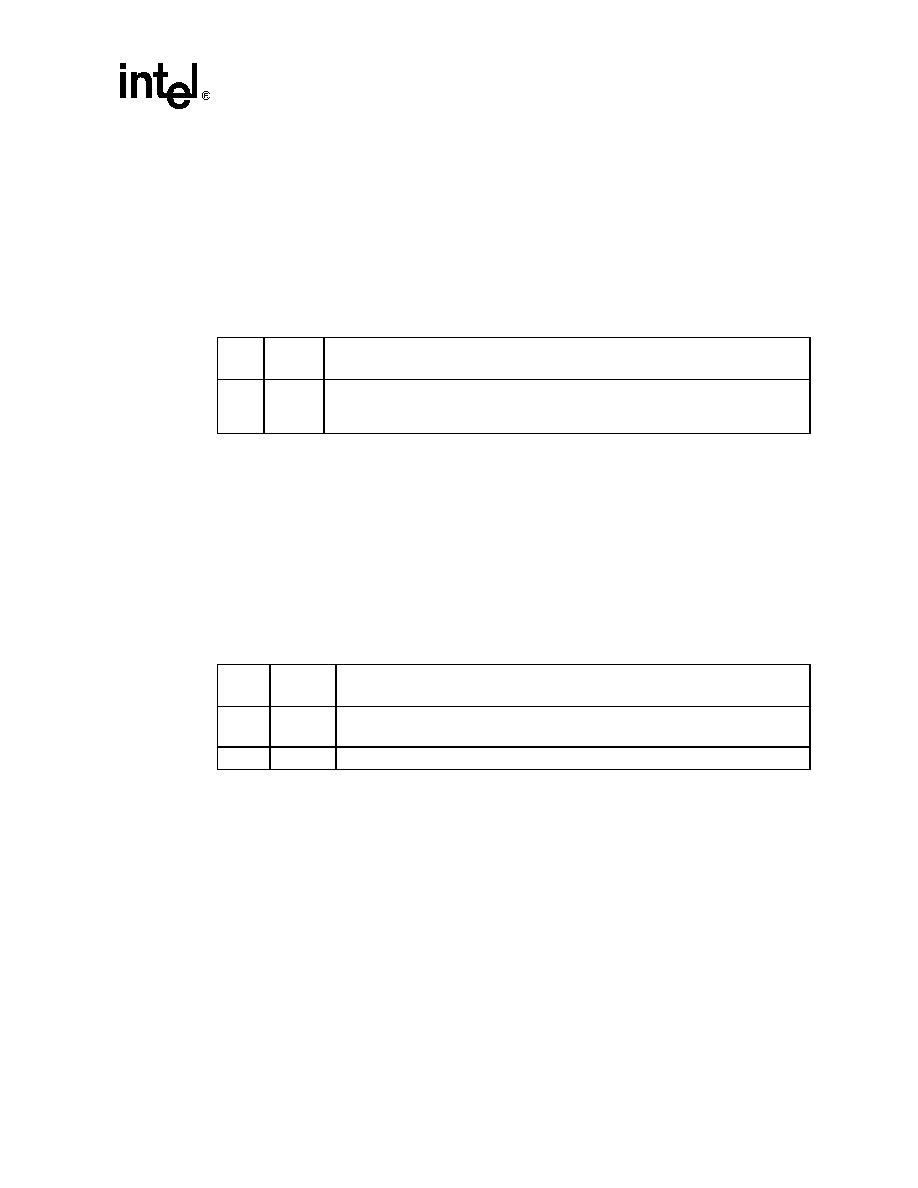

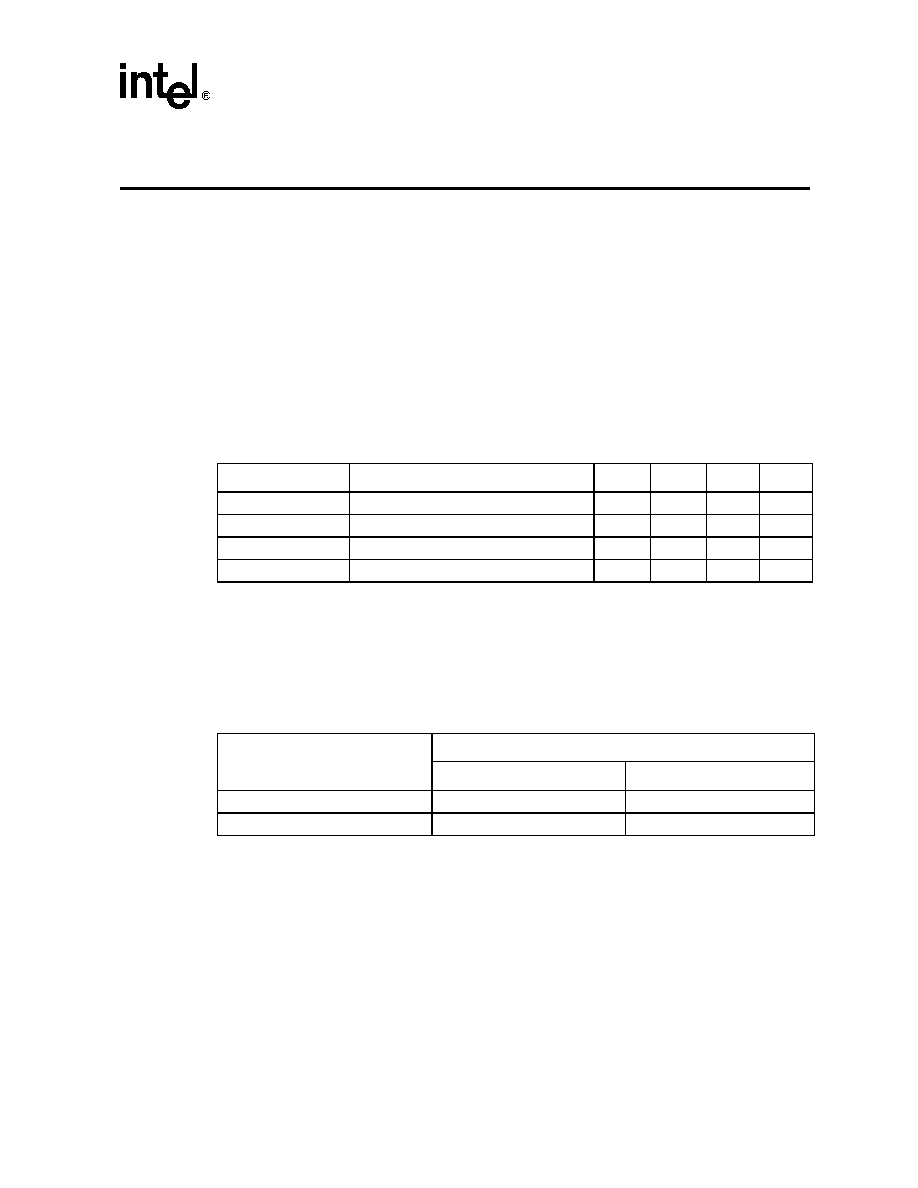

The supported DIMM configurations are listed in

Table 1-1

.

NOTE: DIMMs must be populated in pairs, and the DIMMs in a pair must be identical.

1.4.3

Hub Interface_A (HI_A)

The 8-bit HI_A connects the MCH to the ICH3-S. All communication between the MCH and the

ICH3-S occurs over HI_A, running at 66 MHz base clock 4x (266 MB/s). HI_A supports upstream

64-bit addressing and downstream 32-bit addressing. All incoming accesses on HI_A are snooped.

HI_A provides preferential treatment for isochronous transfers. The interface supports parallel

termination only.

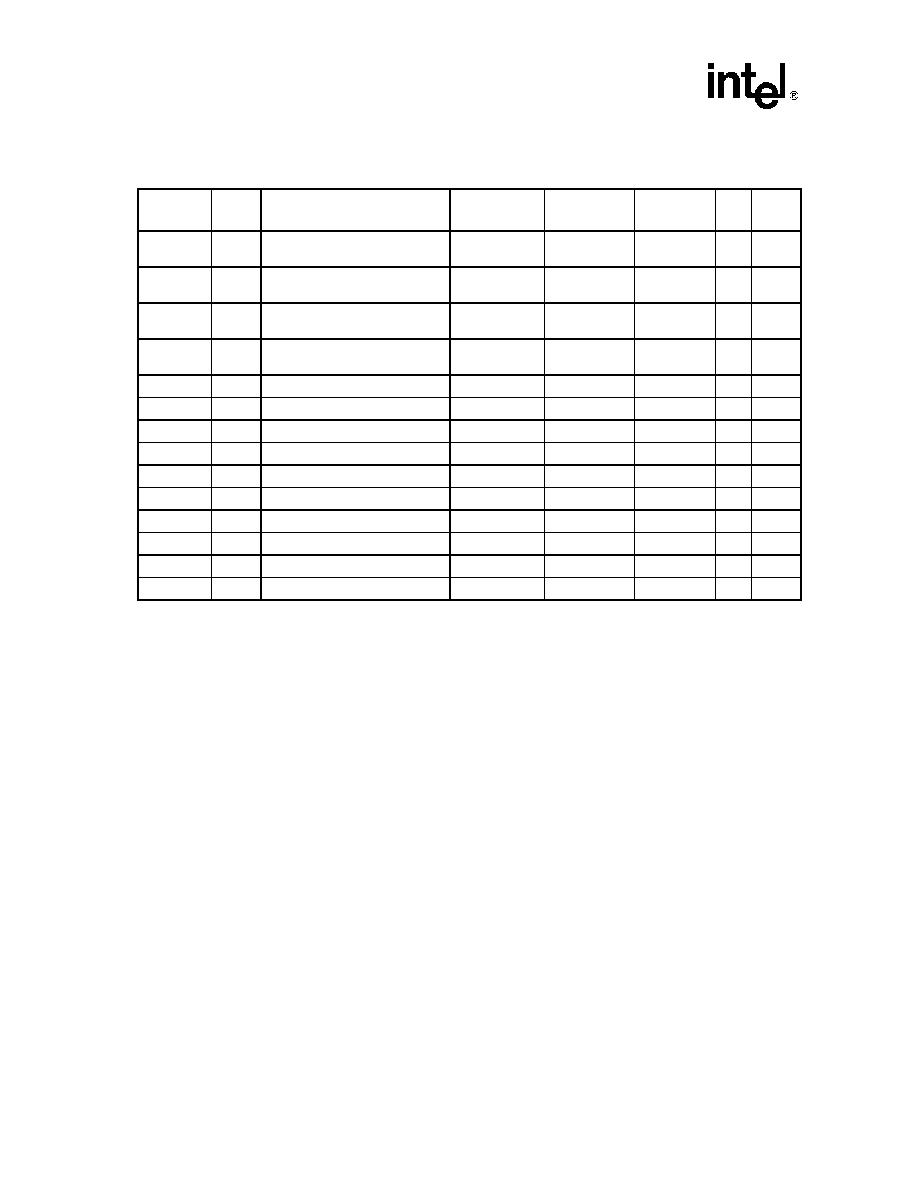

Table 1-1. Supported DIMM Configuration

Density

64 Mbit

128 Mbit

256 Mbit

512 Mbit

Device Width

X4

X8

X4

X8

X4

X8

X4

X8

Single / Double

SS / DS

SS / DS

SS / DS

SS / DS

SS / DS

SS / DS

SS / DS

SS / DS

184 Pin DDR DIMM

Capacity

128 MB /

256 MB

64 MB/

128 MB

256 MB /

512 MB

128 MB /

256 MB

512 MB /

1024 MB

256 MB /

512 MB

1024MB/

2048MB

512MB/

1024 MB

16

Datasheet

Introduction

1.4.4

Hub Interface_B≠D (HI_B≠D)

The MCH supports three 16-bit hub interfaces that run at 66 MHz 8x (1 GB/s). The 16-bit HI 2.0

interfaces support 32-bit downstream addressing and 64-bit upstream addressing. For Hub

Interface_B≠D to main memory accesses, memory read and write accesses are supported. For

processor to Hub Interface_B≠D accesses, memory reads, memory writes, I/O reads, and I/O writes

are supported.

The 16-bit hub interfaces 2.0 support parallel termination only. The 16-bit HI 2.0 may or may not

be connected to a device. The MCH detects the presence of a device on each 16-bit hub. If a hub

interface is not connected to a valid hub interface device, the bridge configuration register space for

that interface is disabled.

1.4.5

MCH Clocking

The MCH has the following clock input pins:

∑

Differential HCLKINP/HCLKINN for the host interface

∑

66 MHz clock input for the HI_A, HI_B, HI_C, HI_D interfaces

Clock synthesizer chip(s) generate the system bus clock and hub interface clock. The system bus

interface clock speed is 100 MHz. The MCH does not require any relationship between the

HCLKIN host clock and the 66 MHz clock generated for hub interfaces. The HI_A, HI_B, HI_C

and HI_D interfaces run at a 66 MHz base clock frequency. HI_A runs at 4x, HI_B, HI_C, and

HI_D run at 8x.

The DDR clocks generated by the MCH have a 1:1 relationship with the system bus.

1.4.6

SMBus Interface

The SMBus address for the MCH is 011_0000. This interface has no configuration registers

associated with it. The SMBus controller has access to all internal MCH registers. It does not allow

access to devices on the hub interface or PCI buses. The SMBus port can read all MCH error

registers. It can only write a special set of "shadowed" error registers. These error registers are an

exact copy of what the processor has access to. This allows the processor to read and clear its set of

error registers independently from the set the SMBus port controls. The SMBus port can only write

the error registers to clear them; the only supported write operation is a byte write. Reads are

always performed as 4-byte accesses.

Datasheet

17

Signal Description

Signal Description

2

This section provides a detailed description of MCH signals. The signals are arranged in functional

groups according to their associated interface.

The "#" symbol at the end of a signal name indicates that the active, or asserted state occurs when

the signal is at a low voltage level. When "#" is not present after the signal name the signal is

asserted when at the high voltage level.

The following notations are used to describe the signal type:

I

Input pin

O

Output pin

I/O

Bidirectional Input/Output pin

as/t/s

Active Sustained tristate. This applies to some of the hub interface (HI)

signals. This pin is weakly driven to its last driven value

2x

Double-pump clocking. Addressing at 2x of HCLKINx

4x

Quad-pump clocking. Data transfer at 4x of HCLKINx

SSTL-2

Stub series terminated logic for 2.5 Volts. Refer to the JEDEC

specification D8-9A for complete details

The signal description also includes the type of buffer used for the particular signal:

AGTL+

Open drain AGTL+ interface signal. Refer to the AGTL+ I/O

Specification for complete details. The MCH integrates AGTL+

termination resistors

CMOS

CMOS buffers

Note: Certain signals are logically inverted signals. The logical values are the inversion of the electrical

values on the system bus.

Signal Description

18

Datasheet

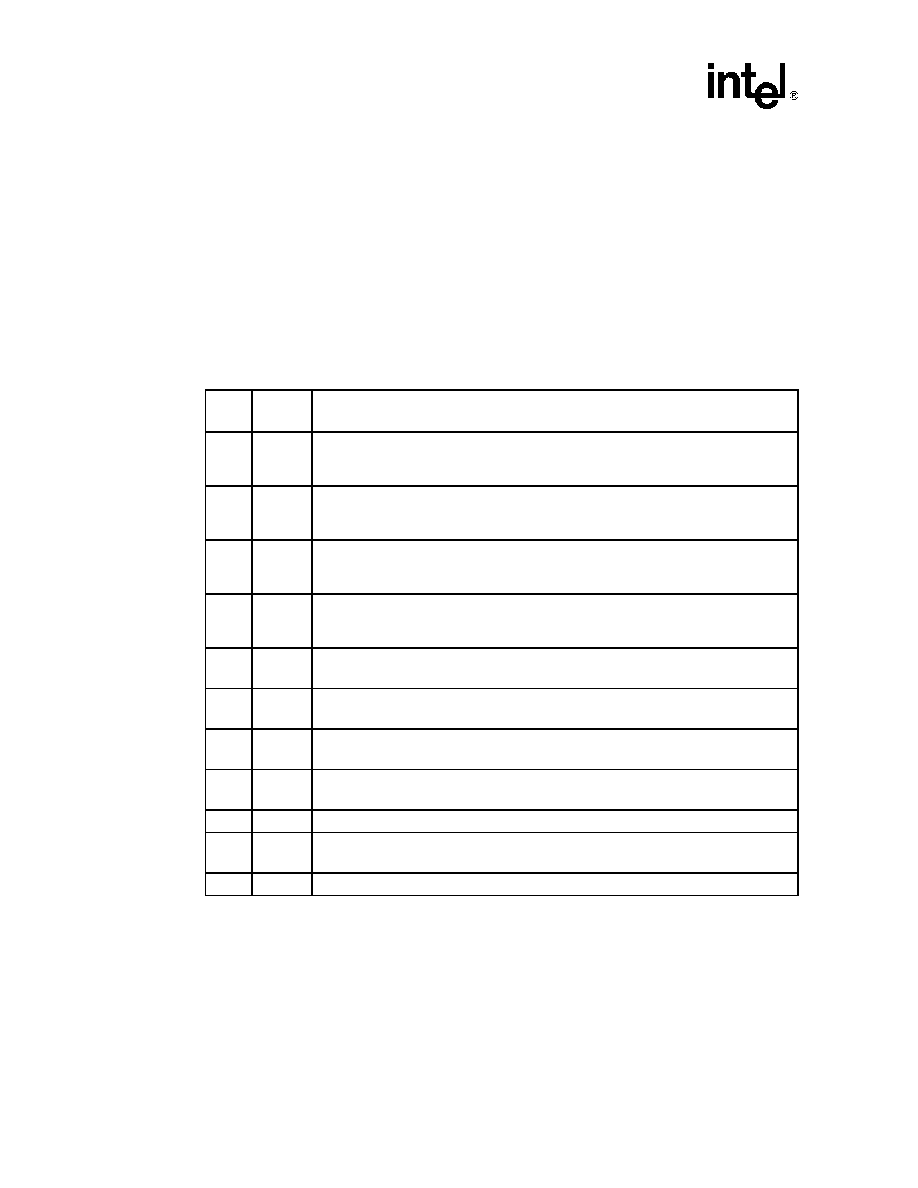

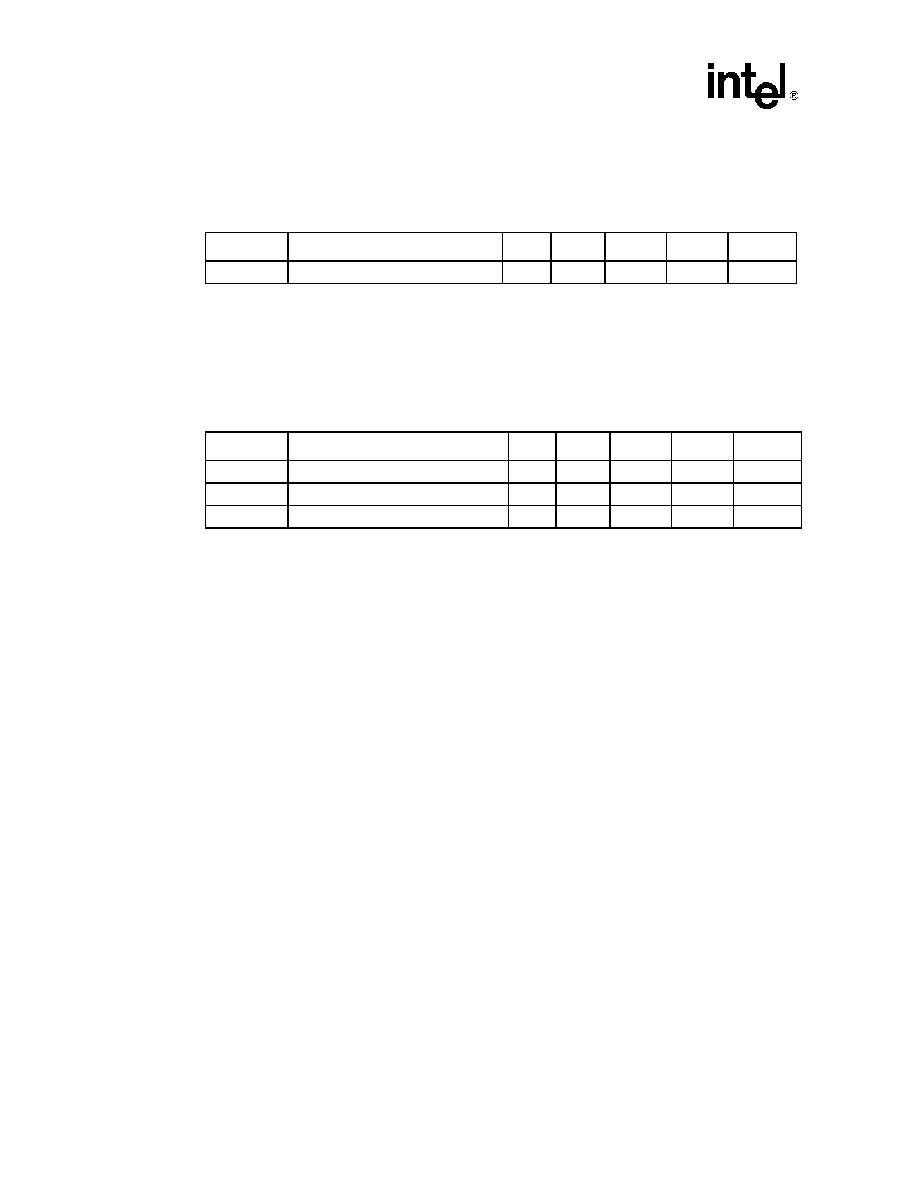

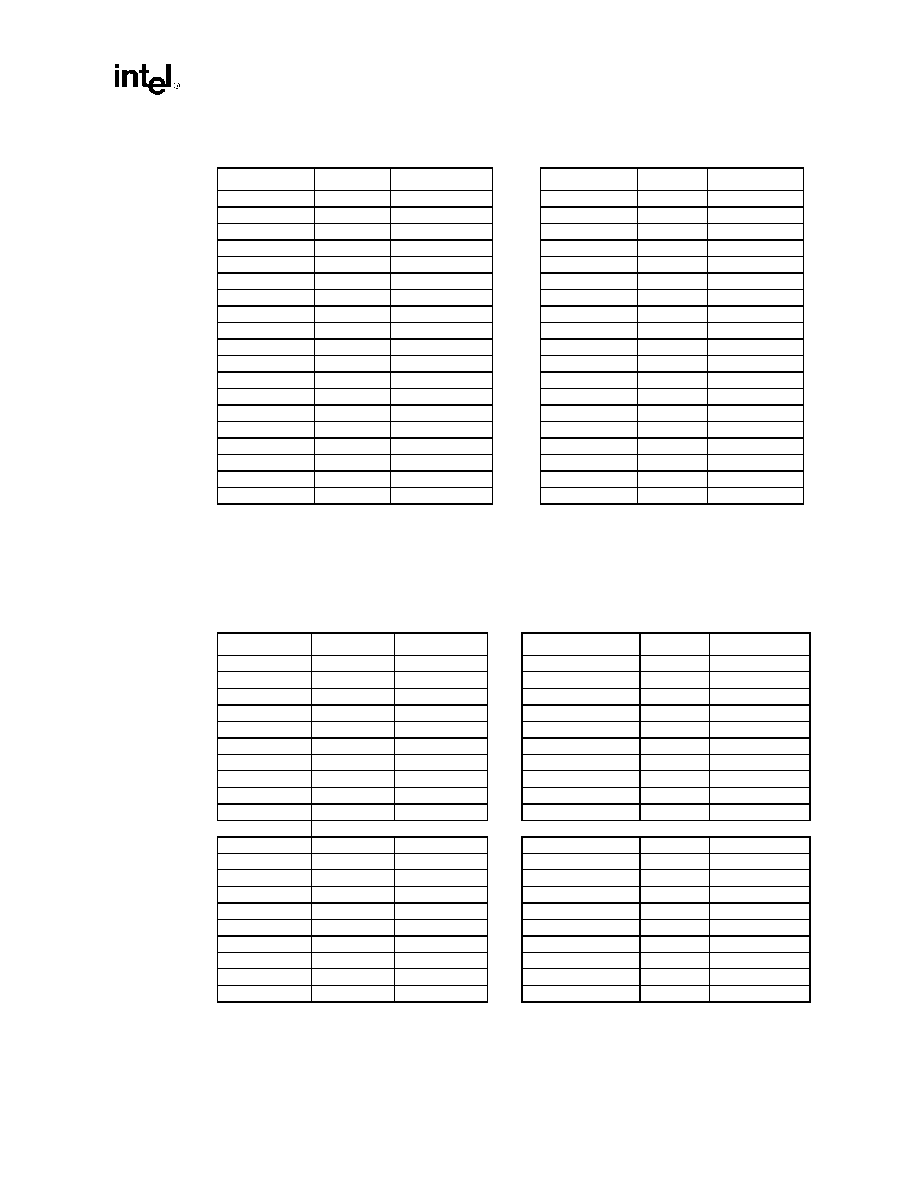

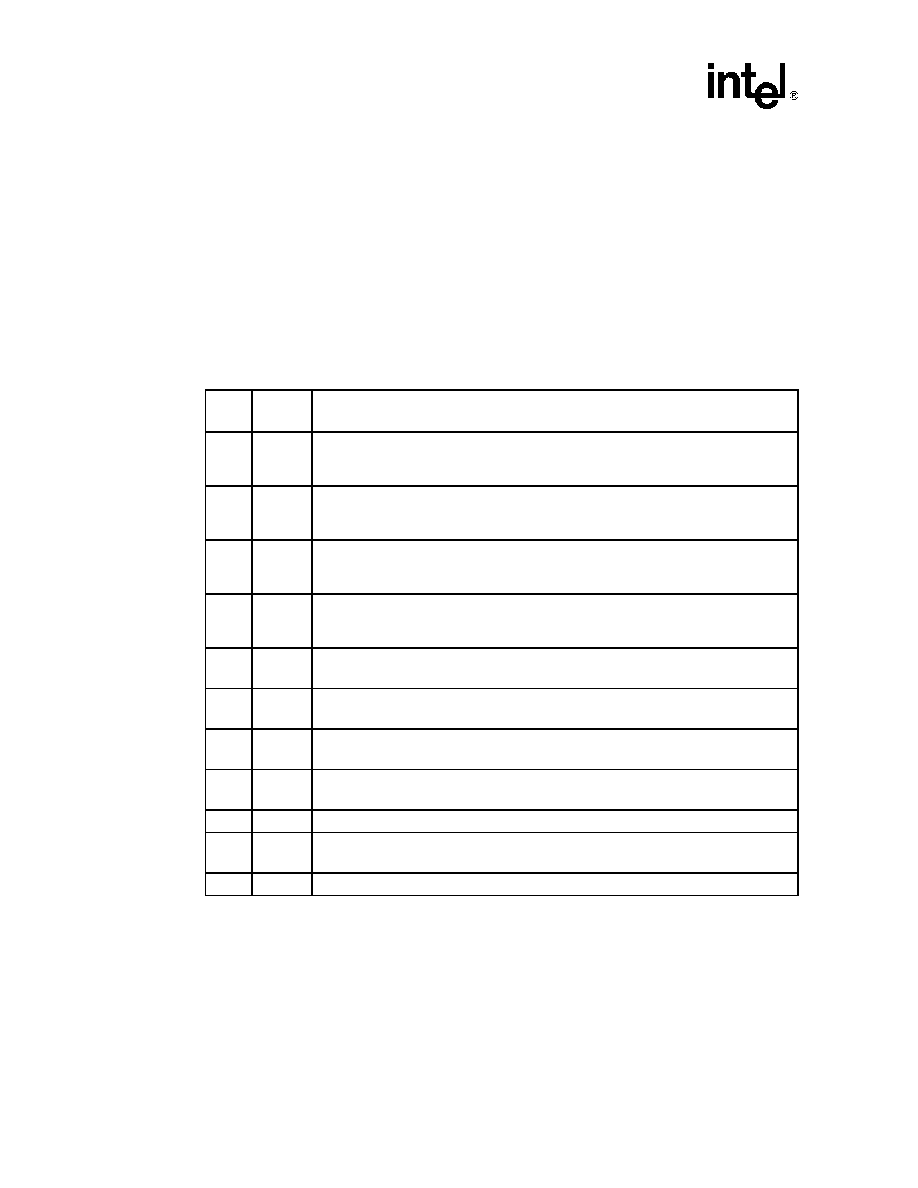

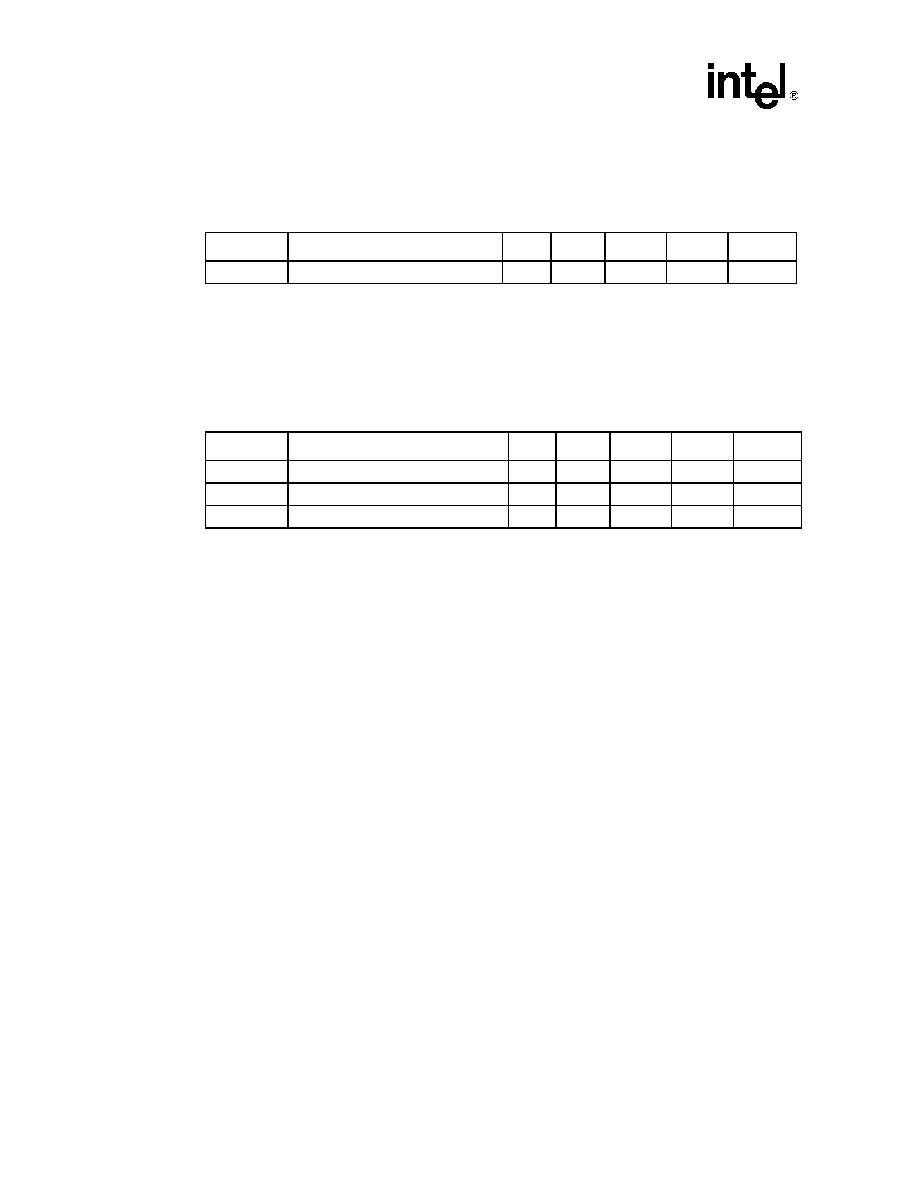

Figure 2-1. MCH Interface Signals

CB_A[7:0]

DQ_A[63:0]

DQS_A[17:0]

CMDCLK_A[3:0], CMDCLK_A[3:0]#

MA_A[12:0]

BA_A[1:0]

RAS_A#

CAS_A#

WE_A#

CS_A[7:0]#

CKE_A

RCVENIN_A#

RCVENOUT_A#

DDRCOMP_A

DDRCVOH_A

DDRCVOL_A

DDRVREF_A[5:0]

Hub

Interface

A

HI_A[11:0]

HI_STBF

HI_STBS

HIRCOMP_A

HISWNG_A

HIVREF_A

CLK66

Processor

System

Bus

Interface

HA[35:3]#

HD[63:0]#

ADS#

BNR#

BPRI#

DBSY#

DEFER#

DRDY#

HIT#

HITM#

HLOCK#

HREQ[4:0]#

HTRDY#

RS[2:0]#

CPURST#

BREQ0#

DBI[3:0]#

HADSTB[1:0]#

HDSTBP[3:0]#/HDSTBN[3:0]#

AP[1:0]#

XERR#

BINIT#

DP[3:0]#

RSP#

HCLKINP, HLCKINN

HDVREF[3:0]

HAVREF[1:0]

HCCVREF

HXSWNG, HYSWNG

HXRCOMP, HYRCOMP

DDR

Channel

A

RSTIN#

XORMODE#

PWRGOOD

SMB_CLK

SMB_DATA

Clocks

and

Reset

CB_B[7:0]

DQ_B[63:0]

DQS_B[17:0]

CMDCLK_A[3:0], CMDCLK_B[3:0]#

MA_B[12:0]

BA_B[1:0]

RAS_B#

CAS_B#

WE_B#

CS_B[7:0]#

CKE_B

RCVENIN_B#

RCVENOUT_B#

DDRCOMP_B

DDRCVOH_B

DDRCVOL_B

DDRVREF_B[5:0]

DDR

Channel

B

Hub

Interface

B

HI_B[21:20]

HI_B[18:0]

PSTRBF_B

PSTRBS_B

PUSTRBF_B

PUSTRBS_B

HIRCOMP_B

HISWNG_B

HIVREF_B

CLK66

Hub

Interface

C

HI_C[21:20]

HI_C[18:0]

PSTRBF_C

PSTRBS_C

PUSTRBF_C

PUSTRBS_C

HIRCOMP_C

HISWNG_C

HIVREF_C

CLK66

Hub

Interface

D

HI_D[21:20]

HI_D[18:0]

PSTRBF_D

PSTRBS_D

PUSTRF_D

PUSTRS_D

HIRCOMP_D

HISWNG_D

HIVREF_D

CLK66

Datasheet

19

Signal Description

2.1

System Bus Interface Signals

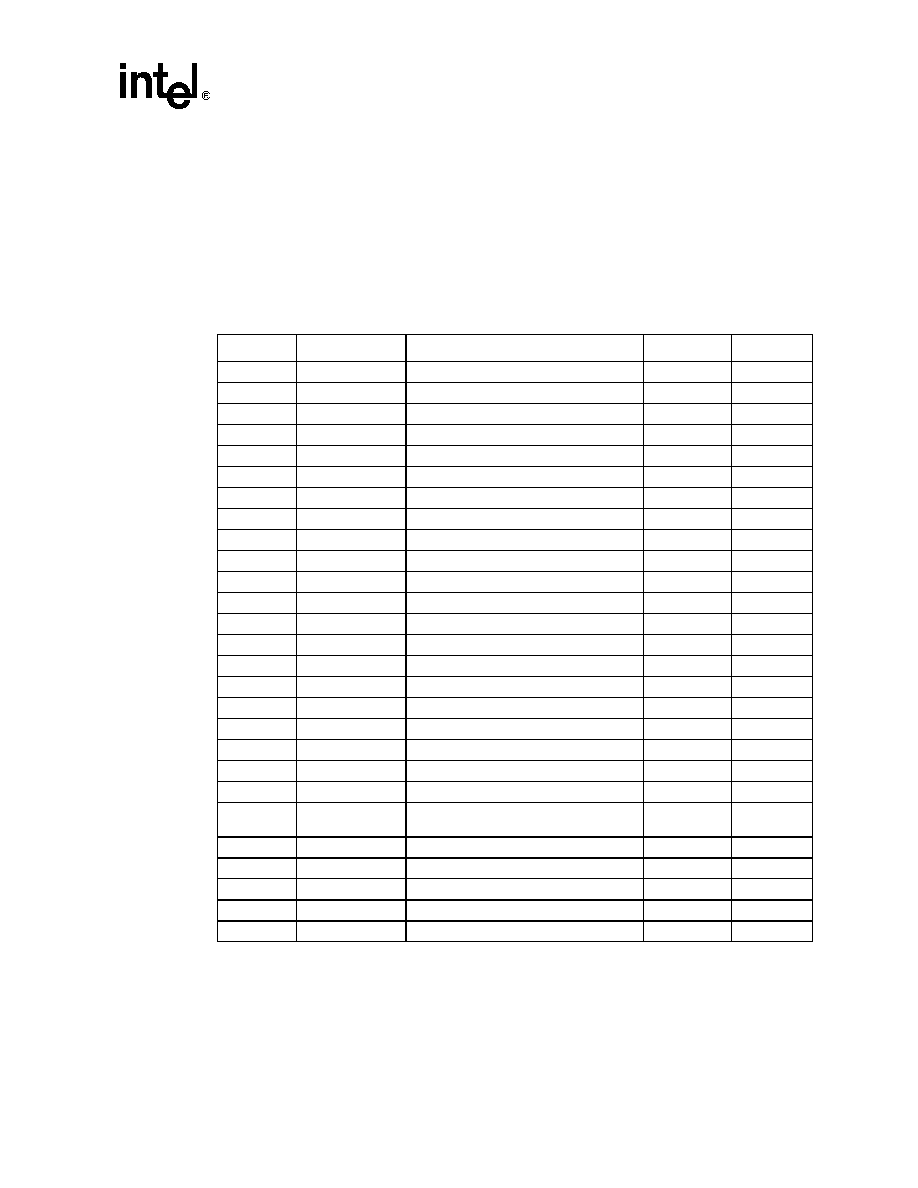

Table 2-1. System Bus Interface Signals (Sheet 1 of 3)

Signal Name

Type

Description

ADS#

I/O

AGTL+

Address Strobe: The system bus owner asserts ADS# to indicate the first of

two cycles of a request phase.

AP[1:0]#

I/O

AGTL+

Address Parity: The AP[1:0]# lines are driven by the request initiator and

provide parity protection for the Request Phase signals. AP[1:0]# are common

clock signals and are driven one common clock after the request phase.

Address parity is correct if there are an even number of electrically low signals

(low voltage) in the set consisting of the covered signals plus the parity signal.

Note that the MCH only connects to HA[35:3]#.

XERR#

I

AGTL+

Bus Error: This signal may be connected to the MCERR# signal or IERR#

signal, depending on system usage. The MCH detects an electrical high to low

transition on this input and set the correct error bit. The MCH will take no other

action except setting that bit.

BINIT#

I

AGTL+

Bus Initialize: This signal indicates an unrecoverable error occurred and can

be driven by the processor. It is latched by the MCH.

BNR#

I/O

AGTL+

Block Next Request: BNR# is used to block the current request bus owner

from issuing a new requests. This signal is used to dynamically control the

system bus pipeline depth.

BPRI#

O

AGTL+

Priority Agent Bus Request: The MCH is the only Priority Agent on the

system bus. It asserts this signal to obtain ownership of the address bus. The

MCH has priority over symmetric bus requests and will cause the current

symmetric owner to stop issuing new transactions unless the HLOCK# signal is

asserted.

BREQ0#

I/O

AGTL+

Bus Request 0: The MCH pulls the processor bus BREQ0# signal low during

CPURST#. The signal is sampled by the processors on the active-to-inactive

transition of CPURST#. The minimum setup time for this signal is four HCLKs.

The minimum hold time is two HCLKs and the maximum hold time is 20 HCLKs.

BREQ0# should be Tristate after the hold time requirement has been satisfied.

CPURST#

O

AGTL+

CPU Reset: The MCH asserts CPURST# while RSTIN# (PCIRST# from

ICH3-S) is asserted and for approximately 1 ms after RSTIN# is deasserted.

CPURST# allows the processors to begin execution in a known state.

DBSY#

I/O

AGTL+

Data Bus Busy: This signal is used by the data bus owner to hold the data bus

for transfers requiring more than one cycle.

DEFER#

O

AGTL+

Defer: When asserted, the MCH will terminate the transaction currently being

snooped with either a deferred response or with a retry response.

DP[3:0]#

I/O

AGTL+

Host Data Parity: The DP[3:0]# signals provide parity protection for HD[63:0]#.

The DP[3:0]# signals are common clock signals and are driven one common

clock after the data phases they cover. DP[3:0]# are driven by the same agent

driving HD[63:0]#.

Data parity is correct if there are an even number of electrically low signals (low

voltage) in the set consisting of the covered signals plus the parity signal.

DBI[3:0]#

I/O

AGTL+

4x

Dynamic Bus Inversion: The DBI[3:0]# signals are driven along with the

HD[63:0]# signals. They indicate when the associated signals are inverted.

DBI[3:0]# are asserted such that the number of data bits driven electrically low

(low voltage) within the corresponding 16 bit group never exceeds 8.

DRDY#

I/O

AGTL+

Data Ready: This signal is asserted for each cycle that data is transferred.

Signal Description

20

Datasheet

HA[35:3]#

I/O

GTL+

2x

Host Address Bus: HA[35:3]# connect to the system address bus. During

processor cycles, HA[35:3]# are inputs. The MCH drives HA[35:3]# during

snoop cycles on behalf of hub interface initiators.

HADSTB[1:0]#

I/O

AGTL+

2x

Host Address Strobe: The source synchronous strobes are used to latch

HA[35:3]# and HREQ[4:0]#.

HD[63:0]#

I/O

AGTL+

4x

Host Data: These signals are connected to the system data bus.

HDSTBP[3:0]#

HDSTBN[3:0]#

I/O

AGTL+

4x

Differential Host Data Strobes: The differential source synchronous strobes

are used to latch HD[63:0]# and DBI[3:0]#.

Strobe Data Bits Associated

HDSTBP3#, HDSTBN3# HD[63:48]#, DBI3#

HDSTBP2#, HDSTBN2# HD[47:32]#, DBI2#

HDSTBP1#, HDSTBN1# HD[31:16]#, DBI1#

HDSTBP0#, HDSTBN0# HD[15:0]#, DBI0#

HIT#

I/O

AGTL+

Hit: HIT# indicates that a caching agent holds an unmodified version of the

requested line. This signal is also driven in conjunction with HITM# by the target

to extend the snoop window.

HITM#

I/O

AGTL+

Hit Modified: HITM# indicates that a caching agent holds a modified version of

the requested line and that this agent assumes responsibility for providing the

line. HITM# is driven in conjunction with HIT# to extend the snoop window.

HLOCK#

I

AGTL+

Host Lock: All system bus cycles are sampled with the assertion of HLOCK#

and ADS#, until the negation of HLOCK#. This operation is atomic.

HREQ[4:0]#

I/O

AGTL+

2x

Host Request Command: HREQ[4:0]# defines the attributes of the request.

These signals are asserted by the requesting agent during both halves of a

request phase. In the first half the signals define the transaction type to a level

of detail that is sufficient to begin a snoop request. In the second half the signals

carry additional information to define the complete transaction type.

HTRDY#

O

AGTL+

Host Target Ready: HTRDY# indicates that the target of the processor

transaction is able to enter the data transfer phase.

RS[2:0]#

O

AGTL+

Response Signals: RS[2:0]# indicate the type of response according to the

following table:

RS[2:0] Response Type

000 Idle state

001 Retry response

010 Deferred response

011 Reserved (not driven by MCH)

100 Hard Failure (not driven by MCH)

101 No data response

110 Implicit Writeback

111 Normal data response

RSP#

O

AGTL+

Response Parity: RSP# provides parity protection for the RS[2:0]# signals.

RSP# is always driven by the MCH and must be valid on all clocks. Response

parity is correct when there are an even number of low signals (low voltage) in

the set consisting of the RS[2:0]# signals and the RSP# signal itself.

HCLKINP,

HLCKINN

I

CMOS

Differential Host Clock In: These input pins receive a differential host clock

from the external clock synthesizer. The clock is used by all the MCH logic in

the host clock domain.

HDVREF[3:0]

I

Analog

Host Data Reference Voltage: RHDVREF[3:0] are the reference voltage inputs

for the 4x data signals of the Host GTL interface.

Table 2-1. System Bus Interface Signals (Sheet 2 of 3)

Signal Name

Type

Description

Datasheet

21

Signal Description

HAVREF[1:0]

I

Analog

Host Address Reference Voltage: HAVREF[1:0] are the reference voltage

inputs for the 2x address signals of the Host GTL interface.

HCCVREF

I

Analog

Host Common Clock Reference Voltage: HCCVREF is the reference voltage

input for the common clock signals of the Host GTL interface

HXSWNG,

HYSWNG

I

Analog

Host Voltage Swing: These signals provide a reference voltage used by the

system bus RCOMP circuit.

HXRCOMP,

HYRCOMP

I

Analog

Host RCOMP: These signals are used to calibrate the Host AGTL+ I/O buffers.

Table 2-1. System Bus Interface Signals (Sheet 3 of 3)

Signal Name

Type

Description

Signal Description

22

Datasheet

2.2

DDR Channel A Signals

Table 2-2. DDR Channel_A Interface Signals

Signal Name

Type

Description

CB_A[7:0]

I/O

SSTL-2

DDR Channel A Check bits: These check bits are required to

provide ECC support.

DQ_A[63:0]

I/O

SSTL-2

DDR Channel A Data Bus: The DDR data bus provides the data

interface for the DRAM devices.

DQS_A[17:0]

I/O

SSTL-2

DDR Channel A Data Strobes: DQS_A[17:0] are the DDR data

strobes. Each data strobe is used to strobe a set of 4 or 8 data

signals.

CMDCLK_A[3:0],

CMDCLK_A[3:0]#

O

CMOS

DDR Channel A Command CLOCK: These signals are the DDR

command clocks used by the DDR DRAMs to latch MA[12:0],

BA[1:0], RAS#, CAS#, WE#, CKE#, and CS# signals.

MA_A[12:0]

O

SSTL-2

DDR Channel A Memory Address: MA_A[12:0] are the DDR

memory address signals.

BA_A[1:0]

O

SSTL-2

DDR Channel A Bank Address: BA_A[1:0] are the DDR bank

address signals. These bits select the bank within the DDR DRAM.

RAS_A#

O

SSTL-2

DDR Channel A Row Address Strobe: RAS_A# is used to indicate

a valid row address and open a row.

CAS_A#

O

SSTL-2

DDR Channel A Column Address Strobe: CAS_A# is used to

indicate a valid column address and initiate a transaction.

WE_A#

O

SSTL-2

DDR Channel A Write Enable: WE_A# is used to indicate a write

cycle.

CS_A[7:0]#

O

SSTL-2

DDR Channel A Chipselect: The chip select signals are used to

indicate which DRAM device cycles are targeted.

CKE_A

O

SSTL-2

DDR Channel a Clock Enable: CKE_A is the DDR clock enable

signal.

RCVENIN_A#

I

SSTL-2

Receive Enable Input: RCVENIN_A# is used for DRAM timing.

RCVENOUT_A#

O

SSTL-2

Receive Enable Output: RCVENOUT_A# is used for DRAM timing.

DDRCOMP_A

I

CMOS

Compensation for DDR A: This signal is used to calibrate the DDR

buffers.

DDRCVOH_A

I

Analog

Compensation for DDR A: This signal is used to calibrate the DDR

buffers.

DDRCVOL_A

I

Analog

Compensation for DDR A: This signal is used to calibrate the DDR

buffers.

DDRVREF_A[5:0]

I

Analog

DDR Channel A Voltage Reference: DDR reference voltage input.

Datasheet

23

Signal Description

2.3

DDR Channel B Signals

Table 2-3. DDR Channel_B Interface Signals

Signal Name

Type

Description

CB_B[7:0]

I/O

SSTL-2

DDR Channel B Check bits: These check bits are required to provide

ECC support.

DQ_B[63:0]

I/O

SSTL-2

DDR Channel B Data Bus: The DDR data bus provides the data interface

for the DRAM devices.

DQS_B[17:0]

I/O

SSTL-2

DDR Channel B Data Strobes: DQS_B[17:0] are the DDR data strobes.

Each data strobe is used to strobe a set of 4 or 8 data signals.

CMDCLK_B[3:0],

CMDCLK_B[3:0]#

O

CMOS

DDR Channel B Command CLOCK: These signals are the DDR

command clocks used by the DDR DRAMs to latch MA[12:0], BA[1:0],

RAS#, CAS#, WE#, CKE#, and CS# signals.

MA_B[12:0]

O

SSTL-2

DDR Channel B Memory Address: MA_B[12:0] are the DDR memory

address signals.

BA_B[1:0]

O

SSTL-2

DDR Channel B Bank Address: BA_B[1:0] are the DDR bank address

signals. These bits select the bank within the DDR DRAM.

RAS_B#

O

SSTL-2

DDR Channel B Row Address Strobe: RAS_B# is used to indicate a

valid row address and open a row.

CAS_B#

O

SSTL-2

DDR Channel B Column Address Strobe: CAS_B# is used to indicate a

valid column address and initiate a transaction.

WE_B#

O

SSTL-2

DDR Channel B Write Enable: WE_B# is used to indicate a write cycle.

CS_B[7:0]#

O

SSTL-2

DDR Channel B Chipselect: The chip select signals are used to indicate

which DRAM device cycles are targeted.

CKE_B

O

SSTL-2

DDR Channel B Clock Enable: CKE_B is the DDR clock enable signal.

RCVENIN_B#

I

SSTL-2

Receive Enable Input: RCVENIN_B# is used for DRAM timing.

RCVENOUT_B#

O

SSTL-2

Receive Enable Output: RCVENOUT_B# is used for DRAM timing.

DDRCOMP_B

I/O

CMOS

Compensation for DDR B: This signal is used to calibrate the DDR

buffers.

DDRCVOH_B

I

Analog

Compensation for DDR A: This signal is used to calibrate the DDR

buffers.

DDRCVOL_B

I

Analog

Compensation for DDR A: This signal is used to calibrate the DDR

buffers.

DDRVREF_B[5:0]

I

Analog

DDR Channel B Voltage Reference: DDR reference voltage input.

Signal Description

24

Datasheet

2.4

Hub Interface_A Signals

NOTES:

1. Clk66 is being shared by HI_A-D. Physically there is one CLK 66 pin on the MCH.

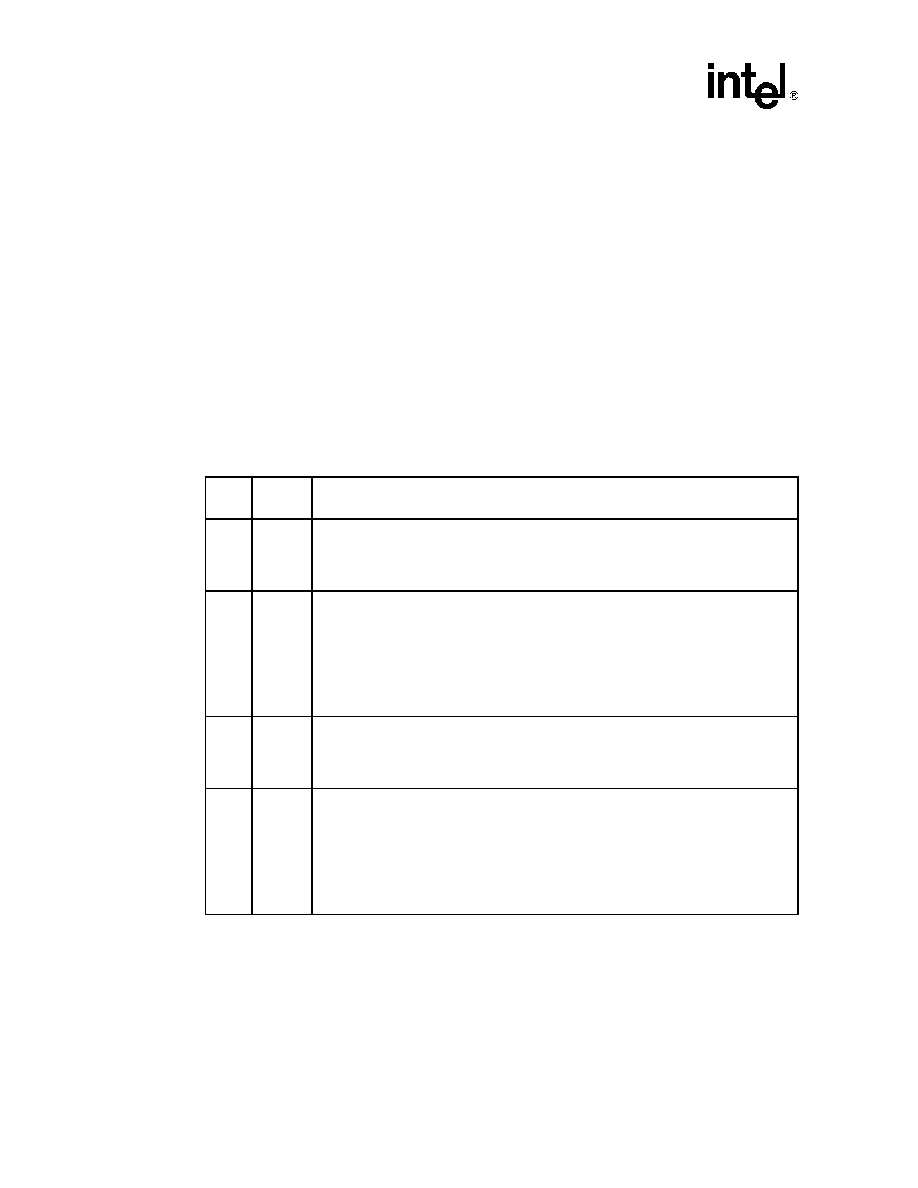

Table 2-4. HI _A Signals

Signal Name

Type

Description

HI_A[11:0]

I/O

(as/t/s)

CMOS

HI_A Signals: HI_A[11:0] are the signals used for the hub interface between

the ICH3-S and the MCH.

HI_STBF

I/O

(as/t/s)

CMOS

HI_A Strobe: HI_STBF is one of the two strobe signals used to transmit and

receive packet data over HI_A.

Note:In Normal Buffer Mode (HI 1.0) the HI_STBF signal is called HI_STB#.

Refer to the platform design guide and the MCH documentation for

appropriate hub interface strobe signals.

HI_STBS

I/O

(as/t/s)

CMOS

HI_A Strobe Compliment: HI_STBS is one of the two strobes signals used to

transmit or receive packet data over HI_A.

Note: In Normal Buffer Mode (HI 1.0) the HI_STB# signal is called HI_STB.

Refer to the platform design guide and the MCH documentation for

appropriate hub interface strobe signals.

HIRCOMP_A

I

Analog

Compensation for HI_A: This signal is used to calibrate the HI_A I/O buffers.

HISWNG_A

I

Analog

HI_A Voltage Swing: This signal provides a reference voltage used by the

HI_A RCOMP circuit.

HIVREF_A

I

Analog

HI_A Reference: HIVREF_A is a reference voltage input for the HI_A

interface.

CLK66

1

I

CMOS

66 MHz Clock In:. This pin receives a 66 MHz clock from the clock

synthesizer. This clock is shared by the HI_A, HI_B, HI_C, and HI_D.

Datasheet

25

Signal Description

2.5

Hub Interface_B Signals

1)

NOTES:

1. Clk66 is being shared by HI_A-D. Physically there is one CLK 66 pin on the MCH.

Table 2-5. HI_B Signals

Signal Name

Type

Description

HI_B[21:20]

I/O

(as/t/s)

CMOS

HI_B Signals: HI_B[21:20] are the ECC signals used for connection between

the 16-bit hub and the MCH.

HI_B[18:0]

I/O

(as/t/s)

CMOS

HI_B Signals: The HI_B[18:0] signals are used for connection between the

16-bit hub and the MCH.

PSTRBF_B

I/O

(as/t/s)

CMOS

HI_B Strobe First: PSTRBF_B is one of two strobes signal pairs used to

transmit or receive lower 8-bit data over HI_B.

PSTRBS_B

I/O

(as/t/s)

CMOS

HI_B Strobe Second: PSTRBS_B is one of two strobes signal pairs used to

transmit or receive lower 8-bit packet data over HI_B.

PUSTRBF_B

I/O

(as/t/s)

CMOS

HI_B Upper Strobe First: PUSTRBF_B is one of two strobes signal pairs

used to transmit or receive upper 8-bit packet data over HI_B.

PUSTRBS_B

I/O

(as/t/s)

CMOS

HI_B Upper Strobe Second: PUSTRBS_B is one of two strobes signal pairs

used to transmit or receive upper 8-bit packet data over HI_B.

HIRCOMP_B

I/O

CMOS

Compensation for HI_B: This signal is used to calibrate the HI_B I/O buffers.

HISWNG_B

I

Analog

HI_B Voltage Swing: This signal provides a reference voltage used by the

HI_B RCOMP circuit.

HIVREF_B

I

Analog

HI_B Reference: HIVREF_B is a reference voltage input for the HI_B

interface.

CLK66

1

I

CMOS

66 MHz Clock In: This pin receives a 66 MHz clock from the clock

synthesizer. This clock is shared by the HI_A, HI_B, HI_C and HI_D.

Signal Description

26

Datasheet

2.6

Hub Interface_C Signals

NOTES:

1. Clk66 is being shared by HI_A-D. Physically there is one CLK 66 pin on the MCH.

Table 2-6. HI_C Signals

Signal Name

Type

Description

HI_C[21:20]

I/O

(as/t/s)

CMOS

HI_C Signals: HI_C[21:20] are the ECC signals used for connection between

the 16-bit hub and the MCH.

HI_C[18:0]

I/O

(as/t/s)

CMOS

HI_C Signals: HI_C[18:0] are the signals used for the connection between the

16-bit hub and the MCH.

PSTRBF_C

I/O

(as/t/s)

CMOS

HI_C Strobe First: PSTRBF_C is one of two strobe signal pairs used to

transmit or receive lower 8-bit data over HI_C.

PSTRBS_C

I/O

(as/t/s)

CMOS

HI_C Strobe second: PSTRBS_C is one of two strobe signals pairs used to

transmit or receive lower 8-bit data over HI_C.

PUSTRBF_C

I/O

(as/t/s)

CMOS

HI_C Upper Strobe First: PUSTRBF_C is one of two strobe signals pairs used

to transmit or receive upper 8-bit data over HI_C.

PUSTRBS_C

I/O

(as/t/s)

CMOS

HI_C Upper Strobe Second: PUSTRBS_C is one of two strobe signals pairs

used to transmit or receive upper 8-bit data over HI_C.

HIRCOMP_C

I/O

CMOS

Compensation for HI_C: This signal is used to calibrate the HI_C I/O buffers.

HISWNG_C

I

Analog

HI_C Voltage Swing: This signal provides a reference voltage used by the

HI_C RCOMP circuit.

HIVREF_C

I

Analog

HI_C Reference: HIVREF_C is a reference voltage input for the HI_C interface.

CLK66

1

I

CMOS

66 MHz Clock In:. This pin receives a 66 MHz clock from the clock synthesizer.

This clock is shared by the HI_A, HI_B, HI_C and HI_D.

Datasheet

27

Signal Description

2.7

Hub Interface_D Signals

NOTES:

1. Clk66 is being shared by HI_A-D. Physically there is one CLK 66 pin on the MCH.

Table 2-7. HI_D Signals

Signal Name

Type

Description

HI_D[21:20]

I/O

(as/t/s)

CMOS

HI_D Signals: HI_D[21:20] are ECC signals used for connection between the

16-bit hub and the MCH.

HI_D[18:0]

I/O

(as/t/s)

CMOS

HI_D Signals: HI_D[18:0] are the signals used for the connection between the

16-bit hub and the MCH.

PSTRBF_D

I/O

(as/t/s)

CMOS

HI_D Strobe First: PSTRBF_D is one of two strobe signal pairs used to

transmit or receive lower 8-bit data over HI_D.

PSTRBS_D

I/O

(as/t/s)

CMOS

HI_D Strobe Second: PSTRBS_D is one of two strobe signal pairs used to

transmit or receive lower 8-bit data over HI_D.

PUSTRF_D

I/O

(as/t/s)

CMOS

HI_D Upper Strobe First: PUSTRF_D is one of two strobe signal pairs used to

transmit or receive upper 8-bit data over HI_D.

PUSTRS_D

I/O

(as/t/s)

CMOS

HI_D Upper Strobe Second: PUSTRS_D is one of two strobe signal pairs

used to transmit or receive upper 8-bit data over HI_D.

HIRCOMP_D

I/O

CMOS

Compensation for HI_D: This signal is used to calibrate the HI_D I/O buffers.

HISWNG_D

I

Analog

HI_D Voltage Swing: This signal provides a reference voltage used by the

HI_DRCOMP circuit.

HIVREF_D

I

Analog

HI_D Reference: HIVREF_D is the reference voltage input for the HI_D

interface.

CLK66

1

I

CMOS

66 MHz Clock In:. This pin receives a 66 MHz clock from the clock synthesizer.

This clock is shared by the HI_A, HI_B, HI_C and HI_D.

Signal Description

28

Datasheet

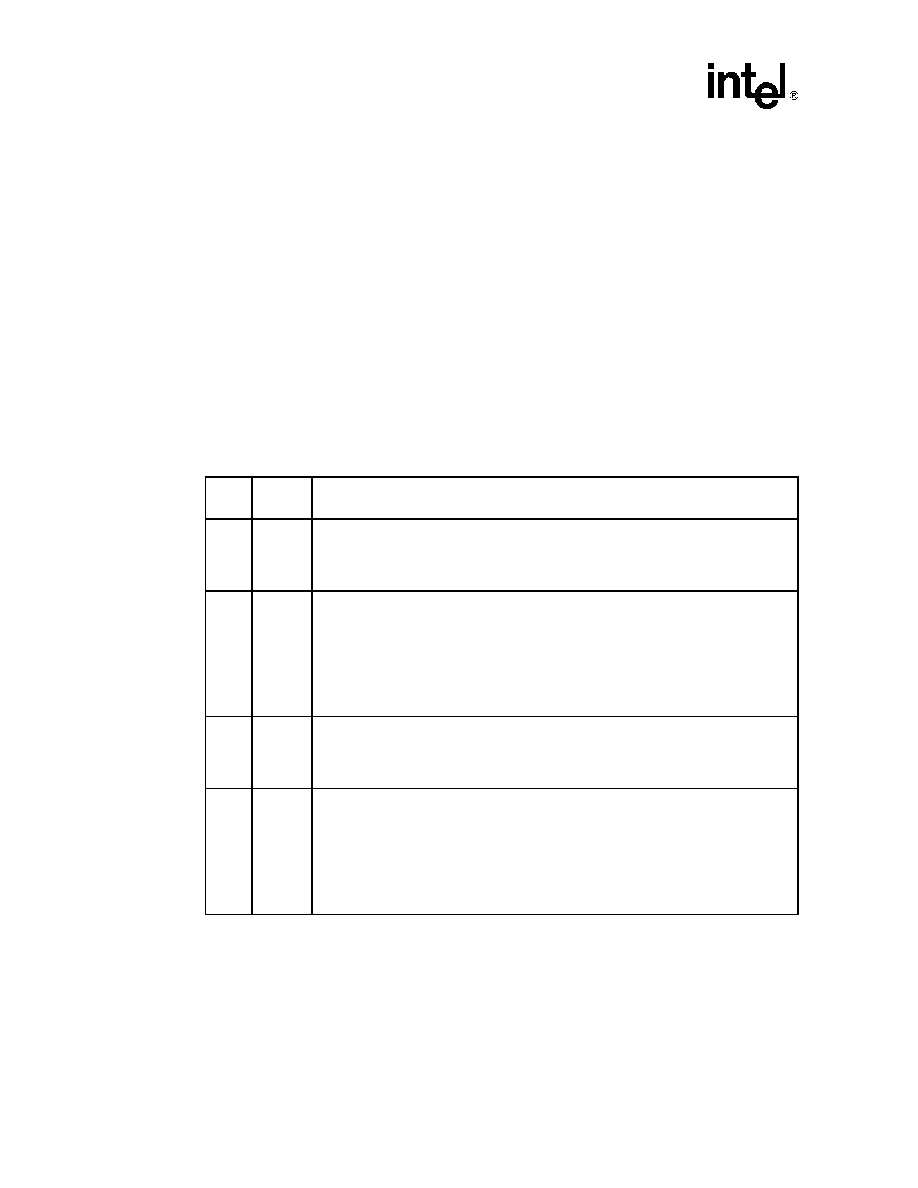

2.8

Clocks, Reset, Power, and Miscellaneous Signals

The voltage reference pins are described in the signal description sections for the associated

interface.

2.9

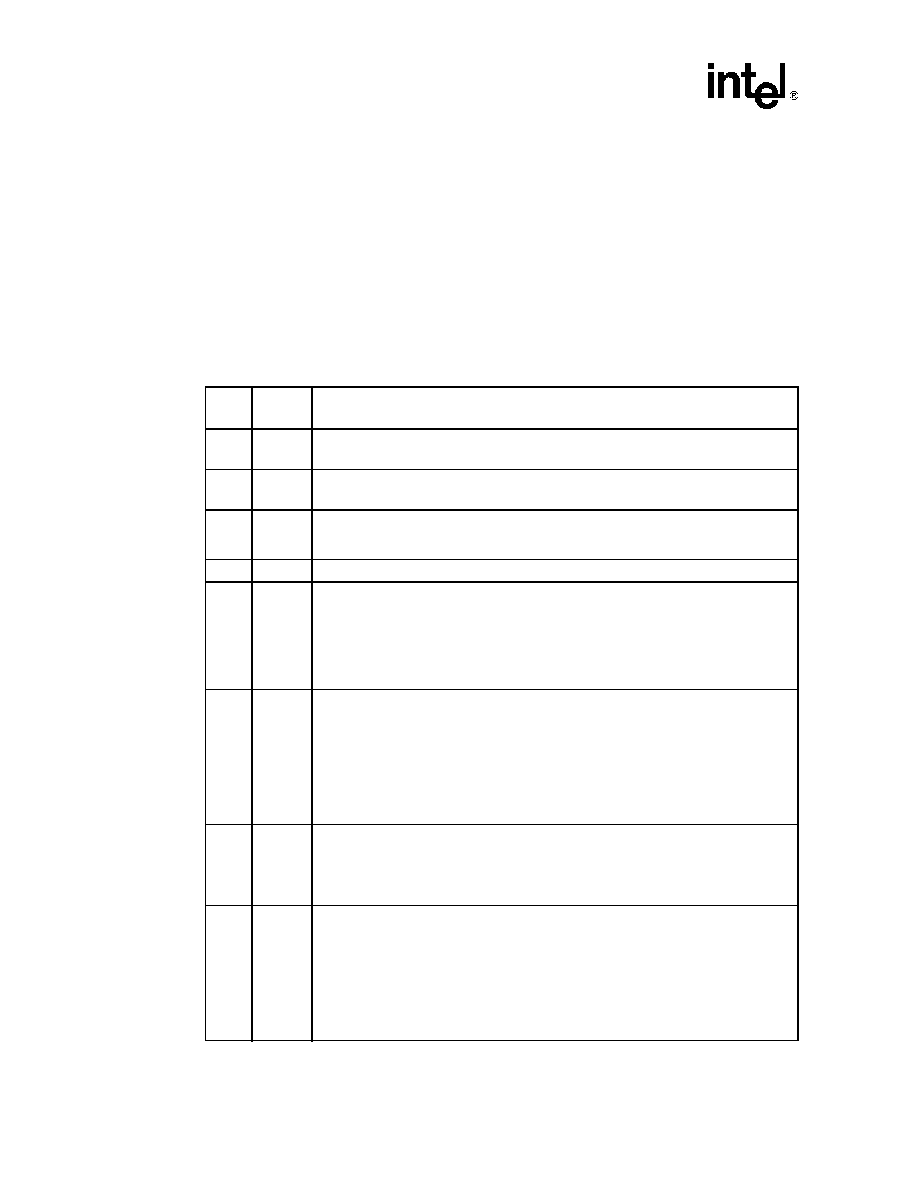

Pin States During and After Reset

This section provides the signal states during reset (assertion of RSTIN#) and immediately

following reset (deassertion of RSTIN#).

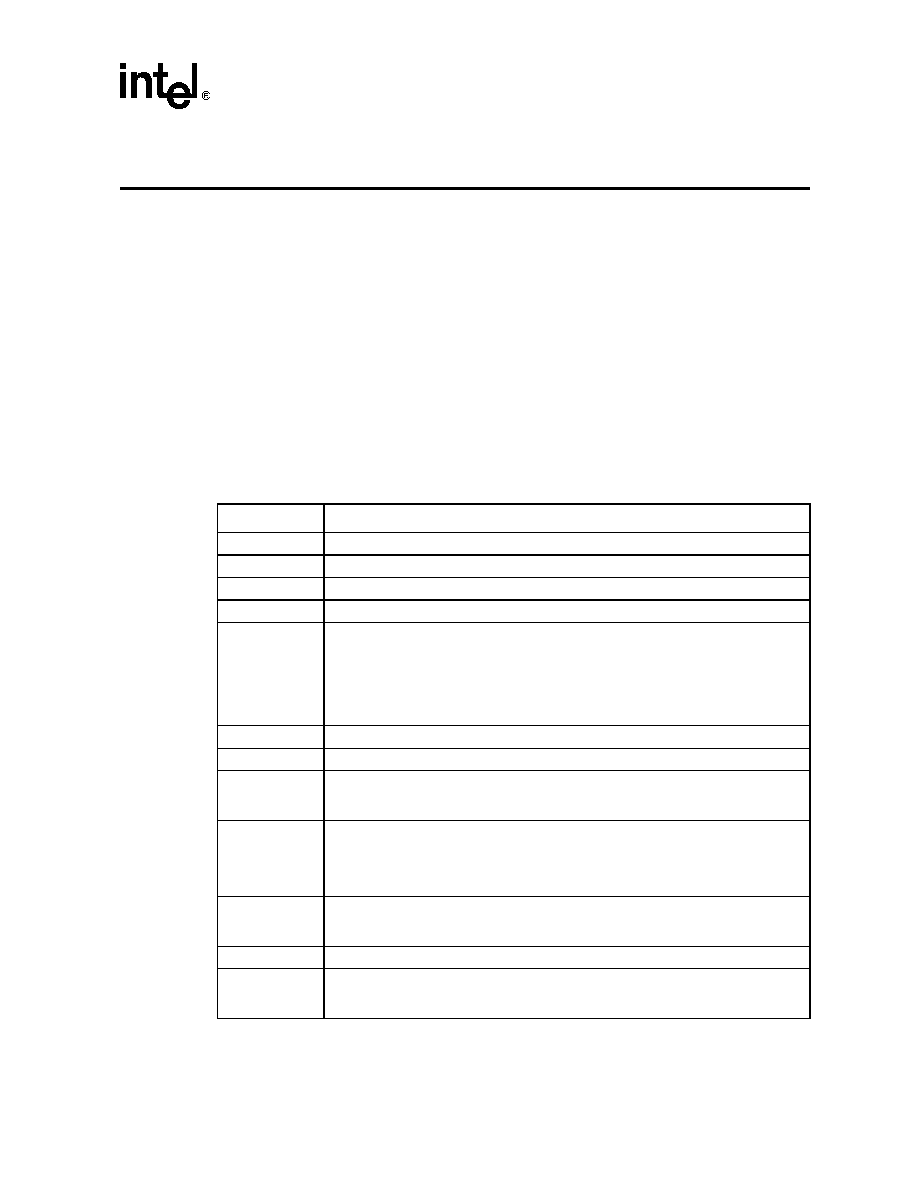

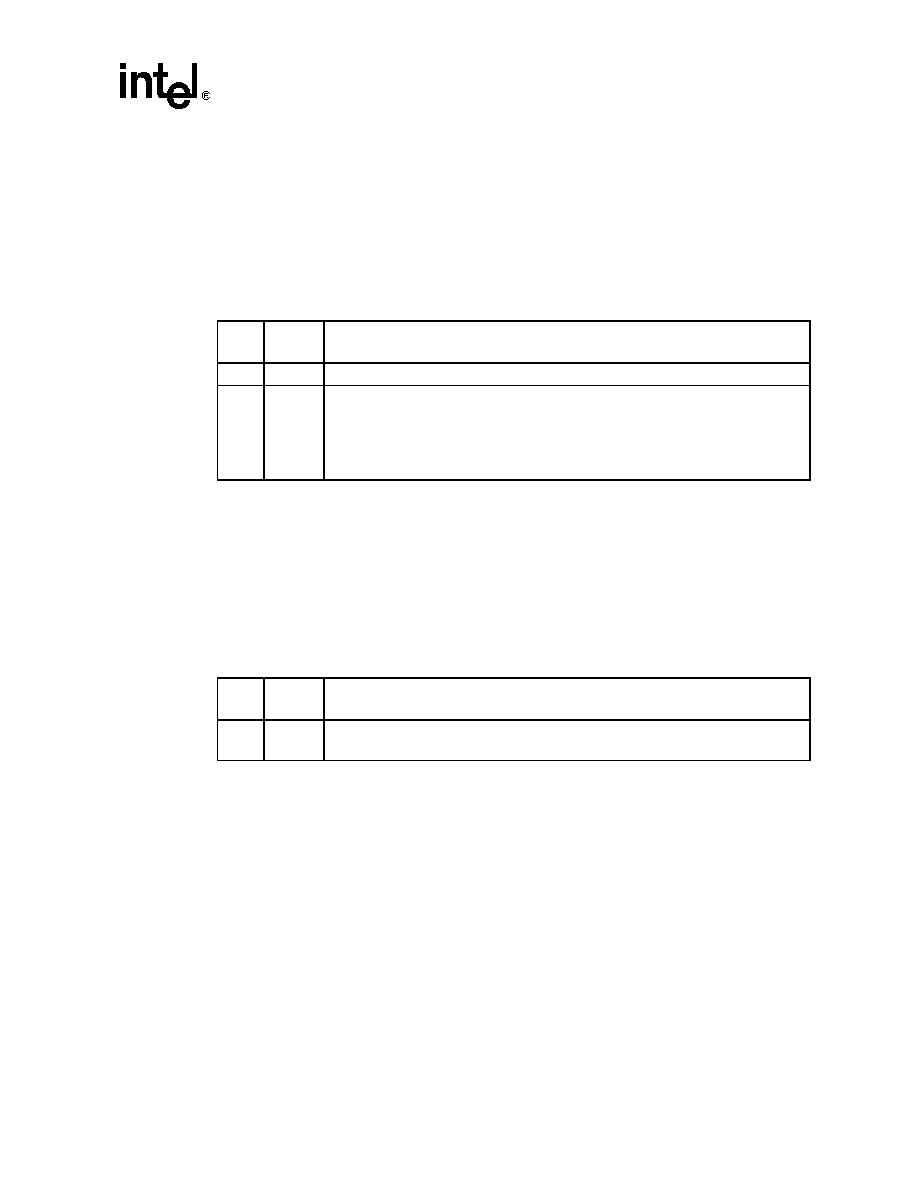

Table 2-8. Clocks, Reset, Power, and Miscellaneous Signals

Signal Name

Type

Description

RSTIN#

I

CMOS

Reset In: When asserted, RSTIN# asynchronously resets the MCH logic.

This signal is connected to the PCIRST# output of the ICH3-S.

XORMODE#

I

CMOS

Test Input: When XORMODE# is asserted, the MCH places all outputs in

XOR mode for board-level testing.

PWRGOOD

I

Power Good: This signal resets the MCH component, including "sticky"

logic. It is driven by external logic to indicate all power rails are present.

SMB_CLK

I/O

SMBus Clock: This is the clock pin for the SMBus interface.

SMB_DATA

I/O

SMBus Data: This is the data pin for the SMBus interface.

VCC1_2

Power: These pins are 1.2 V power input pins for HI_A≠D, and the MCH

core.

VCCA1_2

Power: These pins are 1.2 V analog power input pins.

VCCAHI1_2

Power: This pin is a 1.2 V analog power input pin.

VCCACPU1_2

Power: This pin is a 1.2 V analog power input pin.

VCC_CPU

Power: For the system bus interface.

VCC2_5

Power: These pins are 2.5 V power input pins for DDR.

VSS

Ground: Ground pin.

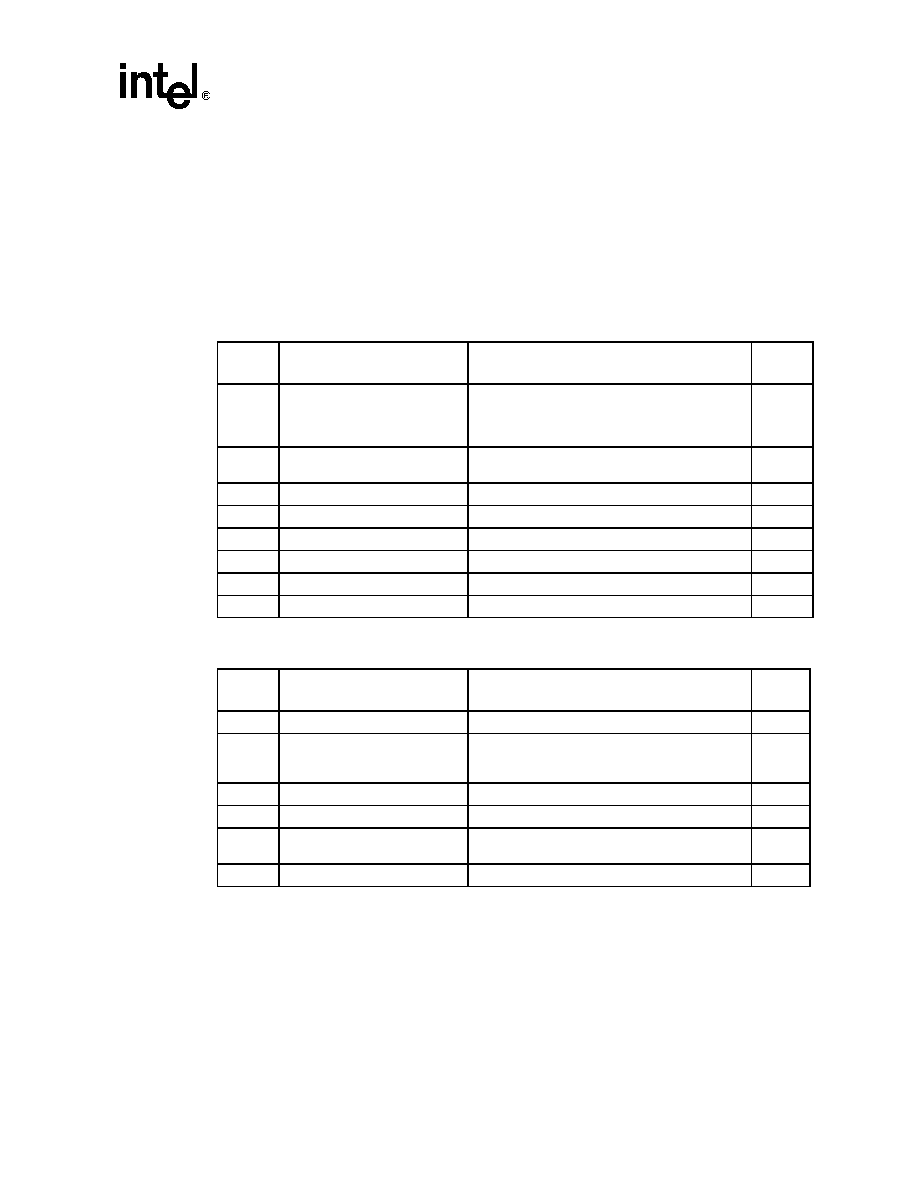

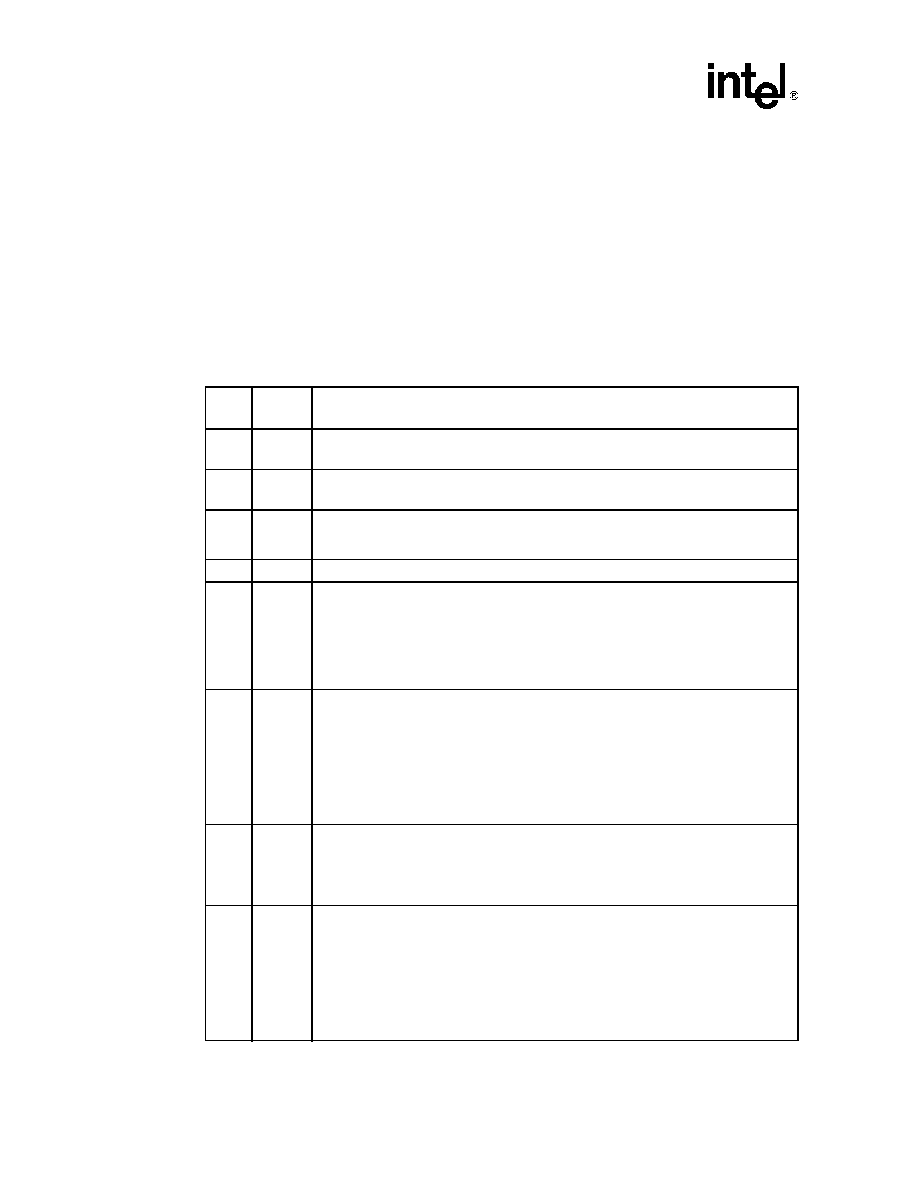

Legend

Interpretation

Drive

Strong drive (to normal value supplied by core logic, if not otherwise stated

TERM

Normal termination devices on

LV

Low voltage

HV

High voltage

IN

Input buffer enabled

ISO

Isolate inputs in inactive states

TRI

Tri-state

PU

Weak pull-up

PD

Weak pull-down

Signal Description

Datasheet

29

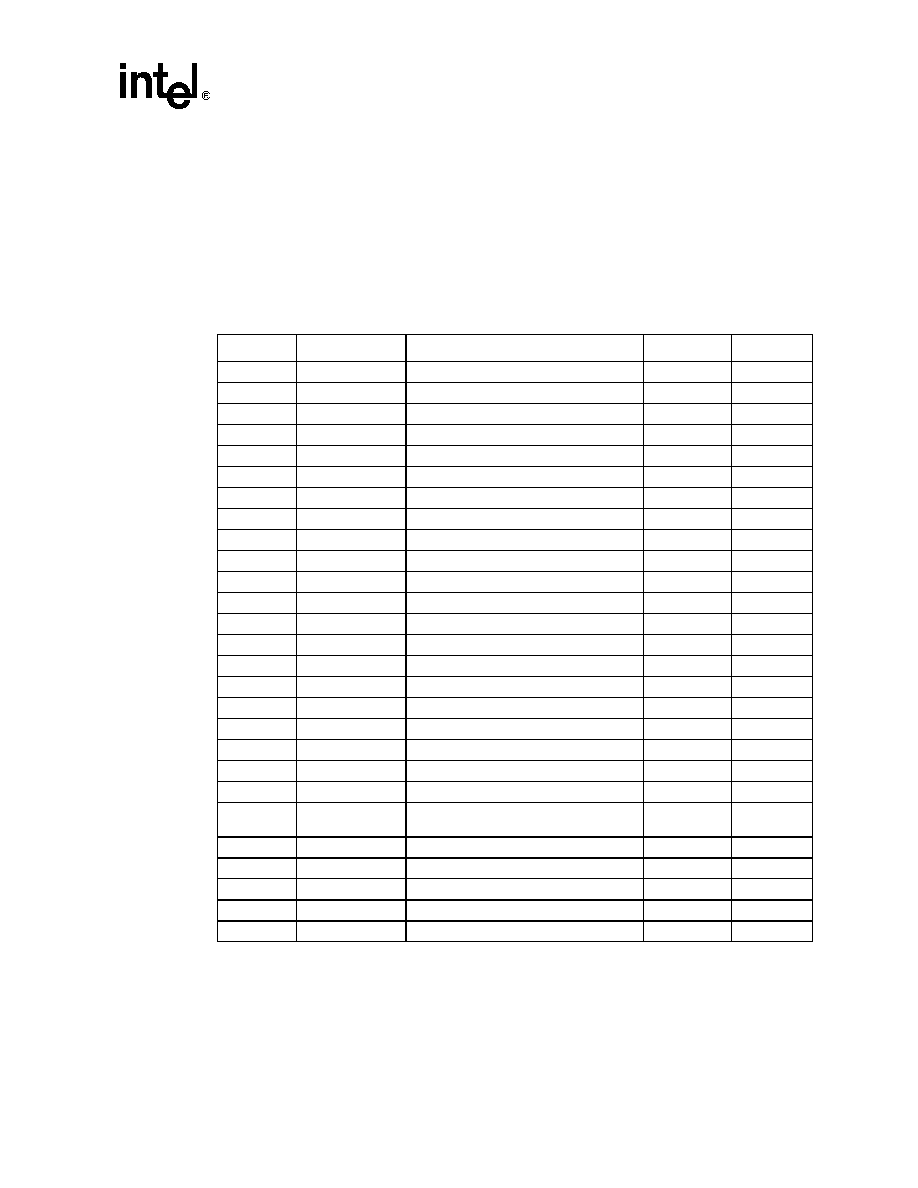

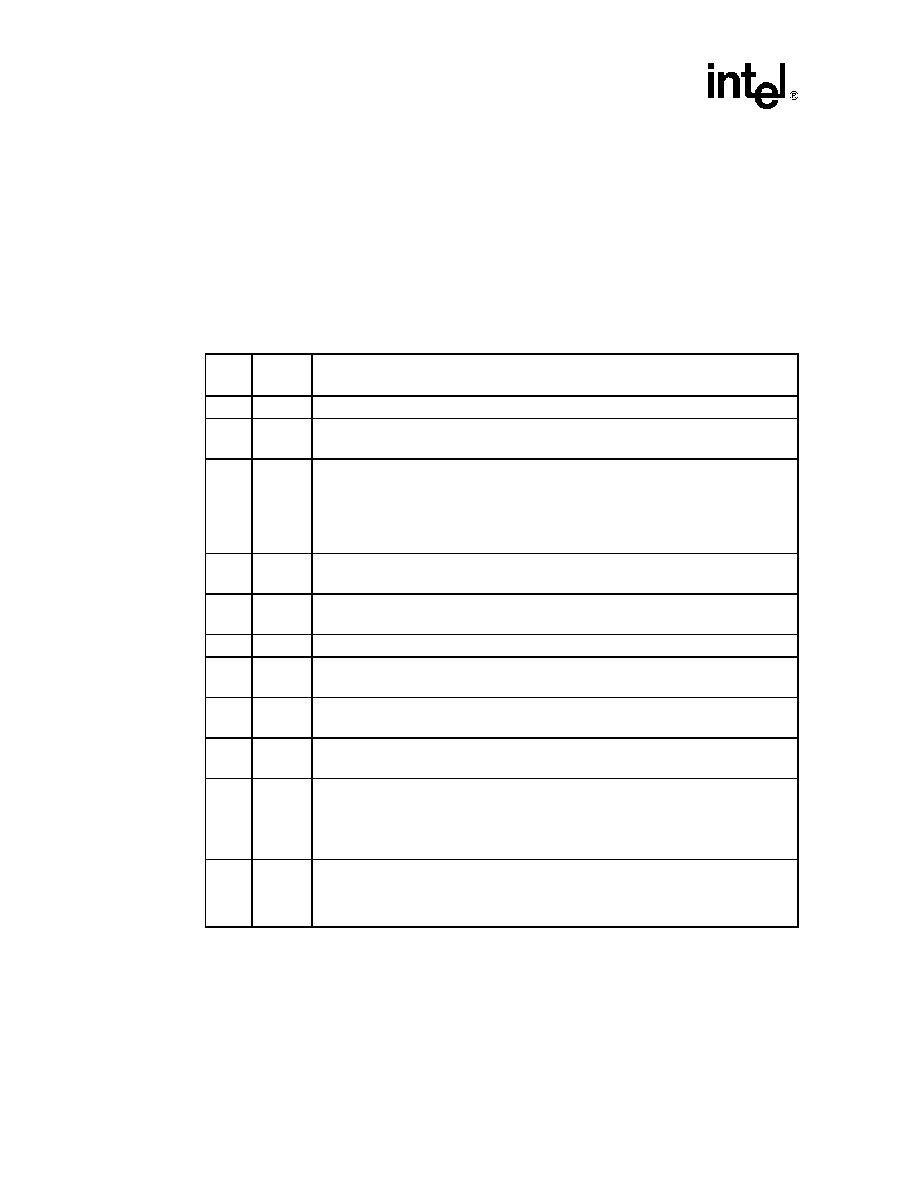

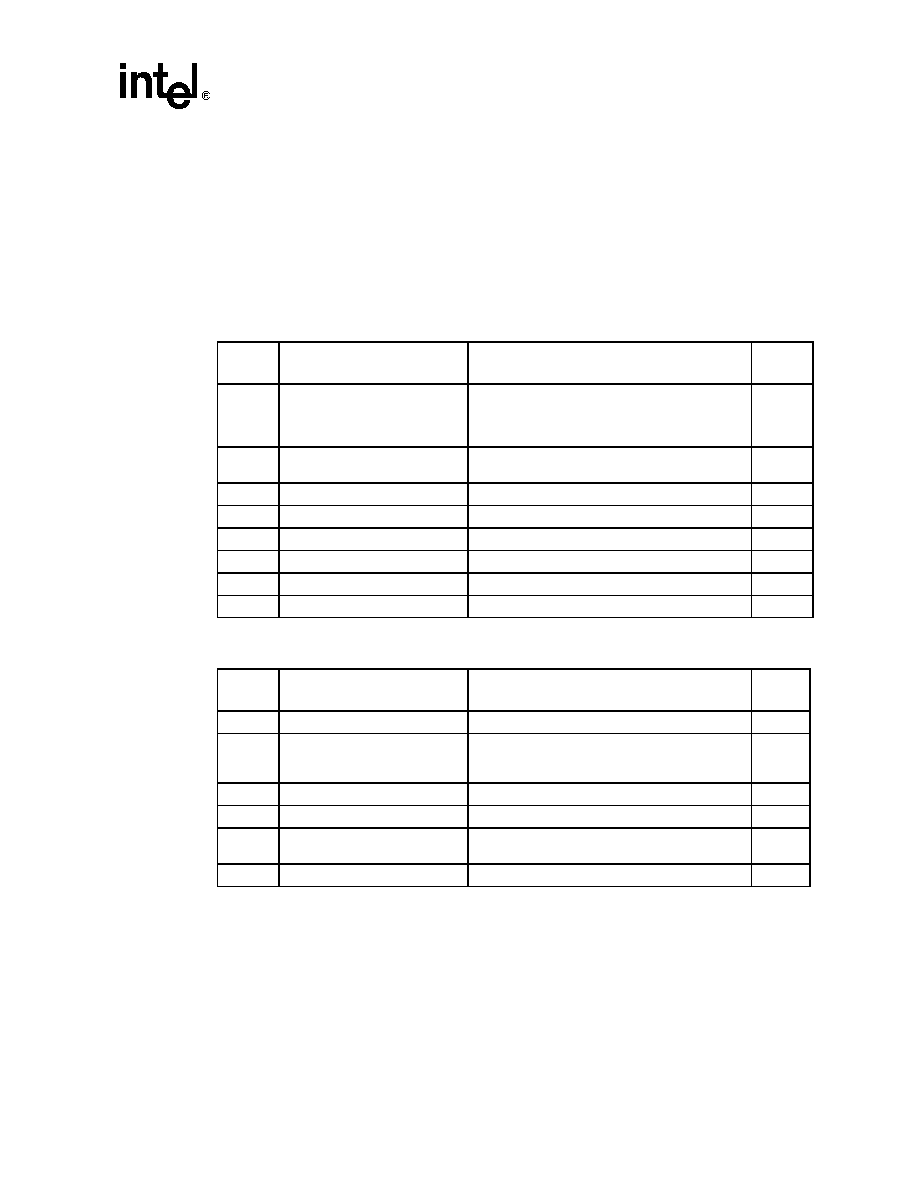

Signal Name

State During

RSTIN#

Assertion

State After

RSTIN#

Deassertion

System Bus Interface

CPURST#

DRIVE LV

TERM HV

(after 1ms)

HA[35:3]#

TERM HV

1

TERM HV

2

HADSTB[1:0]#

TERM HV

TERM HV

AP[1:0]#

TERM HV

TERM HV

HD[63:0]#

TERM HV

TERM HV

HDSTBp[3:0]#

TERM HV

TERM HV

HDSTBn[3:0]#

TERM HV

TERM HV

DEP[3:0]#

TERM HV

TERM HV

DBI[3:0]#

TERM HV

TERM HV

ADS#

TERM HV

TERM HV

BNR#

TERM HV

TERM HV

BPRI#

TERM HV

TERM HV

DBSY#

TERM HV

TERM HV

DEFER#

TERM HV

TERM HV

DRDY#

TERM HV

TERM HV

HIT#

TERM HV

TERM HV

HITM#

TERM HV

TERM HV

HLOCK#

TERM HV

TERM HV

HREQ[4:0]#

TERM HV

TERM HV

HTRDY#

TERM HV

TERM HV

RS[2:0]#

TERM HV

TERM HV

RSP#

TERM HV

TERM HV

BERR#

TERM HV

TERM HV

BREQ0#

TERM HV

DRIVE LV

3

HDVREF[3:0]

IN

IN

HAVREF[1:0]

IN

IN

HCCVREF

IN

IN

HXRCOMP

TRI

TRI after

RCOMP

HYRCOMP

TRI

TRI after

RCOMP

HXSWNG

IN

IN

HYSWNG

IN

IN

DDR Channel A Interface

CB_A[7:0]

TRI

TRI

DQ_A[63:0]

TRI

TRI

DQS_A[17:0]

TRI

TRI

CMDCLK_A[3:0]

LV

Starts to

toggle

CMDCLK_A[3:0]#

LV

Starts to

toggle

MA_A[12:0]

Note 4

Note 4

BA_A[1:0]

Note 4

Note 4

RAS_A#

LV

LV

CAS_A#

HV

HV

WE_A#

HV

HV

CS_A[7:0]#

HV

HV

CKE_A

LV

Note 6

RCVENIN_A#

IN

IN

RCVENOUT_A#

HV

HV

DDR Channel B Interface

CB_B[7:0]

TRI

TRI

DQ_B[63:0]

TRI

TRI

DQS_B[17:0]

TRI

TRI

CMDCLK_B[3:0]

LV

Starts to

toggle

CMDCLK_B[3:0]#

LV

Starts to

toggle

MA_B[12:0]

Note 4

Note 4

BA_B[1:0]

Note 4

Note 4

RAS_B#

LV

LV

CAS_B#

HV

HV

WE_B#

HV

HV

CS_B[7:0]#

HV

HV

CKE_B

LV

Note 6

RCVENIN_B#

IN

IN

RCVENOUT_B#

HV

HV

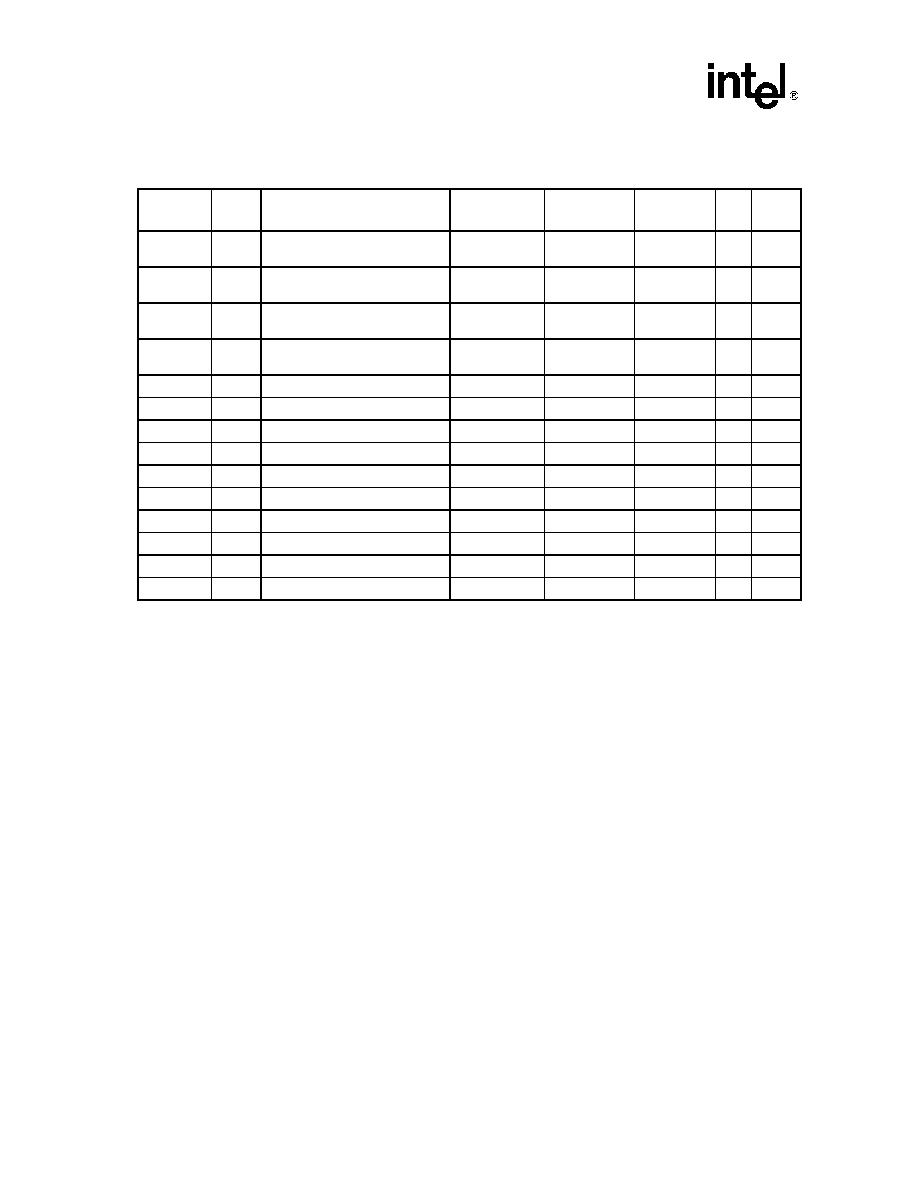

Signal Name

State During

RSTIN#

Assertion

State After

RSTIN#

Deassertion

Signal Description

30

Datasheet

NOTES:

1. DRIVE LV if POC or Straps are set

2. Any signals driven LV from POC Register go to

TERM HV two clocks after CPURST# deasserts