2051nt

ACC Microelectronics Corporation, 2500 Augustine Drive, Santa Clara, CA 95054

Phone: (408) 980-0622 Fax: (408) 980-0626

ACC MICRO 2051nt

PENTIUM-CLASS PCI SINGLE CHIP SOLUTION

FOR NOTEBOOK APPLICATIONS

DATA BOOK

ADVANCED INFORMATION

JANUARY 1997

Revision 3.0

ACC Micro

2051nt

TM

ACC Microelectronics Corporation, 2500 Augustine Drive, Santa Clara, CA 95054

Phone: (408) 980-0622 Fax: (408) 980-0626

ACC Microelectronics Corporation

2500 Augustine Drive,

Santa Clara, CA 95054

Phone: (408) 980-0622 Fax: (408) 980-0626

Copyright 1996 ACC Microelectronics Corporation. All rights reserved.

P/N 520210

Rev. 3.0

January 1997

Copyright

No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or

translated into any language or computer language, in any form or by any means, electronic, mechanical,

magnetic, optical, chemical, manual, or otherwise, without the prior written permission of ACC

Microelectronics Corp, 2500 Augustine Drive, Santa Clara, CA 95054.

Disclaimer

ACC Microelectronics Corp. makes no representations or warranties with respect to the design and

documentation herein described and especially disclaims any implied warranties of merchantability or fitness

for any particular purpose. Further, ACC Microelectronics Corp. reserves the right to revise the design and

associated documentation and to make changes from time to time in the content without obligation of ACC

Microelectronics Corp. to notify any person of such revisions or changes.

Trademarks

Single Chip Solution is registered trademark of ACC Microelectronics Corp.

All other trademarks and copyrights are the property of their respective holders.

ACC Micro

2051nt

TM

i

Table of Contents

Title

Page

1.0

Introduction

1

1.1 ACC Micro 2051nt PCI Single Chip Solution Description

1

1.2 ACC Micro 2051nt PCI Single Chip Solution Features

1

1.3 ACC Micro 2051nt Block Diagram

3

2.0

Functional Description

4

2.1 L2 Cache

4

2.2 DRAM Interface

4

2.3 PCI Bus

4

2.4 Posted Write/Pre-fetch Buffers

4

2.5 Clock

4

2.6 Power Management Modes

5

2.6.1 Fully-On

5

2.6.2 Standby

5

2.6.3 Suspend

5

2.6.4 Doze

5

2.7 Idle Timers

6

2.7.1 Global-StandBy Timer

6

2.7.2 Auto-Suspend

6

2.7.3 Local-Standby Timers

6

2.7.4 Doze Timers

6

2.7.5 Warning Timers

6

2.8 SMM/SMIs

6

2.9 Thermal Control

7

2.10 Battery Management

7

2.11 AC Power

7

2.12 Mobile PC/PCI

7

2.13 CLKRUN#

7

2.14 Device I/O Shadowing

7

3.0

ACC Micro Pin Specifications

8

3.1 Pin Description

8

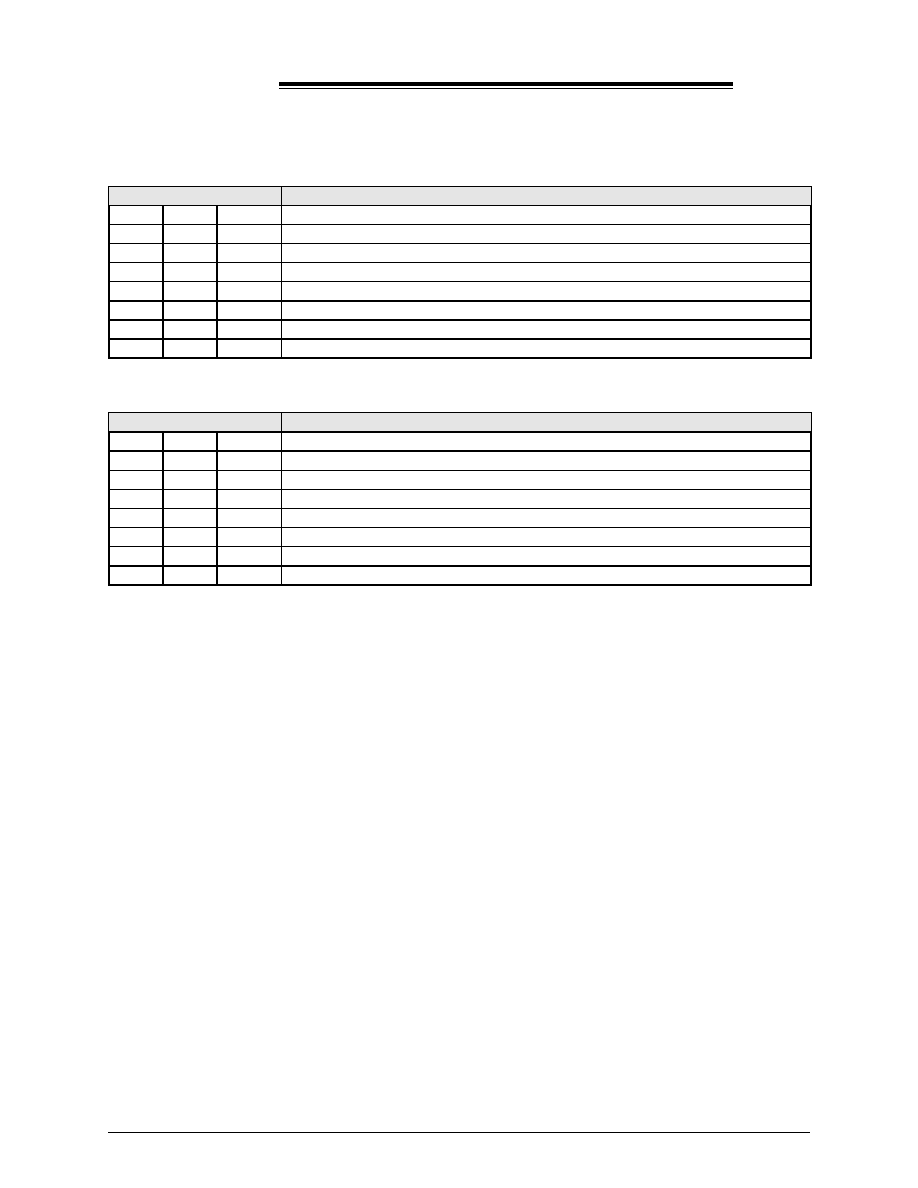

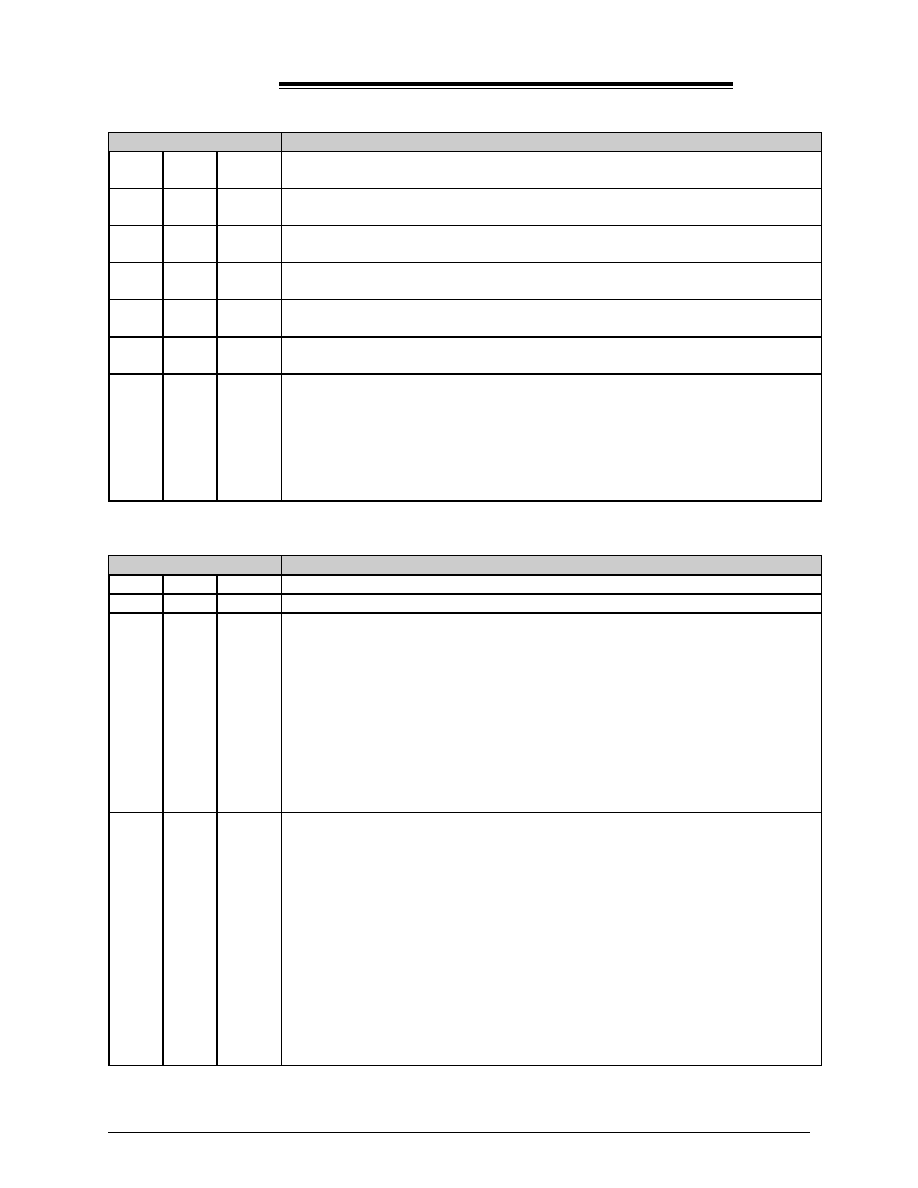

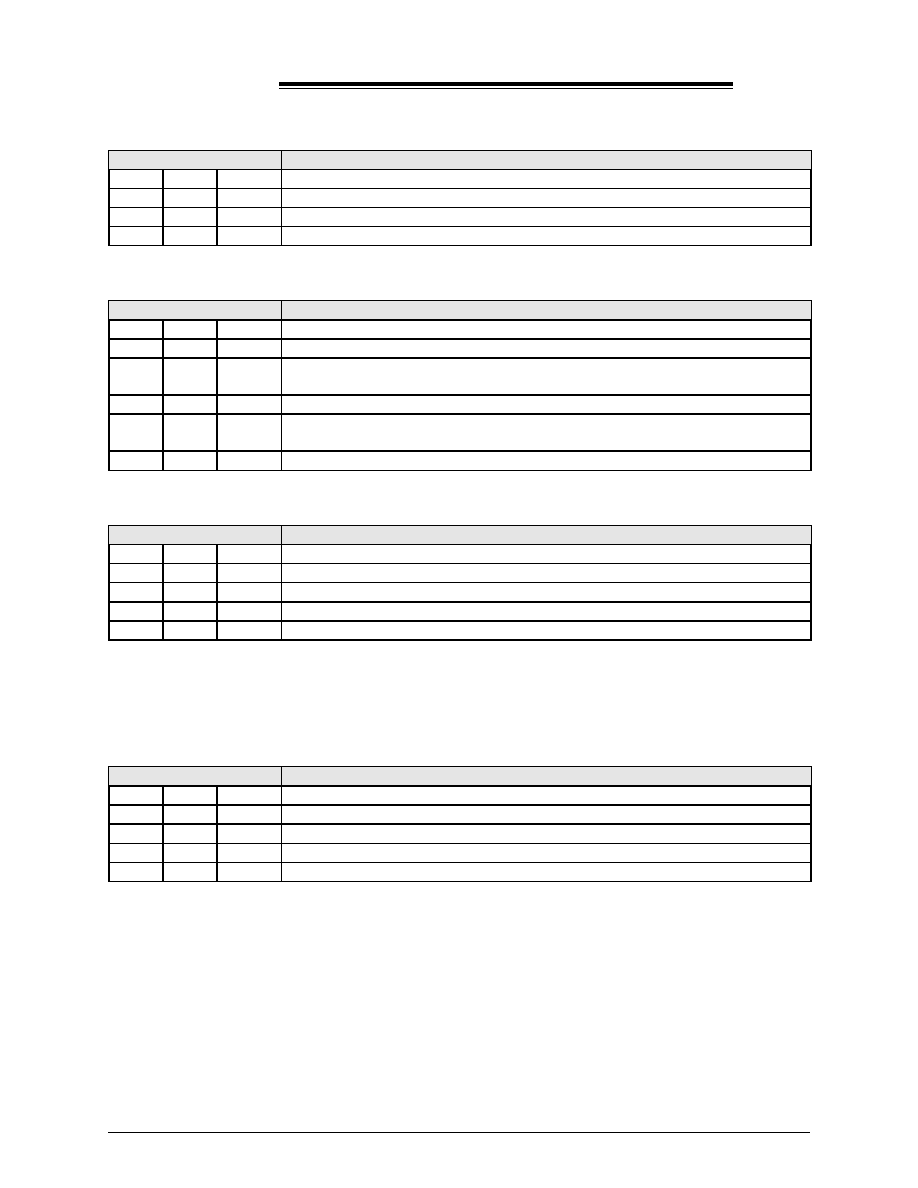

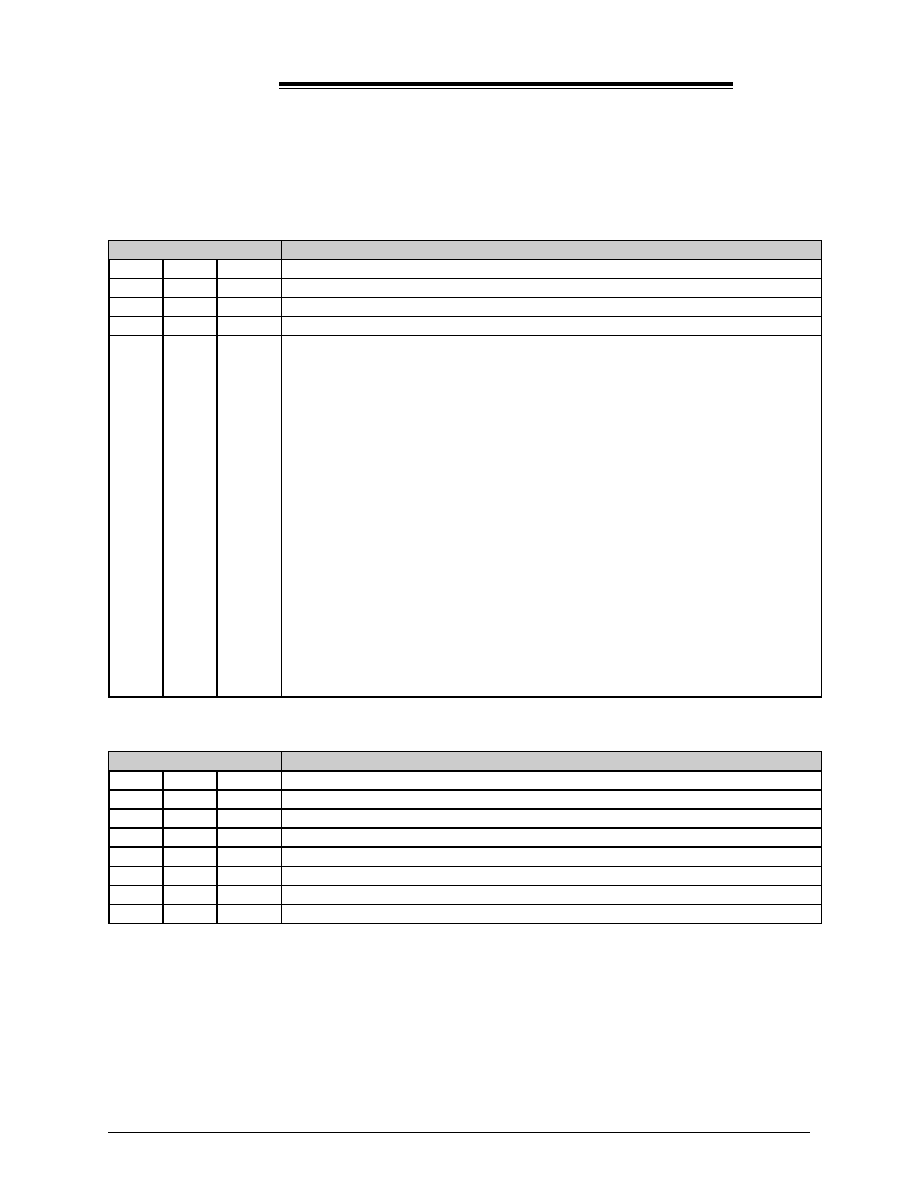

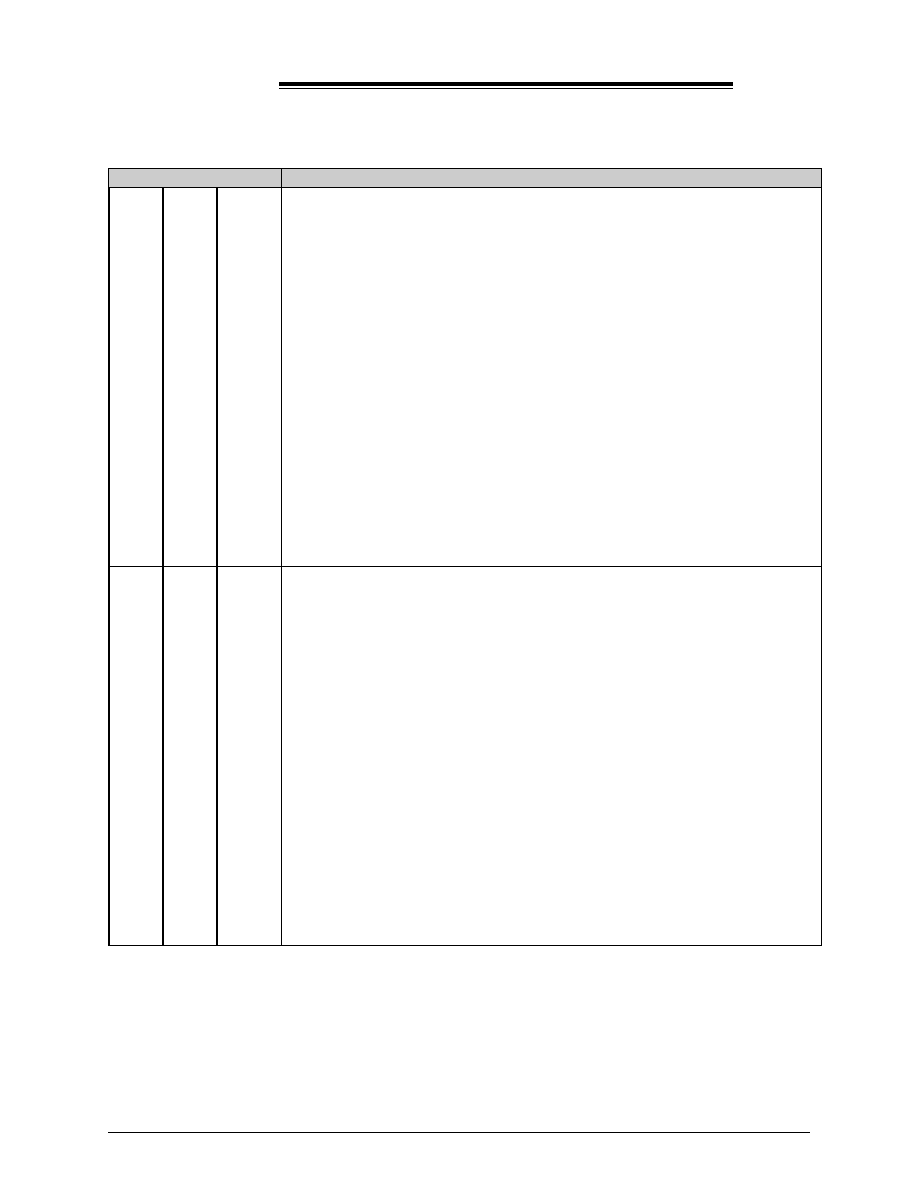

Table 3-1 Clock Interface

8

Table 3-2 CPU Interface

8

Table 3-3 Cache Interface

9

Table 3-4 DRAM Interface

11

Table 3-5 PCI Interface

11

Table 3-6 Reset Interface

12

Table 3-7 ISA Interface

12

Table 3-8 ISA/IRQ Interface

13

Table 3-9 ISA/XD Interface

14

Table 3-10 Real time Clock Interface

14

Table 3-11 Address Buffers Decodes Interface

14

ACC Micro

2051nt

TM

ii

Title

Page

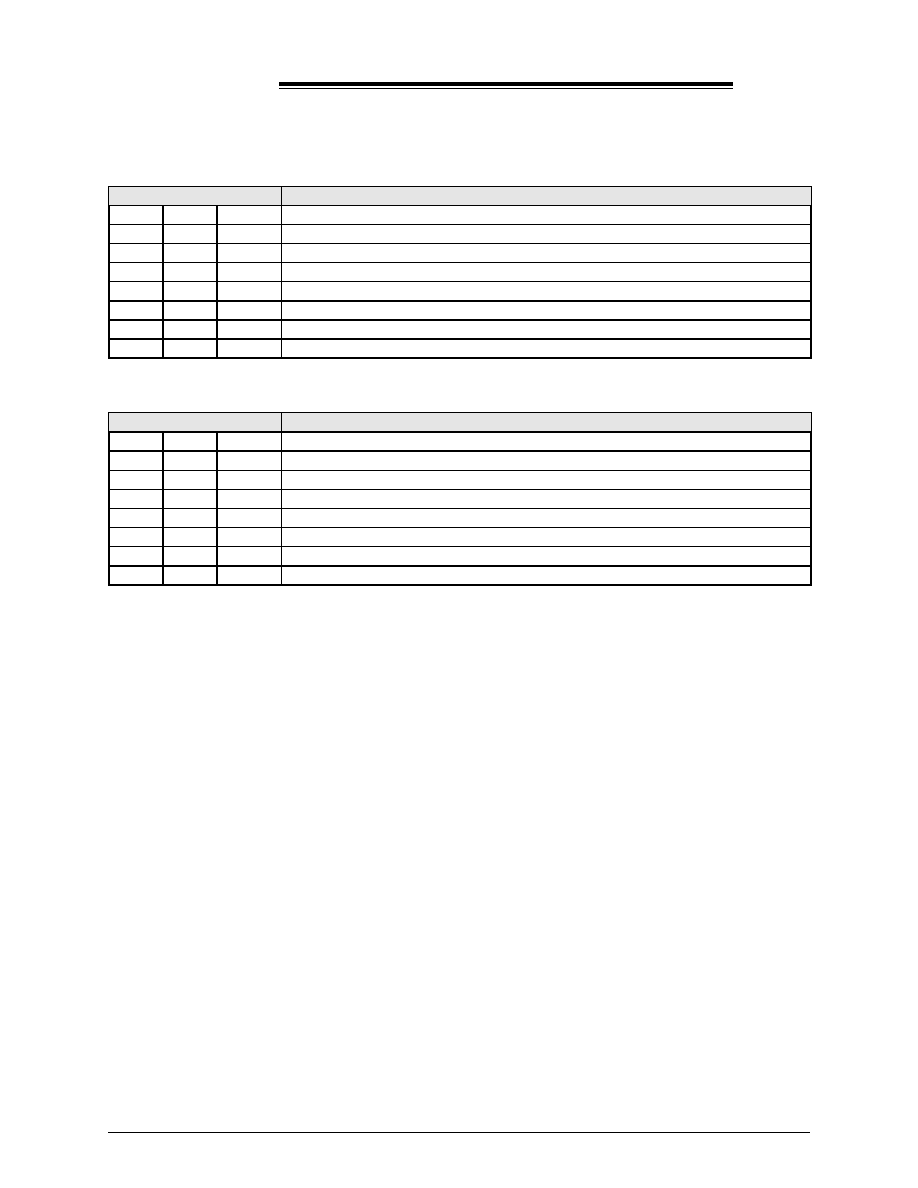

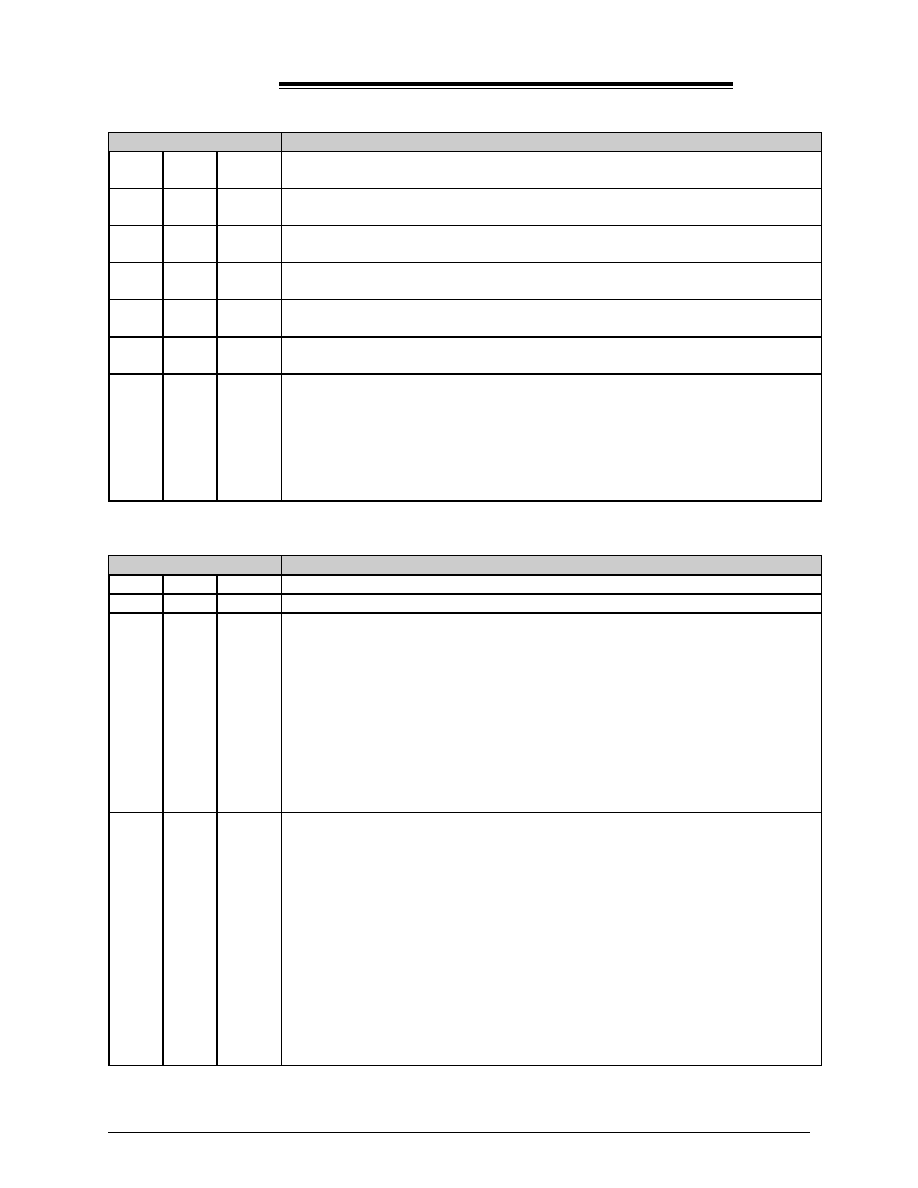

Table 3-12 PC/PCI Interface

14

Table 3-13 PMC Interface

15

Table 3-14 Misc. Interface

15

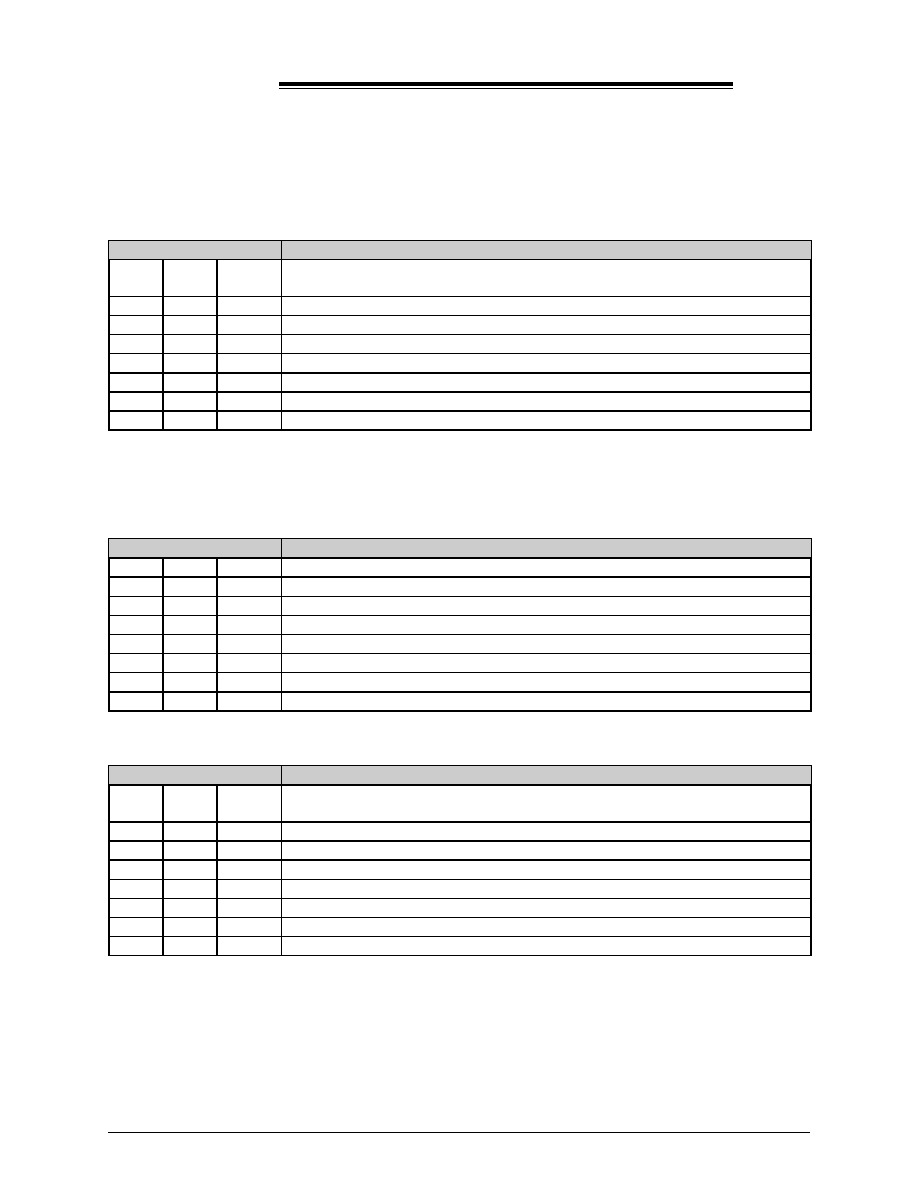

3.2 ACC Micro 2051nt Numerical Pin Arrangement (w/ L2 Cache)

16

3.3 ACC Micro 2051nt Alphabetical Pin Arrangement (w/ L2 Cache)

18

3.4 ACC Micro 2051nt Summary Table for Multiplex Pins

20

3.5 ACC Micro 2051nt Power Plane Summany Table

23

3.6 ACC Micro 2051nt Shadow Register Application

24

4.0

ACC Micro 2051nt Register Settings

26

4.1 Device 0, Function 0 Configuration

27

4.1.1 PCI Range & Control

28

4.1.2 IDE Address

34

4.2 Memory Configuration

36

4.2.1 DRAM Configuration

37

4.2.2 L2 Cache Configuration

43

4.3 Power Management

48

4.3.1 Suspend Control

48

4.3.2 GPIO

50

4.4 Device 1, Function 0 Configuration

51

4.4.1 ISA Configuration

54

4.4.2 Chip Select Functions

57

4.4.3 ISA Peripheral Selection

60

4.5 Device 1, Function 1 Configuration

63

4.5.1 PCI IDE Control

64

4.6 Standard AT Configuration

70

4.6.1 SMI Registers

70

4.6.2 VRAM & Power Control

72

4.6.3 Doze Mode Control

74

4.6.4 Warning Timers

77

4.6.5 General Chip Select

79

4.6.6 Standby Control

84

4.6.7 Suspend Control

90

4.6.8 Battery Low Control

93

4.6.9 Thermal Control Through Software Emulation

96

4.6.10 STOP Clock Control

97

4.7 Interrupt Controller Register

99

4.7.1 IRQ7-IRQ3 Edge/Level Control Register

99

4.7.2 IRQ15-IRQ9 Edge/Level Control Register

100

5.0

ACC Micro 2051nt DC Specifications

101

ACC Micro

2051nt

TM

iii

Title

Page

6.0

ACC Micro 2051nt AC Specifications

104

6.1 Timing Diagrams

104

6.1.1 Propagation Delay

104

6.1.2 Valid Delay from Rising Clock Edge

104

6.1.3 Setup and Hold Times

104

6.1.4 Float Delay

104

6.1.5 Clock High and Low Timers and Period

105

6.1.6 Pulse Width

105

6.1.7 Output to Output Delay

105

6.2 Signals Timing

106

6.2.1 CLOCK Timing

106

6.2.2.CPU Interface Timing

106

6.2.3 Asynchronous Cache Interface Timing

107

6.2.4 Synchronous Cache Interface Timing

107

6.2.5 Fast Page Mode / EDO DRAM Interface Timing

108

6.2.6 PCI Interface Timing

108

6.2.7 AT Interface Timing

109

6.3 Functional Timing Diagram

110

6.3.1 Reset Timing

110

6.3.2 Shutdown Timing

110

6.3.3 AT Bus 16-Bit Access Timing

111

6.3.4 AT Bus 8-Bit Access Timing

112

6.3.5 Fast Page Mode DRAM Access Timing-Read Cycle

112

6.3.6 Fast Page Mode Access Timing-Write Cycle

113

6.3.7 EDO Page-Write Missed Cycle Timing

114

6.3.8 EDO Page-Read Missed Cycle Timing

115

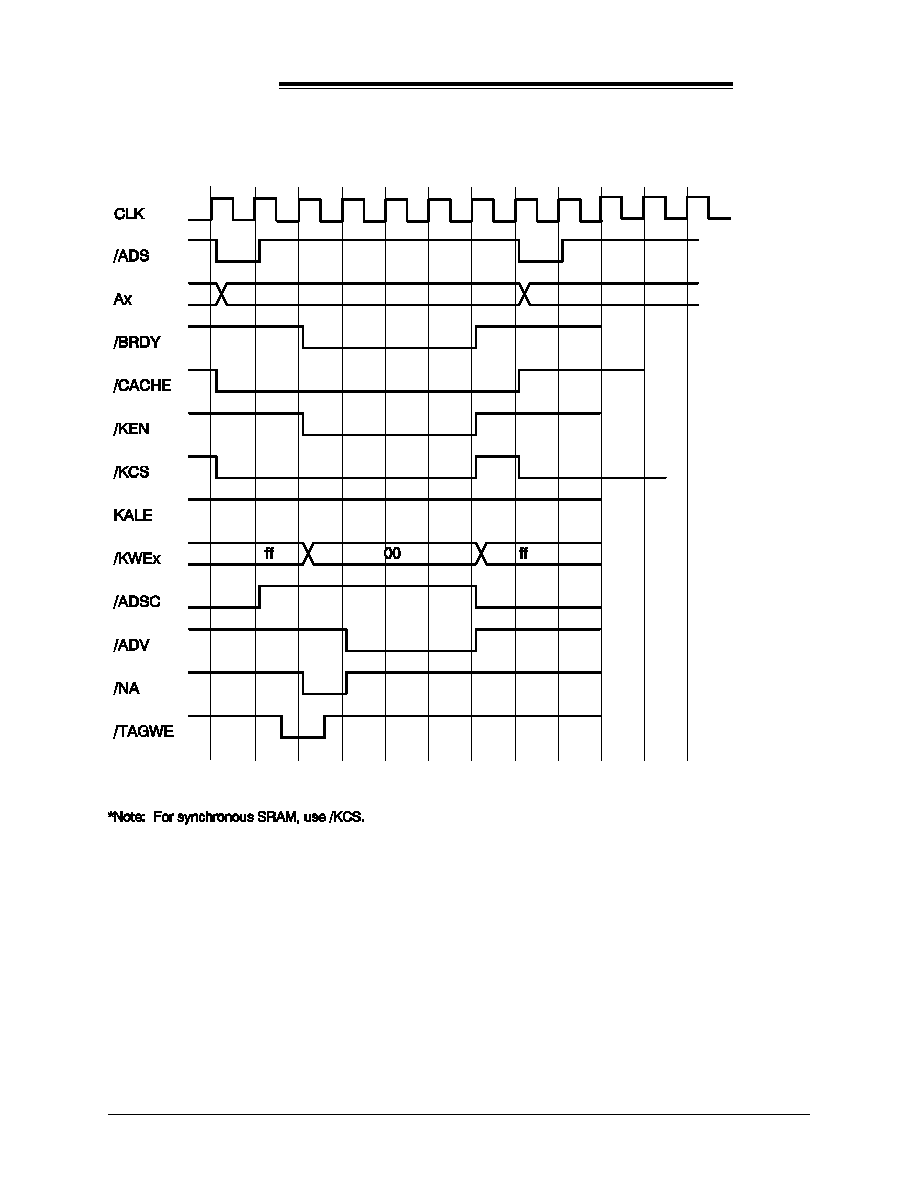

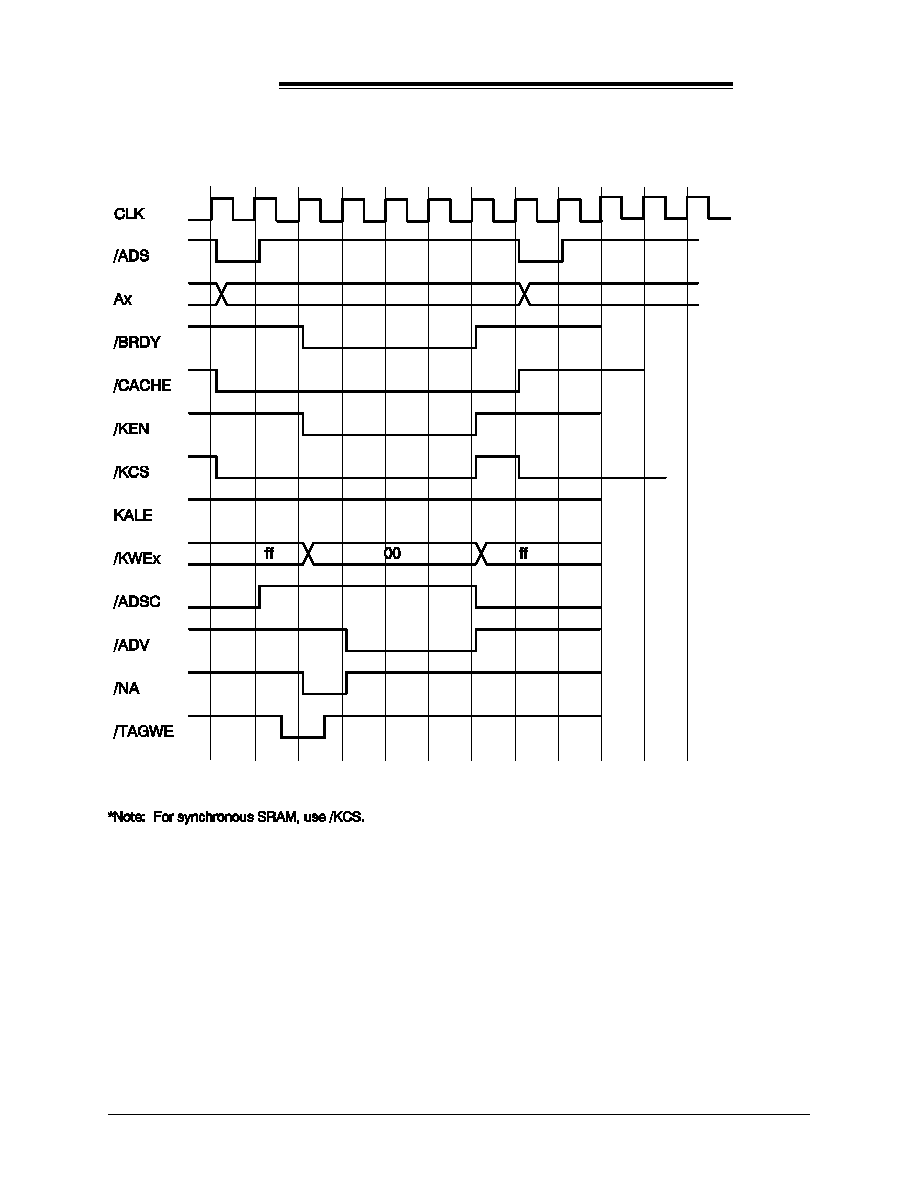

6.3.9 Asynchronous SRAM Burst Read Cycle (3-2-2-2)

117

6.3.10 Asynchronous SRAM Burst Write Cycle (4-2-2-2)

117

6.3.11 Pipeline Synchronous SRAM Burst Read Cycle

118

6.3.12 Pipeline Synchronous SRAM Burst Write Cycle (3-1-1-1)

119

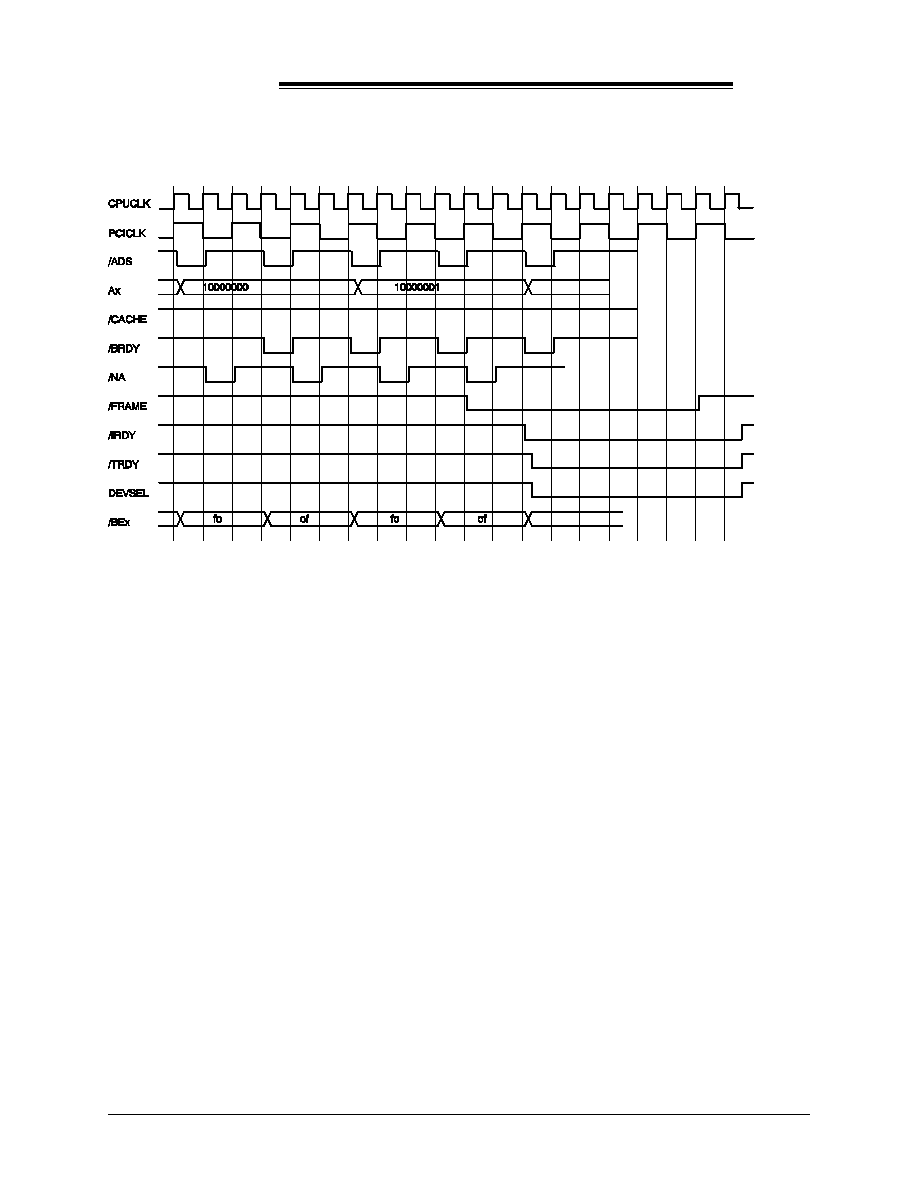

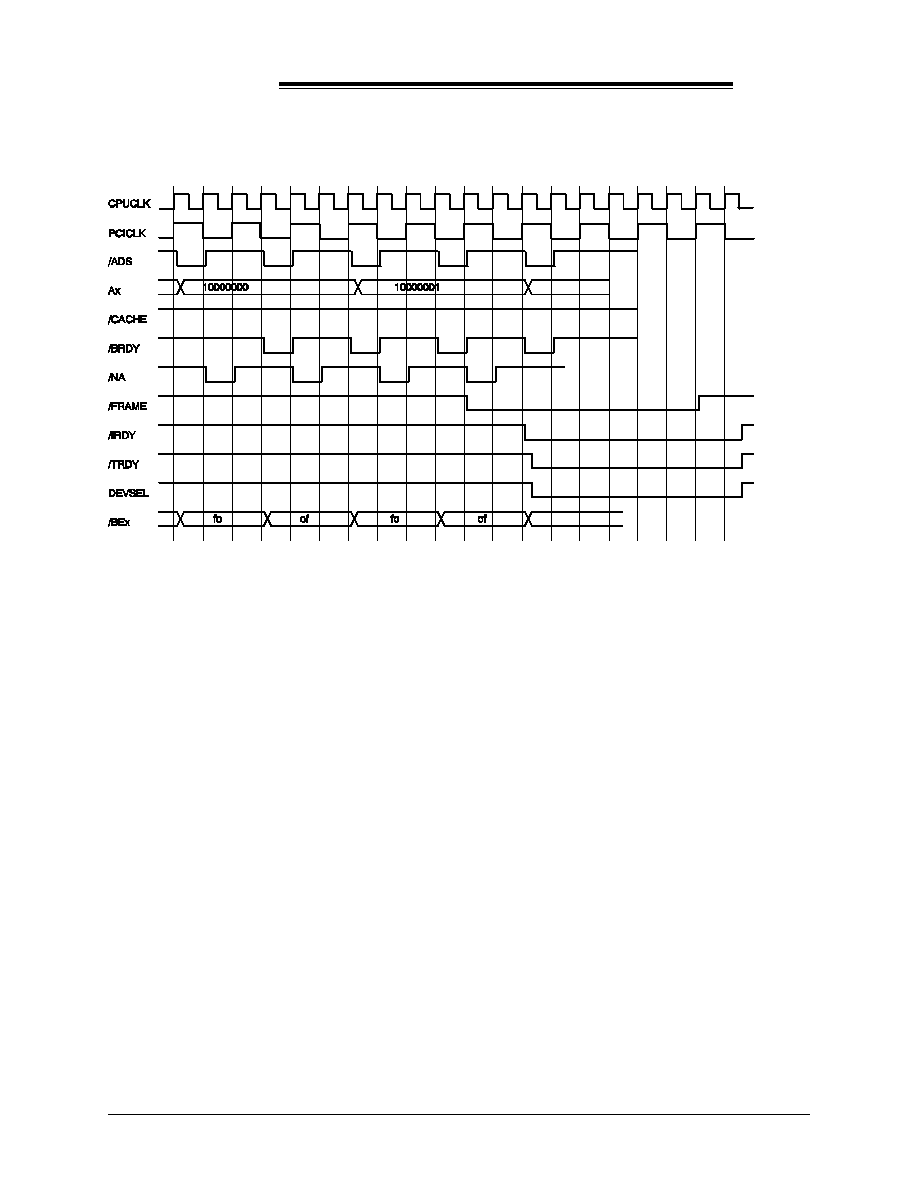

6.3.13 CPU-to-PCI Single Read

120

6.3.14 CPU-to-PCI Single Write, Write Buffer

121

6.3.15 CPU-to-PCI Multiple Write, Write-to-Buffer, PCI Burst Write122

7.0

ACC Micro 2051nt Pin Diagram

123

7.1.1 ACC Micro 2051nt

7.1.2 ACC Micro 2051nt Pin

7.1.3 ACC Micro 2051nt Mechanical Data Top View and Side View

125

7.1.4 ACC Micro 2051nt Mechanical Data - Top View

126

7.1.5 Package Dimensions

127

Appendix A-1 List of Sales Representatives

ACC Micro

2051nt

TM

1

ACC Micro 2051nt

PCI Single Chip Solution for Notebook Applications

Section 1 Introduction

1.1 Description

The ACC Micro 2051nt, PCI Single Chip Solution , is a true 64-bit high performance notebook solution to

support Intel Pentium, Cyrix M1, and AMD K5 microprocessors. The rich feature set of the ACC Micro

2051nt includes: level 2 write-back cache controller, DRAM controller, PCI interface, ISA interface, and ACC

Micro Power Management control. The integrated level 2 cache controller supports different types of SRAM

such as burst, pipeline burst, or standard asynchronous SRAM. Extended Data Output (EDO, and Fast Page

Mode DRAM are supported by the integrated DRAM controller. The built-in PCI bus interface can run in

synchronous or asynchronous mode with mobile/PCI support for docking designs.

ACC Micro Power Management allows the system power consumption to be controlled in various operation

modes such as Power-on suspend, Power-down suspend, Standby, and Doze. The whole system is partitioned

into four different power planes: CPU interface and level 2 cache interface, DRAM interface, PCI bus interface,

and ISA bus interface. Every power plane, except ISA (which is always at 5.0V) can be independently

configured to either 3.3V or 5.0V. No external level shifter is required.

1.2 Features

Supports Intel P54C, Cyrix M1, and AMD K5

Linear burst support

64-bit Pentium class CPU with 66 MHz bus frequency

ACC Micro Power Management Control

SMM/SMI support

Individual sets of system events and break events such as for Global Standby, Local Standby,

Suspend, and Doze control.

Dedicated external SMI trigger inputs such as for battery monitoring, suspend/resume button, and

AC power.

Software SMI

Warning Timer for SMI

Patented 'Adaptive Thermal Control' with auto-control or SMI generation

Shadow Registers for suspend to disk

Suspend to DRAM

CPU/PCI/ISA individually suspend/powered-down

Stop clock protocol, STPCLK#

0 Hz suspend

PCI suspend for Warm Docking

Mobile PC, or PC/PCI

CLKRUN# protocol to reduce PCI power consumption

Serialized interrupt protocol, SIN#/SOUT# for interrupt routing in docking design

Serialized DMA protocol for DRQ routing in docking design

ACC Micro

2051nt

TM

2

2051nt Features (continued)

Synchronous/asynchronous PCI bus

Synchronous PCI clock at CPUCLK/2

Asynchronous PCI clock

Four PCI bus masters

Converts back to back sequential CPU to PCI memory writes to PCI burst writes

Bytes merge for CPU to PCI memory write

Eight Dwords deep of CPU to PCI posted write buffers

Four Dwords pre-fetch buffers for CPU read from PCI memory

PCI to DRAM posting 8 Qwords deep

PCI from DRAM pre-fetched buffers 4 Qwords deep

Pre-snoop capability for PCI to DRAM with bandwidth of 119 MB/s

3V or 5V PCI bus

Built-in DRAM controller

Five banks of DRAM, up to 512MB main memory

Self-Refresh DRAM support

EDO or Fast Page Mode DRAM

Five RAS and 12 MA lines

Symmetrical/Asymmetrical DRAMs

64-bit data path to memory

64-bit DRAM option for individual bank

Four Qword posted write buffers for x-1-1-1 DRAM write cycles

Support 3V or 5V DRAM

Built-in level 2 cache controller

Direct mapped write back/write through

Up to 2MB

Burst, pipelined burst, or standard SRAM

Cache hit read/write x-1-1-1-1-1 ... with pipelined burst SRAM

Built-in full-blown ISA bus interface

Integrated 8254x1, 8259x2, 8237x2

Programmable ISA bus speed

Independent edge/level triggered interrupt controller

Optional Type-F DMA

X-bus support for chip select decode

Flash EPROM support

Dedicated ISA cycles option to free up the PCI bus

Integrated Fast IDE interface

Enhanced PCI IDE

Support master/DMA mode IDE

Built-in 8 Dwords posted write buffer

Built-in 8 Dwords pre-fetched buffer

Four independently programmable register sets for IDE timing control

Built-in 64-bit data path

ACC Micro

2051nt

TM

3

1.3

Block Diagram

TAG

CACHE

DRAM

CPU

2051nt

Ax

Dx

CPU Status

Keyboard Data, PS/2 Mouse

Enhanced IDE

EPROM

RTC

Super I/O

Audio

32-bit PCI Bus

MA, CAS

RAS

Power Management Control

ISA Bus

ACC Micro

2051nt

TM

4

Section 2 Functional Description

2.1 L2 Cache

A direct map level 2 cache controller is incorporated to support up to 2MBytes of SRAM by using either

burst, pipelined burst, or standard SRAM. A dynamic write-back/write-through algorithm is implemented

to optimize the bandwidth between cache and main memory. Alternatively, a cache hit 3-1-1-1-1-1-1-1

burst transfer can be achieved by using pipelined burst SRAM. Using standard SRAM, 3-2-2-2 cycles can

be achieved.

2.2 DRAM Interface

The DRAM controller is optimized to support standard fast page mode and Extended Data Out (EDO). Up

to 512MBytes of memory space is supported with 5 RAS and 12 MA lines. Both, symmetrical and

asymmetrical addressing DRAMs are supported. The memory data path can be either 32-bit, 64-bit, or

mixed.

Four Qwords buffers are implemented to support 3-1-1-1 posted write cycles. With the 60ns EDO DRAM,

x-2-2-2 burst read sequence can be achieved at 66 Mhz. A pseudo EDO mode is also available for standard

DRAM to achieve the x-3-3-3 burst read sequences.

2.3 PCI Bus

This 32-bit PCI interface with is PCI Rev. 2.0 compliant and can support up to four PCI master devices in

addition to the CPU host and the ISA DMA/master requests with either fixed or rotated priority scheme.

For CPU initiated write cycles, the PCI controller supports byte/word/Dword merge and will convert

sequential write into PCI burst sequence. Pre-fetch functions are also supported for CPU initiated read

cycles.

The PCI to DRAM burst access can reach X-1-1-1-1-1-1-1 for 32-bit during both read and write cycles.

2.4 Posted Write/Pre-fetch Buffers

A 4-Qword write buffer is implemented for CPU to main memory writes. Another 4-Qword buffer is also

implemented for CPU-to-PCI writes. The PCI pre-fetch buffer and PCI-to-main memory write buffer can

operate concurrently. The PCI pre-fetch buffer with the DRAM posted write buffer, forms an 8-Qword

buffer to provide for PCI-to-main memory transfer.

2.5 Clock

Both CPU clock (CPUCLKO) and PCI clock (PCICLKO) are derived from one clock source, CLKSRC. In

the fully-on mode, CPUCLKO is defined as CLKSRC/1, and the PCICLKO is defined as CLKSRC/2.

During operation, both CPUCLKO and PCICLKO may be scaled, modulated, or stopped independently.

ACC Micro

2051nt

TM

5

2.6 Power Management Modes

ACC Micro Power Management core provides four major power management modes, Fully-On, Standby,

Suspend, and Doze. Every mode has its own associated timers and up to 31 different system events can be

used as the monitor trigger sources. The transition between Fully-On, Standby, and Suspend are fully

programmable through SMI routines and the Doze mode can be enabled during Fully-On as well as

Standby mode. Doze mode, once enabled, will dynamically conserve CPU power without system

intervention. Dedicated input/output pins are also available to further facilitate the system design,

including external SMI inputs, suspend input, power on/off sequencing, etc. This increased flexibility

allows system designers to fully customize and diversify their products.

2.6.1 Fully-On

The default condition after power up is Fully-On. The CPU is running at full speed and all the peripherals

are powered-up. The Doze function can be enabled from this mode to conserve power when a selected idle

condition is detected.

2.6.2 Standby

Standby mode indicates that the system may not need full power, thus can be operated at a lower speed.

Additionally, peripheral devices can be selected to be powered down for further power savings. The

system can enter this mode when no pre-defined system events occur for a pre-programmed period of time.

Any pre-defined break event can bring the system back to the Fully-On mode. Register section 4.6.6

herein shows specific details regarding the programming of the Standby function.

2.6.3 Suspend

Three suspend modes are supported: Freeze, Power-On-Suspend, and the Power-Down-Suspend (Suspend-

To-Disk, or 0V-Suspend). In the Freeze mode, all devices are still powered on but will enter individual

standby modes and the clocks will be stopped. The complexity of the system design is dramatically

reduced since no power plane partitioning or leakage control is required. No data restoration or power-on

sequencing is needed since all devices still retain their own contents and provide the fastest resume process.

Power-On-Suspend also provides a fast resume process yet consumes minimum power by keeping only the

necessary devices powered. Power-hungry devices, such as CPU, SRAM, or some of the peripheral

devices can be turned off. Power-Down-Suspend mode will save all the system contents into disk and

power down all the devices except the RTC. This mode provides the maximum power savings since very

little power is consumed but a longer restart time is required. System designers can implement this mode

as the deepest suspend mode, or enable it only when the battery is exhausted. Register section 4.6.7 herein

shows specific details regarding the programming of the Suspend function.

2.6.4 Doze

When a CPU idle condition has been detected, the CPU will be put into a low-power consumption state.

STPCLK# is asserted and the CPU stays in the STOP-GRANT-STATE. For information of programming

the Doze Mode control, refer to register section 4.6.3.

ACC Micro

2051nt

TM

6

2.7 Idle Timers

2.7.1 Global-StandBy Timer

After a pre-programmed period of time, if no pre-selected system events occur, an SMI is generated. The

system designers can decide either to go to conserve mode or go directly into one of the suspend modes.

If the Standby mode is used, an Auto-Suspend-Timer can also be set and enabled to force the system into

suspend mode after a pre-programmed period of idle time. Any pre-selected break event will generate

another SMI to wake up the system.

2.7.2 Auto-Suspend Timer

The Auto-Suspend Timer when programmed and enabled, will generate an SMI if idleness occurs for a

programmable period of time.

2.7.3 Local-StandBy Timers

Four timers are available to monitor the peripheral activities, including LCD VRAM, LCD keyboard,

general chip select 1, and general chip select 2. The LCD VRAM/keyboard timers monitor the video buffer

access and user activities. A proprietary Video-Idle-Filter is incorporated to filter out the real video

idleness. General chip select 1 and general chip select 2 timers (GCS [0:1]) can be programmed to monitor

access to a specific I/O range.

If no activity is observed during the pre-programmed period of time, SMIs will be generated. Any pre-

selected break event occur will generate another SMI if the associated local suspend bit is set.

2.7.4 Doze Timers

Three timers are used to monitor timer tick, system events, and user activities to decide if the CPU is in an

idle state.

2.7.5 Warning Timers

All the SMI function except global standby mode, local standby mode, and auto suspend mode, can be

qualified with the warning timer to avoid interrupts during other previously requested functions.

2.8 SMM/SMIs

In addition to timer-generated SMIs, both Soft-SMI and External-SMIs are also implemented. Soft-SMIs

are activated through software commands. External-SMIs can be generated by a dedicated button/switch or

a combination of keystrokes. Those pins include general-purpose SMI inputs, EXTSMI#[0:2], and special-

purpose SMI inputs, SRBTN# (Suspend/Resume Button), BATLOW0# (Low Battery), and ACPWR (AC

Power).

ACC Micro

2051nt

TM

7

2.9 Thermal Control

Closed-loop or open-loop thermal control techniques can be used to alleviate temperature problems. An

external thermally coupled circuit can be used to automatically enable the built-in clock throttling function.

The clock throttling function can also be enabled as an open-loop solution.

ACC Micro's patented Adaptive Thermal Control is embedded in the ACC Micro 2051nt and can be used

to eliminate external thermal coupling and provide a pseudo-closed-loop solution. By properly adjusting

the high temperature threshold and low threshold, an over-heat warning zone can be defined and the clock

throttling function will be automatically enabled when the emulated temperature value falls within this

range and is disabled on exit. An SMI can also be generated as an option when entering and exiting the

temperature critical zone.

2.10 Battery Management

One battery status pin, BATLOW0# is provided for the battery exhaustion processing.

When BATLOW0# is asserted, SMI# will be asserted after an optionally pre-programmed POWER-LEFT-

OVER time. A warning tone can be enabled through the register bit during the SMI routine, or can be set

to warn the user of the exhausting battery power before the SMI is issued.

2.11 AC Power

The ACPWR pin can be treated as a special SMI input. SMI# will be asserted when the AC-POWER pin

changes state. The power management routine in the BIOS can read the internal registers to know if the

ACPWR is in an on or off condition.

2.12 Mobile PC/PCI

PC/PCI protocol is supported to facilitate the mobile docking station design. All the PCI master/grant pairs,

INTx#, non-occupied ISA IRQs and DRQs can be programmed to support MHPG architecture.

2.13 CLKRUN#

PCI clock is controlled through PCI CLKRUN protocol. The CLKRUN# pin may be de-asserted and the

PCI clock will be stopped if no PCI activities are observed. The PCI clock may be stretched or slowed

down for extended cycles.

2.14 Device I/O Shadowing

The PCI-Docking extention (PD) supports the full-blown docking capabilities by providing a PCI-to-PCI

and PCI-to-ISA bridge. Alternate devices or I/O ports located on the docking station such as alternate

keyboard, RTC, FDC, or RAMDAC can be programmed to be either the primary or secondary functions.

The access to the primary functions can be programmed to overshadow the secondary functions.

ACC Micro

2051nt

TM

8

Section 3.0 Pin Specifications

3.1 2051nt Pin Description

Table 3-1 Clock Interface

Pin Name

Type

Description

CPUCLKI

I

CPU clock input.

KCLK

I

Cache (advance) clock for the cache tag write. KCLK's 3ns - 8ns faster

than CPU and Host clocks. Used for Asynchronous SRAM only.

PCICLKO

O

Clock to the CPI device and core logic state machine. This clock should

be fed to a separate buffer to provide the clock for core logic and PCI

devices.

CPUCLKO

O

It provides the clock to the core logics and CPU. This clock should be fed

to a separate buffer to provide the clock for core logics and CPU.

PCICLKI

I

PCI clock input for 2051nt.

CLKSRC

I

System clock source. It is an input clock from the CMOS oscillator or

clock chip. CLKSRC provides the clock source for CPUCLKO and

PCICLKO.

14M

I

14.318 MHz input clock from external clock source. It is used for AT bus

clock reference.

SYSCLK

PWR3

O

I

When Standard AT Configuration Register 7h, bit 1 is set to one, it

provides the clock to AT bus.

This is a multifunction pin. As default this pin becomes PWR3 (power

control bit 3) for power management function.

Table 3-2 CPU Interface

Pin Name

Type

Description

/ADS

I

/ADS is driven directly by the CPU ADS# pin. It is asserted in T1 of the

CPU bus cycle.

M/-IO

I

When high, it indicates current bus cycle is a memory access cycle. It is

an I/O cycle when it is low.

D/-C

I

It indicates whether the current bus cycle is a data or control cycle.

W/-R

I

It indicates whether the current bus cycle is a read or write cycle.

ACC Micro

2051nt

TM

9

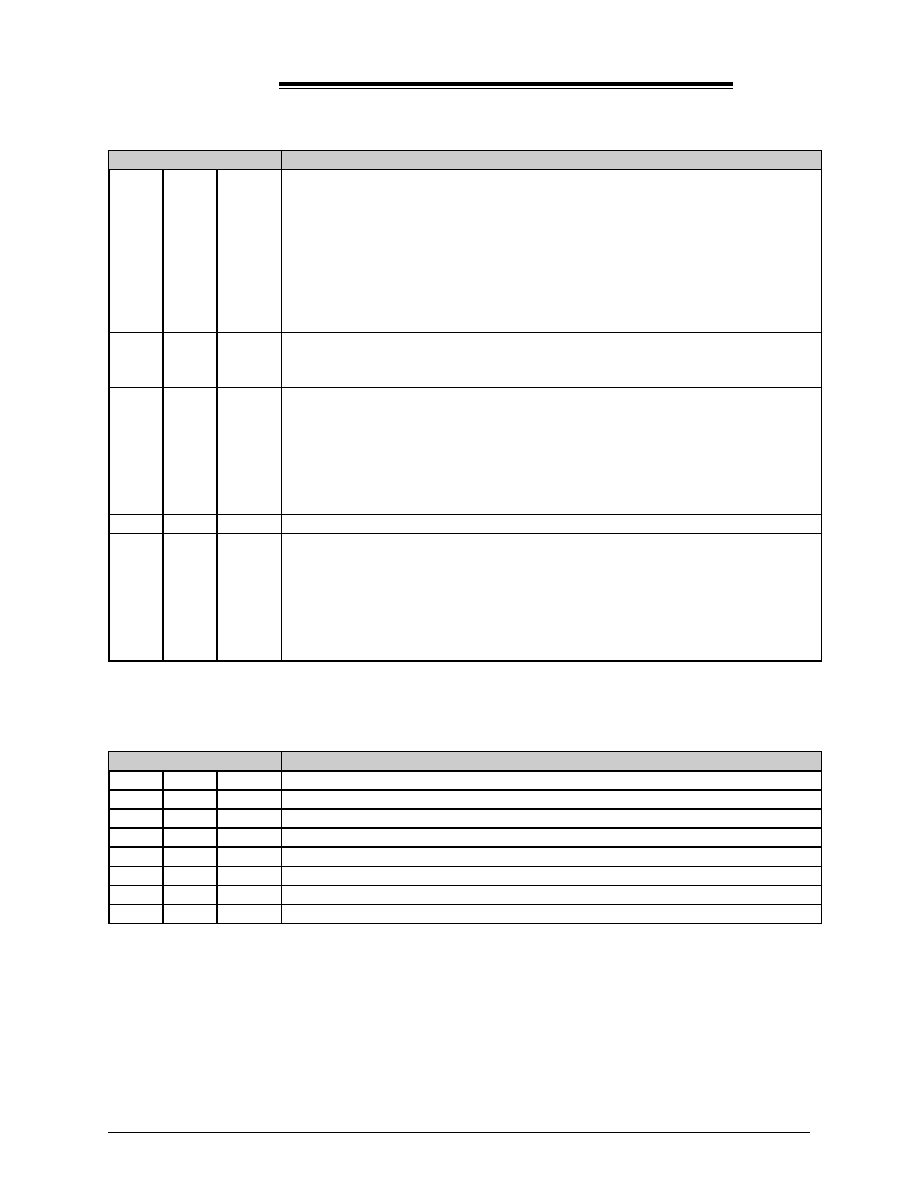

Table 3-2 CPU Interface contd...

/BRDY

O

It indicates to the CPU the data for read/write cycle is ready.

/HIT-M

I

Asserted by the CPU to indicate that a snoop cycle has hit a modified line

and needs to be written back.

/EADS

O

It indicates a valid external address has been driven onto the processor

address pins to be used for an inquiry cycle.

/BOFF

O

It is used to back off the current CPU cycle.

/NA

O

It indicates the system controller is ready to accept a new bus cycle

although all data transfers for the current cycle have not yet completed.

/CACHE

I

/CACHE is asserted by the CPU to indicate internal cacheability of the

cycle (for read), and to indicate a burst writeback cycle (for write).

/KEN

O

In response to the CACHE#, asserted by the CPU, /KEN is asserted to

transform the cycle into a burst line fill cycle.

/LOCK

I

It indicates the current CPU cycle is locked.

/SMIACT

I

It indicates by the CPU that it is in system management mode after /SMI

being served by the CPU.

A[3:31]

I/O

These are input during CPU cycles. They become output during snoop

cycle.

D[0:63]

I/O

CPU Data bus.

/BE[0:7]

I/O

These are used to indicate which byte lanes the CPU cycle is accessing.

NMI

O

Non-Maskable Interrupt. It connects to the NMI of the CPU.

INTR

O

It indicates a valid interrupt request is asserted.

/A20M

O

Gate A20.

/FERR

I/O

Numeric Coprocessor Error. It indicates a coprocessor error.

/IGNNE

O

Ignore Error.

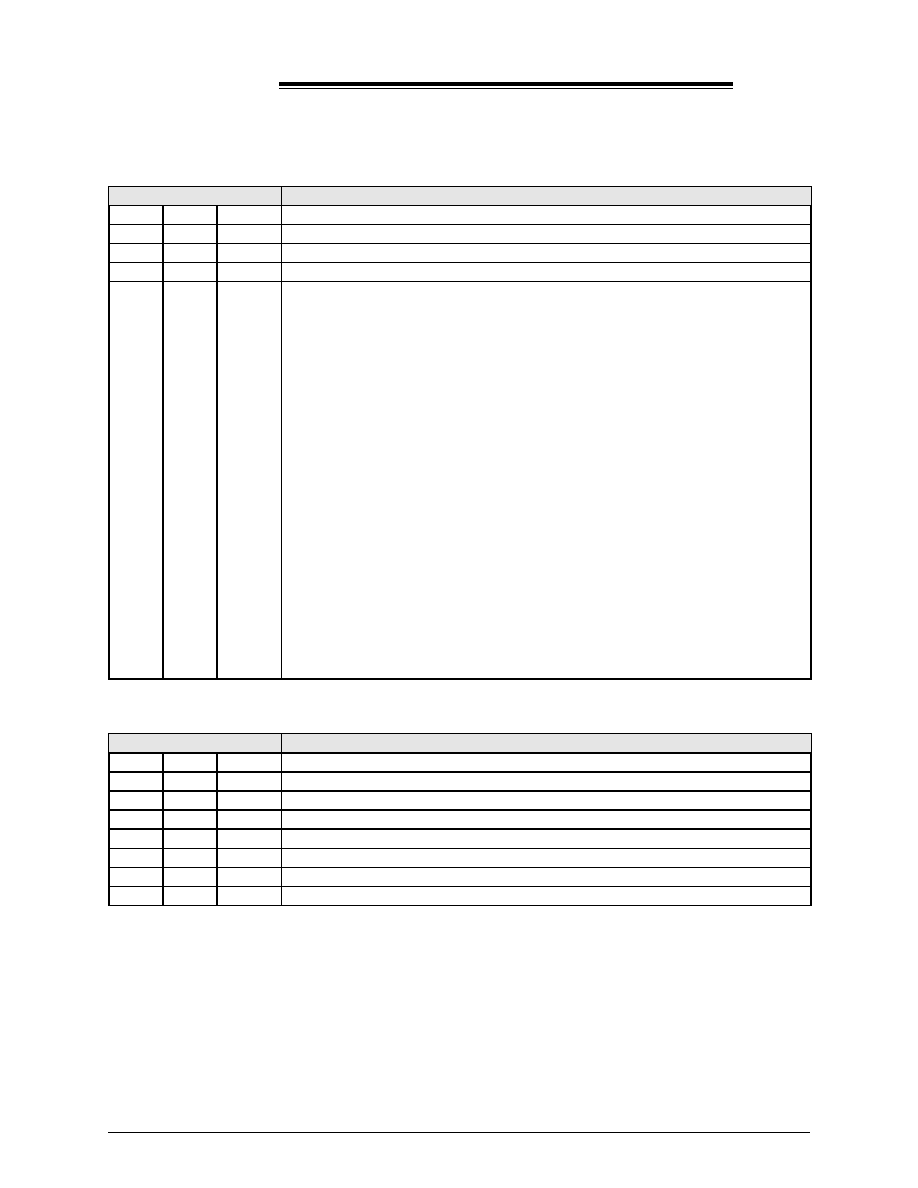

Table 3-3 Multifunction PMC / Cache Interface (The level 2 cache is disabled as power-on default)

Pin Name

Type

Description

TPWROUT0-6

TAG0-6

O

I/O

When Register 82h bit 5 is set to 1, the output value for these signals can be

programmed through Register 8Ah (device 0 function 0)

When level 2 cache is enabled, these signals become TAG0-6. The tag

addresses are used to determine if the cycles (read/write) are 22 hit or miss.

PWROUT4

TAG7

O

I/O

When Reg. 8Ah bit 4 is set to 1, this signal becomes PWROUT4 control

pin.

When level 2 write back cache is enabled, this pin becomes the dirty bit.

ACC Micro

2051nt

TM

10

Table 3-3 Multifunction PMC / Cache Interface (The level 2 cache is disabled as power-on default)

contd...

Pin Name

Type

Description

TPWROUT7

DTY

O

I

When Register 82h bit 5 is set to 1, the output value for this signal can be

programmed through Register 8Ah (device 0 function 0)

When level 2 cache is enabled, DTY will write the dirty line back to DRAM.

KCSTS4

/TAGWE

I

O

The value of this status input pin can be read from Register 88h bit 4.

When level 2 cache is enabled, this pin becomes TAG SRAM write enable.

KCSTS0

/KOE

I

O

The value of this status input pin can be read from Register 88h bit 0.

When level 2 cache is enabled, this pin becomes DATA SRAM output enable.

KWSTS0-7

/KWE0-7

I

O

The value of this status input pins can be read from Register 89h bit 0-7.

When level 2 cache is enabled, this pin becomes DATA SRAM write enable.

KCSTS2

/ADV

/TKA4

I

O

O

The value of this status input pin can be read from Register 88h bit 2.

When Burst SRAM (either pipe or non pipe) is used, this pin becomes

Burst SRAM/ADV.

When level 2 cache is enabled, and when Asynchronous SRAM is used,

this pin becomes burst A4.

KCSTS3

/ADSC

/TKA3

I

O

O

The value of this status input pin can be read from Register 88h bit 3.

When Burst SRAM (either pipe or non-pipe) is used, this pin becomes

Burst SRAM/ADSC.

When Asynchronous SRAM is used, it becomes burst A3.

KCSTS1

/KCS

I

O

The value of this status input pin can be read from Register 88h bit 1.

When the L2 cache is enabled, and this pin becomes DATA SRAM chip select.

PWROUT0

/KALE

I

O

When Reg. 82h, bit 0 of the PCI configuration register device 0, function 0 is

set to one, /KALE becomes power output pin PWROUT0. The value to output

to this pin can be programmed from Register 84h bit 0.

When the L2 cache is enabled, this pin becomes cache address latch enable.

ACC Micro

2051nt

TM

11

Table 3-4 DRAM Interface

Pin Name

Type

Description

/RAS4-3

PWROUT1-2

O

DRAM row address selection.

When Reg. 82h, of the PCI configuration register device 0, function 0 bits 1-2

are set to one, /RAS4-3 becomes power output pin PWROUT1-2. The value to

output to this pin can be programmed from Register 84h bit 1-2.

/RAS2-1

O

DRAM row address selection

/CAS7-0

O

DRAM column address selection.

/WEN

O

DRAM write enable.

MA11-0

O

DRAM row and column address.

MD[0:63]

I/O

Memory data bus.

Table 3-5 PCI Interface

A pull-up resistor to PCI's Vcc is required for PCI interface signals

Pin Name

Type

Description

/FRAME

I/O

It is driven by the current master to indicate the beginning and duration of a

transaction. During master cycle, it is an input. It is an output during the

CPU cycle.

/TRDY

I/O

It indicates the target device is ready to complete the data transfer. The data

transfer is completed when the target is asserting /TRDY and the master is

asserting /IRDY at the rising edge of the clock.

/IRDY

I/O

It indicates the initiator is ready for a data transfer.

/STOP

I/O

It indicates the current target is requesting the initiator to stop the current

transaction.

/DEVSEL

I/O

As an input, it indicates whether any device on the bus has been selected. It

indicates the target device has decoded its address as an output.

/PCILOCK

I/O

It is used to prevent multiple access to the same target device at the

same time.

AD[31:0]

I/O

PCI AD bus bit 31-0.

PAR

I/O

Parity bit for PCI bus. Parity is asserted one clock after the data phase to

ensure even parity across the AD[31:0] and C/BE[7:0].

C/-BE[3:0]

I/O

The state of C/-BE[3:0] indicates which locations in the currently-addressed

doubleword are being addressed or the number of additional bytes

to transfer.

/REQ[3:0]

I

It indicates PCI master requests for PCI bus.

/GNT[3:0]

O

It indicates the PCI bus is granted to the PCI master per its request.

/CLKRUN

I/O

It is used for mobile PC/PCI serial interrupt protocol to restart the PCI

clock if an interrupt received while PCI clock is stopped.

/SERR

I/O

PCI system error. It indicates an address parity / data errors and could

cause a NMI to processor or flag an error condition.

/INTA-/INTD I/O

Interrupt request lines from the PCI devices.

ACC Micro

2051nt

TM

12

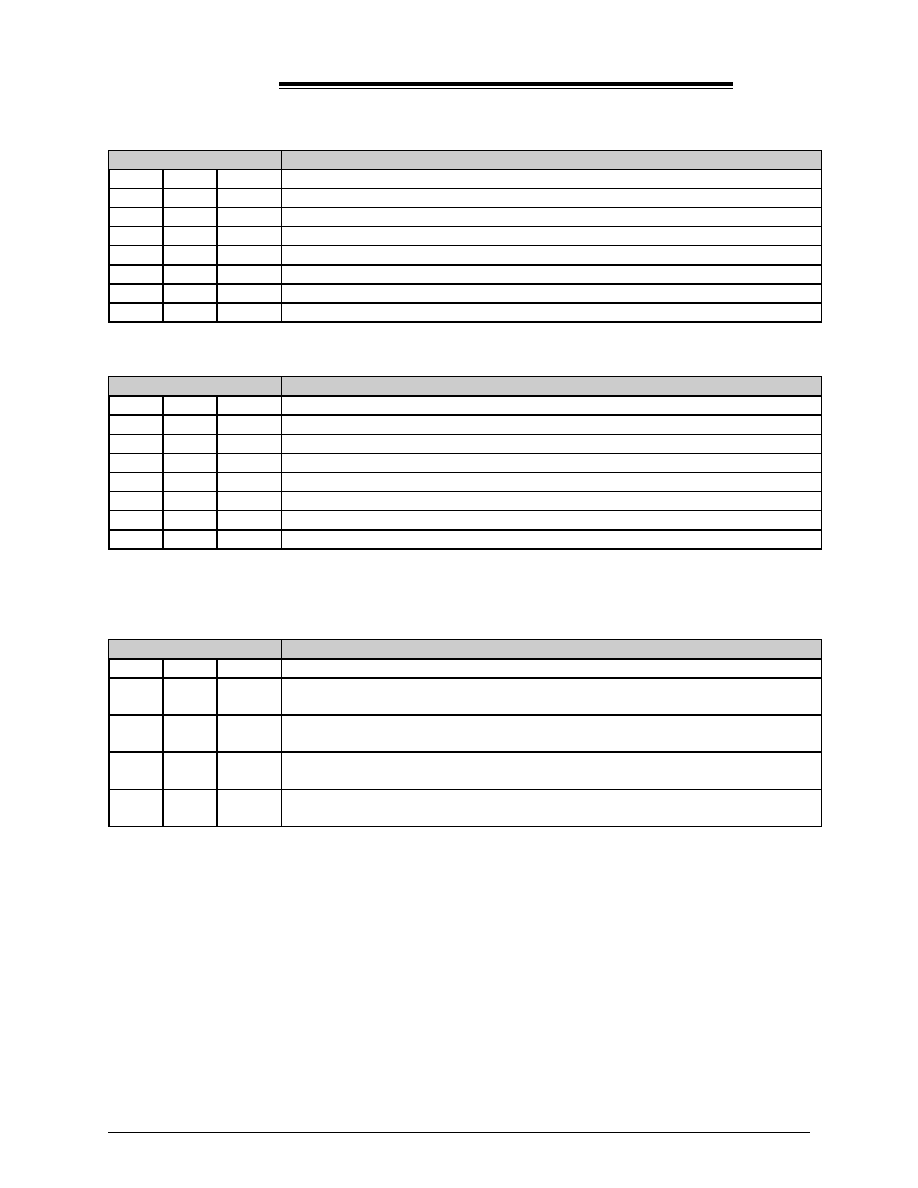

Table 3-6 Reset Interface

Pin Name

Type

Description

PWRGD

SI

Power good signal from system power-good circuitry. It must be stable for

at least 1ms. It is used to reset the chip.

RSTDRV

O

It is used to reset the ISA bus devices when the system is powered-up.

CPURST

O

It is used to reset the CPU when the system is powered-up.

INIT

O

INIT asserts to indicate a shutdown special cycle on the PCI bus.

/PCIRST

O

It is used to reset the PCI bus (for hot insertion). Connect /PCIRST to the PCI

device's reset pin.

Table 3-7 ISA Interface

Pin Name

Type

Description

SA[16:0]

I/O

System address bus.

LA[23-17]

I/O

Latcheable address bus.

/MASTER

I/O

An input from an active device on the I/O channel. After /MASTER is

forced low by an I/O device, the I/O CPU must wait for one system clock

period before driving its address and data lines. It should not be held low

for more than 15ms as this may result in memory loss due to the lack of a

refresh cycle.

BALE

I/O

Indicates a valid address on the SA bus. BALE is used to hold the address

during an AT bus cycle

/SBHE

I/O

System bus byte high enable. /SBHE indicates the upper byte transfer (8-

bit transfer with an odd address and even address for 16-bit transfer).

PWR4

/SMEMR

/PCS2

I

O

O

This is a multifunction pin, as default (Reg. 7h bit 3 is set to zero), this pin

becomes PWR4 (power control bit 4) for power management function.

When Register 7h bit 3 of the ISA configuration register is set to one and

bit 2 equals to 0, it is /SMEMR. It indicates a read cycle is addressed to

the lower 1MB memory space.

When Register 7h, bit [4,3,2] are set to [1,X,1] it becomes programmable

chip select 2 (/PCS2).

PWR2

/SMEMW

/PCS3

I

O

O

This is a multifunction pin, as default (Reg. 7h bit 0 is set to zero), this pin

becomes PWR2 (power control bit 2) for power managment function.

When Register 7h, bit 0 of the ISA configuration register is set to one, this

pin is /SMEMW. It indicates a write cycle is addressed to the lower 1MB

memory space.

When Register 7h, bit [4,0] are set to [1,1] it becomes programmable chip

select 3 (/PCS3).

/MEMR

I/O

It commands the memory to place valid data on the data bus.

/MEMW

I/O

It commands the memory to accept data from the data bus.

/IOR

I/O

It commands the I/O device to place valid data on the data bus.

/IOW

I/O

Commands the I/O device to accept data from the data bus.

/MCS16

I/O

Enables a 16-bit memory access on the I/O channel.

/IOCS16

I/O

Enables a 16-bit I/O access on the I/O channel.

ACC Micro

2051nt

TM

13

Table 3-7 ISA Interface contd...

Pin Name

Type

Description

/ZWS

I/O

When an ISA device requires zero wait state, /ZWS will assert. It causes

the AT bus cycle to terminate. The zero wait state has no effect during 16-

bit I/O cycle.

IOCHK

I/O

Indicates an error condition from an I/O device and causes the system to

generate an NMI to CPU.

IOCHRDY

I/O

It causes the wait state(s) to be asserted in I/O or memory accesses.

X32K

/REF

I

I/O

In suspend mode, this pin can program to become 32KHz clock input for

power management module and DRAM refresh state machine.

As an input, it causes a refresh cycle from an I/O master device. As an

output, it initiates a refresh cycle for the DRAMs.

SD[15:0]

I/O

16-bit System data bus.

DRQ7-0

I/O

DMA request input lines are used by peripherals to obtain DMA service.

TC

O

Transfer completed. DMA controller is actived when the byte or word

transfer count for a DMA channel has been exhausted.

/DACK7-0

PWR9-5

O

Indicates that DMA service has been granted to the DMA request line by

the peripherals.

These signals are multiplexed with power control bits for power

management control signals. When Register 7h, bit 5 of the ISA

configuration register is set to one:

/DACK7 becomes PWR9

/DACK6 becomes PWR8

/DACK3 becomes PWR7

/DACK1 becomes PWR6

/DACK0 becomes PWR5

AEN

O

Address enable for DMA transfer. It is inactive when an external bus

master controls the system bus.

Table 3-8

ISA/IRQ Interface

Pin Name

Type

Description

IRQ1

KEYLOCK

I/O

When internal keyboard is disabled, Reg. 68h, bit 7 equals zero, this pin is

used as IRQ1 input for external keyboard controller (default).

When Reg. 68h, bit 7 of the PCI configuration register device 1 function 0

is set to one, internal keyboard is enabled, this pin is the keyboard lock

signal.

IRQ3-15

I/O

Interrupt request.

IRQ12

MSDATA

I/O

When internal keyboard is disabled, Reg. 68h, bit 7 equals zero, this pin is

an interrupt request line for a PS/2 mouse (default).

When the internal keyboard is enabled, this pin is the mouse data line.

(Reg. 68h, bit 7 of the PCI configuration register device 1 function 0 is set

to one).

ACC Micro

2051nt

TM

14

Table 3-9

ISA/XD Interface

Pin Name

Type

Description

/KBCS

MSCLK

I/O

Keyboard chip select (default). When internal keyboard is disabled, Reg.

68h, bit 7 of the PCI configuration register device 1 function 0 equals zero.

When internal keyboard is enabled, this pin is the mouse clock.

KBGA20

KBDATA

I/O

When the internal keyboard is disabled, Reg. 68h, bit 7 equals zero, this

pin is used as keyboard gate A20 (default).

When Reg. 68h, bit 7 of the PCI configuration register device 1 function 0

is set to one, the internal keyboard is enabled, this pin is the keyboard

data.

/KBRST

KBCLK

I/O

When internal keyboard is disabled, Reg. 68h, bit 7 equals zero, this pin is

used as keyboard reset (default).

When Reg. 68h, bit 7 of the PCI configuration register device 1 function 0

is set to one, the internal keyboard is enabled, this pin is the keyboard

clock.

Table 3-10

Real time Clock Interface

Pin Name

Type

Description

RTCAS

O

Real timer clock address strobe is used to multiplex the bus to an external

real time clock plus ram peripheral device.

/RTCWR

O

Real time clock read/write is used to indicate read or write mode for a

RTC plus ram device.

/RTCDS

O

Real time clock data strobe is used to control the bi-directional bus on an

ext. RTC.

Table 3-11

Address Buffers Decodes Interface

Pin Name

Type

Description

/XDIR

O

It controls the direction of data transfer between the peripheral bus and the

I/O channel. When low, it should drive the SD bus signals toward the

XD bus. When high, it should drive the XD bus toward the SD bus.

/ROMCS

O

It is used to generate XDIR during ROM read cycle.

Table 3-12

PC/PCI Interface

Pin Name

Type

Description

/SOUT

O

Serial out. Mobile PCI serial interrupt handshaking.

/SIN

I

Serial in. Mobile PCI serial interrupt handshaking.

ACC Micro

2051nt

TM

15

Table 3-13

PMC Interface

Pin Name

Type

Description

/STPCLK

O

Indicates a request to switch the CPU clock for power management

control.

/SMI

O

Causes the processor to enter system managment mode once recognized.

PWR0

/LTCH0

/PCS0

O

O

O

As default, this pin is power control bit 0.

When an external latch is used to support the power controls bit 0-7, this

signal will be used to control the 8-bit external latch.

When Register 6h, bits 5 and 4 are set to {1:0], it becomes PCS0,

programmable chip select 0.

PWR1

/LTCH1

/DOZE

/PCS1

O

O

O

O

As default, this pin is power control bit 1.

When an external latch is used to support the power control bits 8-15, this

signal will be used to control the 8-bit external latch.

When Register 6h, bit 3 is set to one and bit 2 is set to zero, it indicates

that the system is in DOZE mode.

When Register 6h, bits 3 and 2 are set to one, it becomes PCS1,

programmable chip select bit 1.

/BATLOW0

I

Battery low status pin are provided for the battery exhaustion processing.

/SMI will be asserted when /BATLOW0 changes state.

/EXTSMI0-2

I

Three external SMI pins are provided for external devices that required

special system handling. /SMI will be asserted when they change state.

/EXTSMI0-2 are edge triggered signals and can be programmed to be

either rising edge or falling-edge trigger.

/SRBTN

I

Suspend/Resume button can be implemented to put system into suspend

mode from normal mode and resume back from suspend mode. An SMI

is generated when the button is pressed. /SRBTN is a rising edge trigger.

ACPWR

I

AC Power can be implemented to report system power status. /SMI will

be asserted when ACPWR changes state.

/EXTSYS

I

The external system event can be used by external device as a trigger

source for break/system event. Core logic will generate SMI once

/EXTSYS is triggered. /EXTSYS is an rising edge trigger.

/SUSP

O

/SUSP will be driven out when the system enters the suspend mode.

GPIO0-2, 5-7

I/O

These are general purpose I/O signal. They can set as the output or input

by programming Reg. 85h-87h.

Table 3-14

Miscellaneous

Pin Name

Type

Description

SPKR

O

Gates the speaker data and timer 2 to drive the internal speaker.

ACC Micro

2051nt

TM

16

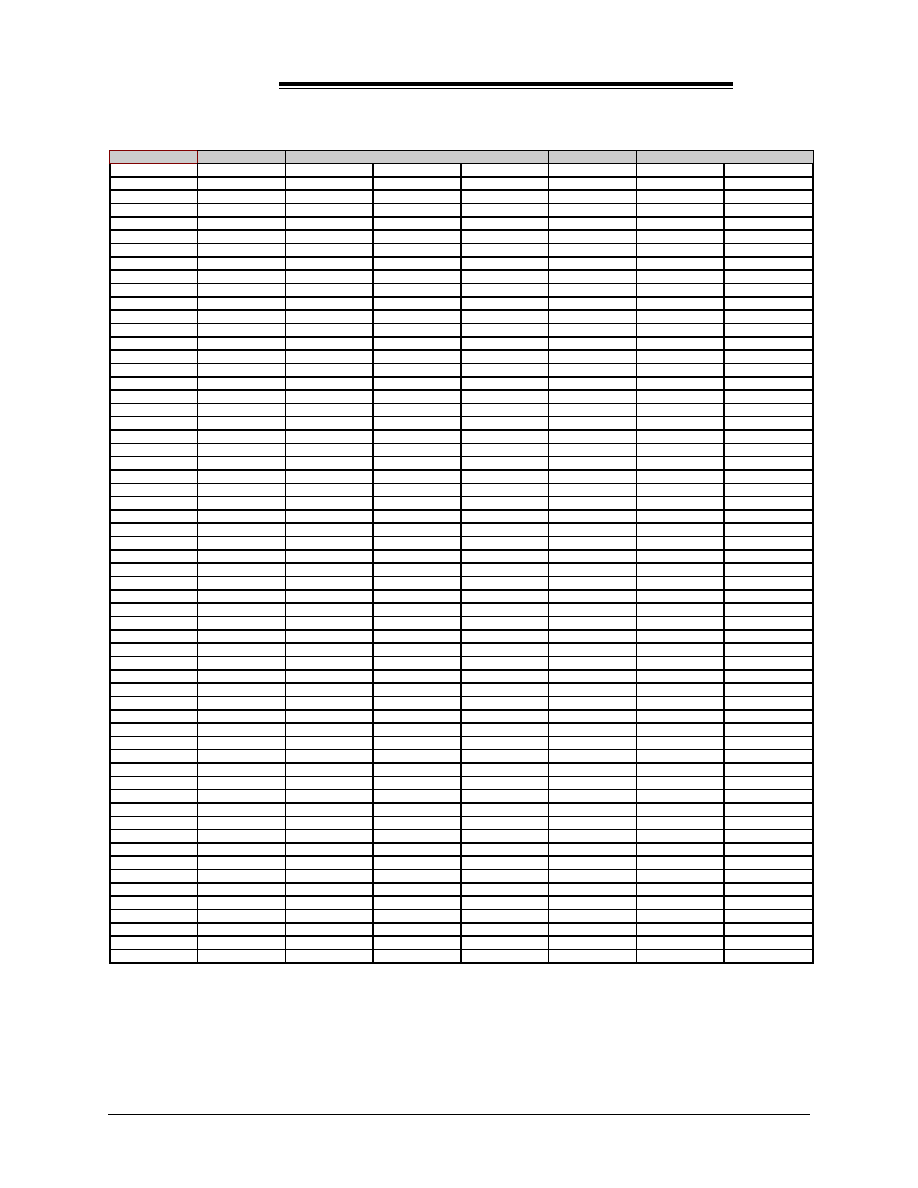

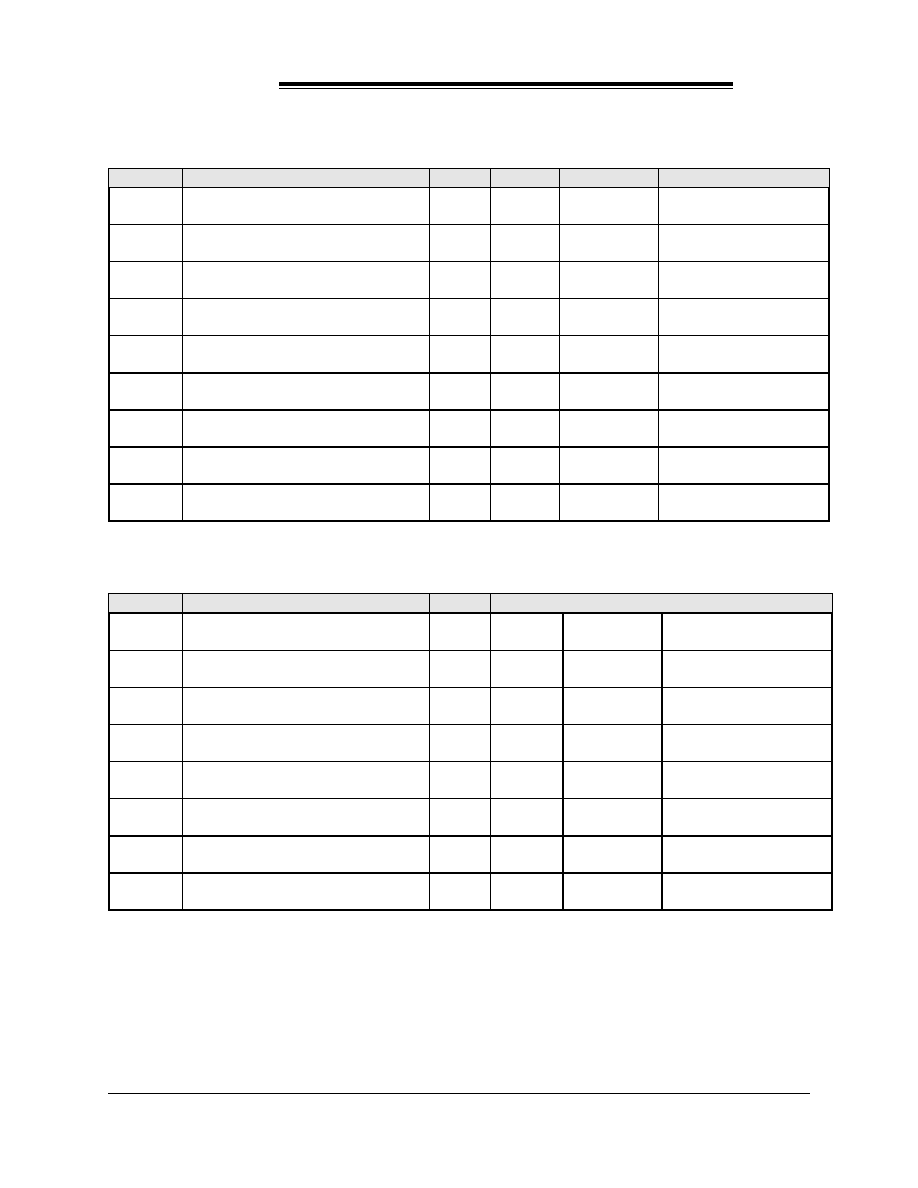

3.2 2051nt Numerical Pin List (with L2 cache)

Pin #

Pin Name

Pin #

Pin Name

Pin #

Pin Name

Pin #

Pin Name

A1

GND

C3

GND

E5

GND

J25

GND

A2

D16

C4

D11

E6

VCC

J26

/ZWS

A3

D15

C5

D8

E7

GND

J27

DRQ2

A4

D13

C6

D4

E8

VCC

J28

IRQ9

A5

D10

C7

D0

E9

GND

J29

RSTDRV

A6

D6

C8

/KWE5

E10

VCC

K1

D45

A7

D2

C9

/KWE1

E11

TAG0

K2

D44

A8

/KWE7

C10

TAG6

E12

KALE

K3

D43

A9

/KWE3

C11

TAG2

E13

/CACHE

K4

D42

A10

DTY

C12

/TKA4/ADSV#

E14

VDD

K5

VCC

A11

TAG4

C13

/FERR

E15

GND

K25

VCC

A12

/TAGWE

C14

/BRDY

E16

VCC

K26

CLKSRC

A13

/KCS

C15

/LOCK

E17

/BE3

K27

14M

A14

AHOLD

C16

/HIT-M

E18

CPURST

K28

/SMEMR

A15

/BOFF

C17

/BE1

E19

A16

K29

/SMEMW

A16

DC

C18

/BE6

E20

VCC

L1

D50

A17

/A20M

C19

A18

E21

GND

L2

D49

A18

/BE4

C20

A13

E22

VCC

L3

D48

A19

A20

C21

A5

E23

GND

L4

D47

A20

A15

C22

A6

E24

A22

L5

D46

A21

A9

C23

A29

E25

GND

L25

/DACK1

A22

A8

C24

A26

E26

/IRQ8

L26

DRQ3

A23

A3

C25

A23

E27

/BATLOW0

L27

/DACK3

A24

A28

C26

INIT

E28

/EXTSMI0

L28

/IOR

A25

A24

C27

/SUSP

E29

/EXTSMI1

L29

/IOW

A26

NMI

C28

/EXTSYS

F1

D29

M1

D55

A27

/STPCLK

C29

PWR0

F2

D28

M2

D54

A28

/IDEDACK

D1

D21

F3

D27

M3

D53

A29

GND

D2

D20

F4

D26

M4

D52

B1

GND

D3

D19

F5

VCC

M5

D51

B2

GND

D4

GND

F25

VCC

M25

IRQ4

B3

D14

D5

D7

F26

SPKR

M26

IRQ5

B4

D12

D6

D3

F27

RTCAS

M27

IRQ6

B5

D9

D7

KCLK

F28

/RTCWR

M28

IRQ7

B6

D5

D8

/KWE4

F29

/RTCDS

M29

DRQ1

B7

D1

D9

/KWE0

G1

D33

N1

D60

B8

/KWE6

D10

TAG5

G2

D32

N2

D59

B9

/KWE2

D11

TAG1

G3

D31

N3

D58

B10

TAG7

D12

CPUCLKI

G4

D30

N4

D57

B11

TAG3

D13

MIO

G5

GND

N5

D56

B12

/TKA3/ADSC#

D14

/NA

G25

GND

N25

/MCS16

B13

/KOE

D15

/ADS

G26

/KBRST

N26

BALE

B14

/KEN

D16

WR

G27

SMCLK

N27

TC

B15

/SMIACT

D17

/BE2

G28

SMDATA

N28

/DACK2

B16

/EADS

D18

/BE7

G29

/ROMCS

N29

IRQ3

B17

/BE0

D19

A17

H1

D37

P1

/CAS0

B18

/BE5

D20

A12

H2

D36

P2

D63

B19

A19

D21

A10

H3

D35

P3

D62

B20

A14

D22

A4

H4

D34

P4

D61

B21

A11

D23

A31

H5

VCC

P5

VCC

B22

A7

D24

A27

H25

VCC

P25

VDD

B23

A30

D25

INTR

H26

/XDIR

P26

IRQ12

B24

A25

D26

/IGNNE

H27

IRQ1

P27

IRQ11

B25

A21

D27

/EXTSMI2

H28

/KBCS

P28

IRQ10

B26

/SMI

D28

/SRBTN

H29

KBGA20

P29

/IOCS16

B27

PWRGD

D29

ACPWR

J1

D41

R1

/CAS4

B28

IDEDRQ

E1

D25

J2

D40

R2

/CAS3

B29

PWR1

E2

D24

J3

D39

R3

/CAS2

C1

D18

E3

D23

J4

D38

R4

/CAS1

C2

D17

E4

D22

J5

GND

R5

GND

ACC Micro

2051nt

TM

17

2051nt Numerical Pin List contd...

Pin #

Pin Name

Pin #

Pin Name

Pin #

Pin Name

Pin #

Pin Name

R25

GND

AA25

GND

AE26

SA14

AG28

SD1

R26

DRQ0

AA26

LA22

AE27

SA13

AG29

SD0

R27

/DACK0

AA27

LA21

AE28

SA12

AH1

MD27

R28

IRQ14

AA28

LA20

AE29

SA11

AH2

MD28

R29

IRQ15

AA29

LA19

AF1

MD24

AH3

MD31

T1

/RAS0

AB1

MD9

AF2

MD23

AH4

MD35

T2

/CAS7

AB2

MD8

AF3

MD22

AH5

MD39

T3

/CAS6

AB3

MD7

AF4

MD33

AH6

MD44

T4

/CAS5

AB4

MD6

AF5

MD37

AH7

MD48

T5

VDD

AB5

VCC

AF6

MD42

AH8

MD52

T25

VCC

AB25

VCC

AF7

MD46

AH9

MD56

T26

DRQ6

AB26

SA1

AF8

MD50

AH10

MD60

T27

/DACK6

AB27

SA0

AF9

MD54

AH11

/TGNT

T28

DRQ5

AB28

/SBHE

AF10

MD58

AH12

AD2

T29

/DACK5

AB29

LA23

AF11

MD63

AH13

AD7

U1

/WEN

AC1

MD13

AF12

AD0

AH14

AD10

U2

/RAS4

AC2

MD12

AF13

AD5

AH15

AD14

U3

/RAS3

AC3

MD11

AF14

AD8

AH16

/SERR

U4

/RAS2

AC4

MD10

AF15

AD12

AH17

/IRDY

U5

/RAS1

AC5

GND

AF16

/CBE1

AH18

AD18

U25

CPUCLKO

AC25

GND

AF17

/DEVSEL

AH19

AD23

U26

PCICLKO

AC26

SA5

AF18

AD16

AH20

AD26

U27

/MASTER

AC27

SA4

AF19

AD21

AH21

AD29

U28

DRQ7

AC28

SA3

AF20

AD24

AH22

/REQ1

U29

/DACK7

AC29

SA2

AF21

PCICLKI

AH23

/GNT1

V1

MA4

AD1

MD17

AF22

AD31

AH24

/INTD

V2

MA3

AD2

MD16

AF23

/REQ3

AH25

/SOUT

V3

MA2

AD3

MD15

AF24

/GNT3

AH26

SD7

V4

MA1

AD4

MD14

AF25

/INTB

AH27

SD5

V5

MA0

AD5

VCC

AF26

IOCHRDY

AH28

SD2

V25

SD11

AD25

SA10

AF27

AEN

V26

SD12

AD26

SA9

AF28

SA16

AJ1

GND

V27

SD13

AD27

SA8

AF29

SA15

AJ2

MD29

V28

SD14

AD28

SA7

AG1

MD26

AJ3

MD32

V29

SD15

AD29

SA6

AG2

MD25

AJ4

MD36

W1

MA9

AE1

MD21

AG3

MD30

AJ5

MD40

W2

MA8

AE2

MD20

AG4

MD34

AJ6

MD45

W3

MA7

AE3

MD19

AG5

MD38

AJ7

MD49

W4

MA6

AE4

MD18

AG6

MD43

AJ8

MD53

W5

MA5

AE5

GND

AG7

MD47

AJ9

MD57

W25

SYSCLK

AE6

MD41

AG8

MD51

AJ10

MD61

W26

/MEMW

AE7

GND

AG9

MD55

AJ11

TPR

W27

SD8

AE8

VCC

AG10

MD59

AJ12

AD3

W28

SD9

AE9

GND

AG11

/TREQ

AJ13

/CBE0

W29

SD10

AE10

VCC

AG12

AD1

AJ14

AD11

Y1

MD1

AE11

MD62

AG13

AD6

AJ15

AD15

Y2

MD0

AE12

/CLKRUN

AG14

AD9

AJ16

/PCILOCK

Y3

MA11

AE13

AD4

AG15

AD13

AJ17

/FRAME

Y4

MA10

AE14

VCC

AG16

PAR

AJ18

AD19

Y5

VCC

AE15

GND

AG17

/TRDY

AJ19

/CBE3

Y25

VCC

AE16

VDD

AG18

AD17

AJ20

AD27

Y26

LA18

AE17

/STOP

AG19

AD22

AJ21

AD30

Y27

LA17

AE18

/CBE2

AG20

AD25

AJ22

/REQ2

Y28

/MEMR

AE19

AD20

AG21

AD28

AJ23

/GNT2

Y29

REF# /32K

AE20

VCC

AG22

/REQ0

AJ24

/INTC

AA1

MD5

AE21

GND

AG23

/GNT0

AJ25

/SIN

AA2

MD4

AE22

VCC

AG24

/PCIRST

AJ26

SD6

AA3

MD3

AE23

GND

AG25

/INTA

AJ27

SD4

AA4

MD2

AE24

VCC

AG26

IOCHCK

AJ28

SD3

AA5

GND

AE25

GND

AJ29

GND

ACC Micro

2051nt

TM

18

3.3 2051nt Alphabetical Pin List (with L2 cache)

Pin Nam

Pin #

Pin Name

Pin #

Pin Name

Pin #

Pin Name

Pin #

14M

K27

AD28

AG21

D23

E3

/EXTSMI1

E29

A3

A23

AD29

AH21

D24

E2

/EXTSMI2

D27

A4

D22

AD30

AJ21

D25

E1

/EXTSYS

C28

A5

C21

AD31

AF22

D26

F4

/FERR

C13

A6

C22

/ADS

D15

D27

F3

/FRAME

AJ17

A7

B22

AEN

AF27

D28

F2

/GNT0

AG23

A8

A22

AHOLD

A14

D29

F1

/GNT1

AH23

A9

A21

BALE

N26

D30

G4

/GNT2

AJ23

A10

D21

/BATLOW0

E27

D31

G3

/GNT3

AF24

A11

B21

/BE0

B17

D32

G2

/HIT-M

C16

A12

D20

/BE1

C17

D33

G1

/IDEDACK

A28

A13

C20

/BE2

D17

D34

H4

IDEDRQ

B28

A14

B20

/BE3

E17

D35

H3

/IGNNE

D26

A15

A20

/BE4

A18

D36

H2

INIT

C26

A16

E19

/BE5

B18

D37

H1

/INTA

AG25

A17

D19

/BE6

C18

D38

J4

/INTB

AF25

A18

C19

/BE7

D18

D39

J3

/INTC

AJ24

A19

B19

/BOFF

A15

D40

J2

/INTD

AH24

A20

A19

/BRDY

C14

D41

J1

INTR

D25

A21

B25

/CACHE

E13

D42

K4

IOCHCK

AG26

A22

E24

/CAS0

P1

D43

K3

IOCHRDY

AF26

A23

C25

/CAS1

R4

D44

K2

/IOCS16

P29

A24

A25

/CAS2

R3

D45

K1

/IOR

L28

A25

B24

/CAS3

R2

D46

L5

/IOW

L29

A26

C24

/CAS4

R1

D47

L4

/IRDY

AH17

A27

D24

/CAS5

T4

D48

L3

IRQ1

H27

A28

A24

/CAS6

T3

D49

L2

IRQ3

N29

A29

C23

/CAS7

T2

D50

L1

IRQ4

M25

A30

B23

/CBE0

AJ13

D51

M5

IRQ5

M26

A31

D23

/CBE1

AF16

D52

M4

IRQ6

M27

/A20M

A17

/CBE2

AE18

D53

M3

IRQ7

M28

ACPWR

D29

/CBE3

AJ19

D54

M2

IRQ8

E26

AD0

AF12

/CLKRUN

AE12

D55

M1

IRQ9

J28

AD1

AG12

CLKSRC

K26

D56

N5

IRQ10

P28

AD2

AH12

CPUCLKI

D12

D57

N4

IRQ11

P27

AD3

AJ12

CPUCLKO

U25

D58

N3

IRQ12

P26

AD4

AE13

CPURST

E18

D59

N2

IRQ14

R28

AD5

AF13

D0

C7

D60

N1

IRQ15

R29

AD6

AG13

D1

B7

D61

P4

KALE

E12

AD7

AH13

D2

A7

D62

P3

/KBCS

H28

AD8

AF14

D3

D6

D63

P2

KBGA20

H29

AD9

AG14

D4

C6

/DACK0

R27

/KBRST

G26

AD10

AH14

D5

B6

/DACK1

L25

/KCS

A13

AD11

AJ14

D6

A6

/DACK2

N28

KCLK

D7

AD12

AF15

D7

D5

/DACK3

L27

/KEN

B14

AD13

AG15

D8

C5

/DACK5

T29

/KOE

B13

AD14

AH15

D9

B5

/DACK6

T27

/KWE0

D9

AD15

AJ15

D10

A5

/DACK7

U29

/KWE1

C9

AD16

AF18

D11

C4

DC

A16

/KWE2

B9

AD17

AG18

D12

B4

/DEVSEL

AF17

/KWE3

A9

AD18

AH18

D13

A4

DRQ0

R26

/KWE4

D8

AD19

AJ18

D14

B3

DRQ1

M29

/KWE5

C8

AD20

AE19

D15

A3

DRQ2

J27

/KWE6

B8

AD21

AF19

D16

A2

DRQ3

L26

/KWE7

A8

AD22

AG19

D17

C2

DRQ5

T28

LA17

Y27

AD23

AH19

D18

C1

DRQ6

T26

LA18

Y26

AD24

AF20

D19

D3

DRQ7

U28

LA19

AA29

AD25

AG20

D20

D2

DTY

A10

LA20

AA28

AD26

AH20

D21

D1

/EADS

B16

LA21

AA27

AD27

AJ20

D22

E4

/EXTSMI0

E28

LA22

AA26

ACC Micro

2051nt

TM

19

2051nt Alphabetical Pin List contd....

Pin Name

Pin #

Pin Name

Pin #

Pin Name

Pin #

Pin Name

Pin #

LA23

AB29

MD41

AE6

SA6

AD29

/TRDY

AG17

/LOCK

C15

MD42

AF6

SA7

AD28

/TREQ

AG11

MA0

V5

MD43

AG6

SA8

AD27

/WEN

U1

MA1

V4

MD44

AH6

SA9

AD26

WR

D16

MA2

V3

MD45

AJ6

SA10

AD25

/XDIR

H26

MA3

V2

MD46

AF7

SA11

AE29

/ZWS

J26

MA4

V1

MD47

AG7

SA12

AE28

GND

A1,A29,B1,

MA5

W5

MD48

AH7

SA13

AE27

B2,C3,D4,

MA6

W4

MD49

AJ7

SA14

AE26

E5,E7,E9,

MA7

W3

MD50

AF8

SA15

AF29

E15,E21,E23,

MA8

W2

MD51

AG8

SA16

AF28

E25,G5,G25,

MA9

W1

MD52

AH8

/SBHE

AB28

J5,J25,R5,

MA10

Y4

MD53

AJ8

SD0

AG29

R25,AA5,

MA11

Y3

MD54

AF9

SD1

AG28

AA25,AC5,

/MASTER

U27

MD55

AG9

SD2

AH28

AC25,AE5,

/MCS16

N25

MD56

AH9

SD3

AJ28

AE7,AE9,

MD0

Y2

MD57

AJ9

SD4

AJ27

AE15,AE21,

MD1

Y1

MD58

AF10

SD5

AH27

AE23,AE25,

MD2

AA4

MD59

AG10

SD6

AJ26

AJ1,AJ29

MD3

AA3

MD60

AH10

SD7

AH26

VCC

E6,E8,E10,

MD4

AA2

MD61

AJ10

SD8

W27

E16,E20,E22,

MD5

AA1

MD62

AE11

SD9

W28

F5,F25,H5,

MD6

AB4

MD63

AF11

SD10

W29

H25,K5,K25,

MD7

AB3

/MEMR

Y28

SD11

V25

P5,T25,Y5,

MD8

AB2

/MEMW

W26

SD12

V26

Y25,AB5,

MD9

AB1

MIO

D13

SD13

V27

AB25,AD5,E8

MD10

AC4

/NA

D14

SD14

V28

AE10,AE14,

MD11

AC3

NMI

A26

SD15

V29

AE20,AE22,

MD12

AC2

PAR

AG16

/SERR

AH16

AE24

MD13

AC1

PCICLKI

AF21

/SIN

AJ25

VDD

E14,P25,

MD14

AD4

PCICLKO

U26

SMCLK

G27

T5,AE16

MD15

AD3

/PCILOCK

AJ16

SMDATA

G28

MD16

AD2

/PCIRST

AG24

/SMEMR

K28

MD17

AD1

PWRGD

B27

/SMEMW

K29

MD18

AE4

PWR0

C29

/SMIACT

B15

MD19

AE3

PWR1

B29

/SMI

B26

MD20

AE2

/RAS0

T1

/SOUT

AH25

MD21

AE1

/RAS1

U5

SPKR

F26

MD22

AF3

/RAS2

U4

/SRBTN

D28

MD23

AF2

/RAS3

U3

/STOP

AE17

MD24

AF1

/RAS4

U2

/STPCLK

A27

MD25

AG2

REF# /32K

Y29

/SUSP

C27

MD26

AG1

/REQ0

AG22

SYSCLK

W25

MD27

AH1

/REQ1

AH22

TAG0

E11

MD28

AH2

/REQ2

AJ22

TAG1

D11

MD29

AJ2

/REQ3

AF23

TAG2

C11

MD30

AG3

RSTDRV

J29

TAG3

B11

MD31

AH3

RTCAS

F27

TAG4

A11

MD32

AJ3

/RTCDS

F29

TAG5

D10

MD33

AF4

/RTCWR

F28

TAG6

C10

MD34

AG4

/ROMCS

G29

TAG7

B10

MD35

AH4

SA0

AB27

/TAGWE

A12

MD36

AJ4

SA1

AB26

TC

N27

MD37

AF5

SA2

AC29

/TGNT

AH11

MD38

AG5

SA3

AC28

/TKA3/ADSC#

B12

MD39

AH5

SA4

AC27

/TKA4/ADSV#

C12

MD40

AJ5

SA5

AC26

TPR

AJ11

ACC Micro

2051nt

TM

20

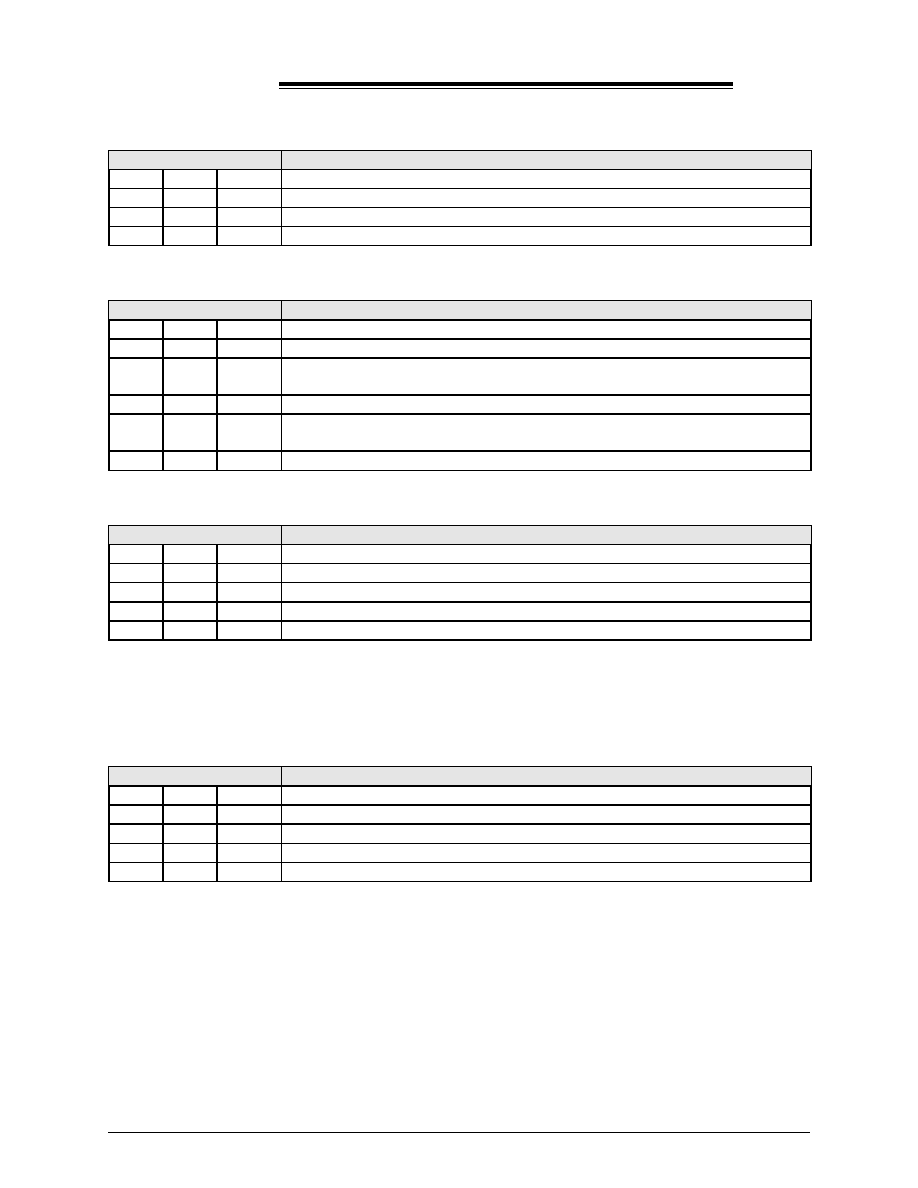

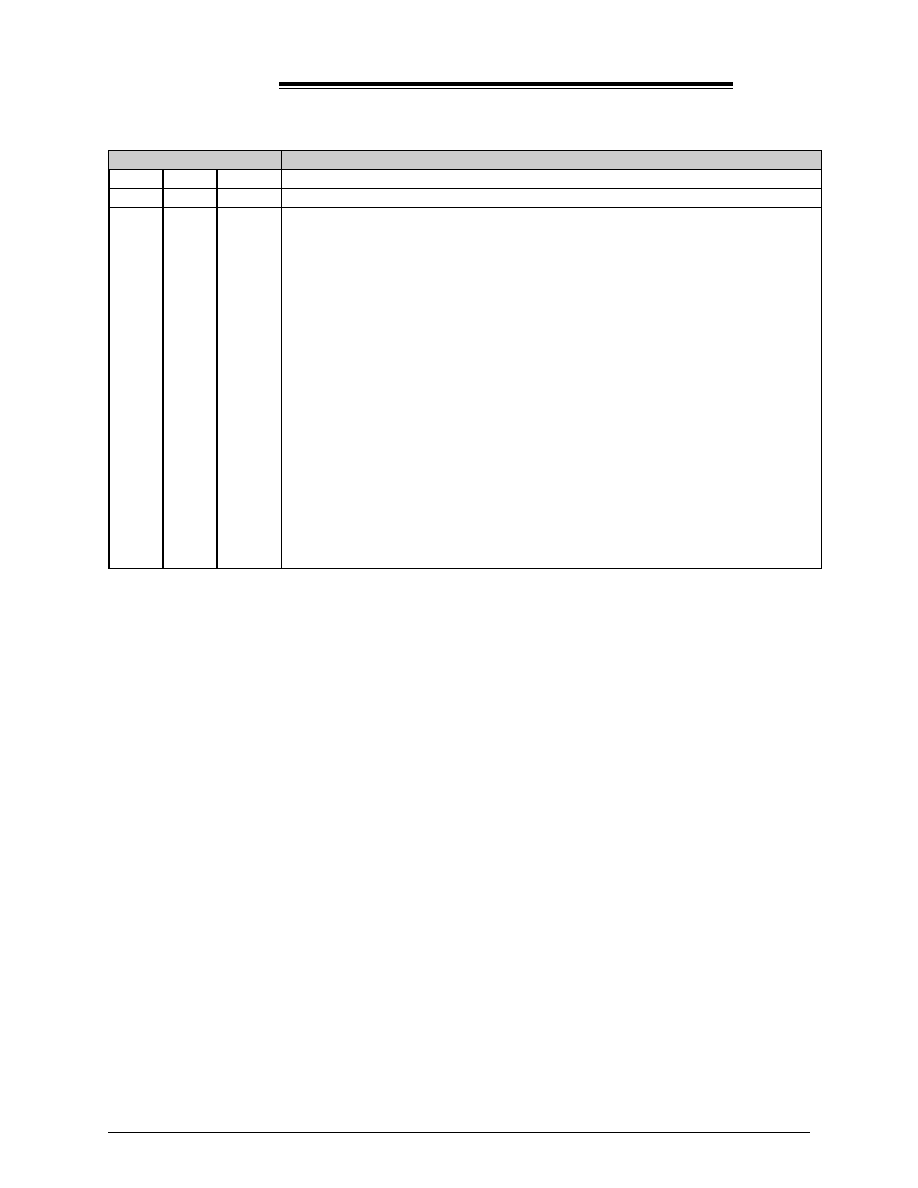

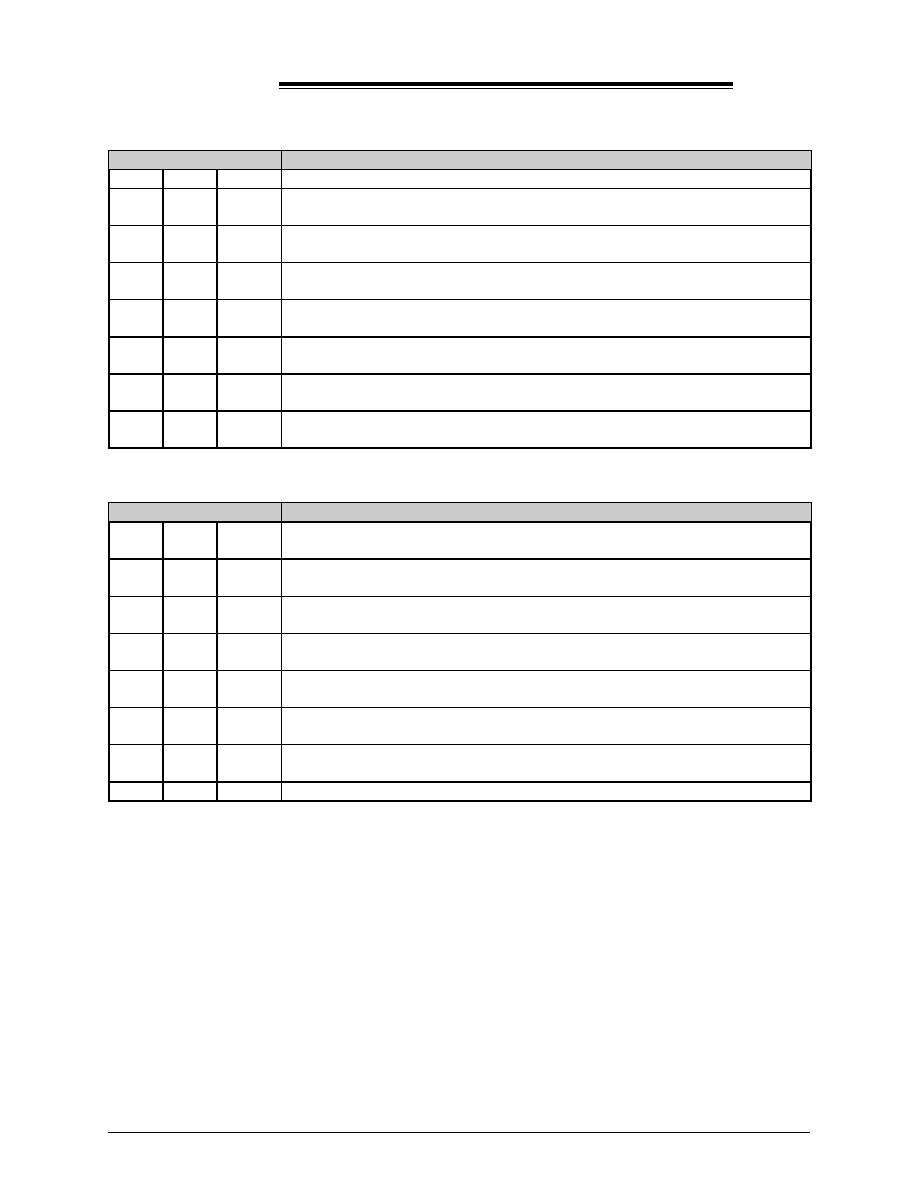

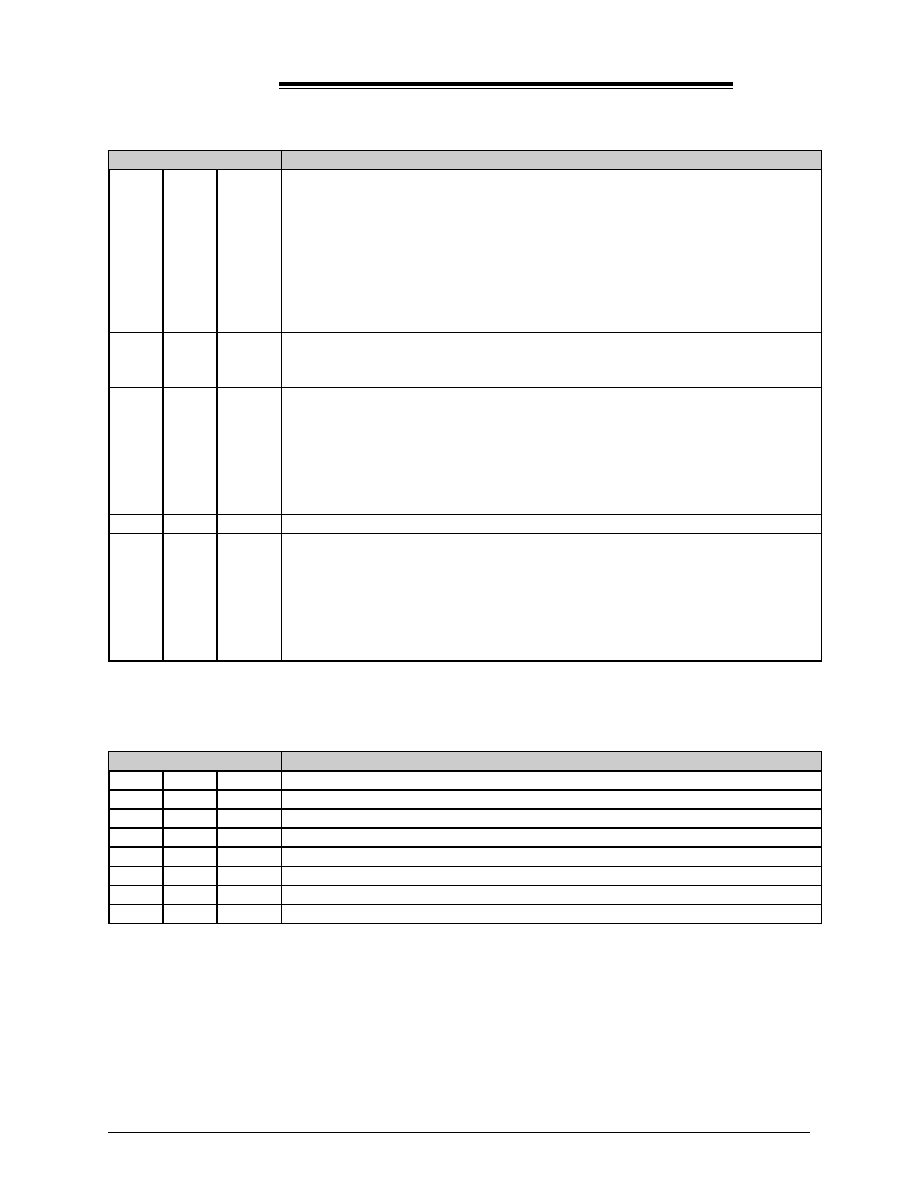

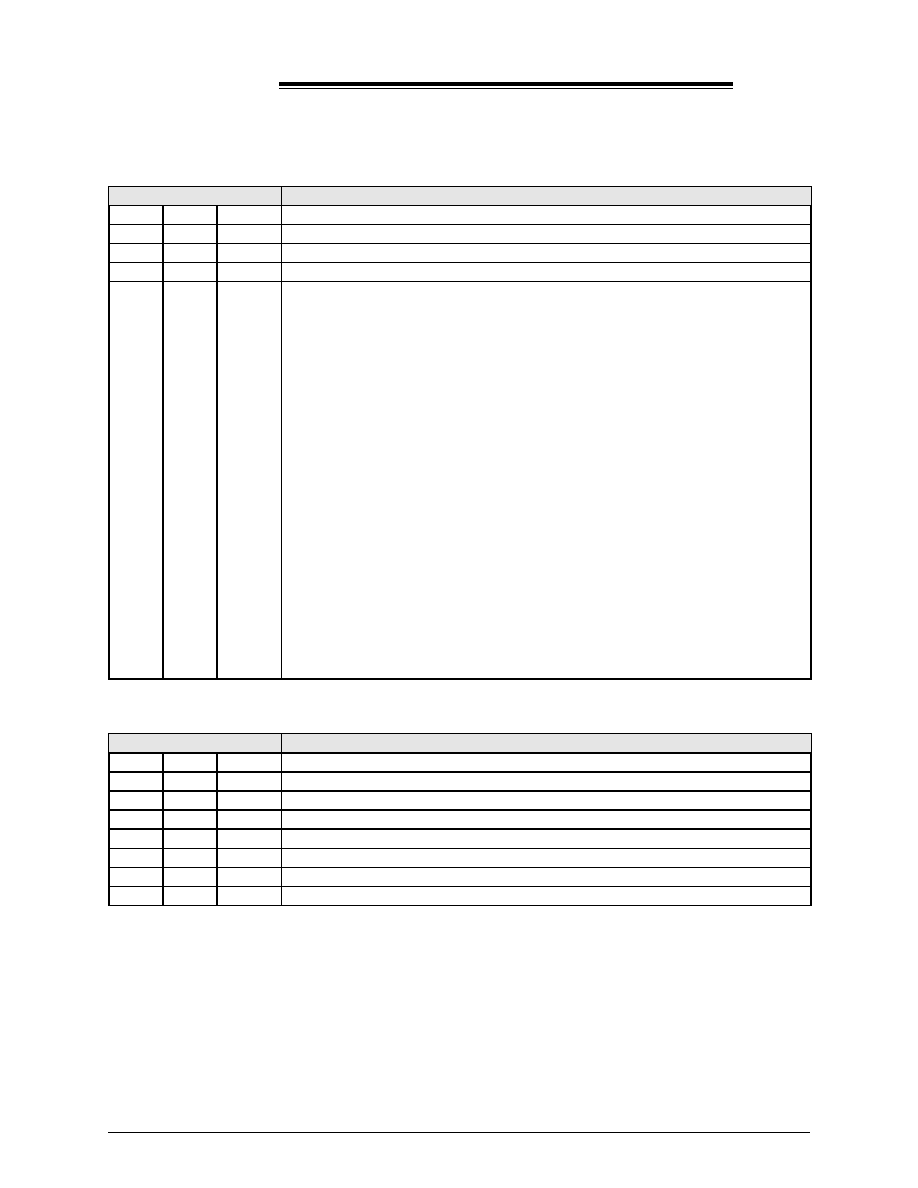

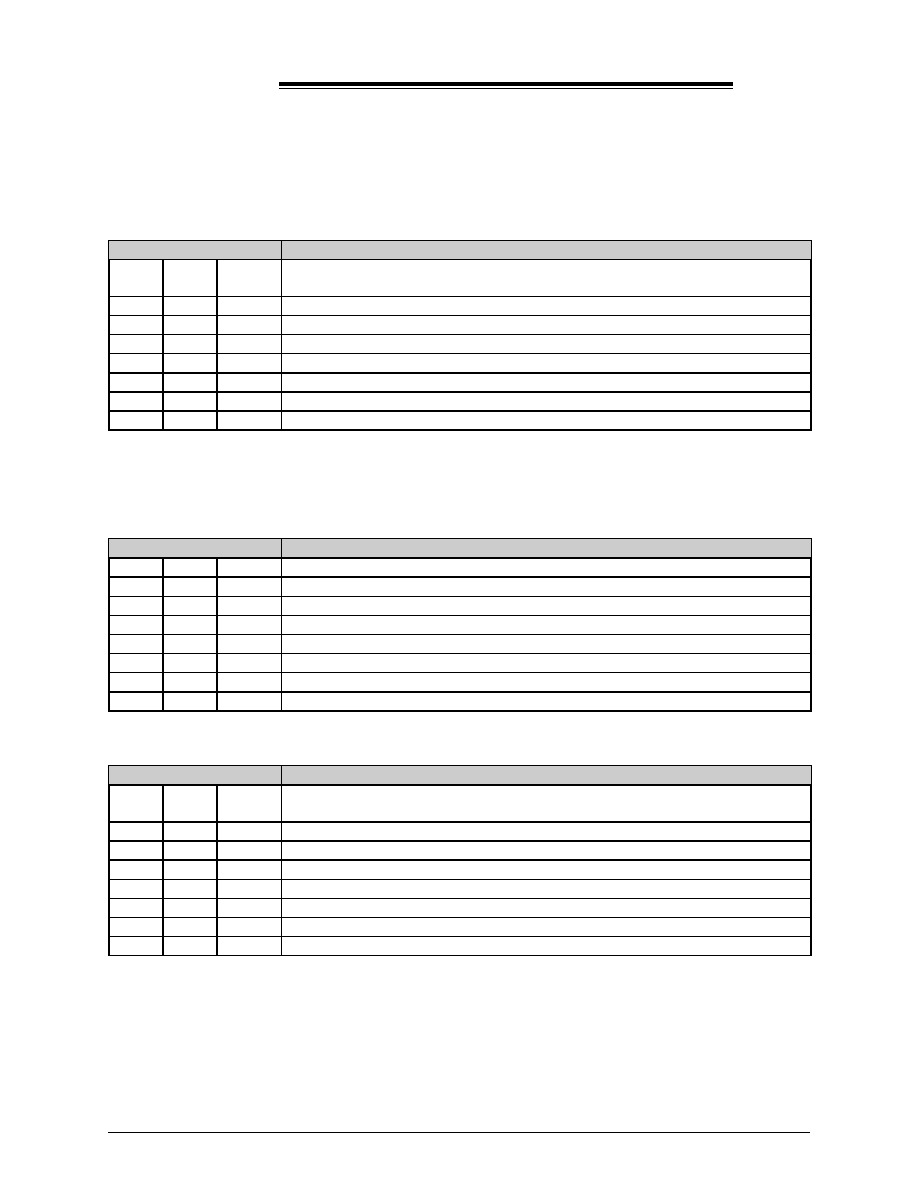

3.4

Summary Table for ACC Micro 2051nt Multiplex Pins

Pin #

Signal Name

Description

Related Register

B13

/KOE

Cache output enable

When L2 cache is enabled (Reg. 74h, 75h)

KCSTS0

Status input bit 0

Reg. 88h, bit 0 = 1 & L2 cache disable

A13

/KCS

Cache chip select

When L2 cache is enabled (Reg. 74h, 75h)

KCSTS1

Status input bit 1

Reg. 88h, bit 1 = 1

E12

KALE

Cache address latch enable

When L2 cache is enabled (Reg. 74h, 75h)

PWROUT0

Power output bit 0

Reg. 82h, bit 0 = 1

C12

/TKA4

A4 for Asyn. SRAM

Reg. 74h, bit 2 = 1 to select Asyn. SRAM

/ADSV

For Burst SRAM

Reg. 74h, bit 1 = 1 to select Burst SRAM

KCSTS2

Status input bit 2

Reg. 88h, bit 2 = 1

B12

/TKA3

A3 for Asyn. SRAM

Reg. 74h, bit 2 = 1 to select Asyn. SRAM

/ADSC

For Burst SRAM

Reg. 74h, bit 1 = 1 to select Burst SRAM

KCSTS3

Status input bit 3

Reg. 88h, bit 3 = 1

A12

/TAGWE

Tag write enable

When L2 cache is enabled (Reg. 74h, 75h)

KCSTS4

Status input bit 4

Reg. 88h, bit 4 = 1

E11

TAG0

Tag bit 0

When L2 cache is enabled (Reg. 74h, 75h)

TPWROUT0

(Tag) power output bit 0

Reg. 8Ah, bit 0 = 1

D11

TAG1

Tag bit 1

When L2 cache is enabled (Reg. 74h, 75h)

TPWROUT1

(Tag) power output bit 1

Reg. 8Ah, bit 1 = 1

C11

TAG2

Tag bit 2

When L2 cache is enabled (Reg. 74h, 75h)

TPWROUT2

(Tag) power output bit 2

Reg. 8Ah, bit 2 = 1

B11

TAG3

Tag bit 3

When L2 cache is enabled (Reg. 74h, 75h)

TPWROUT3

(Tag) power output bit 3

Reg. 8Ah, bit 3 = 1

A11

TAG4

Tag bit 4

When L2 cache is enabled (Reg. 74h, 75h)

TPWROUT4

(Tag) power output bit 4

Reg. 8Ah, bit 4 = 1

D10

TAG5

Tag bit 5

When L2 cache is enabled (Reg. 74h, 75h)

TPWRO5

(Tag) power output bit 5

Reg. 8Ah, bit 5 = 1

C10

TAG6

Tag bit 6

When L2 cache is enabled (Reg. 74h, 75h)

TPWROUT6

(Tag) power output bit 6

Reg. 8Ah, bit 6 = 1

B10

TAG7

Tag bit 7

When L2 cache is enabled (Reg. 74h, 75h)

PWROUT4

Power output bit 4

Reg. 82h, bit 4 = 1

A10

DTY

Cache Dirty

When L2 cache is enabled (Reg. 74h, 75h)

TPWROUT7

(Tag) power output bit 7

Reg. 8Ah, bit 7 = 1

U3

/RAS3

RAS bank 3

Power on default

PWROUT2

Power output bit 2

Reg. 82h, bit 2 = 1

ACC Micro

2051nt

TM

21

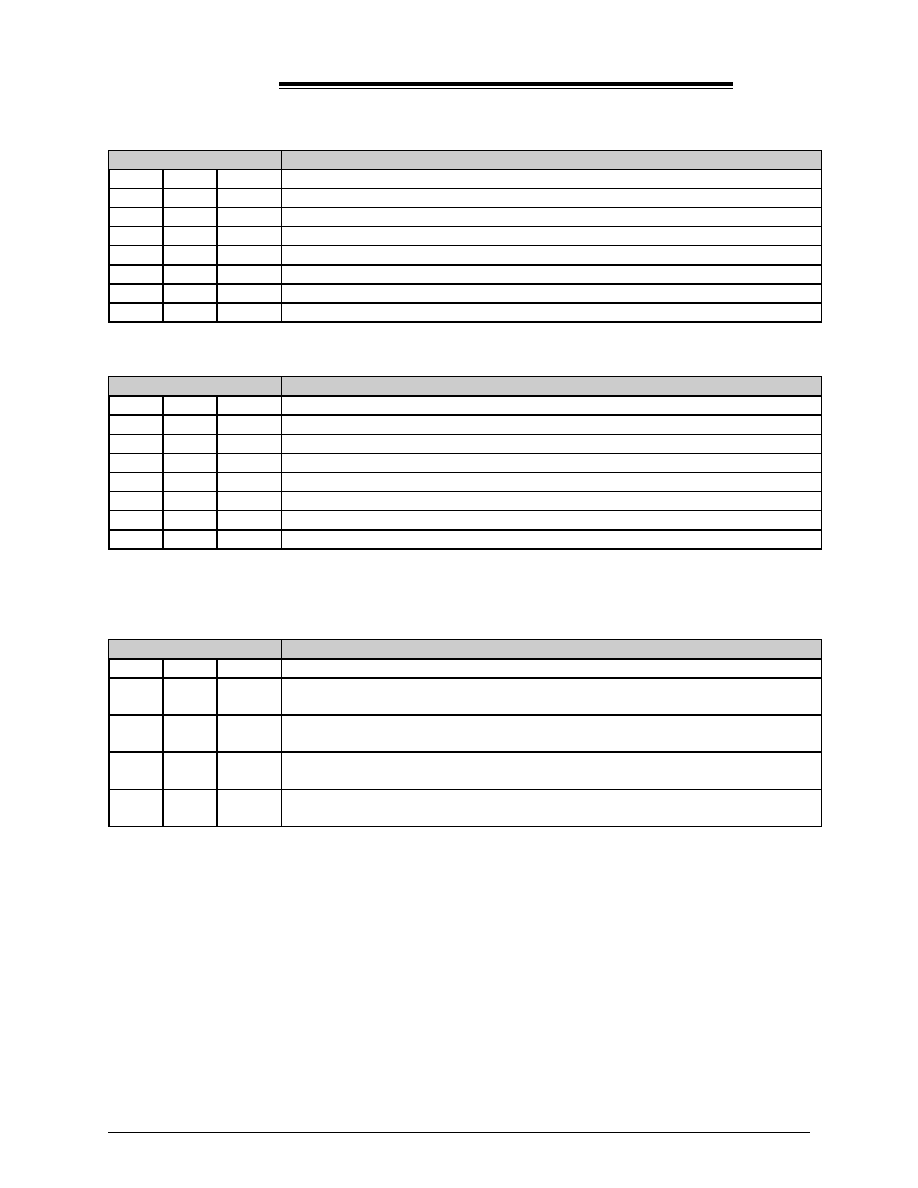

ACC Micro 2051nt Multiplex Pins contd...

Pin #

Signal Name

Description

Related Register

D9

/KWE0

Cache write enable

When L2 cache is enabled (Reg. 74h, 75h)

KWSTS0

(Cache) Status input bit 0

Reg. 89h, bit 0 = 1

C9

/KWE1

Cache write enable

When L2 cache is enabled (Reg. 74h, 75h)

KWSTS1

(Cache) Status input bit 1

Reg. 89h, bit 1 = 1

B9

/KWE2

Cache write enable

When L2 cache is enabled (Reg. 74h, 75h)

KWSTS2

(Cache) Status input bit 2

Reg. 89h, bit 2 = 1

A9

/KWE3

Cache write enable

When L2 cache is enabled (Reg. 74h, 75h)

KWSTS3

(Cache) Status input bit 3

Reg. 89h, bit 3 = 1

D8

/KWE4

Cache write enable

When L2 cache is enabled (Reg. 74h, 75h)

KWSTS4

(Cache) Status input bit 4

Reg. 89h, bit 4 = 1

C8

/KWE5

Cache write enable

When L2 cache is enabled (Reg. 74h, 75h)

KWSTS5

(Cache) Status input bit 5

Reg. 89h, bit 5 = 1

B8

/KWE6

Cache write enable

When L2 cache is enabled (Reg. 74h, 75h)

KWSTS6

(Cache) Status input bit 6

Reg. 89h, bit 6 = 1

A8

/KWE7

Cache write enable

When L2 cache is enabled (Reg. 74h, 75h)

KWSTS7

(Cache) Status input bit 7

Reg. 89h, bit 7 = 1

B29

PWR1

Power output bit 1

Power on default

/LATCH1

External latch control for

PWR8-15

Reg. 6h, bit 3 = 0, Reg. 6h, bit 2 = 1

/DOZE

Doze pin

Reg. 6h, bit 3 =1, Reg. 6h, bit 2 = 0

/PCS1

General chip select bit 2

Reg. 6h, bit 3 = 1, Reg. 6h, bit 2 = 1

C29

PWR0

Power output bit 0

Power on default

/LATCH0

External latch control for

PWR0-7

Reg. 6h, bit 5 = 0, Reg. 6h, bit 4 = 1

/PCS0

General chip select bit 1

Reg. 6h, bit 5 = 1, Reg. 6h, bit 4 = 0

U29

/DACK7

DMA acknowledge channel 7

Power on default

PWR9

Power output bit 9

Regi. 7h, bit 5 = 1

T27

/DACK6

DMA acknowledge channel 6

Power on default

PWR8

Power output bit 8

Reg. 7h, bit 5 = 1

R27

/DACK0

DMA acknowledge channel 0

Power on default

PWR5

Power output bit 5

Reg. 7h, bit 5 = 1

P26

IRQ12

Interrupt 12

Power on default

MSDATA

Mouse data

Reg. 68h, bit 7 = 1

L25

/DACK1

DMA acknowledge channel 1

Power on default

PWR6

Power output bit 6

Reg. 7h, bit 5 = 1

L27

/DACK3

DMA acknowledge channel 3

Power on default

PWR7

Power output bit 7

Reg. 7h, bit 5 = 1

ACC Micro

2051nt

TM

22

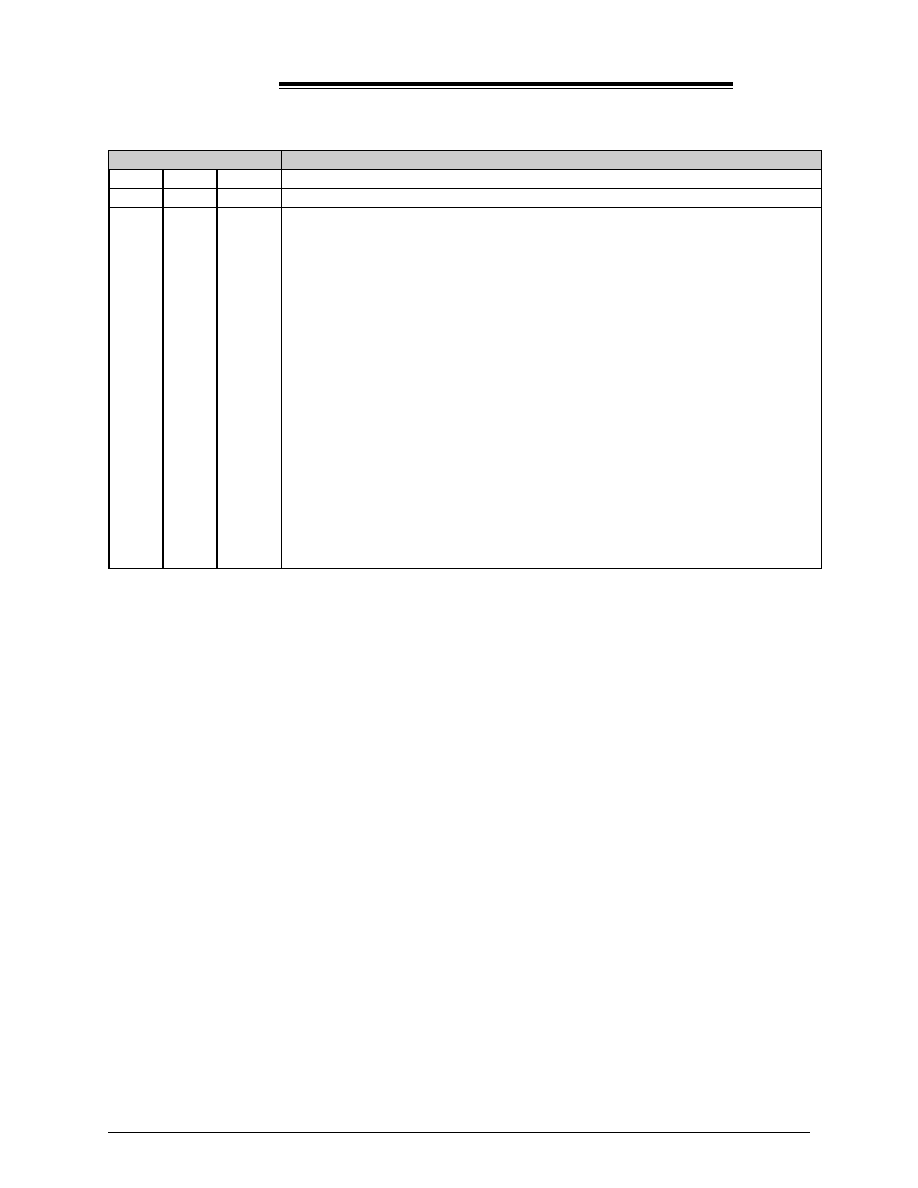

ACC Micro 2051nt Multiplex Pins contd...

Pin #

Signal Name

Description

Related Register

K28

PWR4

Power output bit 4

Power on default Reg. 7h bit 4 = x, bit 3 = x, bit 2 = 0.

/SMEMR

System memory read

Reg. 7h, bit 4 = 0, bit 3 = 1, bit 2 = 1.

/PCS2

Programmable chip select 2

Reg. 7h, bit 4 = 1, bit 3 = 0, bit 2 = 1..

K29

PWR2

Power output bit 2

Power on default. Reg. 7h bit 4 = x, bit 0 = 0.

/SMEMW

System memory write

Reg. 7h, bit 4 = 0, bit 0 = 1.

/PCS3

Programmable chip select 3

Reg. 7h, bit 4 = 1, bit 0 = 1.

H27

IRQ1

Interrupt 1

Power on default

/KEYLOCK

Keylock

Reg. 68h, bit 7 = 1

H28

/KBCS

Keyboard chip select

Power on default

MSCLK

Mouse clock

Reg. 68h, bit 7 = 1

H29

KBGA20

Keyboard GA20

Power on default

KBDATA

Keyboard data

Reg. 68h, bit 7 = 1

G26

/KBRST

Keyboard reset

Power on default

KBCLK

Keyboard clock

Reg. 68h, bit 7 = 1

W25

PWR3

Power output bit 3

Power on default

SYSCLK

System clock

Reg. 7h, bit 1 = 1

U2

/RAS4

RAS bank 4

Power on default

PWROUT1

Power output bit 1

Reg. 82h, bit 1 = 1

Y29

X32K

32KHz Clock Source

Reg. 81h, bit 7 = 1

/REF

DRAM refresh

Power on default

A28

/IDEDACK

IDE master

Reserved.

PWROUT3

Power out bit 3

Reserved. Power on default

AG11

/TREQ

UMA protocol

Reserved.

GPIO0

General purpose I/O

Power on default

AH11

/TGNT

UMA protocol

Reserved.

GPIO1

General purpose I/O

Power on default

AJ11

TPR

UMA protocol

Reserved.

GPIO2

General purpose I/O

Power on default

G28

SMDATA

SM Bus

Reserved

GPIO5

Power on default

G27

SMCLK

SM Bus

Reserved

GPIO6

Power on default

B28

IDEDRQ

IDE master

Reserved.

GPIO7

General purpose I/O

Reserved. Power on default

ACC Micro

2051nt

TM

23

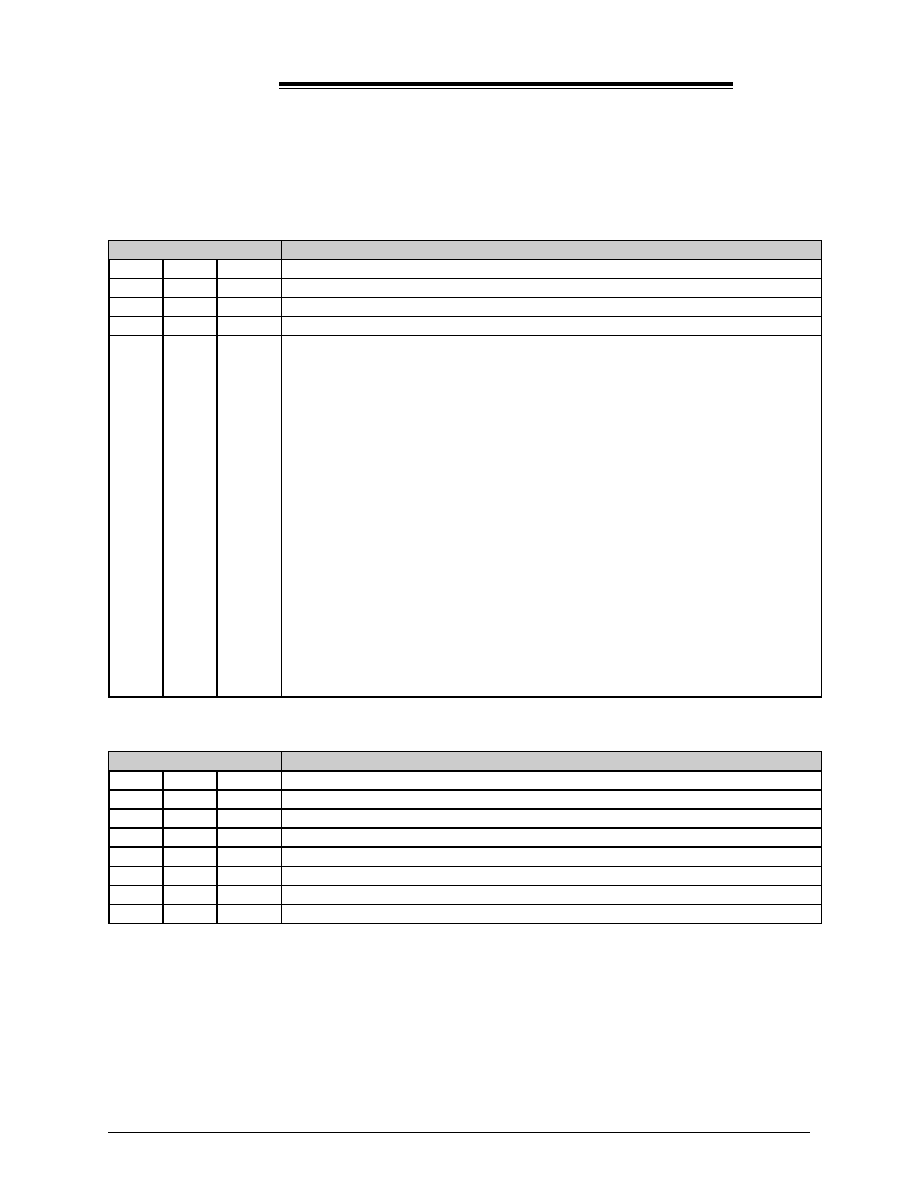

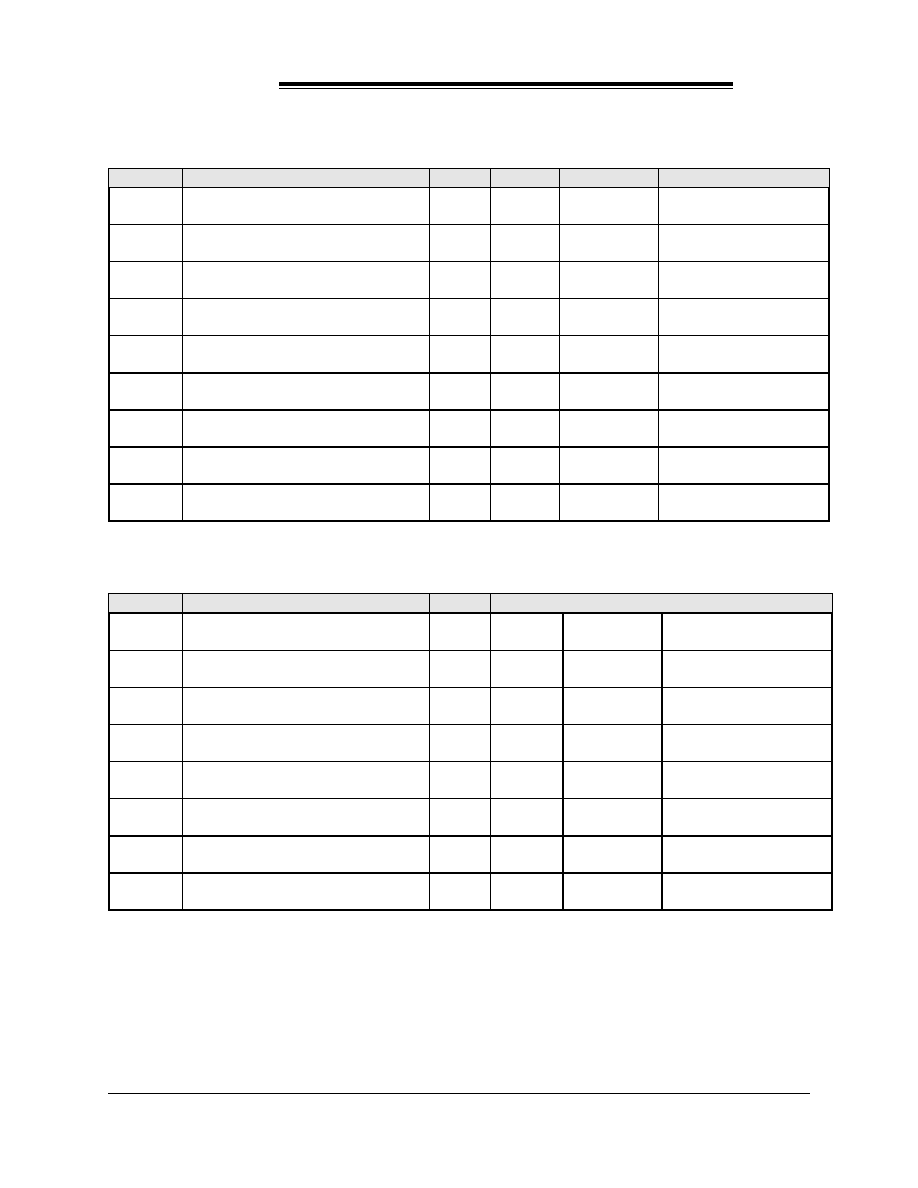

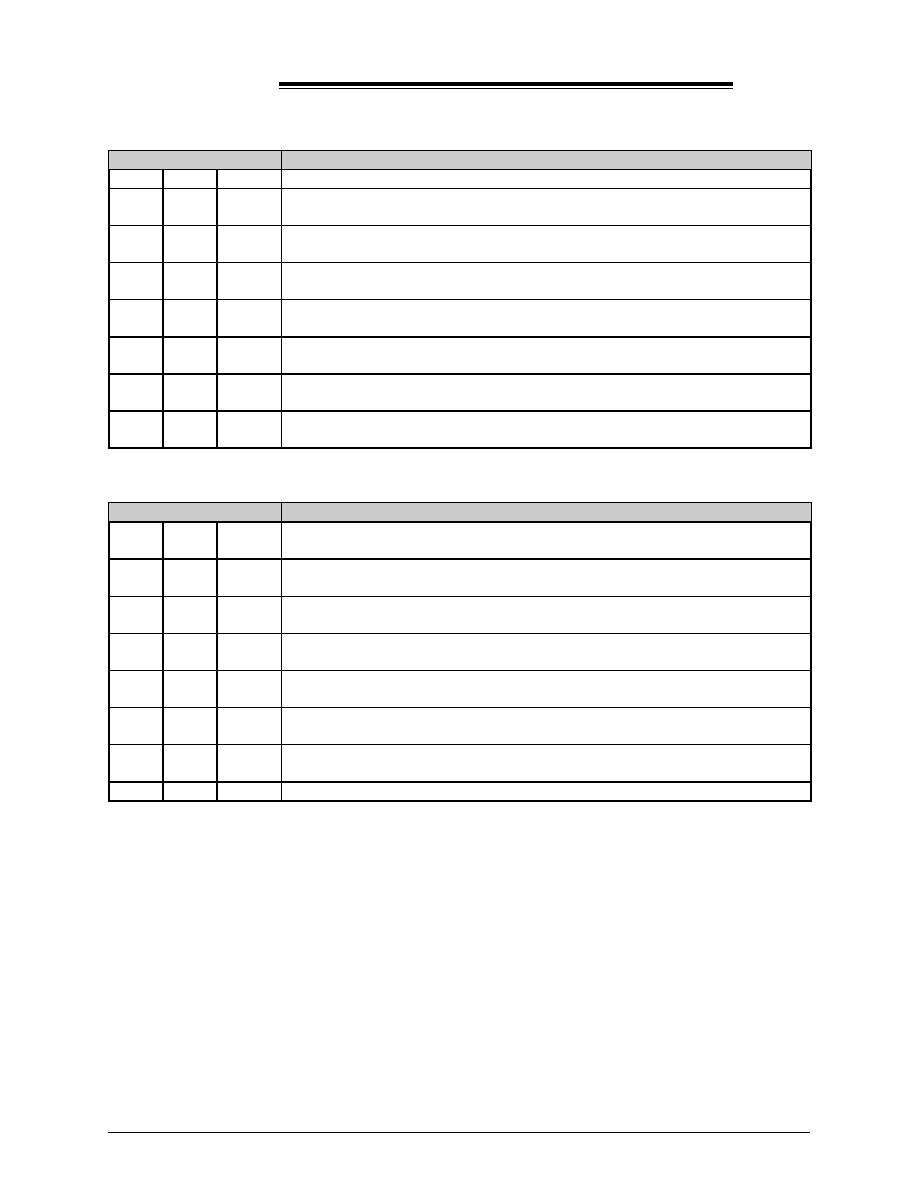

3.5

ACC Micro 2051nt Power Plane Summary Table

VCC Pin Number

VCC

Signal Group

Pin Names

E6, E8, E10, E16, E20,

E22, F5, H5, K5, P5

3.3V / 5.0V

CPU, Cache

D0-63, /STPCLK, /IGNNE, INIT, /SMI, NMI, INTR,

A3-31, CPURST, /BE0-7, /A20M, WR, /HIT-M,

/EADS, DC, /ADS, /LOCK, /SMIACT, /BOFF, /NA,

/BRDY, /KEN, AHOLD, /CACHE, MIO, /FERR,

/KOE, /KCS, KALE, CPUCLKI, /TKA4, TKA3,

/TAGWE, TAG0-7, DTY, /KWE0-7, KCLK

Y5, AB5, AD5, AE8,

AE10,

3.3V / 5.0V

DRAM

/CAS0-7, /RAS0-7, MA0-11MD0-63,

AE14, AE20, AE22,

AE24

3.3V / 5.0V

PCI

GPIO0-2, /CLKRUN, AD0-31, /CBE0-3, PAR,

/SERR, /PCILOCK, /STOP, /DEVSEL, /TRDY,

/IRDY, /FRAME, /REQ0-3, /GNT0-3, /PCIRST,

/INTA-D, /SOUT, /SIN

F25, H25, K25, T25,

Y25, AB25

3.3V / 5.0V

ISA, PMC

IOCHCK, SD0-15, IOCHRDY, AEN, SA0-16,

/SBHE, LA17-23, /MEMR, REF#/32K, SYSCLK,

/MEMW, CPUCLKO, PCICLKO, /MASTER,

/DACK0-3, /DACK5-7, DRQ0-3, DRQ5-7, IRQ1,

IRQ3-12, IRQ14-15, /IOCS16, /MCS16, BALE, TC,

/IOR, /IOW, CLKSRC, 14M, /SMEMR, /SMEMW,

/ZWS, RSTDRV, /XDIR, /KBCS, KBGA20,

/KBRST, SMCLK, SMDATA, /ROMCS, SPKR,

RTCAS, /RTCWR, /RTCDS, /BATLOW0,

/EXTSMI0-2, /SRBTN, ACPWR, /EXTSYS,

PWROUT0, PWROUT1, IDEDRQ, /IDEDACK,

/SUSP, PWRGD

N15, P14-P16, R13-R17,

T14-T16, U15

Thermal

Grounding

GND

ACC Micro

2051nt

TM

24

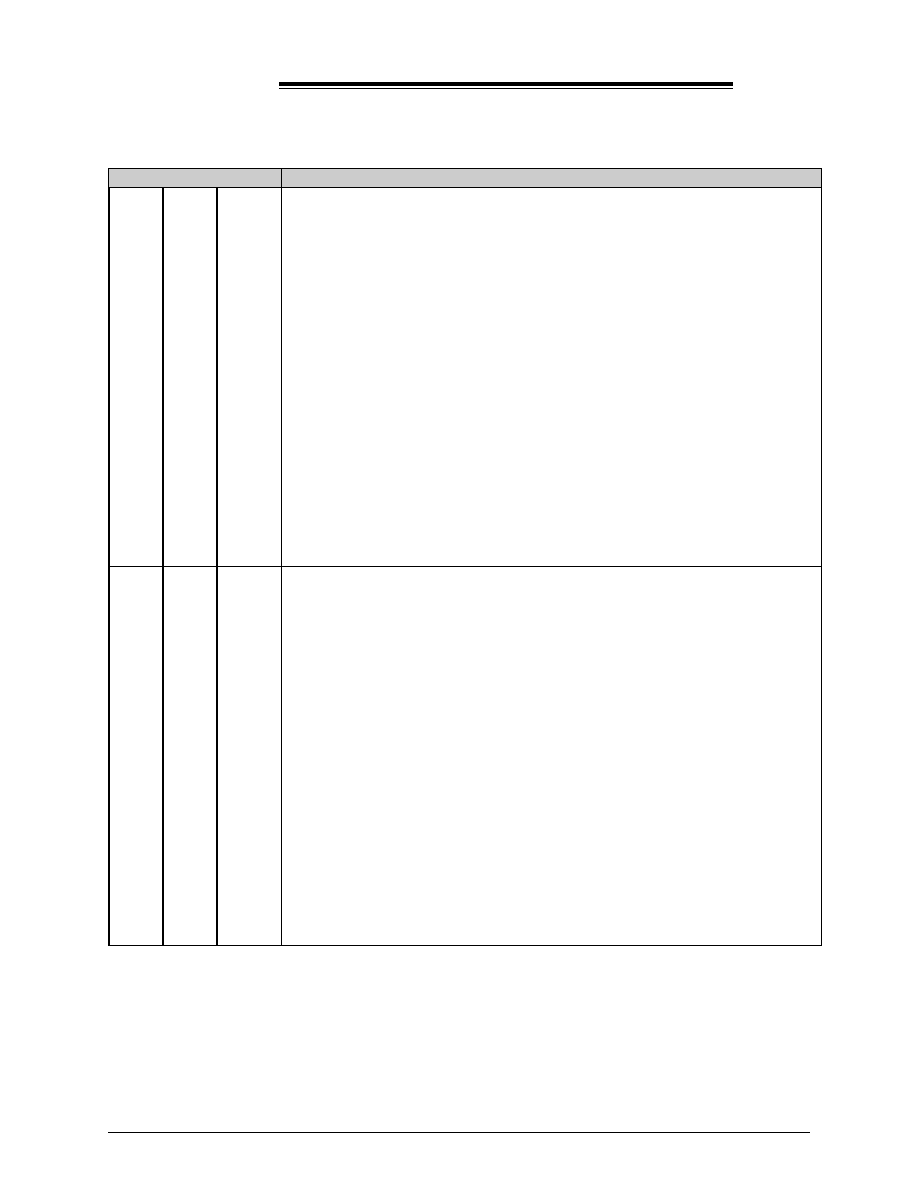

3.6

Shadow Register Application

The ACC Micro 2051nt Shadow Registers are readable and writeable to support Intel SL type of shadow

register. In addition, the ACC Micro 2051nt F2 register is readable to further support the power saving feature

of the ACC Micro 2051nt. Through the shadow registers, the ACC Micro 2051nt can be powered off and its

current state can be suspended to disk. Thus, the device can then be powered back on to the same state as

before the last power off. This suspend and resume capability minimizes the system's battery power

consumption and thus enhances its power management capabilities.

The ACC Micro 2051nt Shadow Registers and its description are listed as below:

1) All the ACC Micro 2051nt Shadow Registers are originally Write-Only in ISA standard. The

shadow

mechanism makes them readable through the 0F2h and 0F3h indexing scheme.

2) For some DMA registers that contain two bytes but have only one index assigned, the following

sequence is recommended:

CLI

; Ensure the sequence would not be broken

OUT

0F2h, INDX ; Output index, clear the byte pointer, point to low byte

MOV

Ah,

AL

; Save it to somewhere

IN

AL,

0F3h

; High byte, byte pointer will not change stay at high byte

Note: Any write to 0F2h with index 0Axh will clear the byte pointer which will set pointer to low

byte.

The first read from 0F3h after writing the index will set the pointer to high byte. Only one byte pointer

is shared by all paired register sets. The first read from 0F3h will return the low byte and the second

read

will return the high byte.

3) For those registers that do not use all the bits, the status of unused bits is reserved. Software needs

to mask out these bits when they are restored.

4) For DMA base address registers, word count registers, channel mode registers and channel mask

registers, the values read back from the shadow registers are the original values loaded.

5) The values read back from shadow registers for the timer count are the original values loaded.

ACC Micro

2051nt

TM

25

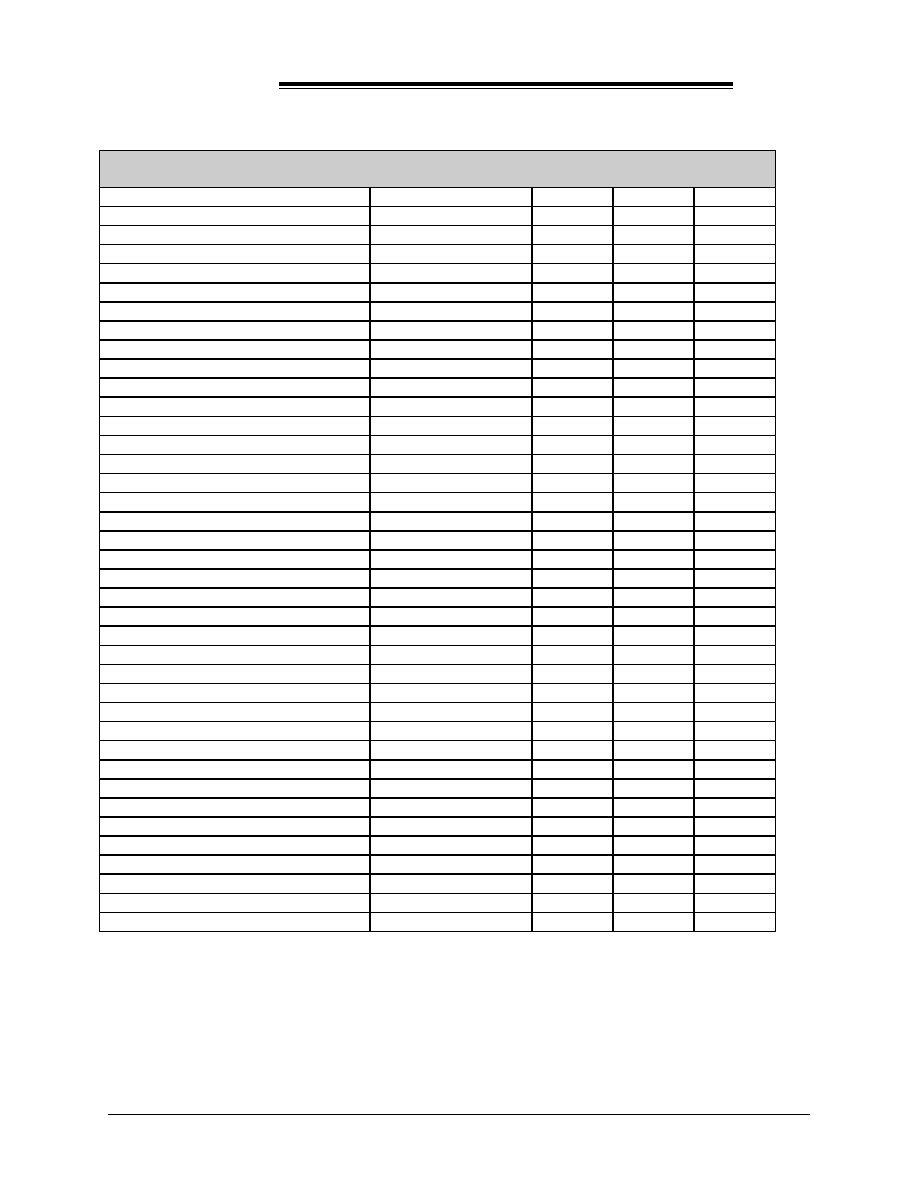

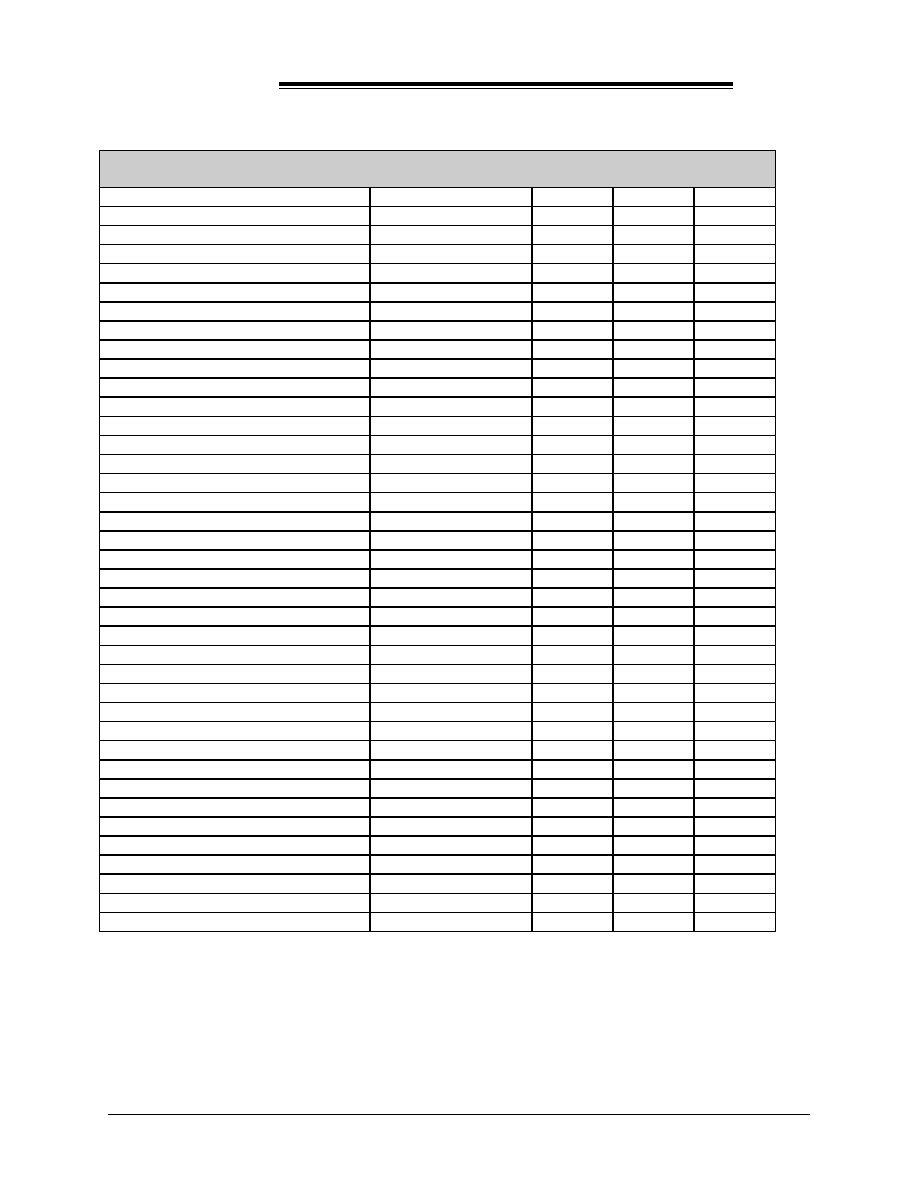

ACC Micro 2051nt Shadow Registers Summary

Register Name

SL Mnemonic

Original

Address

Index

Comment

DMA CH0 Base Address

SHDMA0BA

00H

0A0H

2 bytes

DMA CH0 Count

SHDMA0WC

01h

0A1h

2 bytes

DMA CH1 Base Address

SHDMA1BA

02h

0A2h

2 bytes

DMA CH1 Count

SHDMA1WC

03h

0A3h

2 bytes

DMA CH2 Base Address

SHDMA2BA

04h

0A4h

2 bytes

DMA CH2 Count

SHDMA2WC

05h

0A5h

2 bytes

DMA CH3 Base Address

SHDMA3BA

06h

0A6h

2 bytes

DMA CH3 Count

SHDMA3WC

07h

0A7h

2 bytes

DMA CH0 Mode

SHDMA0MOD

0Bh

0C0h

1 byte

DMA CH1 Mode

SHDMA1MOD

0Bh

0C1h

1 byte

DMA CH2 Mode

SHDMA2MOD

0Bh

0C2h

1 byte

DMA CH3 Mode

SHDMA3MOD

0Bh

0C3h

1 byte

DMA CNTLR 1 Mask Reg.

SHDMAMSK1

0Fh

0C4h

1 byte

PIC1 ICW2

SHINT1ICW2

21h

0D0h

1 byte

PIC1 ICW4

SHINT1ICW4

21h

0D1h

1 byte

PIC1 OCW3

SHINT1OCW3

20h

0D2h

1 byte

NMI Mask & RTC index

SHNMIMASK

70h

0D6h

1 byte

TMR 1 CNTR 0 cnt low

SHT1CH0CL

40h

0CAh

1 byte

TMR 1 CNTR 0 cnt high

SHT1CH0CH

40h

0CBh

1 byte

TMR 1 CNTR 1 cnt low

SHT1CH1CL

41h

0CCh

1 byte

TMR 1 CNTR 1 cnt high

SHT1CH1CH

41h

0CDh

1 byte

TMR 1 CNTR 2 cnt low

SHT1CH2CL

42h

0CEh

1 byte

TMR 1 CNTR 2 cnt high

SHT1CH2CH

42h

0CFh

1 byte

DMA CH4 Base Address

SHDMA4BA

0C0h

0A8h

2 bytes

DMA CH4 Count

SHDMA4WC

0C2h

0A9h

2 bytes

DMA CH5 Base Address

SHDMA5BA

0C4h

0AAh

2 bytes

DMA CH5 Count

SHDMA5WC

0C6h

0ABh

2 bytes

DMA CH6 Base Address

SHDMA6BA

0C8h

0ACh

2 bytes

DMA CH6 Count

SHDMA6WC

0CAh

0ADh

2 bytes

DMA CH7 Base Address

SHDMA7BA

0CCh