1 of 48

REV: 060805

Note: Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device

may be simultaneously available through various sales channels. For information about device errata, click here:

www.maxim-ic.com/errata

.

GENERAL DESCRIPTION

The DS89C430, DS89C440, and DS89C450 offer the

highest performance available in 8051-compatible

microcontrollers. They feature newly designed

processor cores that execute instructions up to 12

times faster than the original 8051 at the same

crystal speed. Typical applications will experience a

speed improvement up to 10x. At 1 million

instructions per second (MIPS) per megahertz, the

microcontrollers achieve 33 MIPS performance from

a maximum 33MHz clock rate.

The Ultra-High-Speed Flash Microcontroller User's Guide should

be used in conjunction with this data sheet. Download it at

www.maxim-ic.com/microcontrollers

.

ORDERING INFORMATION

PART

FLASH

MEMORY SIZE

PIN-PACKAGE

DS89C430-MNL

16kB 40

PDIP

DS89C430-MNL+ 16kB

40

PDIP

DS89C430-QNL 16kB

44

PLCC

DS89C430-QNL+ 16kB

44

PLCC

DS89C430-ENL 16kB

44

TQFP

DS89C430-ENL+ 16kB

44

TQFP

DS89C440-MNL

32kB 40

PDIP

DS89C440-MNL+ 32kB

40

PDIP

DS89C440-QNL 32kB

44

PLCC

DS89C440-QNL+ 32kB

44

PLCC

DS89C440-ENL 32kB

44

TQFP

DS89C440-ENL 32kB

44

TQFP

DS89C450-MNL

64kB 40

PDIP

DS89C450-MNL+ 64kB

40

PDIP

DS89C450-QNL 64kB

44

PLCC

DS89C450-QNL+ 64kB

44

PLCC

DS89C450-ENL 64kB

44

TQFP

DS89C450-ENL+ 64kB

44

TQFP

+ Denotes a lead-free/RoHS-compliant device.

Complete Selector Guide appears at end of data sheet.

Pin Configurations appear at end of data sheet.

FEATURES

� High-Speed 8051 Architecture

One Clock-Per-Machine Cycle

DC to 33MHz Operation

Single Cycle Instruction in 30ns

Optional Variable Length MOVX to Access

Fast/Slow Peripherals

Dual Data Pointers with Automatic

Increment/Decrement and Toggle Select

Supports Four Paged Memory-Access Modes

� On-Chip Memory

16kB/32kB/64kB Flash Memory

In-Application Programmable

In-System Programmable Through Serial Port

1kB SRAM for MOVX

� 80C52 Compatible

8051 Pin and Instruction Set Compatible

Four Bidirectional, 8-Bit I/O Ports

Three 16-Bit Timer Counters

256 Bytes Scratchpad RAM

� Power-Management Mode

Programmable Clock Divider

Automatic Hardware and Software Exit

� ROMSIZE Feature

Selects Internal Program Memory Size from

0 to 64kB

Allows Access to Entire External Memory Map

Dynamically Adjustable by Software

� Peripheral Features

Two Full-Duplex Serial Ports

Programmable Watchdog Timer

13 Interrupt Sources (Six External)

Five Levels of Interrupt Priority

Power-Fail Reset

Early Warning Power-Fail Interrupt

Electromagnetic Interference (EMI) Reduction

APPLICATIONS

Data Logging

Telephones

White Goods

HVAC

Building Energy

Control and

Management

Uninterruptible

Power Supplies

Automotive Text

Equipment

Industrial Control

and Automation

Motor Control

Vending

Magstripe

Reader/Scanner

Gaming

Equipment

Programmable

Logic Controllers

Building Security

and Door Access

Control

Consumer

Electronics

DS89C430/DS89C440/DS89C450

Ultra-High-Speed Flash Microcontrollers

www.maxim-ic.com

DS89C430/DS89C440/DS89C450 Ultra-High-Speed Flash Microcontrollers

2 of 48

ABSOLUTE MAXIMUM RATINGS

Voltage Range on Any Pin Relative to Ground.................................................................................-0.3V to (V

CC

+ 0.5V)

Voltage Range on V

CC

Relative to Ground...............................................................................................-0.3V to +6.0V

Ambient Temperature Range (under bias).............................................................................................-40�C to +85�C

Storage Temperature Range.............................................................................................................-55�C to +125�C

Soldering Temperature......................................................................................................See IPC/JEDEC J-STD-020

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only,

and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is

not implied. Exposure to the absolute maximum rating conditions for extended periods may affect device reliability.

DC ELECTRICAL CHARACTERISTICS

(V

CC

= 4.5V to 5.5V, T

O

= -40�C to +85�C.) (Note 1)

PARAMETER SYMBOL

MIN

TYP

MAX

UNITS

Supply Voltage (Notes 2, 3)

V

CC

4.5 5.0 5.5 V

Power-Fail Warning (Notes 2, 4)

V

PFW

4.2

4.375

4.6 V

Reset Trip Point (Min Operating Voltage) (Notes 2, 3, 4)

V

RST

3.95

4.125

4.35 V

Supply Current, Active Mode (Note 5)

I

CC

75

110

mA

Supply Current, Idle Mode at 33MHz (Note 6)

I

IDLE

40

50

mA

Supply Current, Stop Mode, Bandgap Disabled (Note 7)

I

STOP

1

100

mA

Supply Current, Stop Mode, Bandgap Enabled (Note 7)

I

SPBG

150

300

mA

Input Low Level (Note 2)

V

IL

-0.3 +0.8 V

Input High Level (Note 2)

V

IH

2.0

V

CC

+ 0.3

V

Input High Level XTAL and RST (Note 2)

V

IH2

3.5

V

CC

+ 0.3

V

Output Low Voltage, Port 1 and 3 at I

OL

= 1.6mA (Note 2)

V

OL1

0.15

0.45

V

Output Low Voltage, Port 0 and 2, ALE,

PSEN at I

OL

= 3.2mA

(Note 2)

V

OL2

0.15

0.45

V

Output High Voltage, Port 1, 2, and 3, at I

OH

= -50

mA

(Notes 2, 8)

V

OH1

2.4 V

Output High Voltage, Port 1, 2, and 3 at I

OH

= -1.5mA (Notes 2, 9)

V

OH2

2.4 V

Output High Voltage, Port 0, 1, 2, ALE,

PSEN, RD, WR in Bus

Mode at I

OH

= -8mA (Notes 2, 10)

V

OH3

2.4 V

Output High Voltage, RST at I

OL

= -0.4mA (Note 2, 11)

V

OH4

2.4 V

Input Low Current, Port 1, 2, and 3 at 0.4V

I

IL

-50

mA

Transition Current from 1 to 0, Port 1, 2, and 3 at 2V (Note 12)

I

TL

-650

mA

Input Leakage Current, Port 0 in I/O Mode and

EA (Note 13)

I

L

-10

+10

mA

Input Current, Port 0 in Bus Mode (Note 14)

I

L

-300

+300

mA

RST Pulldown Resistance (Note 13)

R

RST

50 120 200 k

W

DS89C430/DS89C440/DS89C450 Ultra-High-Speed Flash Microcontrollers

3 of 48

Note 1:

Specifications to -40�C are guaranteed by design and not production tested.

Note 2:

All voltages are referenced to ground.

Note 3:

The user should note that this part is tested and guaranteed to operate down to 4.5V (10%) and that V

RST

(min) is specified below

that point. This indicates that there is a range of voltages [(V

MIN

to V

RST

(min)] where the processor's operation is not guaranteed, but

the reset trip point has not been reached. This should not be an issue in most applications, but should be considered when proper

operation must be maintained at all times. For these applications, it may be desirable to use a more accurate external reset.

Note 4:

While the specifications for V

PFW

and V

RST

overlap, the design of the hardware makes it so this is not possible. Within the ranges

given, there is guaranteed separation between these two voltages.

Note 5:

Active current is measured with a 33MHz clock source driving XTAL1, V

CC

= RST = 5.5V. All other pins are disconnected.

Note 6:

Idle mode current is measured with a 33MHz clock source driving XTAL1, V

CC

= 5.5V, RST at ground. All other pins are

disconnected.

Note 7:

Stop mode is measured with XTAL and RST grounded, V

CC

= 5.5V. All other pins are disconnected.

Note 8:

RST = 5.5V. This condition mimics the operation of pins in I/O mode.

Note 9:

During a 0-to-1 transition, a one shot drives the ports hard for two clock cycles. This measurement reflects a port pin in transition

mode.

Note 10:

When addressing external memory.

Note 11:

Guaranteed by design.

Note 12:

Ports 1, 2, and 3 source transition current when pulled down externally. The current reaches its maximum at approximately 2V.

Note 13:

RST = 5.5V. Port 0 is floating during reset and when in the logic-high state during I/O mode.

Note 14:

This port is a weak address holding latch in bus mode. Peak current occurs near the input transition point of the holding latch at

approximately 2V.

DS89C430/DS89C440/DS89C450

4 of 48

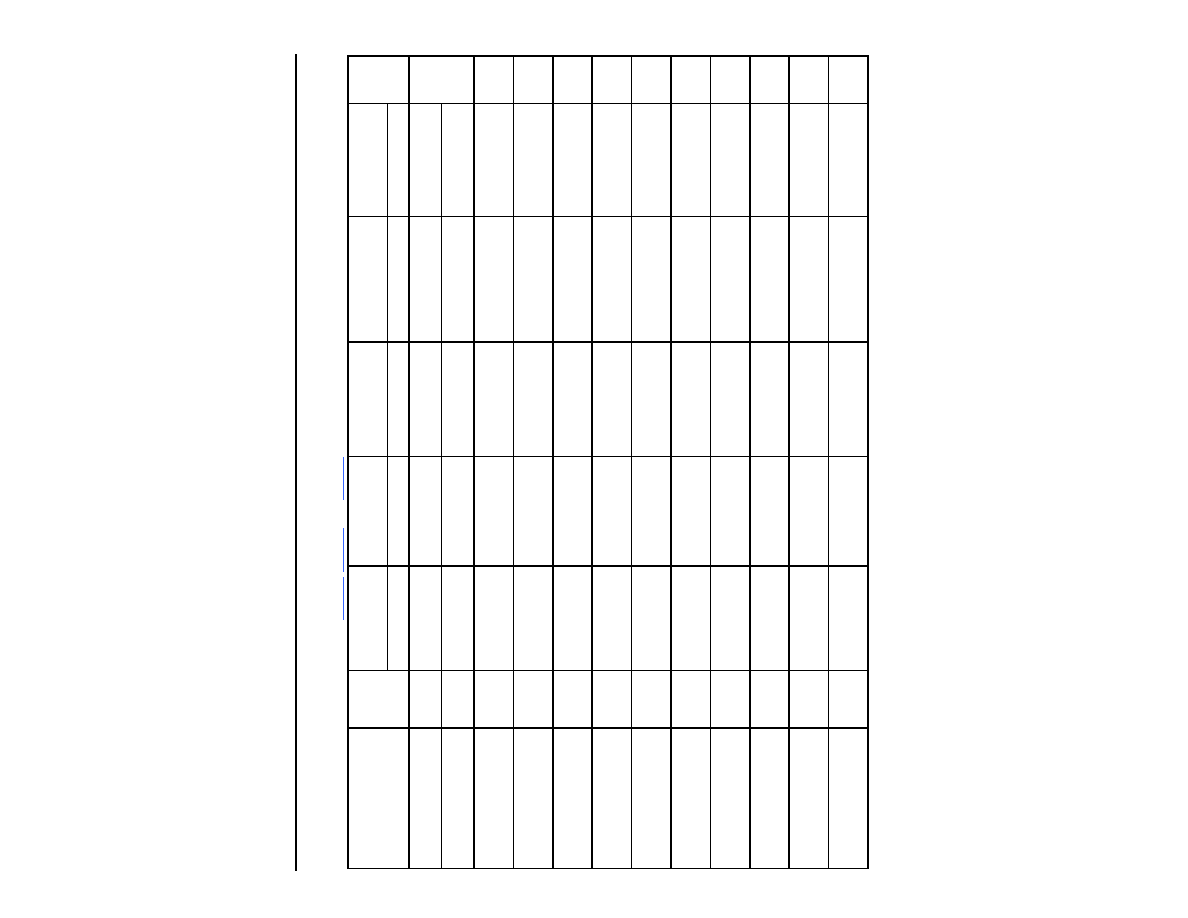

AC CHARACTERISTICS

(V

CC

= 4.5V to 5.5V, T

O

= -40�C to +85�C.) (See

Figure 1

,

Figure 2

, and

Figure 3

.)

1-CYCLE

PAGE MODE 1

2-CYCLE

PAGE MODE 1

4-CYCLE

PAGE MODE 1

PAGE MODE 2

NONPAGE MODE

PARAMETER SYMBOL

MIN

MAX

MIN MAX MIN MAX MIN MAX MIN MAX

UNITS

System Clock External

Oscillator (Note 15)

1/t

CLCL

0 33 0 33 0 33 0

33 0 33

System Clock External Crystal

(Note 15)

1/t

CLCL

1 33 1 33 1 33 1

33 1 33

MHz

ALE Pulse Width (Note 16)

t

LHLL

0.5t

CLCL

- 2

+ t

STC3

t

CLCL

- 2

+ t

STC3

2t

CLCL

- 4

+ t

STC3

1.5t

CLCL

- 5

+ t

STC3

1.5t

CLCL

- 5

+ t

STC3

ns

Port 0 Instruction Address Valid

to ALE Low

t

AVLL

t

CLCL

- 3

0.5t

CLCL

- 3

ns

Port 2 Instruction Address Valid

to ALE Low

t

AVLL2

0.5t

CLCL

- 4

0.5t

CLCL

- 4

1.5t

CLCL

- 4

0.5t

CLCL

- 4

t

CLCL

- 4

ns

Port 0 Data AddressValid to

ALE Low

t

AVLL3

t

CLCL

- 3 +

t

STC3

0.5t

CLCL

- 3

+ t

STC3

ns

Program Address Hold After

ALE Low

t

LLAX

0.5t

CLCL

- 8

1.5t

CLCL

- 8

2.5t

CLCL

- 8

1t

CLCL

- 10

1t

CLCL

- 10

ns

Address Hold after ALE Low

MOVX Write

t

LLAX2

0.5t

CLCL

- 8

+ t

STC4

1.5t

CLCL

- 8

+ t

STC4

2.5t

CLCL

- 8

+ t

STC3

0.5t

CLCL

- 8

+ t

STC2

0.5t

CLCL

- 8

+ t

STC2

ns

Address Hold after ALE Low

MOVX Read

t

LLAX3

0.5t

CLCL

- 8

+ t

STC4

1.5t

CLCL

- 8

+ t

STC4

2.5t

CLCL

- 8

+ t

STC3

0.5t

CLCL

- 8

+ t

STC3

0.5t

CLCL

- 8

+ t

STC2

ns

ALE Low to Valid Instruction In

t

LLIV

2t

CLCL

- 6

2t

CLCL

- 6

ns

ALE Low to

PSEN Low

t

LLPL

1.5t

CLCL

- 6

0.5t

CLCL

- 2

ns

PSEN Pulse Width for Program

Fetch

t

PLPH

t

CLCL

-

5 t

CLCL

- 5

2t

CLCL

- 5

t

CLCL

- 5

2t

CLCL

- 5

ns

DS89C430/DS89C440/DS89C450 Ultra-High-Speed Flash Microcontrollers

5 of 48

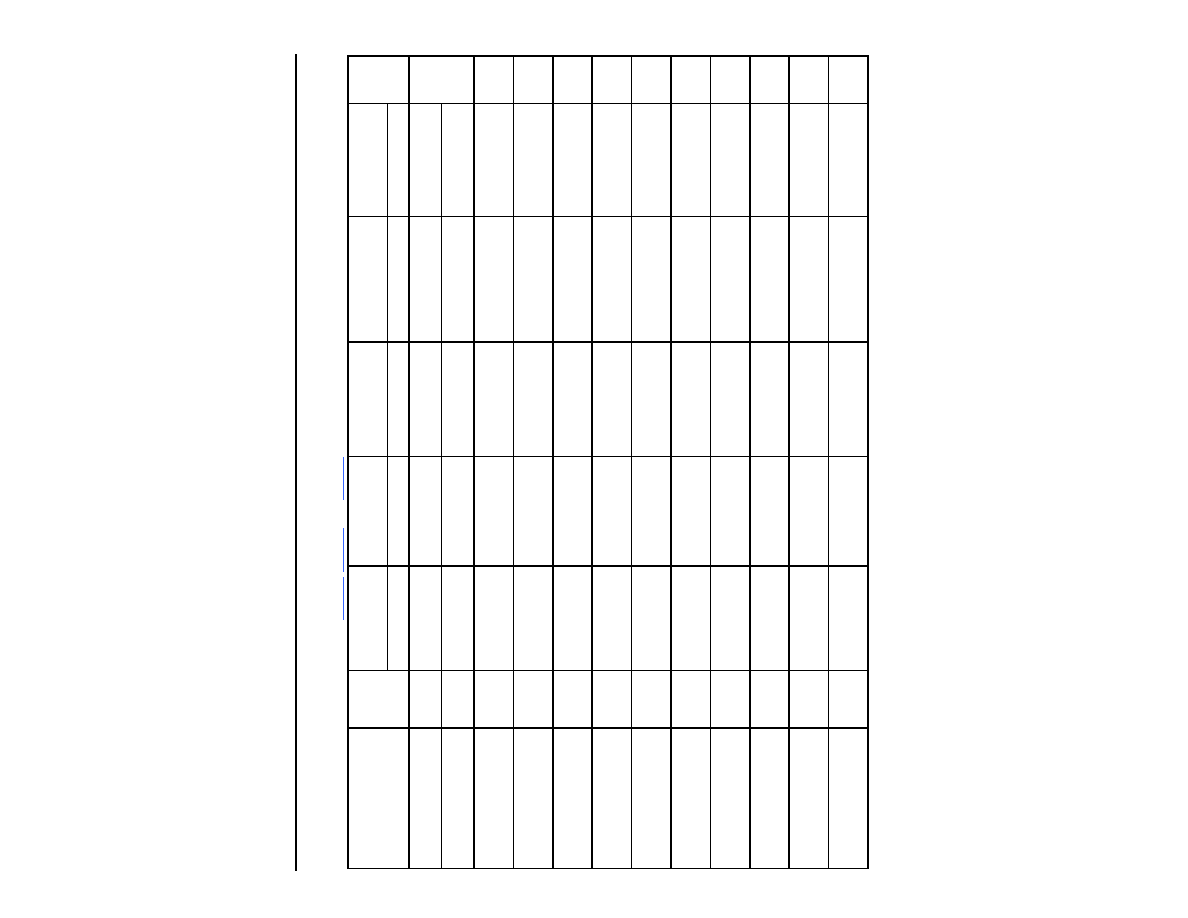

AC CHARACTERISTICS (continued)

(V

CC

= 4.5V to 5.5V, T

O

= -40�C to +85�C.) (See

Figure 1

,

Figure 2

, and

Figure 3

.)

1-CYCLE

PAGE MODE 1

2-CYCLE

PAGE MODE 1

4-CYCLE

PAGE MODE 1

PAGE MODE 2

NONPAGE MODE

PARAMETER SYMBOL

MIN

MAX MIN MAX MIN MAX MIN MAX MIN MAX

UNITS

PSEN Low to Valid Instruction

In

t

PLIV

t

CLCL

- 20

t

CLCL

- 20

2t

CLCL

- 20

t

CLCL

- 20

2t

CLCL

- 20

ns

Input Instruction Hold After

PSEN

t

PXIX

0

0 0 0 0

ns

Input Instruction Float After

PSEN

t

PXIZ

t

CLCL

- 5

t

CLCL

- 5

ns

Port 0 Address to Valid

Instruction In

t

AVIV0

1.5t

CLCL

- 22

3t

CLCL

- 22

ns

Port 2 Address to Valid

Instruction In

t

AVIV2

t

CLCL

- 20

1.5t

CLCL

- 20

2.5t

CLCL

- 20

3t

CLCL

- 20

3.5t

CLCL

- 20

ns

PSEN Low to Port 0 Address

Float

t

PLAZ

0 0

ns

RD Pulse Width (P3.7)

(Note 16)

t

RLRH

t

CLCL

- 5

+ t

STC1

t

CLCL

- 5

+ t

STC1

2t

CLCL

- 5

+ t

STC1

2t

CLCL

- 5

+ t

STC1

2t

CLCL

- 5

+ t

STC1

ns

WR Pulse Width (P3.6)

(Note 16)

t

WLWH

t

CLCL

- 5

+ t

STC1

t

CLCL

- 5

+ t

STC1

2t

CLCL

- 5

+ t

STC1

2t

CLCL

- 5

+ t

STC1

2t

CLCL

- 5

+ t

STC1

ns

RD (P3.7) Low to Valid Data In

(Note 16)

t

RLDV

t

CLCL

- 18

+ t

STC1

t

CLCL

- 18

+ t

STC1

2t

CLCL

- 18

+ t

STC1

2t

CLCL

- 18

+ t

STC1

2t

CLCL

- 18

+ t

STC1

ns

Data Hold After

RD (P3.7)

t

RHDX

0

0 0 0 0

ns

Data Float After

RD (P3.7) t

RHDZ

t

CLCL

- 5

t

CLCL

- 5

ns

MOVX ALE Low to Input Data

Valid (Note 16)

t

LLDV

2t

CLCL

- 8

+ t

STC1

2t

CLCL

- 5

+ t

STC1

ns