PRELIMINARY

This document contains information on a product under development at Advanced Micro Devices. The information

is intended to help you evaluate this product. AMD reserves the right to change or discontinue work on this proposed

product without notice.

Publication# 21510

Rev: E Amendment/0

Issue Date: August 2000

R f

t AMD' W b it (

d

) f

th l t t i f

ti

Am79C973/Am79C975

PCnetTM-FAST III

Single-Chip 10/100 Mbps PCI Ethernet Controller with Integrated PHY

DISTINCTIVE CHARACTERISTICS

s

Single-chip PCI-to-Wire Fast Ethernet controller

-- 32-bit glueless PCI host interface

-- Supports PCI clock frequency from DC to

33 MHz independent of network clock

-- Supports network operation with PCI clock

from 15 MHz to 33 MHz

-- High performance bus mastering

architecture with integrated Direct Memory

Access (DMA) Buffer Management Unit for

low CPU and bus utilization

-- PCI specification revision 2.2 compliant

-- Supports PCI Subsystem/Subvendor ID/

Vendor ID programming through the

EEPROM interface

-- Supports both PCI 5.0 V and 3.3 V signaling

environments

-- Plug and Play compatible

-- Big endian and little endian byte alignments

supported

s

Fully Integrated 10/100 Mbps Physical Layer

Interface (PHY)

-- Conforms to IEEE 802.3 standard for

10BASE-T, 100BASE-TX, and 100BASE-FX

interfaces

-- Integrated 10BASE-T transceiver with on-

chip filtering

-- Fully integrated MLT-3 encoder/decoder for

100BASE-TX

-- Provides a PECL interface for 100BASE-FX

fiber implementations

-- Full-duplex capability for 10BASE-T and

100BASE-TX

-- IEEE 802.3u Auto-Negotiation between 10

Mbps and 100 Mbps, half- and full-duplex op-

eration

s

Dual-speed CSMA/CD (10 Mbps and 100 Mbps)

Media Access Controller (MAC) compliant with

IEEE/ANSI 802.3 and Blue Book Ethernet

standards

s

Supports PC98/PC99 and Wired for

Management baseline specifications

-- Full OnNow support including pattern

matching and link status wake-up events

-- Implements AMD's patented Magic PacketTM

technology for remote wake-up & power-on

-- Magic Packet mode and the physical address

loaded from EEPROM at power up without

requiring PCI clock

-- Supports PCI Bus Power Management

Interface Specification Revision 1.1

-- Supports Advanced Configuration and

Power Interface (ACPI) Specification Version

1.0

-- Supports Network Device Class Power

Management Specification Version 1.0a

s

Serial Management Interface enables remote

alerting of system management events

-- Inter-IC (I

2

C) compliant electrical interface

-- System Management Bus (SMBus)

compliant signaling interface and register

access protocol

-- Optional interrupt pin simplifies software

interface

s

Large independent internal TX and RX FIFOs

-- Programmable FIFO watermarks for both TX

and RX operations

-- RX frame queuing for high latency PCI bus

host operation

-- Programmable allocation of buffer space

between RX and TX queues

s

EEPROM interface supports jumperless design

and provides through-chip programming

-- Supports extensive programmability of

device operation through EEPROM mapping

s

Supports up to 1 megabyte (Mbyte) optional

Boot PROM and Flash for diskless node

application

s

Extensive programmable internal/external

loopback capabilities

s

Extensive programmable LED status support

2

Am79C973/Am79C975

P R E L I M I N A R Y

s

Look-Ahead Packet Processing (LAPP) data

handling technique reduces system overhead

by allowing protocol analysis to begin before

the end of a receive frame

s

Includes Programmable Inter Packet Gap (IPG)

to address less network aggressive MAC

controllers

s

Offers the Modified Back-Off algorithm to

address the Ethernet Capture Effect

s

IEEE 1149.1-compliant JTAG Boundary Scan

test access port interface and NAND tree test

mode for board-level production connectivity

test

s

Compatible with the existing PCnet Family

driver/diagnostic software

s

Software compatible with AMD PCnet Family

and LANCETM/C-LANCETM register and

descriptor architecture

s

Available in 160-pin PQFP and 176-pin TQFP

packages

s

Advanced +3.3 V CMOS process technology for

low power operation

GENERAL DESCRIPTION

The Am79C973 and Am79C975 controllers are single-

chip 32-bit full- duplex, 10/100-Megabit per second

(Mbps) fully integrated PCI-to-Wire Fast Ethernet sys-

tem solution, designed to address high-performance

system application requirements. They are flexible bus

mastering device that can be used in any application,

including network-ready PCs and bridge/router de-

signs. The bus master architecture provides high data

throughput and low CPU and system bus utilization.

The Am79C973 and Am79C975 controllers are fabri-

cated with advanced low-power 3.3-V CMOS process

to provide low operating current for power sensitive ap-

plications.

The third generation Am79C973 and Am79C975 Fast

Ethernet controllers also have several enhancements

ove r t h e i r p r e d e c e s s o r s, t h e A m 7 9 C 9 7 1 a n d

Am79C972 devices. Besides integrating the complete

10/100 Physical Layer (PHY) interface, they further re-

duce system implementation cost by integrating the

SRAM buffers on chip.

The Am79C973 and Am79C975 controllers contain 12-

kilobyte (Kbyte) buffers, the largest of their class in 10/

100 Mbps Ethernet controllers. The large internal buff-

ers are fully programmable between the RX and TX

queues for optimal performance.

The Am79C973 and Am79C975 controllers are also

compliant with PC98/PC99 and Wired for Management

specifications. They fully support Microsoft's OnNow

and ACPI specifications, which are backward compati-

ble with Magic Packet technology and compliant with

the PCI Bus Power Management Interface Specifica-

tion by supporting the four power management states

(D0, D1, D2, and D3), the optional PME pin, and the

necessary configuration and data registers.

The Am79C973 and Am79C975 controllers are com-

plete Ethernet nodes integrated into a single VLSI de-

vice. It contains a bus interface unit, a Direct Memory

Access (DMA) Buffer Management Unit, an ISO/IEC

8802-3 (IEEE 802.3)- compliant Media Access Control-

ler (MAC), a large Transmit FIFO and a large Receive

FIFO, and an IEEE 802.3-compliant 10/100 Mbps PHY.

The integrated 10/100 PHY unit of the Am79C973 and

Am79C975 controllers implement the complete physi-

cal layer for 10BASE-T and the Physical Coding Sub-

layer (PCS), Physical Medium Attachment (PMA), and

Physical Medium Dependent (PMD) functionality for

100BASE-TX, including MLT-3 encoding/decoding. It

also supports 100BASE-FX operation by providing a

Pseudo-ECL (PECL) interface for direct connection to

a fiber optic transceiver module. The internal 10/100

PHY implements Auto-Negotiation for twisted-pair

(10T/100TX) operation by using a modified 10BASE-T

link integrity test pulse sequence as defined in the

IEEE 802.3u specification. The Auto-Negotiation func-

tion automatically configures the controller to operate

at the maximum performance level supported across

the network link.

The Am79C975 controller also implements a Serial

Management Interface in addition to the advanced

management features offered with the Am79C973 con-

troller. The Serial Management Interface is based on

the industry standard Inter-IC (I

2

C) and System Man-

agement Bus (SMBus) specifications and enables a

system to communicate with another network station

for remote monitoring and alerting of local system man-

agement parameters and events. This simple yet pow-

erful Serial Management Interface is capable of

communicating within the system and over the network

during normal operation or in low-power modes, even if

the device is not initialized or set up for transmit or re-

ceive operation by the network software driver.

The 32-bit multiplexed bus interface unit provides a di-

rect interface to the PCI local bus, simplifying the

design of an Ethernet node in a PC system. The

Am79C973 and Am79C975 controllers provide the

complete interface to an Expansion ROM or Flash de-

vice allowing add-on card designs with only a single

load per PCI bus interface pin. With their built-in sup-

port for both little and big endian byte alignment, the

Am79C973/Am79C975

3

P R E L I M I N A R Y

controllers also address non-PC applications. The

Am79C973 and Am79C975 controllers' advanced

CMOS design allows the bus interface to be connected

to either a +5-V or a +3.3-V signaling environment. A

compliant IEEE 1149.1 JTAG test interface for board-

level testing is also provided, as well as a NAND tree

test structure for those systems that cannot support the

JTAG interface.

The Am79C973 and Am79C975 controllers support

auto-configuration in the PCI configuration space. Ad-

ditional Am79C973 and Am79C975 controller configu-

ration parameters, including the unique IEEE physical

address, can be read from an external non-volatile

memory (EEPROM) immediately following system re-

set.

In addition, the Am79C973 and Am79C975 controllers

provide programmable on-chip LED drivers for trans-

mit, receive, collision, link integrity, Magic Packet sta-

tus, activity, link active, address match, full-duplex, 10

Mbps or 100 Mbps, or jabber status.

The Am79C973 and Am79C975 controllers are regis-

ter compatible with the LANCETM (Am7990) Ethernet

controller, the C-LANCETM (Am79C90) Ethernet con-

troller, and all Ethernet controllers in the PCnetTM Fam-

ily, except ILACCTM (Am79C900), including the PCnet-

ISATM (Am79C960), PCnet-ISA+TM (Am79C961),

P C n e t - I S A I I TM ( A m 7 9 C 9 6 1 A ) , P C n e t - 3 2 TM

( A m 7 9 C 9 6 5 ) , P C n e t - P C I TM ( A m 7 9 C 9 7 0 ) ,

P C n e t -PC I II TM (A m 7 9 C9 7 0 A ), P Cn e t - FAST TM

(Am79C971), and PCnet-FAST+TM (Am79C972). The

Buffer Management Unit supports the LANCE and

PCnet descriptor software models.

The Am79C973 and Am79C975 controllers are ideally

suited for LAN on the motherboard, network adapter

card, and embedded designs. It is available in a 160-

pin Plastic Quad Flat Pack (PQFP) package and also in

a 176-pin Thin Quad Flat Pack (TQFP) package for

form factor sensitive designs.

4

Am79C973/Am79C975

P R E L I M I N A R Y

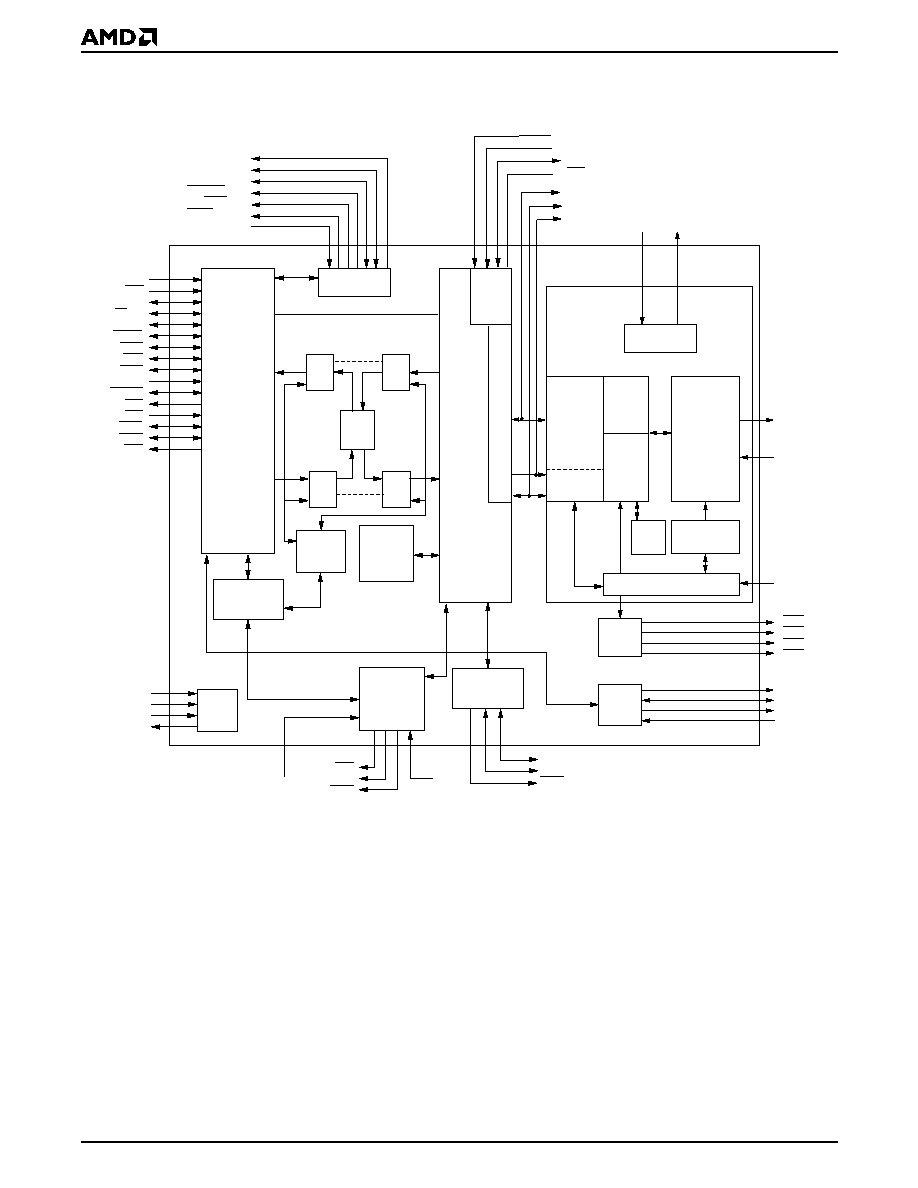

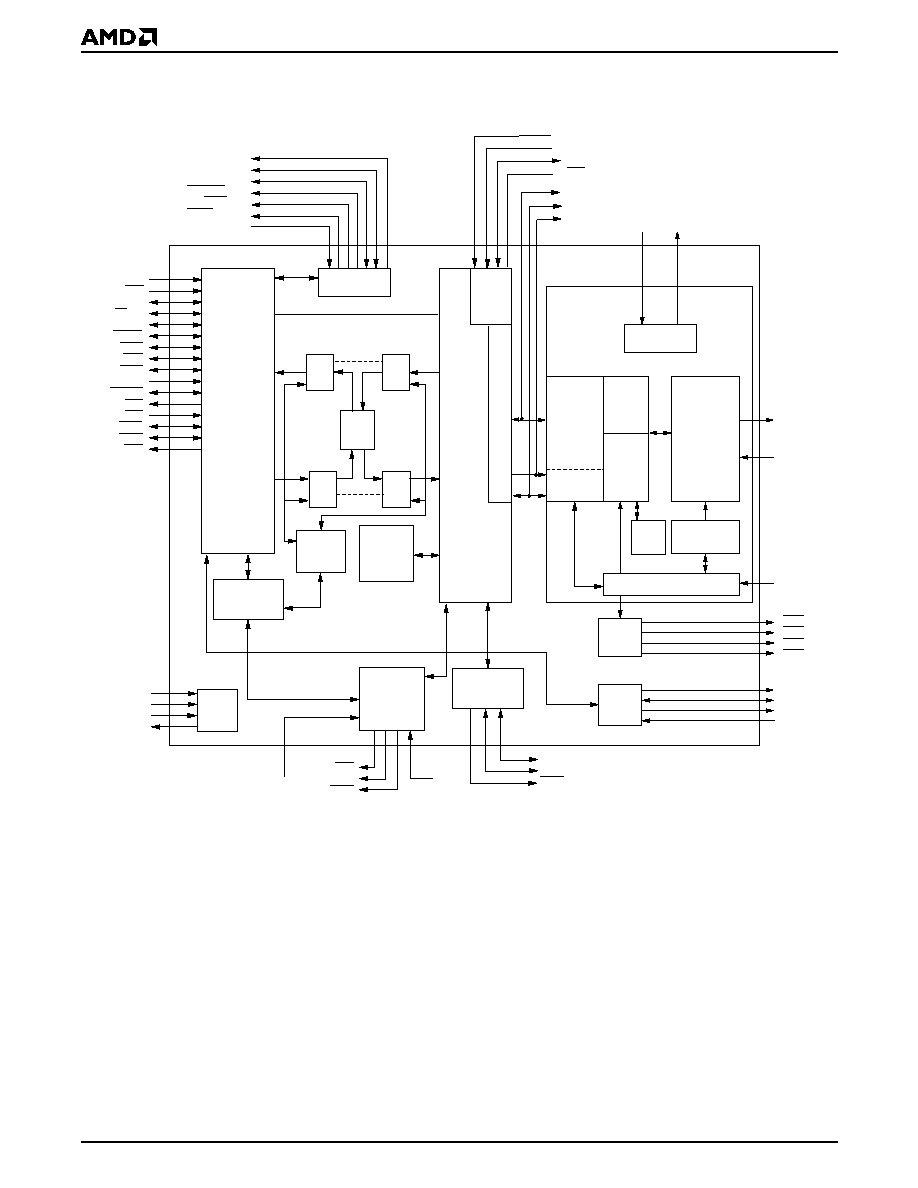

BLOCK DIAGRAM

CLK

RST

AD[31:0]

C/BE[3:0]

PAR

FRAME

TRDY

IRDY

STOP

IDSEL

DEVSEL

REQ

GNT

PERR

SERR

INTA

PCI Bus

Interface

Unit

Expansion Bus

Interface

Bus

Rcv

FIFO

Bus

Xmt

FIFO

FIFO

Control

Network

Port

Manager

MAC

Rcv

FIFO

12K

SRAM

MAC

Xmt

FIFO

JTAG

Port

Control

OnNow

Power

Management

Unit

802.3

MAC

Core

93C46

EEPROM

Interface

LED

Control

Buffer

Management

Unit

PME

RWU

WUMI

PG

TCK

TMS

TDI

TDO

EBUA_EBA[7:0]

EBDA[15:8]

EBD[7:0]

EROMCS

AS_EBOE

EBWE

EBCLK

Transmit

Block

MII

Interface

MII

Management

MDC

MDIO

Receive

Block

PHY Control

Link

Monitor

Auto

Negotiation

10/100 PHY Core

MLT3

(100 BASE-TX)

PECL

(100 BASE-FX)

10 BASE-T

TX�

SDI�

RX�

XTAL1

XTAL2

LED0

LED1

LED2

LED3

EECS

EESK

EEDI

EEDO

Clock

Reference

MII

EADI

Serial

Management

Interface Unit

MCLOCK

MDATA

MIRQ

RXD[3:0],TXD[3:0]

MDIO

MDC

SFBD

EAR

MIIRXFRTGE

MIIRXFRTGD

VAUXDET

21510D-1

Am79C973/Am79C975

5

P R E L I M I N A R Y

DISTINCTIVE CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

GENERAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

BLOCK DIAGRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

TABLE OF CONTENTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

LIST OF FIGURES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

LIST OF TABLES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

RELATED AMD PRODUCTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

CONNECTION DIAGRAM (PQR160) - AM79C973 . . . . . . . . . . . . . . . . . . . . . . . . . . 18

CONNECTION DIAGRAM (PQL176) AM79C973 . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

CONNECTION DIAGRAM (PQR160) - AM79C975 . . . . . . . . . . . . . . . . . . . . . . . . . . 20

CONNECTION DIAGRAM (PQL176) - AM79C975 . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

PIN DESIGNATIONS (PQR160) (Am79C973/Am79C975) . . . . . . . . . . . . . . . . . . . . 22

Listed By Pin Number . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

PIN DESIGNATIONS (PQL176) (Am79C973/Am79C975) . . . . . . . . . . . . . . . . . . . . . 23

Listed By Pin Number . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

PIN DESIGNATIONS (PQR160, PQL176) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Listed By Group . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

PIN DESIGNATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Listed By Group . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

PIN DESIGNATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Listed By Driver Type . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

ORDERING INFORMATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

PIN DESCRIPTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

PCI Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Board Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

EEPROM Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Expansion Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Media Independent Interface (MII) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

External Address Detection Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

IEEE 1149.1 (1990) Test Access Port Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Network Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Clock Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Serial Management Interface (SMI) (Am79C975 only) . . . . . . . . . . . . . . . . . . . . . . 37

Power Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

BASIC FUNCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

System Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Software Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Network Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Serial Management Interface (Am79C975) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

MII Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

DETAILED FUNCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Slave Bus Interface Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Slave Configuration Transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Slave I/O Transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Expansion ROM Transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Slave Cycle Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Parity Error Response . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Master Bus Interface Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

TABLE OF CONTENTS