Publication# 19436

Rev: E Amendment/0

Issue Date:

June 2000

Am79C970A

PCnetTM-PCI II Single-Chip Full-Duplex Ethernet

Controller for PCI Local Bus Product

DISTINCTIVE CHARACTERISTICS

n Single-chip Ethernet controller for the

Peripheral Component Interconnect (PCI) local

bus

n Supports ISO 8802-3 (IEEE/ANSI 802.3) and

Ethernet standards

n Direct interface to the PCI local bus (Revision

2.0 compliant)

n High-performance 32-bit Bus Master

architecture with integrated DMA buffer

management unit for low CPU and bus

utilization

n Software-compatible with AMD PCnet family,

LANCE/C-LANCE, and Am79C900 ILACC

register and descriptor architecture

n Compatible with PCnet family driver software

n Full-duplex operation for increased network

bandwidth

n Big endian and little endian byte alignments

supported

n 3.3 V/5 V signaling for PCI bus interface

n Low-power CMOS design with two sleep modes

allows reduced power consumption for critical

battery-powered applications and Green PCs

n Integrated Magic PacketTM support for remote

wake up of Green PCs

n Individual 272-byte transmit and 256-byte

receive FIFOs provide frame buffering for

increased system latency and support the

following features:

-- Automatic retransmission with no FIFO reload

-- Automatic receive stripping and transmit

padding (individually programmable)

-- Automatic runt frame rejection

-- Automatic selection of received collision frames

n Microwire EEPROM interface supports

jumperless design and provides through-chip

programming

n Supports optional Boot PROM for diskless node

applications

n Look-Ahead Packet Processing (LAPP) data

handling technique reduces system overhead

by allowing protocol analysis to begin before

end of receive frame

n Integrated Manchester encoder/decoder

n Provides integrated attachment unit interface

(AUI) and 10BASE-T transceiver with automatic

port selection

n Automatic twisted-pair receive polarity

detection and automatic correction of the

receive polarity

n Optional byte padding to long-word boundary

on receive

n Dynamic transmit FCS generation

programmable on a frame-by-frame basis

n Internal/external loopback capabilities

n Supports the following types of network

interfaces:

-- AUI to external 10BASE-2, 10BASE-5,

10BASE-T, or 10BASE-F MAU

-- Internal 10BASE-T transceiver with Smart

Squelch to twisted-pair medium

n JTAG Boundary Scan (IEEE 1149.1) test access

port interface and NAND Tree test mode for

board-level production connectivity test

n Supports external address detection interface

(EADI)

n 4 programmable LEDs for status indication

n 132-pin PQFP and 144-pin TQFP packages

n Support for operation in industrial temperature

range (40°C to +85°C) available in both

packages

GENERAL DESCRIPTION

The 32-bit PCnet-PCI II single-chip full-duplex Ethernet

controller is a highly integrated Ethernet system solu-

tion designed to address high-performance system ap-

plication requirements. It is a flexible bus-mastering

device that can be used in any application, including

network-ready PCs, printers, fax modems, and

bridge/router designs. The bus-master architecture

provides high data throughput in the system and low

2

Am79C970A

CPU and system bus utilization. The PCnet-PCI II con-

troller is fabricated with AMD's advanced low-power

CMOS process to provide low operating and standby

current for power-sensitive applications.

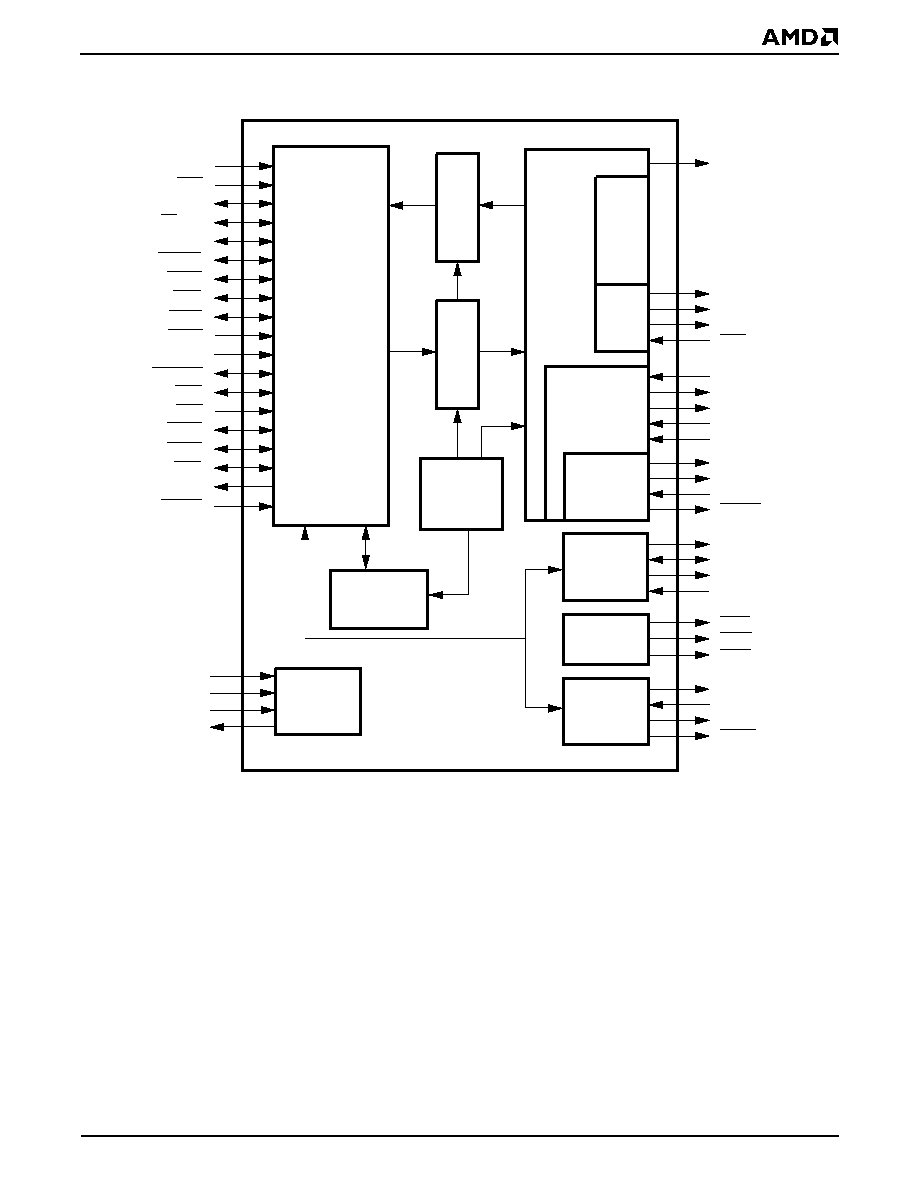

The PCnet-PCI II controller is a complete Ethernet

node integrated into a single VLSI device. It contains a

bus interface unit, a DMA buffer management unit, an

IEEE 802.3-compliant media access control (MAC)

function, individual 272-byte transmit and 256-byte re-

ceive FIFOs, an IEEE 802.3-compliant attachment unit

interface (AUI) and twisted-pair transceiver medium at-

tachment unit (10BASE-T MAU) that can both operate

in either half-duplex or full-duplex mode.

The PCnet-PCI II controller is register-compatible with

th e L ANC E (Am 79 90) Eth er n et co nt rolle r, th e

C-LANCE (Am79C90) Ethernet controller, the ILACC

(Am79C900) Ethernet controller, and all Ethernet con-

trollers in the PCnet family, including the PCnet-ISA

controller (Am79C960), PCnet-ISA+ controller

(Am79C961), PCnet-ISA II controller (Am79C961A),

PCnet-32 controller (Am79C965), PCnet-PCI control-

ler (Am79970), and the PCnet-SCSI controller

(Am79C974). The buffer management unit supports

the C-LANCE, ILACC, and PCnet descriptor software

models. The PCnet-PCI II controller is software com-

patible with the Novell® NE2100 and NE1500 Ethernet

adapter card architectures.

The 32-bit multiplexed bus interface unit provides a di-

rect interface to PCI local bus applications, simplifying

the design of an Ethernet node in a PC system. The

PCnet-PCI II controller provides the complete interface

to an expansion ROM, allowing add-on card designs

with only a single load per PCI bus interface pin. With

its built-in support for both little and big endian byte

alignment, this controller also addresses proprietary

non-PC applications. The PCnet-PCI II controller's ad-

vanced CMOS design allows the bus interface to be

connected to either a 5 V or a 3.3 V signaling environ-

ment. Both NAND Tree and JTAG test interfaces are

provided.

The PCnet-PCI II controller supports automatic config-

uration in the PCI configuration space. Additional PC-

net-PCI II configuration parameters, including the

unique IEEE physical address, can be read from an ex-

ternal non-volatile memory (microwire EEPROM) im-

mediately following system reset.

The controller has the capability to automatically select

either the AUI port or the twisted-pair transceiver. Only

one interface is active at any one time. Both network in-

terfaces can be programmed to operate in either half-

duplex or full-duplex mode. The individual transmit and

receive FIFOs optimize system overhead, providing

sufficient latency during frame transmission and recep-

tion, and minimizing intervention during normal net-

work error recovery. The integrated Manchester

encoder/decoder (MENDEC) eliminates the need for

an external serial interface adapter (SIA) in the system.

In addition, the device provides programmable on-chip

LED drivers for transmit, receive, collision, receive po-

larity, link integrity, activity, or jabber status. The PC-

net-PCI II controller also provides an external address

detection interface (EADI) to allow fast external hard-

ware address filtering in internetworking applications.

For power-sensitive applications where low standby

current is desired, the device incorporates two sleep

functions to reduce overall system power consumption,

excellent for notebooks and Green PCs. In conjunction

with these low power modes, the PCnet-PCI II control-

ler also has integrated functions to support Magic

Packet, an inexpensive technology that allows remote

wakeup of Green PCs.

With the rise of embedded networking applications op-

erating in harsh environments where temperatures

may exceed the normal commercial temperature win-

dow (0°C to +70°C), an industrial temperature (40°C

to +85°C) version is available in both the 132-pin PQFP

and the 144-pin TQFP package. The industrial temper-

ature version of the PCnet-PCI II Ethernet controller is

characterized across the industrial temperature range

(40°C to +85°C) within the published power supply

specification (4.75 V to 5.25 V; i.e., ±5% V

CC

).

4

Am79C970A

TABLE OF CONTENTS

DISTINCTIVE CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

GENERAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

BLOCK DIAGRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

CONNECTION DIAGRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

ORDERING INFORMATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

PIN DESIGNATIONS 132 PIN PQFP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

LISTED BY PIN NUMBER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

LISTED BY GROUP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

LISTED BY GROUP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

LISTED BY PIN NUMBER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

LISTED BY GROUP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

LISTED BY GROUP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

LISTED BY DRIVER TYPE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

PIN DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

PCI INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

BOARD INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

MICROWIRE EEPROM INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

EXPANSION ROM INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

ATTACHMENT UNIT INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

TWISTED PAIR INTERFACE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

EXTERNAL ADDRESS DETECTION INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

IEEE 1149.1 TEST ACCESS PORT INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

TEST INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

POWER SUPPLY PINS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

BASIC FUNCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

SYSTEM BUS INTERFACE FUNCTION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

SOFTWARE INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

NETWORK INTERFACES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

DETAILED FUNCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

SLAVE BUS INTERFACE UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

SLAVE CONFIGURATION TRANSFERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

SLAVE I/O TRANSFERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

EXPANSION ROM TRANSFERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

EXCLUSIVE ACCESS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

SLAVE CYCLE TERMINATION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

PARITY ERROR RESPONSE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

MASTER BUS INTERFACE UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

BUS ACQUISITION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

BUS MASTER DMA TRANSFERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

BASIC NON-BURST READ TRANSFER. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

BASIC BURST READ TRANSFER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

BASIC NON-BURST WRITE TRANSFER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

BASIC BURST WRITE TRANSFER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

TARGET INITIATED TERMINATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

DISCONNECT WITH DATA TRANSFER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

DISCONNECT WITHOUT DATA TRANSFER. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

TARGET ABORT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

MASTER INITIATED TERMINATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

PREEMPTION DURING NON-BURST TRANSACTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

PREEMPTION DURING BURST TRANSACTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Am79C970A

5

MASTER ABORT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

PARITY ERROR RESPONSE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

ADVANCED PARITY ERROR HANDLING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

INITIALIZATION BLOCK DMA TRANSFERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

DESCRIPTOR DMA TRANSFERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

FIFO DMA TRANSFERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

NON-BURST FIFO DMA TRANSFERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

BURST FIFO DMA TRANSFERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

BUFFER MANAGEMENT UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

INITIALIZATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

RE-INITIALIZATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

SUSPEND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

BUFFER MANAGEMENT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

DESCRIPTOR RINGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

POLLING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

TRANSMIT DESCRIPTOR TABLE ENTRY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

RECEIVE DESCRIPTOR TABLE ENTRY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

MEDIA ACCESS CONTROL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

TRANSMIT AND RECEIVE MESSAGE DATA ENCAPSULATION . . . . . . . . . . . . . . . . . . . . . . . . . . 69

FRAMING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

DESTINATION ADDRESS HANDLING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

ERROR DETECTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

MEDIA ACCESS MANAGEMENT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

MEDIUM ALLOCATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

COLLISION HANDLING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

TRANSMIT OPERATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

TRANSMIT FUNCTION PROGRAMMING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

AUTOMATIC PAD GENERATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

TRANSMIT FCS GENERATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

TRANSMIT EXCEPTION CONDITIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

LOSS OF CARRIER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

LATE COLLISION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

SQE TEST ERROR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

RECEIVE OPERATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

RECEIVE FUNCTION PROGRAMMING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

ADDRESS MATCHING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

AUTOMATIC PAD STRIPPING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

RECEIVE FCS CHECKING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

RECEIVE EXCEPTION CONDITIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

LOOPBACK OPERATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

AUI LOOPBACK MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

T-MAU LOOPBACK MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

MISCELLANEOUS LOOPBACK FEATURES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

MAGIC PACKET MODE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

MANCHESTER ENCODER/DECODER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

EXTERNAL CRYSTAL CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

EXTERNAL CLOCK DRIVE CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

MENDEC TRANSMIT PATH . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

TRANSMITTER TIMING AND OPERATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

RECEIVER PATH . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

INPUT SIGNAL CONDITIONING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

CLOCK ACQUISITION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

PLL TRACKING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

CARRIER TRACKING AND END OF MESSAGE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

DATA DECODING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

JITTER TOLERANCE DEFINITION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81