| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: AK4382A | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

ASAHI KASEI

[AK4382A]

MS0071-J-01

2002/2

- 1 -

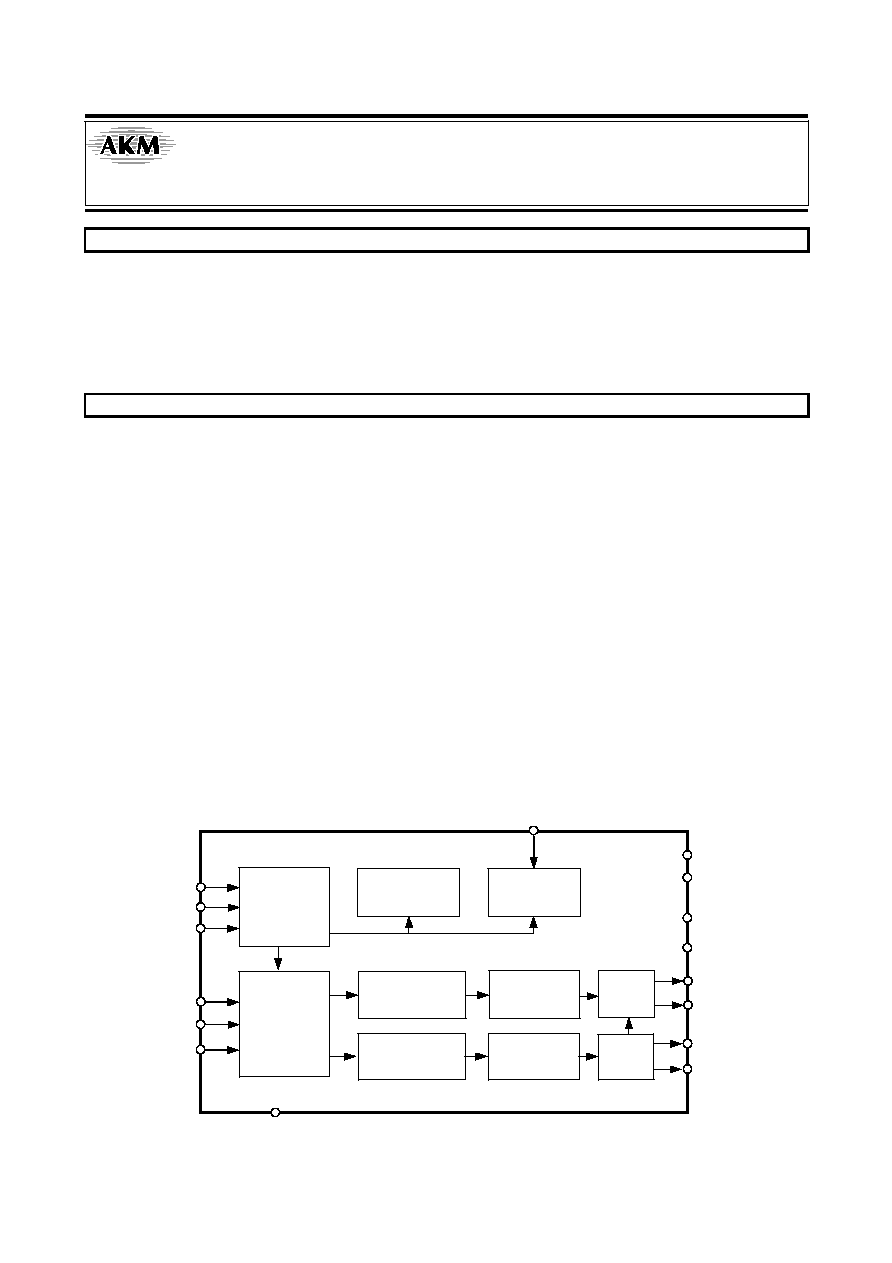

AK4382A

24

DAC

(SCF)

192kHz

DVD, AC-3

AK4382A

16pin TSSOP

o

: 8kHz

192kHz

o

128

o

64

2

o

32

4

o

24

8

FIR

o

SCF

o

(32kHz, 44.1kHz, 48kHz

)

o

o

ATT (256

)

o

I/F

: 24

, 24/20/16

, I

2

S

o

: 256fs, 384fs, 512fs or 768fs

128fs, 192fs, 256fs or 384fs

2

128fs or 192fs

4

o

THD+N: -94dB

o

Dynamic Range: 112dB

o

o

: 4.75

5.25V

o

: 16pin TSSOP (6.4mm x 5.0mm)

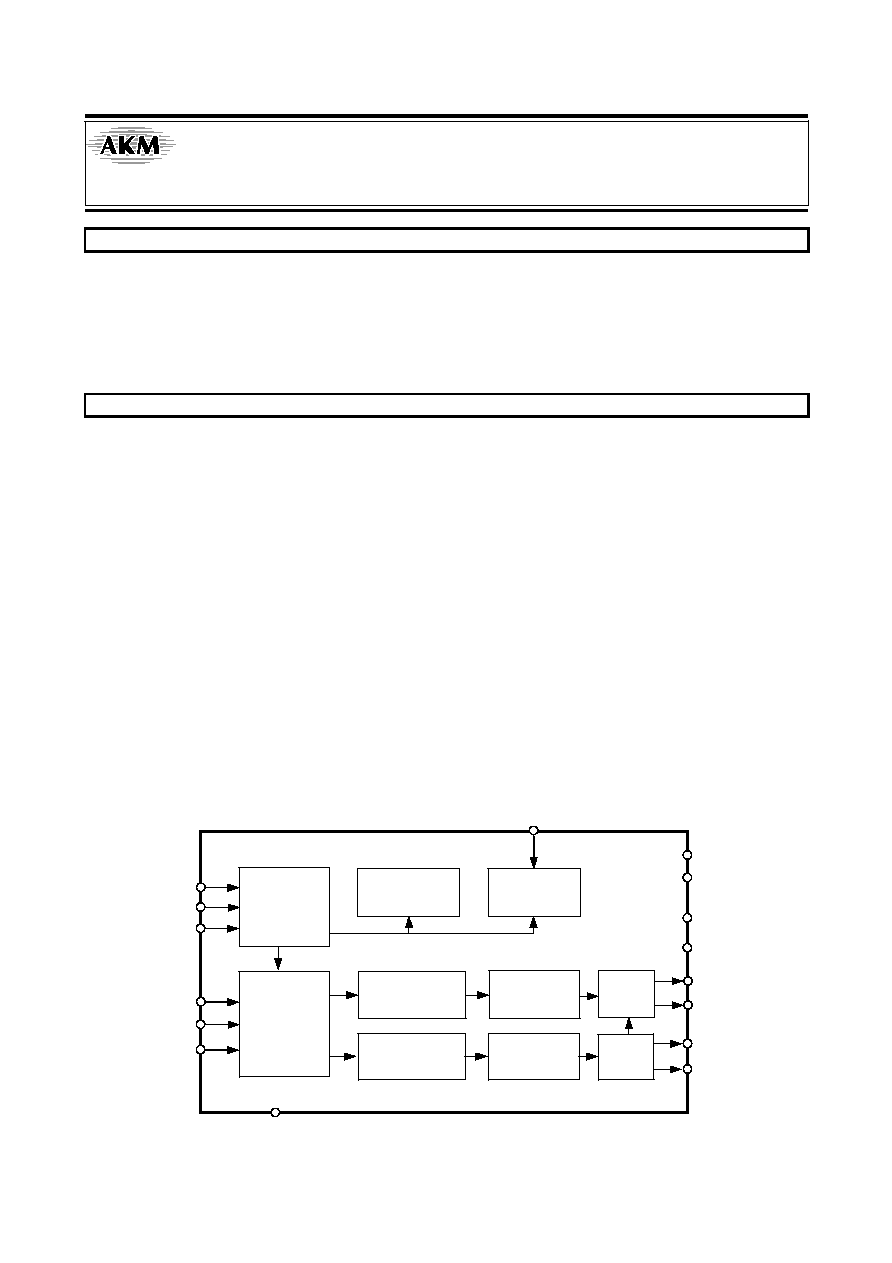

LRCK

BICK

SDTI

Audio

Data

Interface

MCLK

PDN

Modulator

AOUTL+

8X

Interpolator

SCF

AOUTR+

SCF

VDD

VSS

De-emphasis

Control

µP

Interface

Clock

Divider

CSN

CCLK

CDTI

DZFR

Modulator

8X

Interpolator

AOUTL-

AOUTR-

DZFL

112dB 192kHz 24-Bit 2ch

DAC

AK4382A

ASAHI KASEI

[AK4382A]

MS0071-J-01

2002/2

- 2 -

n

AK4382AVT -40

+85

∞

C 16pin TSSOP (0.65mm pitch)

AKD4382 AK4382A

n

1

MCLK

LRCK

BICK

CSN

CCLK

CDTI

Top

View

2

3

4

5

6

7

8

DZFL

DZFR

VSS

VDD

AOUTL+

AOUTL-

AOUTR+

AOUTR-

16

15

14

13

12

11

10

9

PDN

SDTI

No.

Pin Name

I/O

Function

1

MCLK

I

Master Clock Input Pin

An external TTL clock should be input on this pin.

2

BICK

I

Audio Serial Data Clock Pin

3

SDTI

I

Audio Serial Data Input Pin

4

LRCK

I

L/R Clock Pin

5

PDN

I

Power-Down Mode Pin

When at "L", the AK4382A is in the power-down mode and is held in reset.

The AK4382A should always be reset upon power-up.

6

CSN

I

Chip Select Pin

7

CCLK

I

Control Data Input Pin

8

CDTI

I

Control Data Input Pin

9

AOUTR-

O

Rch Negative Analog Output Pin

10

AOUTR+

O

Rch Positive Analog Output Pin

11

AOUTL-

O

Lch Negative Analog Output Pin

12

AOUTL+

O

Lch Positive Analog Output Pin

13

VSS

-

Ground Pin

14

VDD

-

Power Supply Pin

15

DZFR

O

Rch Data Zero Input Detect Pin

16

DZFL

O

Lch Data Zero Input Detect Pin

Note: All input pins should not be left floating.

ASAHI KASEI

[AK4382A]

MS0071-J-01

2002/2

- 3 -

(VSS=0V; Note 1)

Parameter

Symbol

min

max

Units

Power Supply

VDD

-0.3

6.0

V

Input Current (any pins except for supplies)

IIN

-

±

10

mA

Input Voltage

VIND

-0.3

VDD+0.3

V

Ambient Operating Temperature

Ta

-40

85

∞

C

Storage Temperature

Tstg

-65

150

∞

C

Note: 1.

:

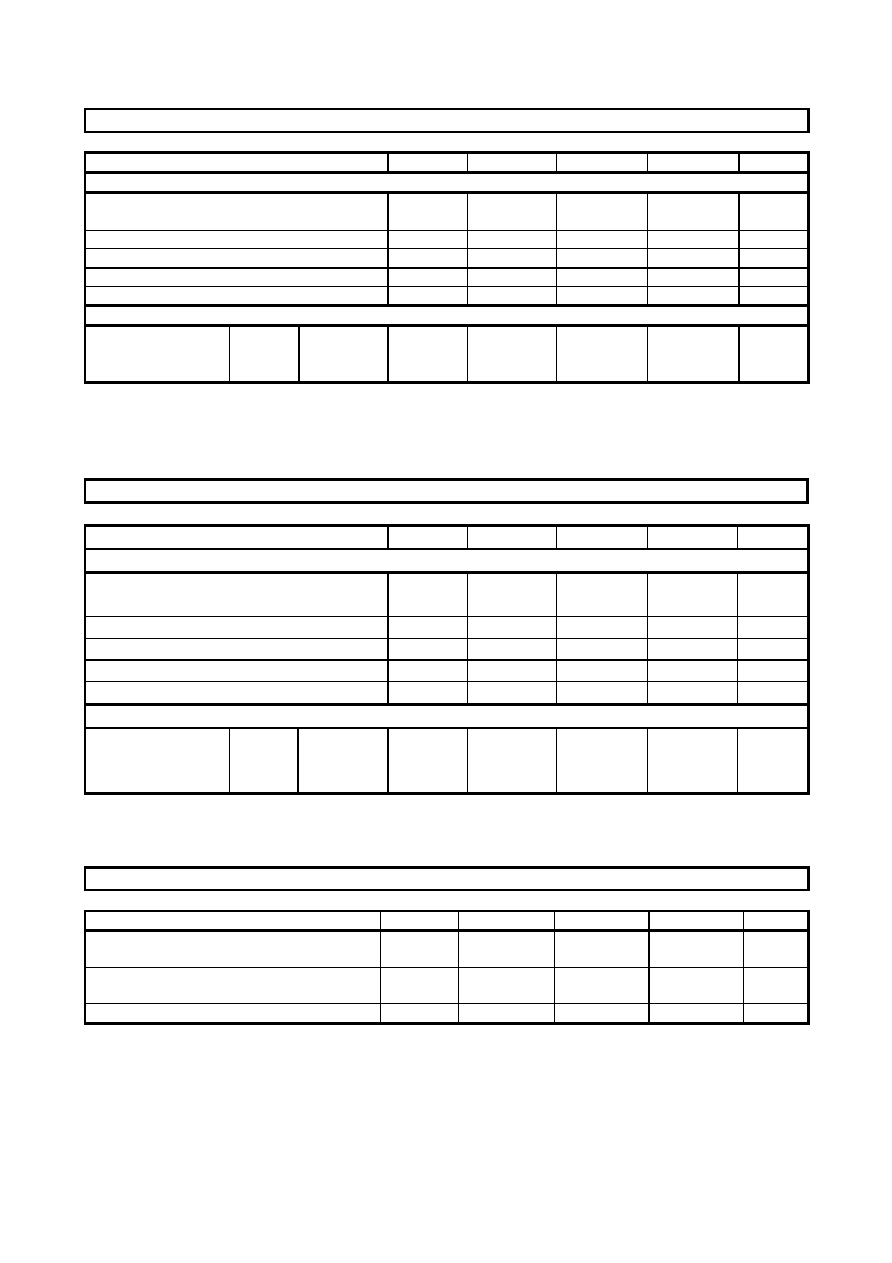

(VSS=0V; Note 1)

Parameter

Symbol

min

typ

max

Units

Power Supply

VDD

4.75

5.0

5.25

V

:

ASAHI KASEI

[AK4382A]

MS0071-J-01

2002/2

- 4 -

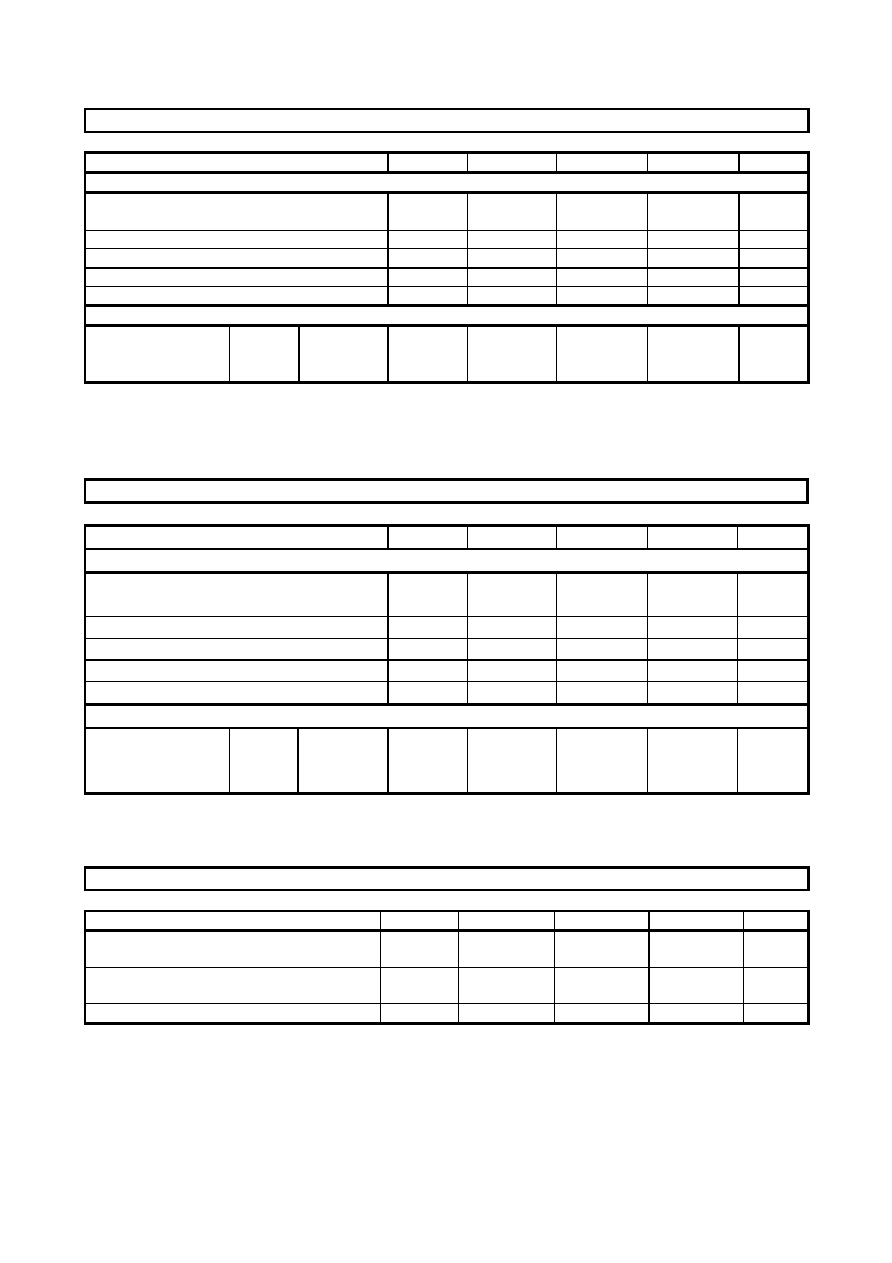

(Ta = 25

∞

C; VDD = 5.0V; fs = 44.1kHz; BICK = 64fs; Signal Frequency = 1kHz;

24bit Input Data; Measurement frequency = 20Hz

20kHz; R

L

2k

)

Parameter

min

typ

max

Units

Resolution

24

Bits

Dynamic Characteristics (Note 3)

fs=44.1kHz

BW=20kHz

0dBFS

-60dBFS

-94

-48

-86

-

dB

dB

fs=96kHz

BW=40kHz

0dBFS

-60dBFS

-92

-45

-84

-

dB

dB

THD+N

fs=192kHz

BW=40kHz

0dBFS

-60dBFS

-92

-45

-

-

dB

dB

Dynamic Range (-60dBFS with A-weighted) (Note 4)

102

112

dB

S/N (A-weighted) (Note 5)

102

112

dB

Interchannel Isolation (1kHz)

90

110

dB

Interchannel Gain Mismatch

0.2

0.5

dB

DC Accuracy

Gain Drift

100

-

ppm/

∞

C

Output Voltage (Note 6)

±

2.55

±

2.75

±

2.95

Vpp

Load Resistance (Note 7)

2

k

Power Supplies

Power Supply Current (VDD)

Normal Operation (PDN = "H", fs

96kHz)

Normal Operation (PDN = "H", fs=192kHz)

Power-Down Mode (PDN = "L") (Note 8)

20

25

10

34

42

100

mA

mA

µA

Notes: 3. Audio Precision (System Two)

4. 100dB at 16bit data.

5. S/N

6. (0dB) VDD

AOUT (typ.@0dB) = (AOUT+) - (AOUT-) =

±

2.75Vpp◊VDD/5

7. ACDCk

8. (MCLK, BICK, LRCK) VDD VSS

ASAHI KASEI

[AK4382A]

MS0071-J-01

2002/2

- 5 -

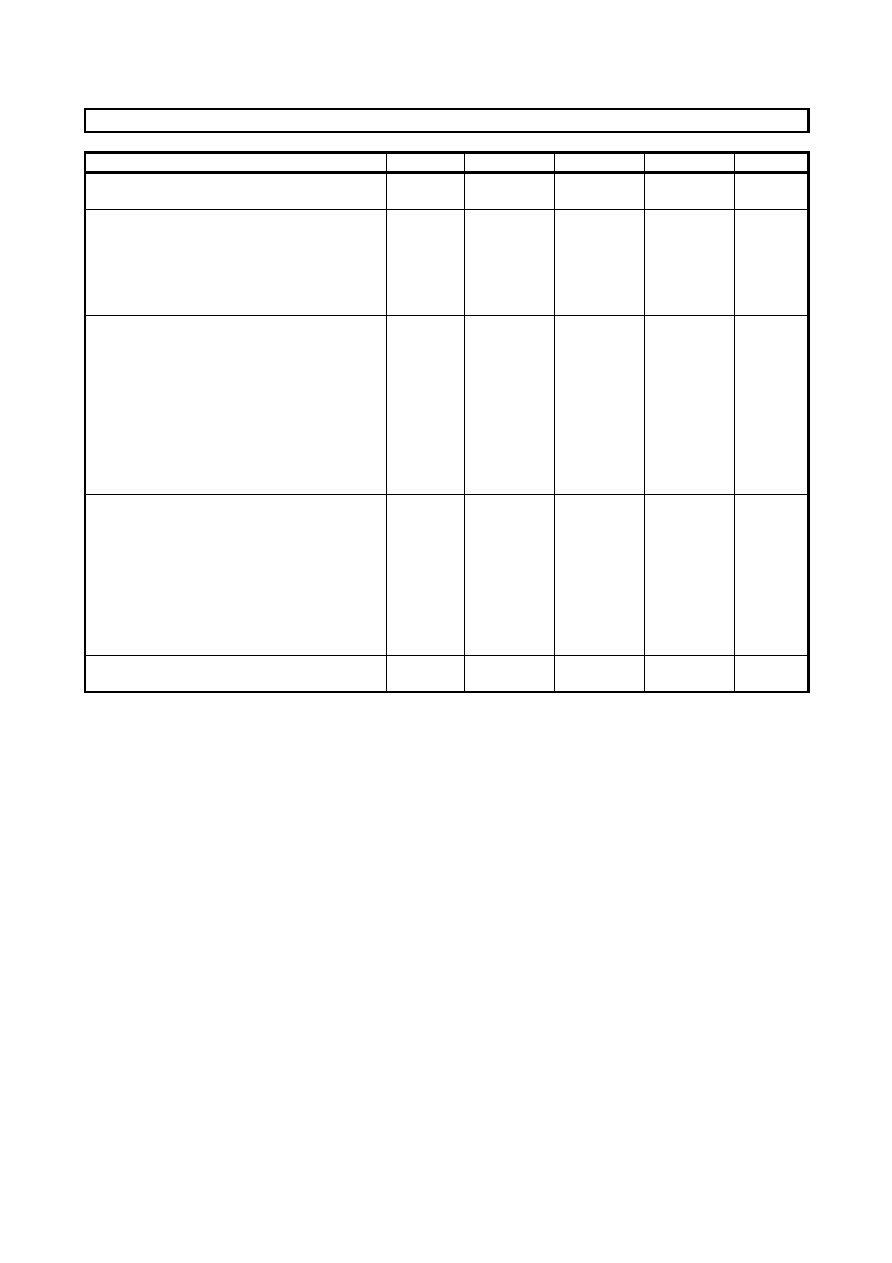

(Ta = 25

∞

C; VDD = 4.75

5.25V; fs = 44.1kHz; DEM = OFF; SLOW = "0")

Parameter

Symbol

min

typ

max

Units

Digital filter

Passband

±

0.05dB (Note 9)

-6.0dB

PB

0

-

22.05

20.0

-

kHz

kHz

Stopband (Note 9)

SB

24.1

kHz

Passband Ripple

PR

±

0.02

dB

Stopband Attenuation

SA

54

dB

Group Delay (Note 10)

GD

-

19.3

-

1/fs

Digital Filter + SCF

Frequency Response

20.0kHz

40.0kHz

80.0kHz

fs=44.1kHz

fs=96kHz

fs=192kHz

FR

FR

FR

-

-

-

±

0.2

±

0.3

+0/-0.6

-

-

-

dB

dB

dB

Notes: 9. fs ()

PB=0.4535*fs(@

±

0.05dB)SB=0.546*fs

10. 16/24

(Ta = 25

∞

C; AVDD, DVDD = 4.75~5.25V; fs = 44.1kHz; DEM = OFF; SLOW = "1")

Parameter

Symbol

min

typ

max

Units

Digital Filter

Passband

±

0.04dB (Note 11)

-3.0dB

PB

0

-

18.2

8.1

-

kHz

kHz

Stopband (Note 11)

SB

39.2

kHz

Passband Ripple

PR

±

0.005

dB

Stopband Attenuation

SA

72

dB

Group Delay (Note 10)

GD

-

19.3

-

1/fs

Digital Filter + SCF

Frequency Response

20.0kHz

40.0kHz

80.0kHz

fs=44.kHz

fs=96kHz

fs=192kHz

FR

FR

FR

-

-

-

+0/-5

+0/-4

+0/-5

-

-

-

dB

dB

dB

Note: 11. The passband and stopband frequencies scale with fs.

For example, PB = 0.185◊fs (@

±

0.04dB), SB = 0.888◊fs.

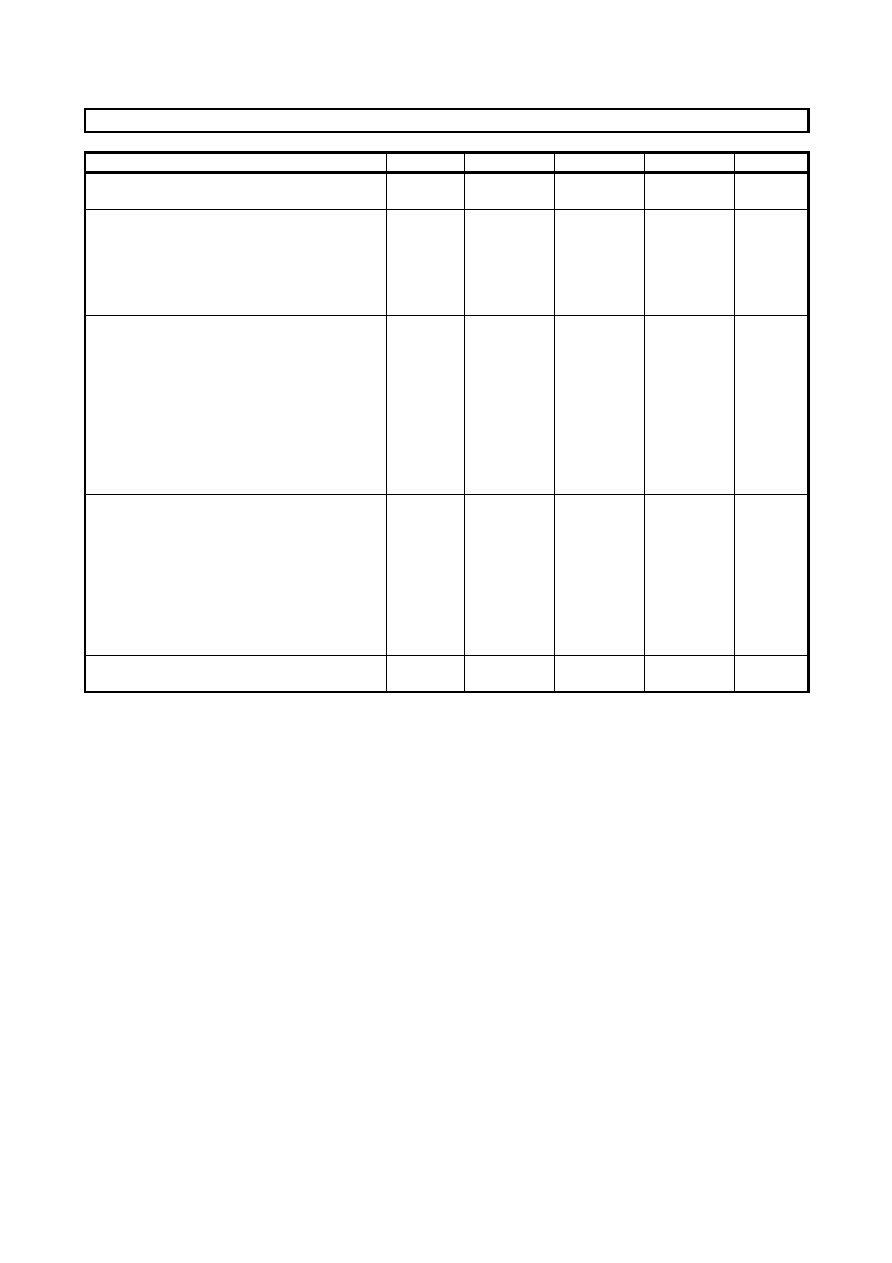

DC

(Ta = 25

∞

C; VDD = 4.75

5.25V)

Parameter

Symbol

min

typ

max

Units

High-Level Input Voltage

Low-Level Input Voltage

VIH

VIL

2.2

-

-

-

-

0.8

V

V

High-Level Output Voltage (Iout = -80µA)

Low-Level Output Voltage (Iout = 80µA)

VOH

VOL

VDD-0.4

-

-

-

0.4

V

V

Input Leakage Current

Iin

-

-

±

10

µA

ASAHI KASEI

[AK4382A]

MS0071-J-01

2002/2

- 6 -

(Ta = 25

∞

C; VDD = 4.75

5.25V; C

L

= 20pF)

Parameter

Symbol

min

typ

max

Units

Master Clock Frequency

Duty Cycle

fCLK

dCLK

2.048

40

11.2896

36.864

60

MHz

%

LRCK Frequency

Normal Speed Mode

Double Speed Mode

Quad Speed Mode

Duty Cycle

fsn

fsd

fsq

Duty

8

60

120

45

48

96

192

55

kHz

kHz

kHz

%

Audio Interface Timing

BICK Period

Normal Speed Mode

Double/Quad Speed Mode

BICK Pulse Width Low

Pulse Width High

BICK "

" to LRCK Edge (Note 12)

LRCK Edge to BICK "

" (Note 12)

SDTI Hold Time

SDTI Setup Time

tBCK

tBCK

tBCKL

tBCKH

tBLR

tLRB

tSDH

tSDS

1/128fs

1/64fs

30

30

20

20

20

20

ns

ns

ns

ns

ns

ns

ns

ns

Control Interface Timing

CCLK Period

CCLK Pulse Width Low

Pulse Width High

CDTI Setup Time

CDTI Hold Time

CSN High Time

CSN "

" to CCLK "

"

CCLK "

" to CSN "

"

tCCK

tCCKL

tCCKH

tCDS

tCDH

tCSW

tCSS

tCSH

200

80

80

40

40

150

50

50

ns

ns

ns

ns

ns

ns

ns

ns

Reset Timing

PDN Pulse Width (Note 13)

tPD

150

ns

Notes: 12. LRCK BICK "

"

13. PDN "L" "H"

ASAHI KASEI

[AK4382A]

MS0071-J-01

2002/2

- 7 -

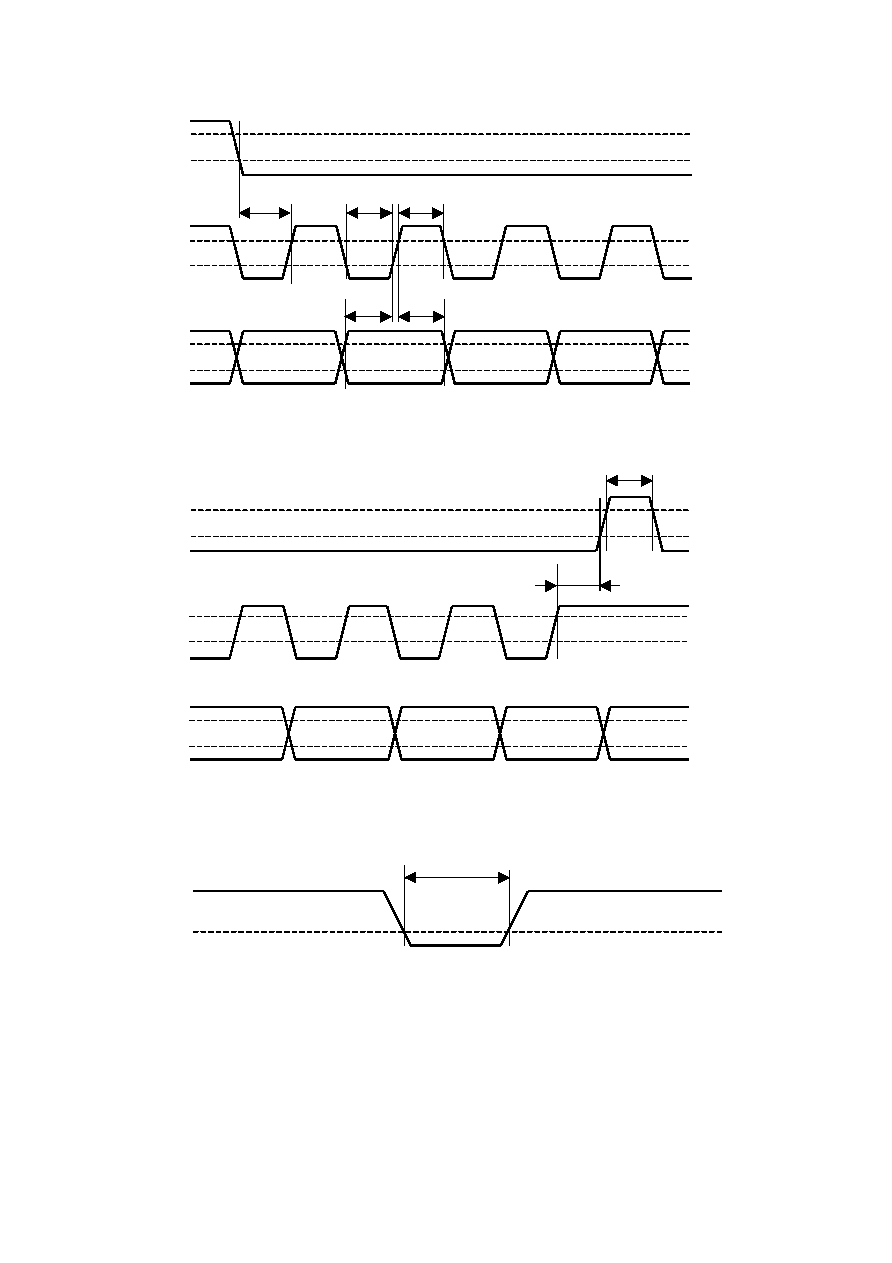

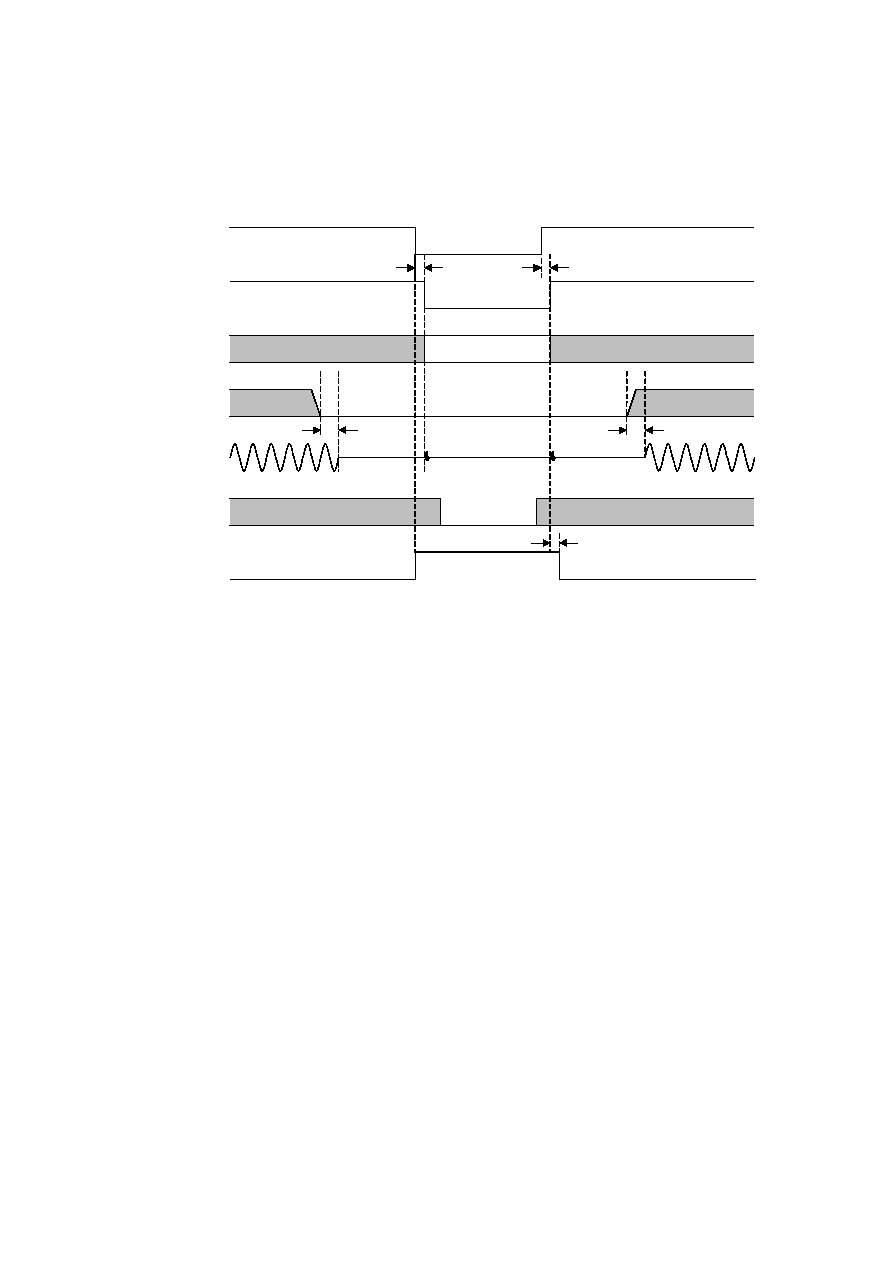

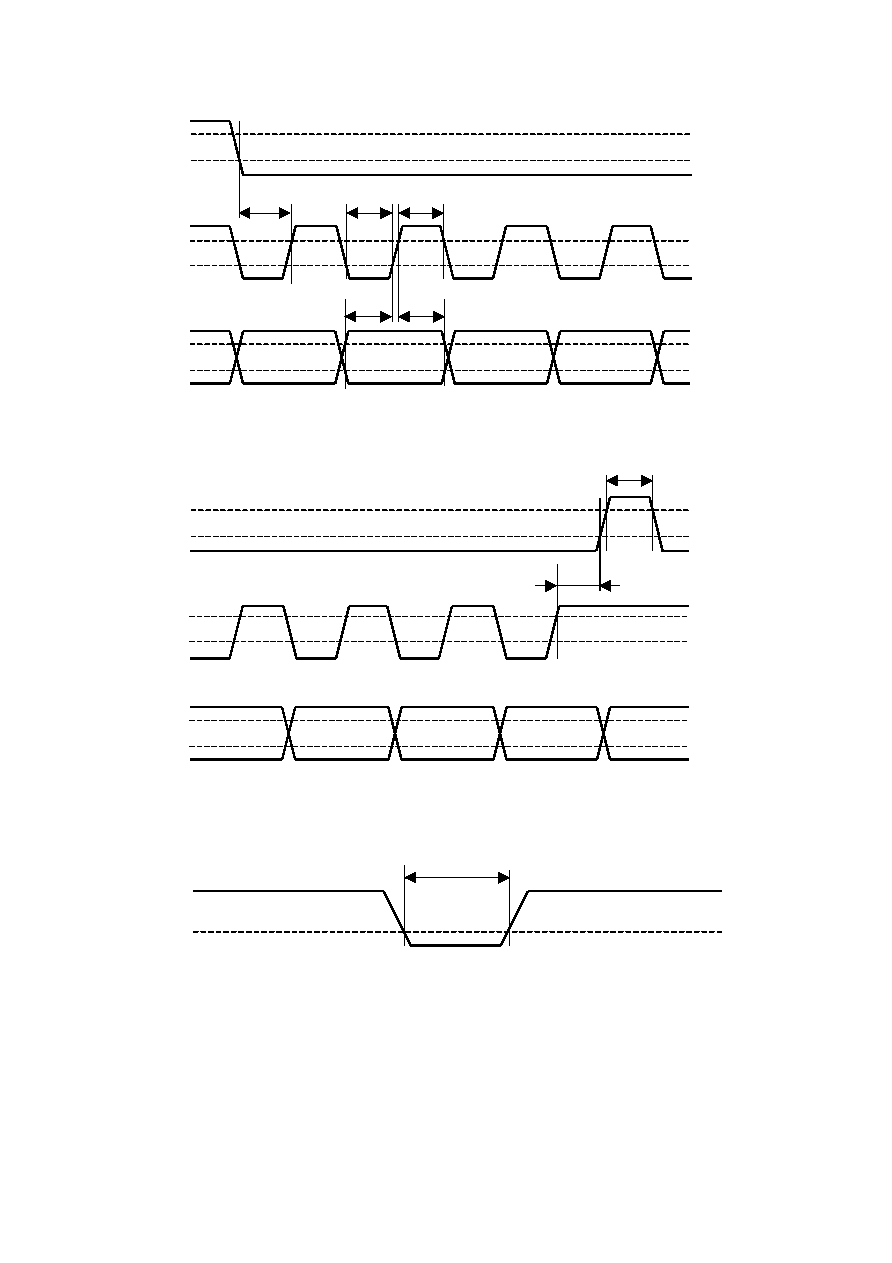

n

1/fCLK

tCLKL

VIH

tCLKH

MCLK

VIL

dCLK=tCLKH x fCLK, tCLKL x fCLK

1/fs

VIH

LRCK

VIL

tBCK

tBCKL

VIH

tBCKH

BICK

VIL

Clock Timing

tLRB

LRCK

VIH

BICK

VIL

tSDS

VIH

SDTI

VIL

tSDH

VIH

VIL

tBLR

Serial Interface Timing

ASAHI KASEI

[AK4382A]

MS0071-J-01

2002/2

- 8 -

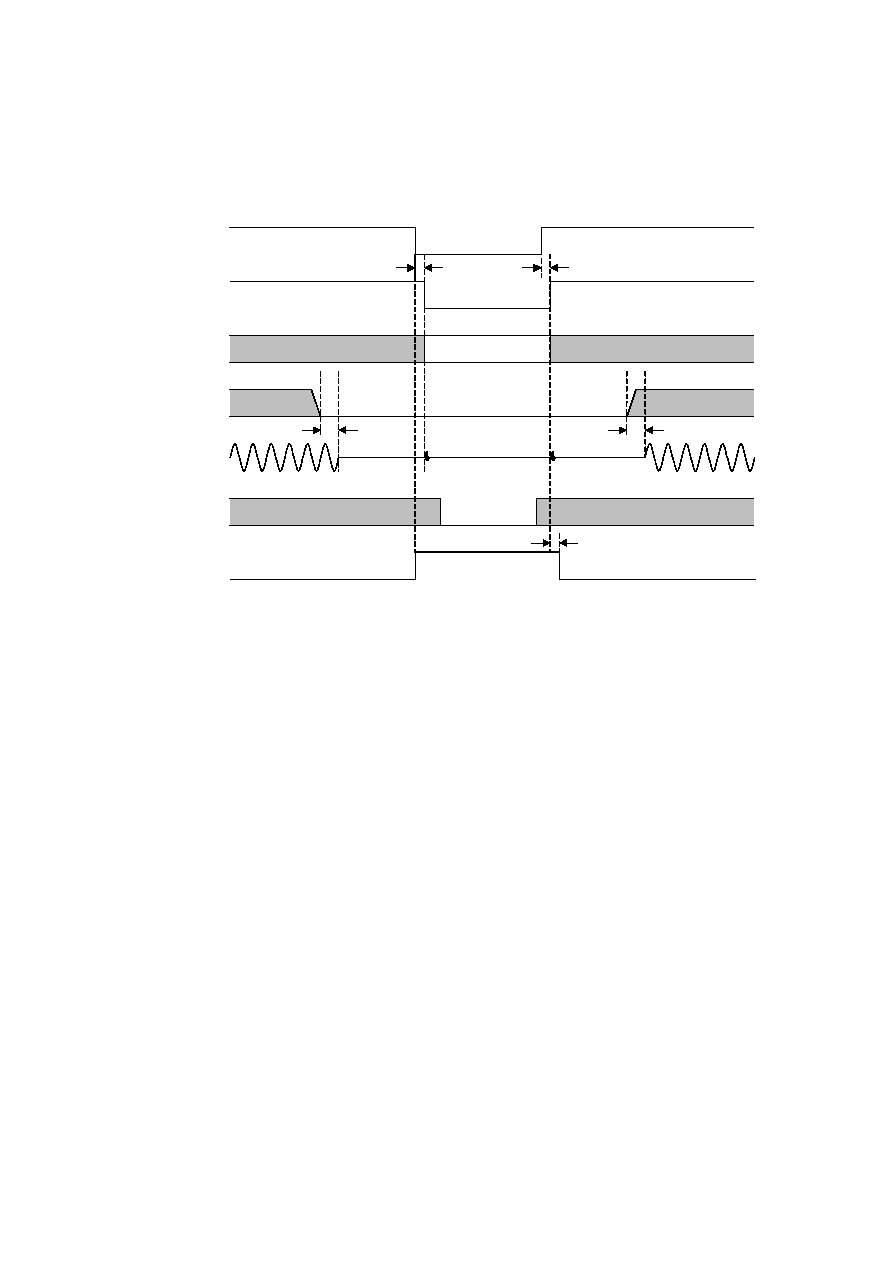

tCSS

CSN

VIH

CCLK

VIL

VIH

CDTI

VIL

VIH

VIL

C1

C0

R/W

A4

tCCKL tCCKH

tCDS

tCDH

WRITE Command Input Timing

CSN

VIH

CCLK

VIL

VIH

CDTI

VIL

VIH

VIL

D3

D2

D1

D0

tCSW

tCSH

WRITE Data Input Timing

tPD

VIL

PDN

Power-down Timing

ASAHI KASEI

[AK4382A]

MS0071-J-01

2002/2

- 9 -

n

MCLK, LRCK, BICK (MCLK) (LRCK)

MCLK -

MCLK (Manual Setting Mode)

(Auto Setting Mode) Manual Setting Mode (ACKS = "0":

Register 00H)DFS0/1 (Table 1)MCLK

(Table 2~4) (PDN = "

") Auto Setting Mode Auto Setting Mode

(ACKS = "1": Default) MCLK(Table 5)

(Table 6) DFS0/1

(PDN= "H") (MCLK, BICK, LRCK)

(PDN= "L") ON

(PDN = "

") MCLK, LRCK

DFS1

DFS0

Sampling Rate (fs)

0

0

Normal Speed Mode

8kHz~48kHz

Default

0

1

Double Speed Mode

60kHz~96kHz

1

0

Quad Speed Mode

120kHz~192kHz

Table 1. (Manual Setting Mode)

LRCK

MCLK

BICK

fs

256fs

384fs

512fs

768fs

64fs

32.0kHz 8.1920MHz 12.2880MHz 16.3840MHz 24.5760MHz 2.0480MHz

44.1kHz 11.2896MHz 16.9344MHz 22.5792MHz 33.8688MHz 2.8224MHz

48.0kHz 12.2880MHz 18.4320MHz 24.5760MHz 36.8640MHz 3.0720MHz

Table 2. (Normal Speed Mode Manual Setting Mode)

LRCK

MCLK

BICK

fs

128fs

192fs

256fs

384fs

64fs

88.2kHz 11.2896MHz 16.9344MHz 22.5792MHz 33.8688MHz 5.6448MHz

96.0kHz 12.2880MHz 18.4320MHz 24.5760MHz 36.8640MHz 6.1440MHz

Table 3. (Double Speed Mode Manual Setting Mode)

LRCK

MCLK

BICK

fs

128fs

192fs

64fs

176.4kHz 22.5792MHz 33.8688MHz 11.2896MHz

192.0kHz 24.5760MHz 36.8640MHz 12.2880MHz

Table 4. (Quad Speed Mode Manual Setting Mode)

ASAHI KASEI

[AK4382A]

MS0071-J-01

2002/2

- 10 -

MCLK

Sampling Speed

512fs

768fs

Normal

256fs

384fs

Double

128fs

192fs

Quad

Table 5. (Auto Setting Mode: Default)

LRCK

MCLK (MHz)

fs

128fs

192fs

256fs

384fs

512fs

768fs

Sampling Speed

32.0kHz

-

-

-

-

16.3840

24.5760

44.1kHz

-

-

-

-

22.5792

33.8688

48.0kHz

-

-

-

-

24.5760

36.8640

Normal

88.2kHz

-

-

22.5792

33.8688

-

-

96.0kHz

-

-

24.5760

36.8640

-

-

Double

176.4kHz

22.5792

33.8688

-

-

-

-

192.0kHz

24.5760

36.8640

-

-

-

-

Quad

Table 6. (Auto Setting Mode)

n

BICK LRCK SDTI 5 (Table 7)

DIF0-2 MSB 2's BICK

Mode 2 16/20 LSB "0"

Mode

DIF2 DIF1 DIF0 SDTI Format

BICK

Figure

0

0

0

0

16bit

32fs

Figure 1

1

0

0

1

20bit

40fs

Figure 2

2

0

1

0

24bit

48fs

Figure 3

Default

3

0

1

1

24bit I

2

S

48fs

Figure 4

4

1

0

0

24bit

48fs

Figure 2

Table 7.

ASAHI KASEI

[AK4382A]

MS0071-J-01

2002/2

- 11 -

SDTI

BICK

LRCK

SDTI

15 14

6

5

4

BICK

0

1

10

11

12

13

14

15

0

1

10

11

12

13

14

15

0

1

3

2

1

0

15 14

(32fs)

(64fs)

0

14

1

15

16

17

31

0

1

14

15

16

17

31

0

1

15 14

0

15 14

0

Mode 0

Don't care

Don't care

15:MSB, 0:LSB

Mode 0

15 14

6

5

4

3

2

1

0

Lch Data

Rch Data

Figure 1. Mode 0 Timing

SDTI

LRCK

BICK

(64fs)

0

9

1

10

11

12

31

0

1

9

10

11

12

31

0

1

19

0

19

0

Mode 1

Don't care

Don't care

19:MSB, 0:LSB

SDTI

Mode 4

23:MSB, 0:LSB

20 19

0

20 19

0

Don't care

Don't care

22 21

22 21

Lch Data

Rch Data

8

23

23

8

Figure 2. Mode 1,4 Timing

LRCK

BICK

(64fs)

SDTI

0

22

1

2

24

31

0

1

31

0

1

23:MSB, 0:LSB

22

1

0

Don't care

23

Lch Data

Rch Data

23

30

22

2

24

23

30

22

1

0

Don't care

23

22

23

Figure 3. Mode 2 Timing

ASAHI KASEI

[AK4382A]

MS0071-J-01

2002/2

- 12 -

LRCK

BICK

(64fs)

SDTI

0

3

1

2

24

31

0

1

31

0

1

23:MSB, 0:LSB

22

1

0

Don't care

23

Lch Data

Rch Data

23

25

3

2

24

23

25

22

1

0

Don't care

23

23

Figure 4. Mode 3 Timing

n

IIR 3 (32kHz, 44.1kHz, 48kHz) (50/15

µ

s )

Double Speed Mode, Quad Speed Mode OFF

DEM1

DEM0

Mode

0

0

44.1kHz

0

1

OFF

Default

1

0

48kHz

1

1

32kHz

Table 8. (Normal Speed Mode)

n

AK4382AMUTE256 ATT

DAC0dB-48dB

1

256 Table 9

Sampling Speed

1 Level

255 to 0

Normal Speed Mode

4LRCK

1020LRCK

Double Speed Mode

8LRCK

2040LRCK

Quad Speed Mode

16LRCK

4080LRCK

Table 9. ATT

ASAHI KASEI

[AK4382A]

MS0071-J-01

2002/2

- 13 -

n

AK4382A8192 "0"

DZF "H" "0"

DZF "L"RSTN "0"DZF "H"

RSTN "1" "0"DZF

4~5LRCK "L"DZFM "1"8192

"0"DZF "H"DZFE

DZF "L"DZFDZFB

n

SMUTE "1"ATT

ATT

◊

ATT (Table 9)-

("0")SMUTE"0"

-

-

ATT

◊

ATTATT

-

ATT

SMUTE bit

Attenuation

DZF pin

ATT Level

-

AOUT

8192/fs

GD

GD

(1)

(2)

(3)

(4)

(1)

:

(1) ATT

◊

ATT (Table 9) Normal Speed ModeATT "255"

1020LRCK

(2) (GD)

(3) -

0dB

(4)8192"0"DZF"H"

"0"DZF"L"

Figure 5.

ASAHI KASEI

[AK4382A]

MS0071-J-01

2002/2

- 14 -

n

ON PDN "L" MCLK

LRCK "

" LRCK

n

PDN "L" (Hi-Z)

Figure5

Normal Operation

Internal

State

PDN

Power-down

Normal Operation

GD

GD

"0" data

D/A Out

(Analog)

D/A In

(Digital)

Clock In

MCLK, LRCK, BICK

(1)

(3)

(6)

DZF

External

MUTE

(5)

(3)

(1)

Mute ON

(2)

(4)

Don't care

(1) (GD)

(2) Hi-Z

(3) PDN ("

")

"0"

(4) (PDN = "L")(MCLK, BICK, LRCK)

(5) (3)

(6) (PDN= "L")DZF "L"

Figure 6. /

ASAHI KASEI

[AK4382A]

MS0071-J-01

2002/2

- 15 -

n

RSTN "0"DAC

VCOM DZFL/DZFR"H"Figure 7RSTN

Internal

State

RSTN bit

Digital Block Power-down

Normal Operation

GD

GD

"0" data

D/A Out

(Analog)

D/A In

(Digital)

Clock In

MCLK,LRCK,BICK

(1)

(3)

DZF

(3)

(1)

(2)

Normal Operation

2/fs(5)

Internal

RSTN bit

2~3/fs (6)

3~4/fs (6)

Don't care

(4)

(1) (GD)

(2) RSTN = "0"VCOM(VDD/2)

(3) RSTN("

") "0"

(4) (RSTN = "0")(MCLK, BICK, LRCK)

(5) DZFRSTN "H"LSIRSTN

2/fs "L"

(6) RSTNLSIRSTN3 ~4/fs

2 ~ 3/fs

Figure 7.

ASAHI KASEI

[AK4382A]

MS0071-J-01

2002/2

- 16 -

n

AK4382A 3 I/F : CSN, CCLK, CDTI

I/F Chip address (2bit, C1/0, "01"), Read/Write (1bit, "1", Write only),

Register address (MSB first, 5bit) Control data (MSB first, 8bit)CCLK "

"

"

" CSN "

" CCLK

5MHz (max)CSN "H"

PDN "L"RSTN "L"

CDTI

CCLK

C1

0

1

2

3

4

5

6

7

8

9

10 11 12 13 14 15

D4

D5

D6

D7

A1

A2

A3

A4

R/W

C0

A0

D0

D1

D2

D3

CSN

C1-C0: Chip Address (Fixed to "01")

R/W: READ/WRITE (Fixed to "1", Write only)

A4-A0: Register Address

D7-D0: Control Data

Figure 8. Control I/F Timing

*AK4382AC1/0, R/W ("011")

*PDN = "L"

n

Register Map

Addr

Register Name

D7

D6

D5

D4

D3

D2

D1

D0

00H Control 1

ACKS

0

0

DIF2

DIF1

DIF0

PW

RSTN

01H Control 2

DZFE

DZFM

SLOW

DFS1

DFS0

DEM1

DEM0

SMUTE

02H Control 3

0

0

0

0

0

DZFB

0

0

03H Lch ATT

ATT7

ATT6

ATT5

ATT4

ATT3

ATT2

ATT1

ATT0

04H Rch ATT

ATT7

ATT6

ATT5

ATT4

ATT3

ATT2

ATT1

ATT0

Notes:

For addresses from 05H to 1FH, data must not be written.

When PDN pin goes "L", the registers are initialized to their default values.

When RSTN bit goes "0", the only internal timing is reset and the registers are not initialized to their default values.

All data can be written to the register even if PW or RSTN bit is "0".

ASAHI KASEI

[AK4382A]

MS0071-J-01

2002/2

- 17 -

n

Register Definitions

Addr

Register Name

D7

D6

D5

D4

D3

D2

D1

D0

00H Control 1

ACKS

0

0

DIF2

DIF1

DIF0

PW

RSTN

default

1

0

0

0

1

0

1

1

RSTN: Internal timing reset control

0: Reset. All registers are not initialized.

1: Normal Operation

When MCLK frequency or DFS changes, the AK4382A should be reset by PDN pin or RSTN bit.

PW: Power down control

0: Power down. All registers are not initialized.

1: Normal Operation

DIF2-0: Audio data interface formats (see Table 7)

Initial: "010", Mode 2

ACKS: Master Clock Frequency Auto Setting Mode Enable

0: Disable, Manual Setting Mode

1: Enable, Auto Setting Mode

Master clock frequency is detected automatically at ACKS bit "1". In this case, the setting of DFS1-0

are ignored. When this bit is "0", DFS1-0 set the sampling speed mode.

Addr

Register Name

D7

D6

D5

D4

D3

D2

D1

D0

01H Control 2

DZFE

DZFM

SLOW

DFS1

DFS0

DEM1

DEM0

SMUTE

default

0

0

0

0

0

0

1

0

SMUTE: Soft Mute Enable

0: Normal operation

1: DAC outputs soft-muted

DEM1-0: De-emphasis Response (see Table 8)

Initial: "01", OFF

DFS1-0: Sampling speed control

00: Normal Speed Mode

01: Double Speed Mode

10: Quad Speed Mode

When changing between Normal/Double Speed Mode and Quad Speed Mode, some click noise occurs.

SLOW: Slow Roll-off Filter Enable

0: Sharp Roll-off Filter

1: Slow Roll-off Filter

DZFE: Data Zero Detect Enable

0: Disable

1: Enable

Zero detect function can be disabled by DZFE bit "0". In this case, the DZF pins of both channels are

always "L".

ASAHI KASEI

[AK4382A]

MS0071-J-01

2002/2

- 18 -

DZFM: Data Zero Detect Mode

0: Channel Separated Mode

1: Channel ANDed Mode

If the DZFM bit is set to "1", the DZF pins of both channels go to "H" only when the input data at both

channels are continuously zeros for 8192 LRCK cycles.

Addr

Register Name

D7

D6

D5

D4

D3

D2

D1

D0

02H Control 3

0

0

0

0

0

DZFB

0

0

default

0

0

0

0

0

0

0

0

DZFB: Inverting Enable of DZF

0: DZF goes "H" at Zero Detection

1: DZF goes "L" at Zero Detection

Addr

Register Name

D7

D6

D5

D4

D3

D2

D1

D0

03H Lch ATT

ATT7

ATT6

ATT5

ATT4

ATT3

ATT2

ATT1

ATT0

04H Rch ATT

ATT7

ATT6

ATT5

ATT4

ATT3

ATT2

ATT1

ATT0

default

1

1

1

1

1

1

1

1

ATT = 20 log

10

(ATT_DATA / 255) [dB]

00H: Mute

Figure 9 (AKD4382)

MCLK

1

BICK

2

SDTI

3

LRCK

4

PDN

5

CSN

6

CCLK

7

CDTI

8

DZFL

16

DZFR

15

VDD

14

VSS

13

AOUTL+

12

AOUTL-

11

AOUTR+

10

AOUTR-

9

Master Clock

Micro-

controller

AK4382A

fs

24bit Audio Data

Reset & Power down

64fs

10u

0.1u

+

Lch

LPF

Rch

LPF

Rch Out

Lch Out

MUTE

Analog Ground

Digital Ground

Lch

MUTE

Rch

MUTE

Analog

Supply 5V

Figure 9. Typical Connection Diagram

Notes:

- LRCK = fs, BICK=64fs.

- AOUT

-

ASAHI KASEI

[AK4382A]

MS0071-J-01

2002/2

- 19 -

1.

VDD VSS

VDD

VDD VSS

2.

2.5V 0.55 x VDD Vpp (typ)

AOUT+ AOUT-V

AOUT

= (AOUT+)-(AOUT-)

5.5Vpp (typ@VDD=5V)

2's (2 ) 7FFFFFH(@24bit)

800000H(@24bit) 000000H(@24bit) V

AOUT

0V

SCF

AK4382ADCAOUT+/-DC

Figure 1011 LPF

4.7k

4.7k

R1

4.7k

R1

4.7k

470p

Vop

470p

Vop

1k

1k

47u

0.1u

BIAS

AOUT-

AOUT+

3300p

When R1=200

When R1=180

fc=93.2kHz, Q=0.712, g=-0.1dB at 40kHz

fc=98.2kHz, Q=0.681, g=-0.2dB at 40kHz

Analog

Out

Figure 10. External 2

nd

order LPF Circuit Example (using op-amp with single power supply)

4.7k

4.7k

R1

4.7k

R1

4.7k

470p

+Vop

470p

-Vop

AOUT-

AOUT+

3300p

When R1=200

When R1=180

fc=93.2kHz, Q=0.712, g=-0.1dB at 40kHz

fc=98.2kHz, Q=0.681, g=-0.2dB at 40kHz

Analog

Out

Figure 11. External 2

nd

order LPF Circuit Example (using op-amp with dual power supplies)

ASAHI KASEI

[AK4382A]

MS0071-J-01

2002/2

- 20 -

0-10

∞

Detail A

Seating Plane

0.10

0.17

±

0.05

0.22

±

0.1

0.65

*5.0

±

0.1

1.05

±

0.05

A

1

8

9

16

16pin TSSOP (Unit: mm)

*4.4

±

0.1

6.4

±

0.2

0.5

±

0.2

0.1

±

0.1

NOTE: Dimension "*" does not include mold flash.

0.13

M

n

:

:

: ()

ASAHI KASEI

[AK4382A]

MS0071-J-01

2002/2

- 21 -

AKM

4382AT

XXYYY

1)

Pin #1 indication

2)

Date Code : XXYYY (5 digits)

XX: Lot#

YYY: Date Code

3)

Marketing Code : 4382AT

4)

Asahi Kasei Logo

∑

∑

∑

()

∑

∑

∑