eroflex Circuit Technology - Advanced Multichip Modules © SCD3359 REV B 12/17/98

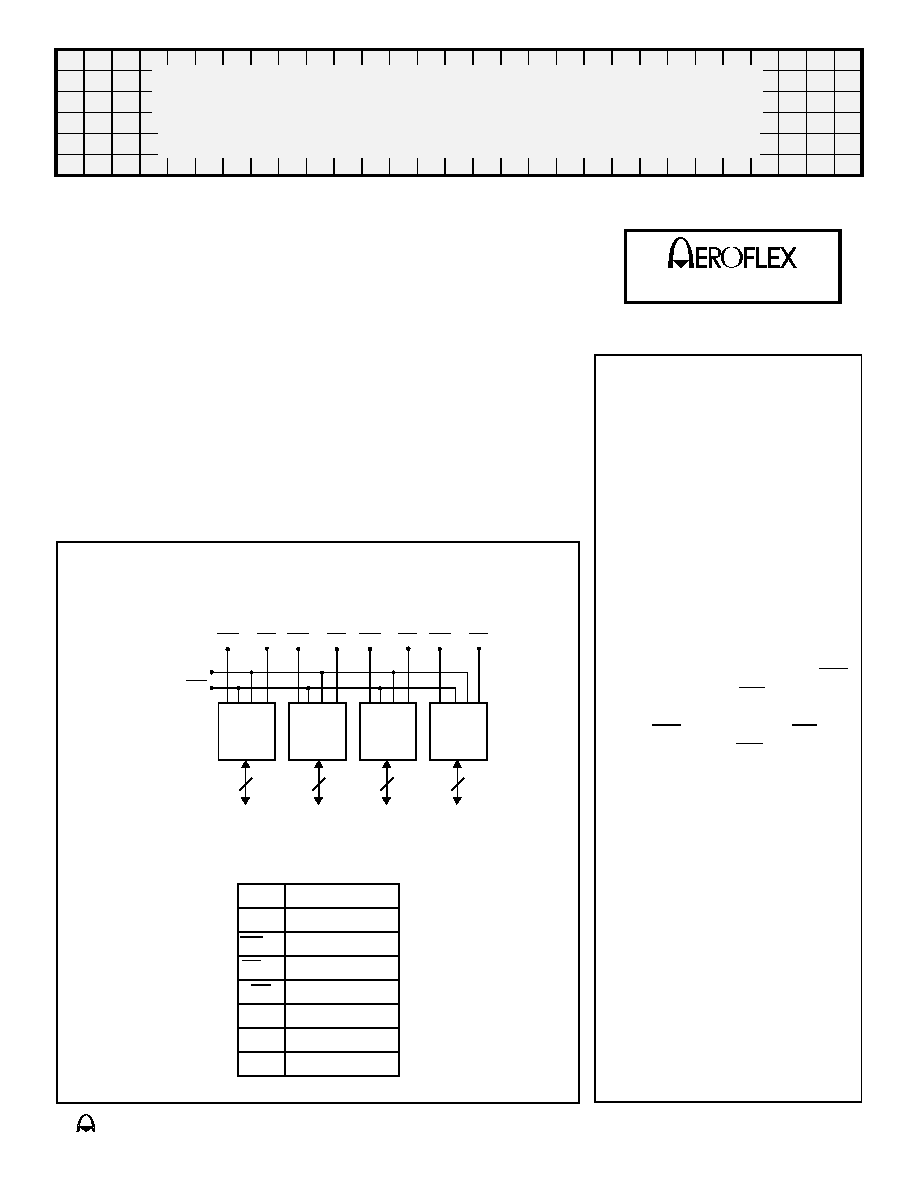

Block Diagram ≠ PGA Type Package(P7) & CQFP(F2)

128Kx8

128Kx8

128Kx8

128Kx8

CE

4

OE

A

0

≠

A

16

I/O

0-7

I/O

8-15

I/O

16-23

I/O

24-31

8

8

8

8

CE

3

WE

4

WE

3

WE

2

WE

1

CE

1

CE

2

Pin Description

I/O

0-31

Data I/O

A

0≠16

Address Inputs

WE

1≠4

Write Enables

CE

1≠4

Chip Enables

OE

Output Enable

V

cc

Power Supply

GND

Ground

NC

Not Connected

General Description

The ACT≠S128K32V is a High

Speed 4 megabit CMOS SRAM

Multichip Module (MCM)

designed for full temperature

range, 3.3V Power Supply,

military, space, or high reliability

mass memory and fast cache

applications.

The MCM can be organized

as a 128K x 32 bits, 256K x 16

bits or 512k x 8 bits device and

is input and output TTL

compatible. Writing is executed

when the write enable (WE)

and chip enable (CE) inputs are

low. Reading is accomplished

when WE is high and CE and

output enable (OE) are both

low. Access time grades of

17ns, 20ns, 25ns, 35ns, 45ns

and 55ns maximum are

standard.

The products are designed for

operation over the temperature

range of -55∞C to +125∞C and

screened under the full military

environment. DESC Standard

Military Drawing (SMD) part

numbers are pending.

The ACT-S128K32V is

manufactured in Aeroflex's

80,000ft

2

MIL-PRF-38534

certified facility in Plainview,

N.Y.

Features

s

4 Low Power CMOS 128K x 8 SRAMs in one MCM

s

Overall configuration as 128K x 32

s

Input and Output TTL Compatible

s

17, 20, 25, 35, 45 & 55ns Access Times, 15ns Available by

Special Order

s

Full Military (-55∞C to +125∞C) Temperature Range

s

+3.3V Power Supply

s

Choice of Surface Mount or PGA Type Co-fired Packages:

q

68≠Lead, Dual-Cavity CQFP (F2), .88"SQ x .20"max (.18"max thickness

available, contact factory for details) (Drops into the 68 Lead JEDEC .99"SQ

CQFJ footprint)

q

66≠Lead, PGA-Type (P7), 1.08"SQ x .160"max

s

Internal Decoupling Capacitors

s

DESC SMD# Pending

CIRCUIT TECHNOLOGY

www.aeroflex.com/act1.htm

ACT-S128K32V High Speed 3.3Volt

4 Megabit SRAM Multichip Module

Aeroflex Circuit Technology ACT-S128K32V

SCD3359 REV B 12/17/98 Plainview NY (516) 694-6700

2

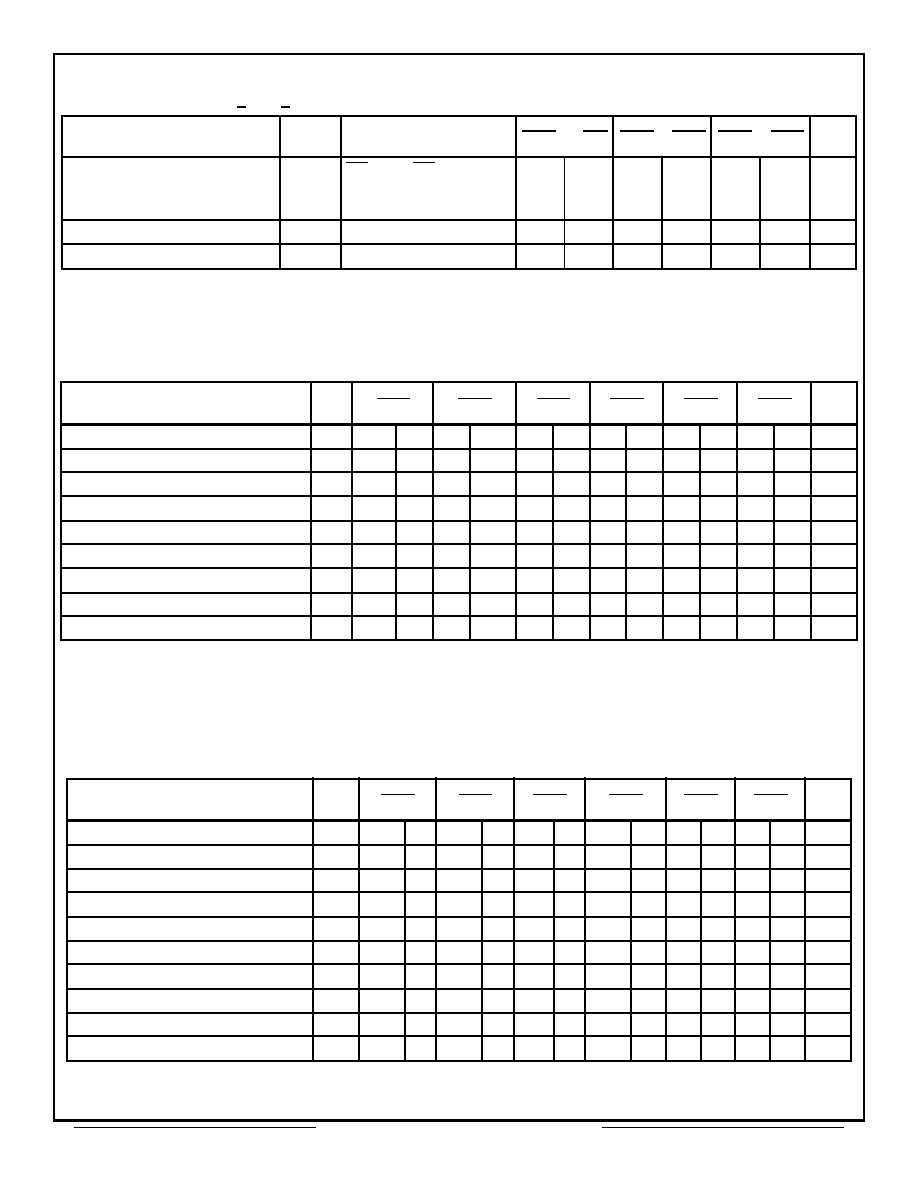

Absolute Maximum Ratings

Symbol

Rating

Range

Units

T

C

Case Operating Temperature

-55 to +125

∞C

T

STG

Storage Temperature

-65 to +150

∞C

P

D

Maximum Package Power Dissipation

P7 Packages

3.0

W

F2 Package

2.7

W

ÿ

J-C

Hottest Die, Max Thermal Resistance - Junction to Case

P7 Packages

3.0

∞C/W

F2 Package

9.0

∞C/W

V

G

Maximum Signal Voltage to Ground

-0.5 to +4.6

V

T

L

Maximum Lead Temperature (10 seconds)

300

∞C

Normal Operating Conditions

Symbol

Parameter

Minimum

Maximum

Units

V

CC

Power Supply Voltage

+3.0

+3.6

V

V

IH

Input High Voltage

+2.0

V

CC

+ 0.3

V

V

IL

Input Low Voltage

-0.3

+0.8

V

Truth Table

Mode

CE

OE

WE

Data I/O

Power

Standby

H

X

X

High Z

Standby (deselect/power down)

Read

L

L

H

Data Out

Active

Read

L

H

H

High Z

Active (deselected)

Write

L

X

L

Data In

Active

Capacitance

(

f = 1MHz, T

C

= 25∞C

)

Symbol Parameter

Maximum

Units

C

AD

A

0

≠

A

16

Capacitance

50

pF

C

OE

OE Capacitance

50

pF

C

WE

Write Enable Capacitance

20

pF

C

CE

Chip Enable Capacitance

20

pF

C

I

/

O

I/O

0

≠ I/O

31

Capacitance

20

pF

Capacitance is guaranteed by design but not tested.

DC Characteristics

(3.0Vdc< V

CC

< 3.6Vdc, V

SS

= 0V, T

C

= -55∞C to +125∞C, Unless otherwise specified)

Parameter

Sym

Conditions

≠017 & ≠020

Min Max

≠025 & ≠035

Min Max

≠045 & ≠055

Min Max

Units

Input Leakage Current

I

LI

V

CC

= Max,

V

IN

= 0 or V

CC

10

10

10

µA

Output Leakage Current

I

LO

CE = V

IH

, OE = V

IH

,

V

OUT

= 0 or V

CC

10

10

10

µA

Operating Supply Current 32

Bit Mode

I

CC

x32

CE = V

IL

, OE = V

IH

,

f = 5 MHz, V

CC

= Max,

CMOS Compatible

750

500

420

mA

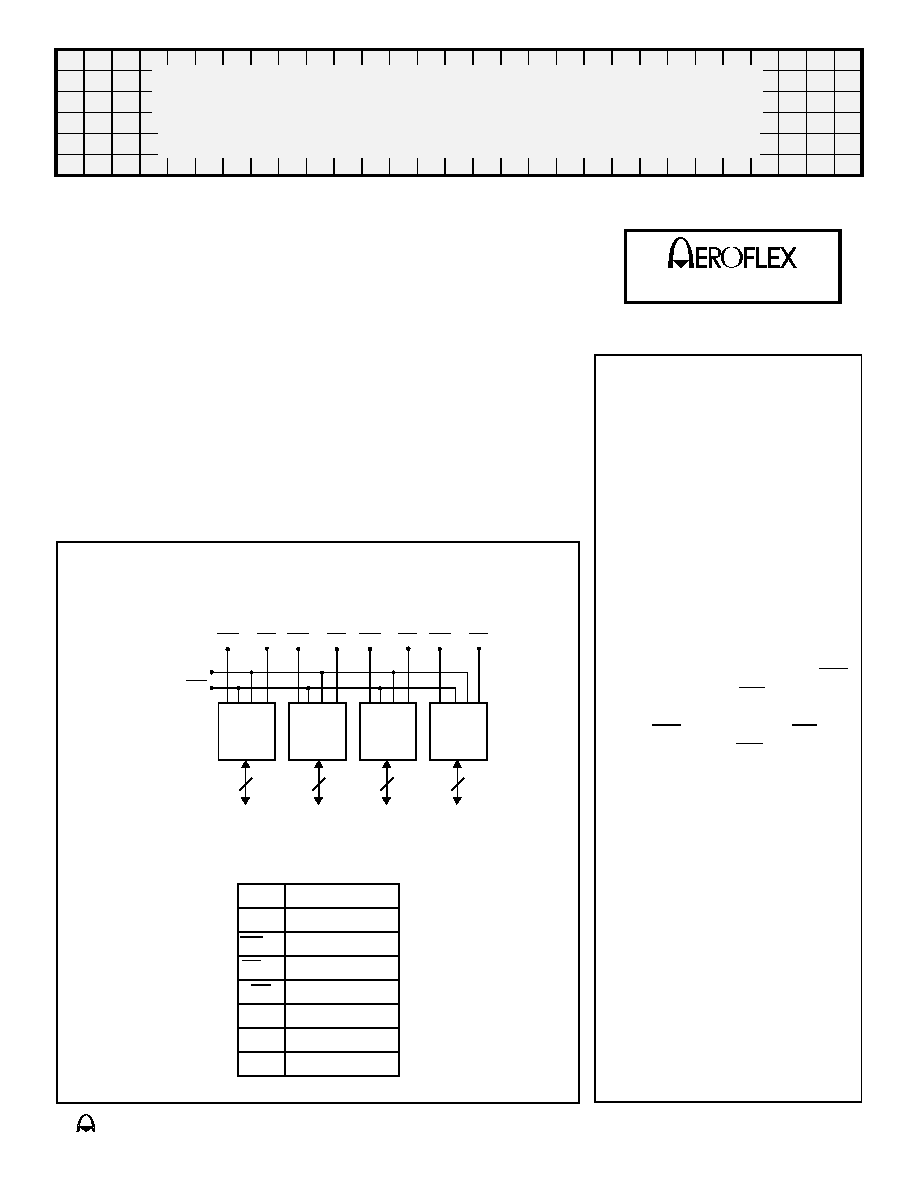

Aeroflex Circuit Technology ACT-S128K32V

SCD3359 REV B 12/17/98 Plainview NY (516) 694-6700

3

Standby Current

I

SB

CE = V

IH

, OE = V

IH

,

f = 5 MHz, V

CC

= Max,

CMOS Compatible

80

60

60

mA

Output Low Voltage

V

OL

I

OL

= 8 mA, V

CC

= Min

0.4

0.4

0.4

V

Output High Voltage

V

OH

I

OH

= -4.0 mA, V

CC

= Min

2.4

2.4

2.4

V

AC Characteristics

(V

CC

= 3.3V, V

SS

= 0V, T

C

= -55∞C to +125∞C)

Read Cycle

Parameter

Sym

≠017

Min Max

≠020

Min Max

≠025

Min Max

≠035

Min Max

≠045

Min Max

≠055

Min Max

Units

Read Cycle Time

t

RC

17

20

25

35

45

55

ns

Address Access Time

t

AA

17

20

25

35

45

55

ns

Chip Enable Access Time

t

ACE

17

20

25

35

45

55

ns

Output Hold from Address Change

t

OH

0

0

0

0

0

0

ns

Output Enable to Output Valid

t

OE

9

12

15

20

25

30

ns

Chip Enable to Output in Low Z *

t

CLZ

3

3

3

3

3

3

ns

Output Enable to Output in Low Z *

t

OLZ

0

0

0

0

0

0

ns

Chip Deselect to Output in High Z *

t

CHZ

12

12

12

15

20

20

ns

Output Disable to Output in High Z * t

OHZ

10

11

12

15

20

20

ns

* Parameters guaranteed by design but not tested

Write Cycle

Parameter

Sym

≠017

Min Max

≠020

Min Max

≠025

Min ax

≠035

Min Max

≠045

Min Max

≠055

Min Max

Units

Write Cycle Time

t

WC

17

20

25

35

45

55

ns

Chip Enable to End of Write

t

CW

12

15

20

25

30

40

ns

Address Valid to End of Write

t

AW

12

15

20

25

30

40

ns

Data Valid to End of Write

t

DW

10

12

15

18

20

20

ns

Write Pulse Width

t

WP

13

15

20

25

30

40

ns

Address Setup Time

t

AS

0

0

0

0

0

0

ns

Output Active from End of Write *

t

OW

3

3

3

4

4

4

ns

Write to Output in High Z *

t

WHZ

10

10

10

15

15

15

ns

Data Hold from Write Time

t

DH

0

0

0

0

0

0

ns

Address Hold Time

t

AH

0

0

0

0

0

0

ns

* Parameters guaranteed by design but not tested

DC Characteristics (continued)

(3.0Vdc< V

CC

< 3.6Vdc, V

SS

= 0V, T

C

= -55∞C to +125∞C, Unless otherwise specified)

Parameter

Sym

Conditions

≠017 & ≠020

Min Max

≠025 & ≠035

Min Max

≠045 & ≠055

Min Max

Units

Aeroflex Circuit Technology ACT-S128K32V

SCD3359 REV B 12/17/98 Plainview NY (516) 694-6700

4

Timing Diagrams

D

I/O

t

RC

t

OH

t

AA

Data Valid

Previous Data Valid

t

OE

High Z

t

OHZ

Read Cycle Timing Diagrams

Data Valid

t

CLZ

CE

OE

t

ACS

t

CHZ

UNDEFINED

DON'T CARE

Read Cycle 2 (WE = V

IH

)

Write Cycle 2 (CE Controlled, OE = V

IH

)

D

I/O

AC Test Circuit

I

OL

Parameter

Typical

Units

Input Pulse Level

0 ≠ 3.0

V

Input Rise and Fall

5

ns

Input and Output Timing Reference

Level

1.5

V

Notes:

1) V

Z

is programmable from -2V to +4.6V. 2) I

OL

and I

OH

programmable from 0 to 16 mA. 3) Tester Impedance

Z

O

= 75

. 4)

V

Z

is typically the midpoint of V

OH

and V

OL

. 5) I

OL

and I

OH

are adjusted to simulate a typical resistance

load circuit. 6) ATE Tester includes jig capacitance.

I

OH

To Device Under Test

V

Z

~ 1.5 V (Bipolar Supply)

Current Source

Current Source

C

L

=

50 pF

t

RC

t

AA

t

OLZ

S

EE

N

OTE

S

EE

N

OTE

S

EE

N

OTE

S

EE

N

OTE

Note: Guaranteed by design, but not tested.

Read Cycle 1 (CE = OE = V

IL

, WE = V

IH

)

t

WP

t

DW

Data Valid

t

WC

t

AW

t

AH

D

I/O

t

DH

CE

WE

t

CW

t

AS

A

0-18

A

0-18

A

0-18

t

CW

t

AS

t

WP

t

DW

t

OW

CE

WE

Data Valid

t

WC

t

AW

t

AH

D

I/O

t

DH

t

WHZ

S

EE

N

OTE

A

0-16

S

EE

N

OTE

Write Cycle Timing Diagrams

Write Cycle 1 (WE Controlled, OE = V

IL

)

Aeroflex Circuit Technology ACT-S128K32V

SCD3359 REV B 12/17/98 Plainview NY (516) 694-6700

5

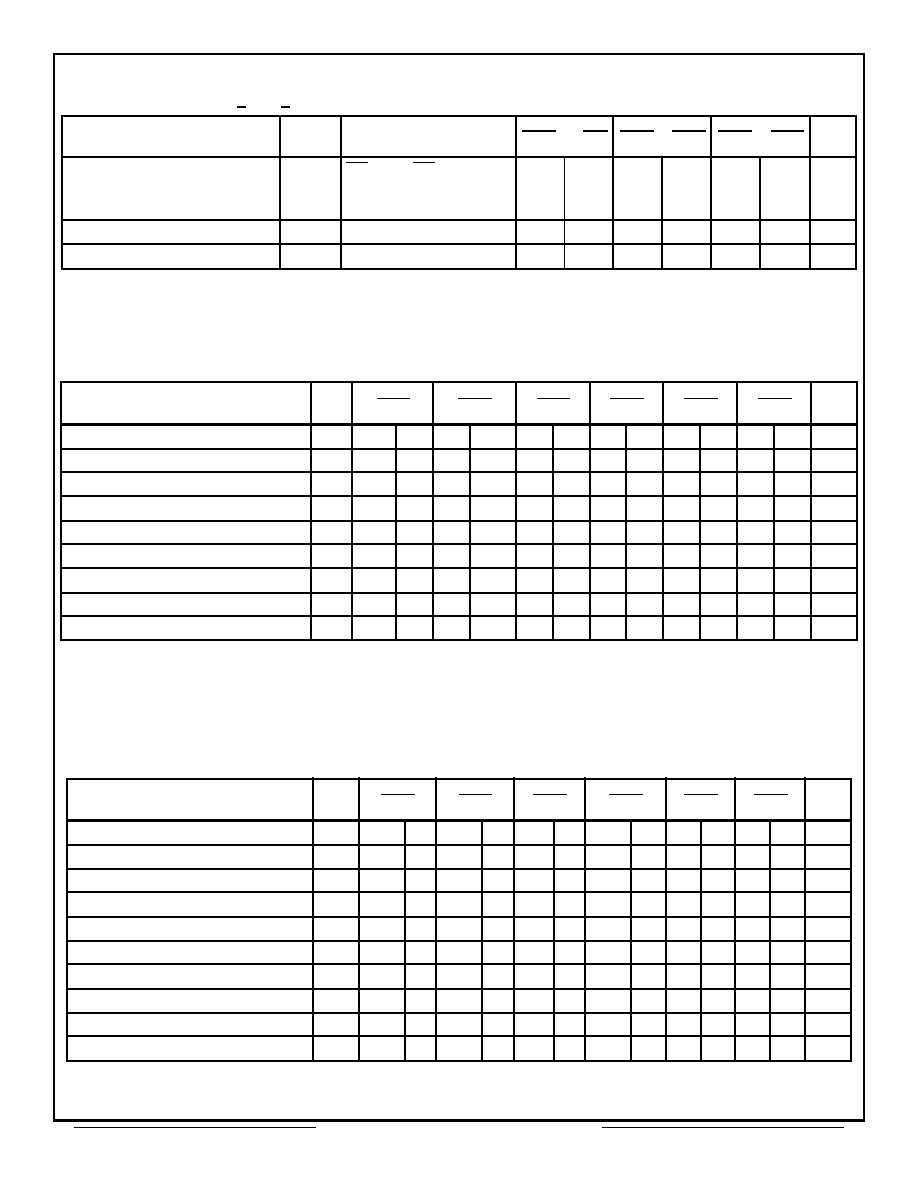

Pin Numbers & Functions

66 Pins -- PGA-Type

Pin # Function Pin # Function Pin # Function Pin # Function Pin # Function Pin # Function Pin # Function

1

I/O

8

11

I/O

2

21

NC

31

I/O

6

41

A

9

51

A

5

61

A

1

2

I/O

9

12

WE

2

22

I/O

3

32

I/O

5

42

I/O

16

52

WE

3

62

A

2

3

I/O

10

13

CE

2

23

I/O

15

33

I/O

4

43

I/O

17

53

CE

3

63

I/O

23

4

A

13

14

GND

24

I/O

14

34

I/O

24

44

I/O

18

54

GND

64

I/O

22

5

A

14

15

I/O

11

25

I/O

13

35

I/O

25

45

V

CC

55

I/O

19

65

I/O

21

6

A

15

16

A

10

26

I/O

12

36

I/O

26

46

CE

4

56

I/O

31

66

I/O

20

7

A

16

17

A

11

27

OE

37

A

6

47

WE

4

57

I/O

30

8

NC

18

A

12

28

NC

38

A

7

48

I/O

27

58

I/O

29

9

I/O

0

19

Vcc

29

WE

1

39

NC

49

A

3

59

I/O

28

10

I/O

1

20

CE

1

30

I/O

7

40

A

8

50

A

4

60

A

0

"P7" -- 1.08" SQ PGA Type Package Standard (with shoulders on Pins 1, 11, 56 & 66)

1.085 SQ MAX

1.000 TYP

.600 TYP

1.000

.100 TYP

.100 TYP

Pin 56

Pin 66

Pin 11

Pin 1

.020

.016

.100

.025

.185

MAX

Side View

.050 DIA

.035

TYP

TYP

TYP

.145

MIN

Bottom View