| ÐлекÑÑоннÑй компоненÑ: ADV7170 | СкаÑаÑÑ:  PDF PDF  ZIP ZIP |

Äîêóìåíòàöèÿ è îïèñàíèÿ www.docs.chipfind.ru

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

a

ADV7170/ADV7171*

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700

World Wide Web Site: http://www.analog.com

Fax: 781/326-8703

© Analog Devices, Inc., 1998

Digital PAL/NTSC Video Encoder with 10-Bit

SSAFTM and Advanced Power Management

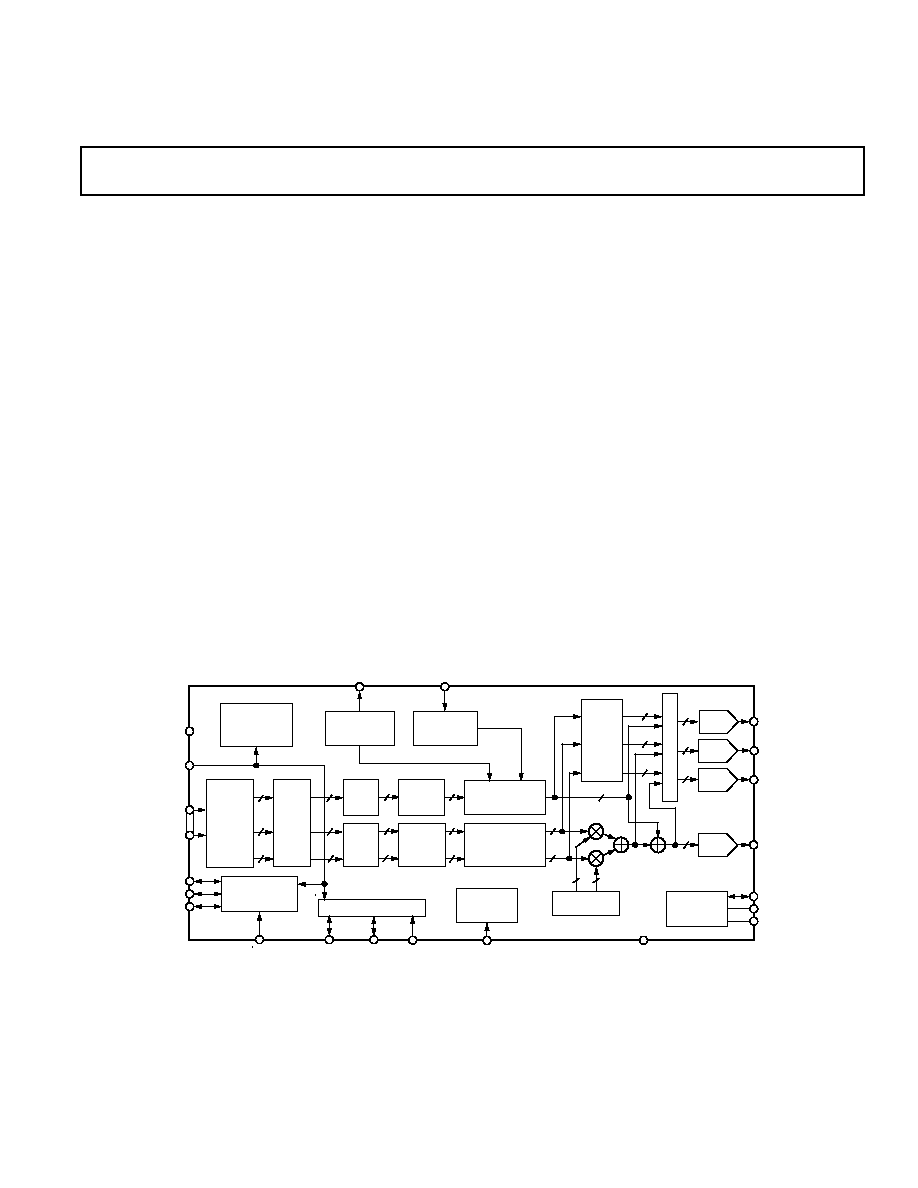

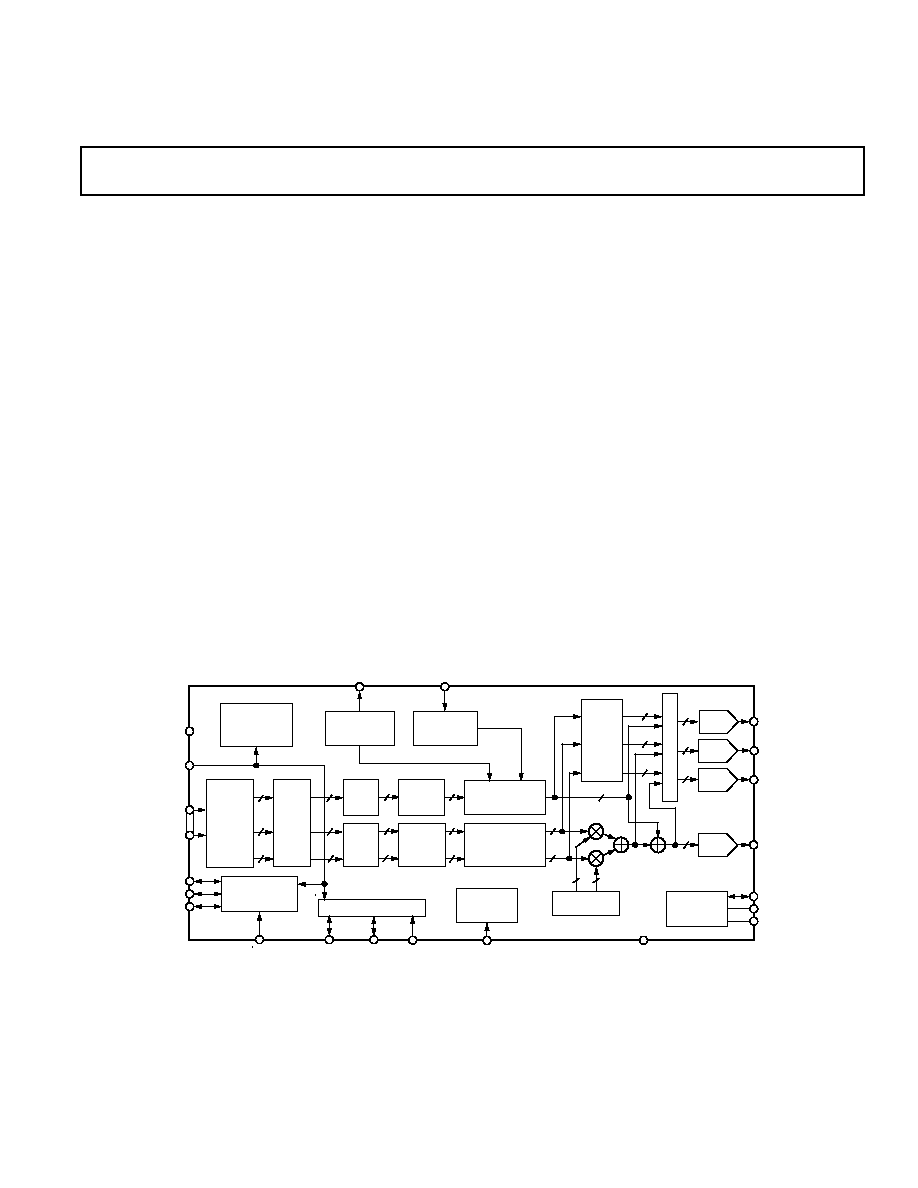

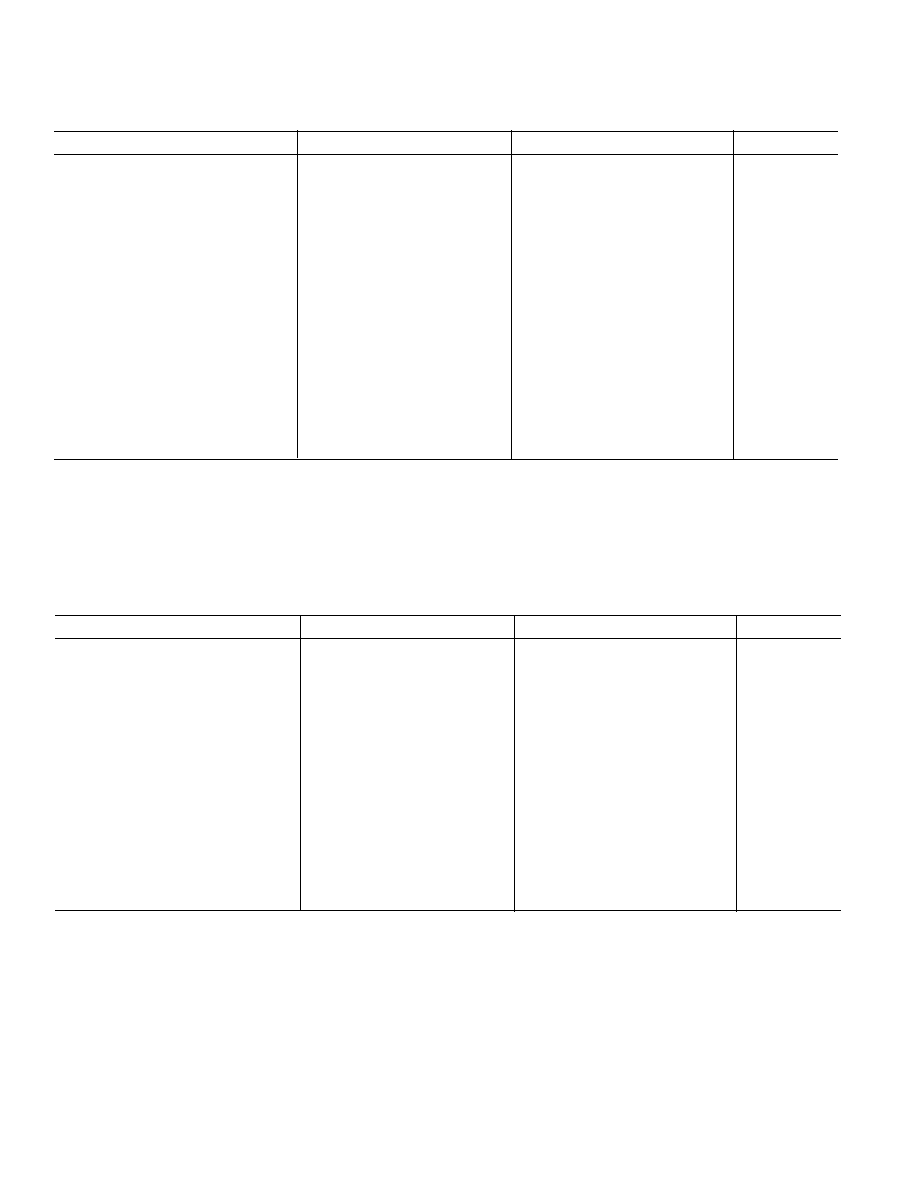

FUNCTIONAL BLOCK DIAGRAM

YUV TO

RBG

MATRIX

VIDEO TIMING

GENERATOR

9

9

8

10

8

8

8

10

8

8

8

10

YCrCb

TO

YUV

MATRIX

SIN/COS

DDS BLOCK

10

10

10

10

10

10

M

U

L

T

I

P

L

E

X

E

R

I

2

C MPU PORT

4:2:2 TO

4:4:4

INTER-

POLATOR

VOLTAGE

REFERENCE

CIRCUIT

SCLOCK

SDATA

ALSB

HSYNC

FIELD/

VSYNC

BLANK

CLOCK

GND

DAC D (PIN 27)

DAC A (PIN 32)

V

REF

R

SET

COMP

8

8

8

ADV7170/ADV7171

10-BIT

DAC

COLOR

DATA

P7P0

P15P8

10-BIT

DAC

10-BIT

DAC

REAL-TIME

CONTROL

CIRCUIT

SCRESET/RTC

INTER-

POLATOR

ADD

SYNC

PROGRAMMABLE

LUMINANCE

FILTER

10-BIT

DAC

DAC C (PIN 26)

DAC B (PIN 31)

ADD

BURST

INTER-

POLATOR

V

AA

Y

U

V

POWER

MANAGEMENT

CONTROL

(SLEEP MODE)

RESET

PROGRAMMABLE

CHROMINANCE

FILTER

CGMS & WSS

INSERTION

BLOCK

TELETEXT

INSERTION

BLOCK

TTXREQ

TTX

10

10

10

U

V

FEATURES

ITU-R BT601/656 YCrCb to PAL/NTSC Video Encoder

High Quality 10-Bit Video DACs

SSAF (Super Sub-Alias Filter)

Advanced Power Management Features

CGMS (Copy Generation Management System)

WSS (Wide Screen Signalling)

Simultaneous Y, U, V, C Output Format

NTSC-M, PAL-M/N, PAL-B/D/G/H/I, PAL-60

Single 27 MHz Clock Required ( 2 Oversampling)

80 dB Video SNR

32-Bit Direct Digital Synthesizer for Color Subcarrier

Multistandard Video Output Support:

Composite (CVBS)

Component S-Video (Y/C)

Component YUV and RGB

EuroSCART Output (RGB + CVBS/LUMA)

Component YUV + CHROMA

Video Input Data Port Supports:

CCIR-656 4:2:2 8-Bit Parallel Input Format

4:2:2 16-Bit Parallel Input Format

SMPTE 170M NTSC-Compatible Composite Video

ITU-R BT.470 PAL-Compatible Composite Video

Programmable Simultaneous Composite

and S-Video or RGB (SCART)/YUV Video Outputs

Programmable Luma Filters (Low-Pass [PAL/NTSC])

Notch, Extended (SSAF, CIF and QCIF)

Programmable Chroma Filters (Low-Pass [0.65 MHz,

1.0 MHz, 1.2 MHz and 2.0 MHz], CIF and QCIF)

Programmable VBI (Vertical Blanking Interval)

Programmable Subcarrier Frequency and Phase

Programmable LUMA Delay

Individual ON/OFF Control of Each DAC

CCIR and Square Pixel Operation

Integrated Subcarrier Locking to External Video Source

Color Signal Control/Burst Signal Control

Interlaced/Noninterlaced Operation

Complete On-Chip Video Timing Generator

Programmable Multimode Master/Slave Operation

Macrovision AntiTaping Rev 7.01 (ADV7170 Only)**

Closed Captioning Support

Teletext Insertion Port (PAL-WST)

On-Board Color Bar Generation

On-Board Voltage Reference

2-Wire Serial MPU Interface (I

2

C

®

Compatible and Fast I

2

C)

Single Supply +5 V or +3.3 V Operation

Small 44-Lead PQFP/TQFP Packages

APPLICATIONS

High Performance DVD Playback Systems, Portable

Video Equipment Including Digital Still Cameras and

Laptop PCs, Video Games, PC Video/Multimedia and

Digital Satellite/Cable Systems (Set-Top Boxes/IRD)

*Protected by U.S. Patent Numbers 5,343,196 and 5,442,355 and other intellectual property rights.

**This device is protected by U.S. Patent Numbers 4,631,603, 4,577,216, 4,819,098 and other intellectual property rights. The Macrovision anticopy process is

licensed for noncommercial home use only, which is its sole intended use in the device. Please contact sales office for latest Macrovision version available.

NOTE: ITU-R and CCIR are used interchangeably in this document (ITU-R has replaced CCIR recommendations).

SSAF is a trademark of Analog Devices, Inc.

I

2

C is a registered trademark of Philips Corporation.

2

REV. 0

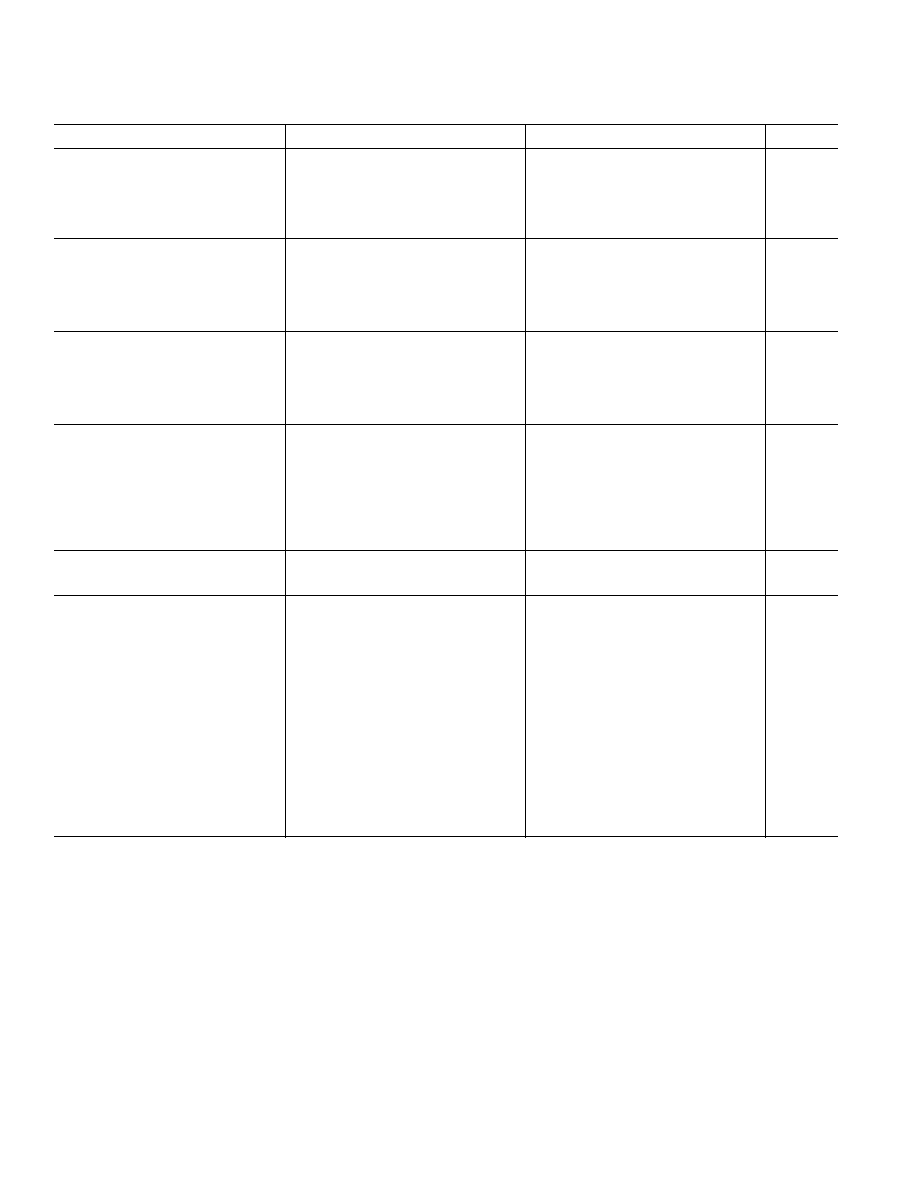

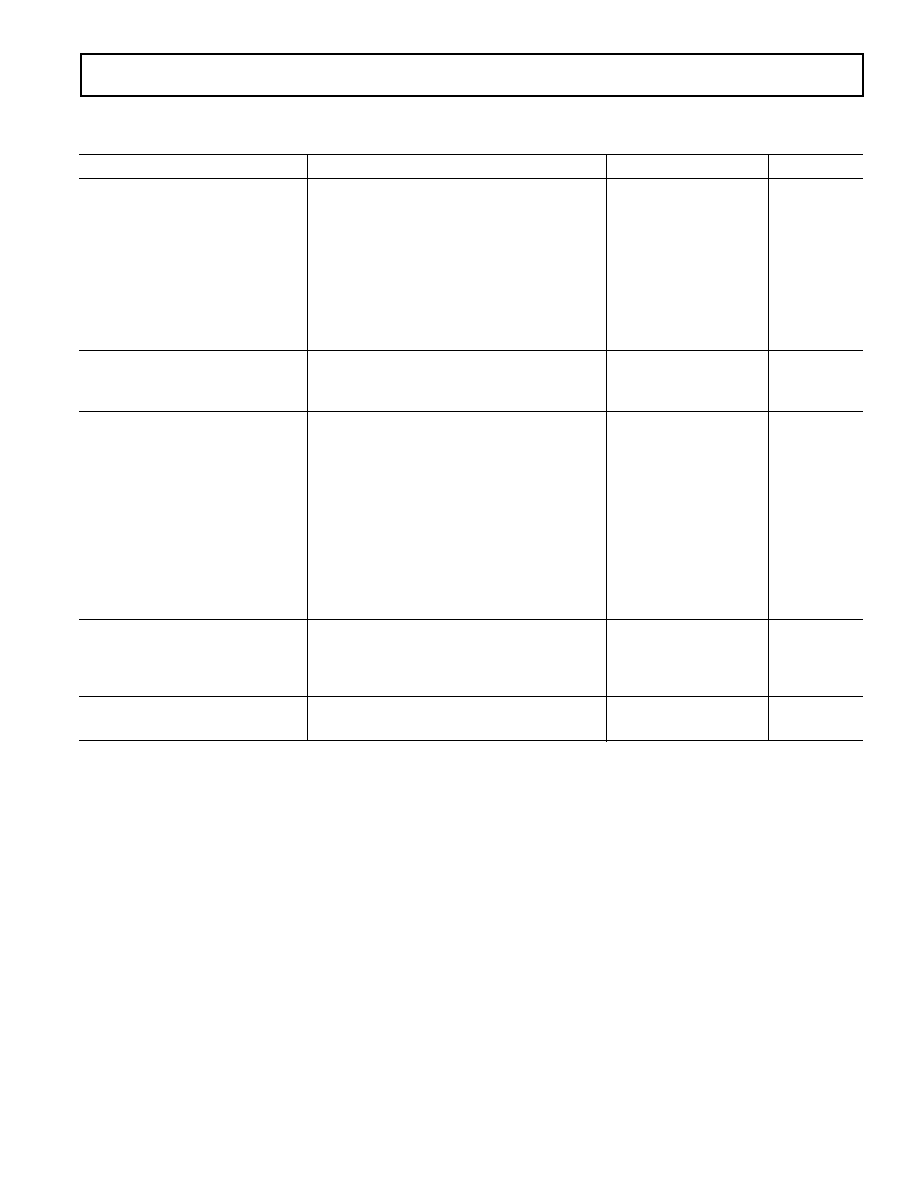

ADV7170/ADV7171SPECIFICATIONS

(V

AA

= +5 V 5%

1

, V

REF

= 1.235 V, R

SET

= 150 . All specifications T

MIN

to T

MAX

2

unless otherwise noted.)

Parameter

Conditions

1

Min

Typ

Max

Units

STATIC PERFORMANCE

Resolution (Each DAC)

10

Bits

Accuracy (Each DAC)

Integral Nonlinearity

R

SET

= 300

±

0.6

LSB

Differential Nonlinearity

Guaranteed Monotonic

±

1

LSB

DIGITAL INPUTS

Input High Voltage, V

INH

2

V

Input Low Voltage, V

INL

0.8

V

Input Current, I

IN

V

IN

= 0.4 V or 2.4 V

±

1

µ

A

Input Capacitance, C

IN

10

pF

DIGITAL OUTPUTS

Output High Voltage, V

OH

I

SOURCE

= 400

µ

A

2.4

V

Output Low Voltage, V

OL

I

SINK

= 3.2 mA

0.4

V

Three-State Leakage Current

10

µ

A

Three-State Output Capacitance

10

pF

ANALOG OUTPUTS

Output Current

3

R

SET

= 150

, R

L

= 37.5

33

34.7

37

mA

Output Current

4

R

SET

= 1041

, R

L

= 262.5

5

mA

DAC-to-DAC Matching

1.5

%

Output Compliance, V

OC

0

+1.4

V

Output Impedance, R

OUT

30

k

Output Capacitance, C

OUT

I

OUT

= 0 mA

30

pF

VOLTAGE REFERENCE

Reference Range, V

REF

I

VREFOUT

= 20

µ

A

1.142

1.235

1.327

V

POWER REQUIREMENTS

5

V

AA

4.75

5.0

5.25

V

Normal Power Mode

I

DAC

(max)

6

R

SET

= 150

, R

L

= 37.5

150

155

mA

I

DAC

(min)

6

R

SET

= 1041

, R

L

= 262.5

20

mA

I

CCT

7

75

90

mA

Low Power Mode

I

DAC

(max)

6

80

mA

I

DAC

(min)

6

20

mA

I

CCT

7

75

90

mA

Sleep Mode

I

DAC

8

0.1

µ

A

I

CCT

9

0.001

µ

A

Power Supply Rejection Ratio

COMP = 0.1

µ

F

0.01

0.5

%/%

NOTES

1

The max/min specifications are guaranteed over this range. The max/min values are typical over 4.75 V to 5.25 V.

2

Temperature range T

MIN

to T

MAX

: 0

°

C to +70

°

C.

3

Full

drive into 37.5

doubly terminated load.

4

Minimum drive current (used with buffered/scaled output load).

5

Power measurements are taken with Clock Frequency = 27 MHz. Max T

J

= 110

°

C.

6

I

DAC

is the total current (min corresponds to 5 mA output per DAC, max corresponds to 37 mA output per DAC) to drive all four DACs. Turning off individual

DACs reduces I

DAC

correspondingly.

7

I

CCT

(Circuit Current) is the continuous current required to drive the device.

8

Total DAC current in Sleep Mode.

9

Total continuous current during Sleep Mode.

Specifications subject to change without notice.

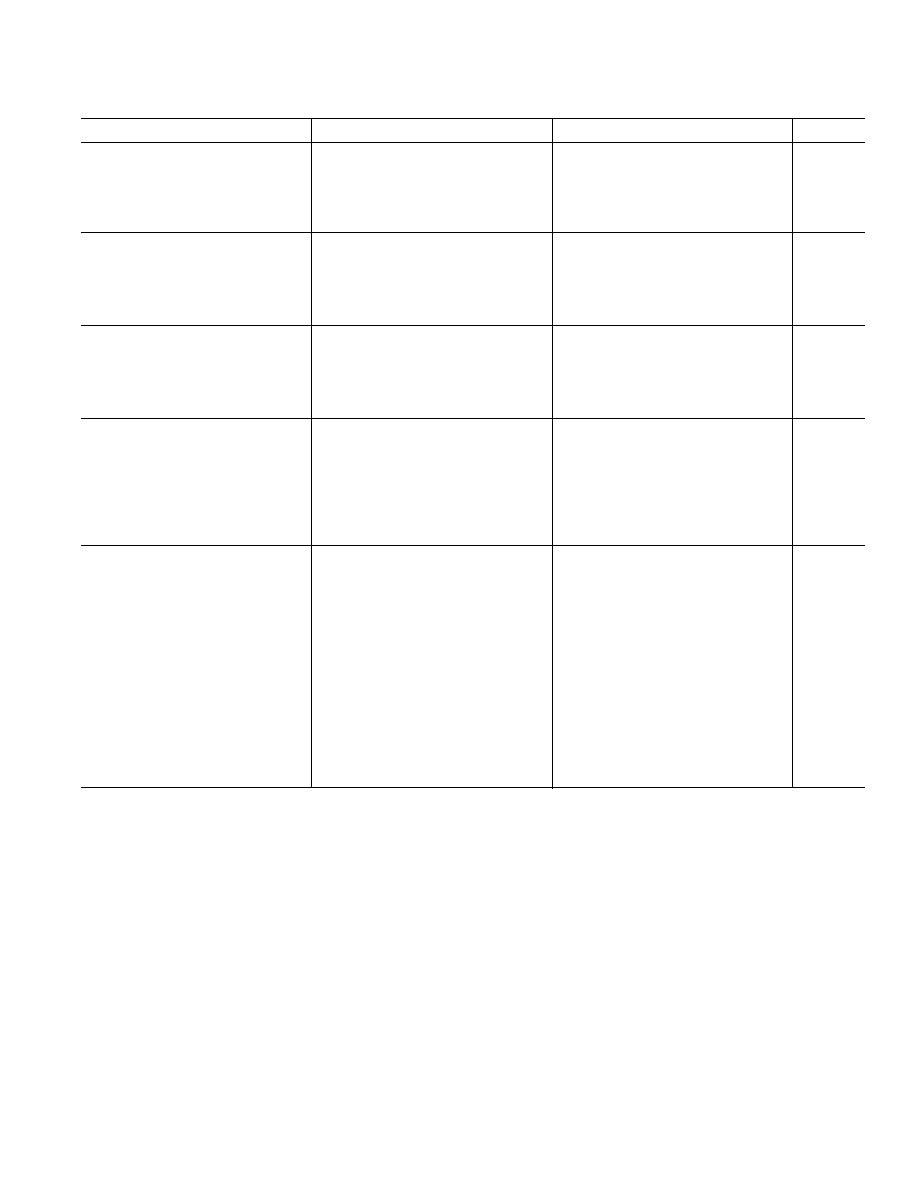

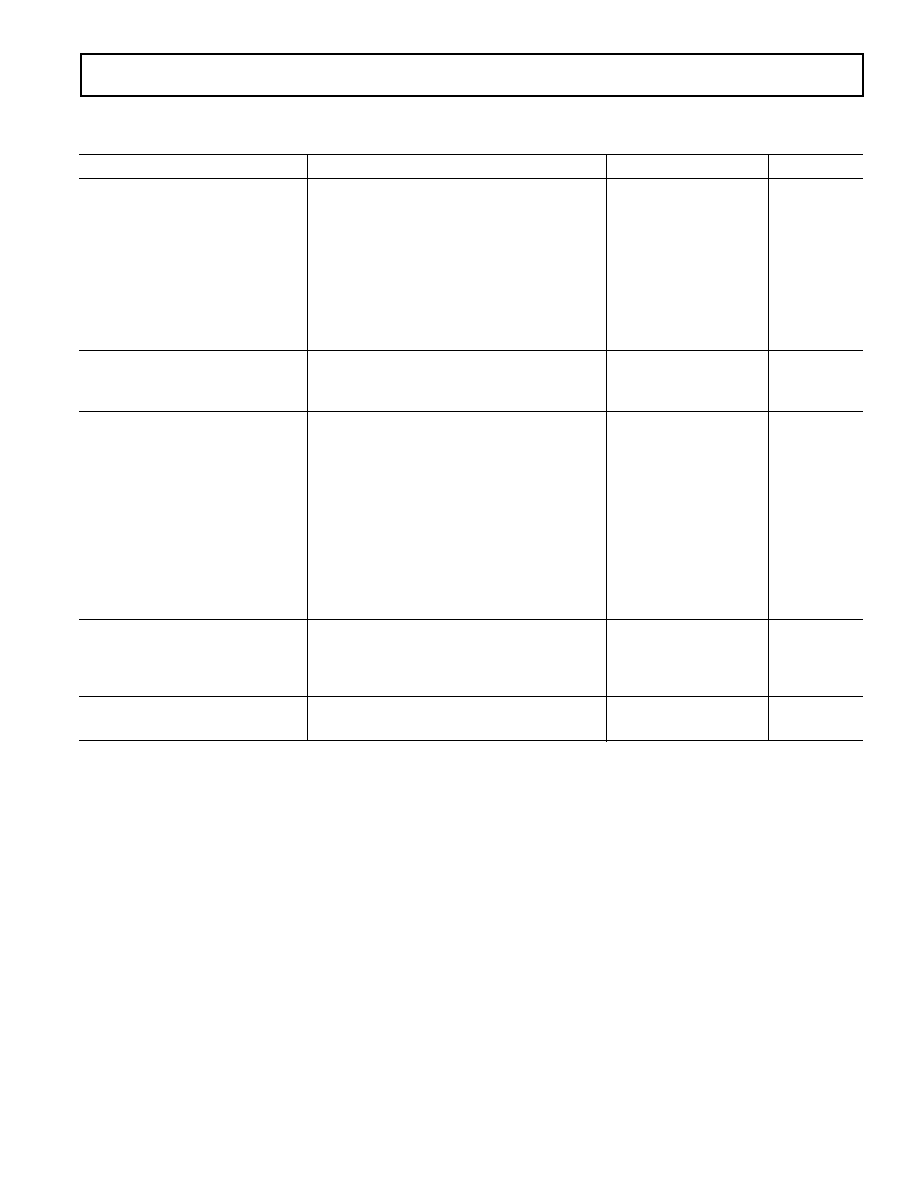

5 V SPECIFICATIONS

3

REV. 0

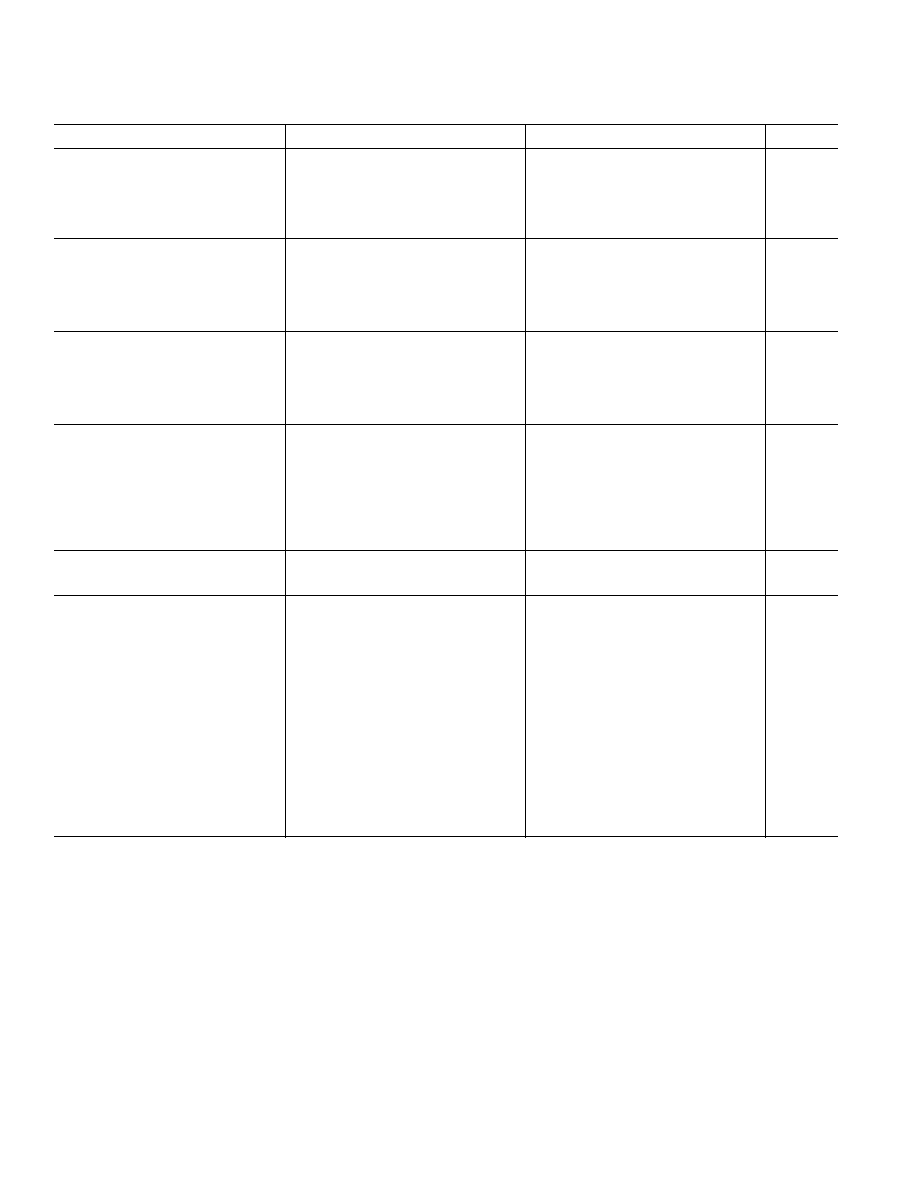

ADV7170/ADV7171

Parameter

Conditions

1

Min

Typ

Max

Units

STATIC PERFORMANCE

3

Resolution (Each DAC)

10

Bits

Accuracy (Each DAC)

Integral Nonlinearity

R

SET

= 300

±

0.6

LSB

Differential Nonlinearity

Guaranteed Monotonic

±

1

LSB

DIGITAL INPUTS

3

Input High Voltage, V

INH

2

V

Input Low Voltage, V

INL

0.8

V

Input Current, I

IN

3, 4

V

IN

= 0.4 V or 2.4 V

±

1

µ

A

Input Capacitance, C

IN

10

pF

DIGITAL OUTPUTS

3

Output High Voltage, V

OH

I

SOURCE

= 400

µ

A

2.4

V

Output Low Voltage, V

OL

I

SINK

= 3.2 mA

0.4

V

Three-State Leakage Current

10

µ

A

Three-State Output Capacitance

10

pF

ANALOG OUTPUTS

3

Output Current

4, 5

R

SET

= 150

, R

L

= 37.5

33

34.7

37

mA

Output Current

6

R

SET

= 1041

, R

L

= 262.5

5

mA

DAC-to-DAC Matching

2.0

%

Output Compliance, V

OC

0

+1.4

V

Output Impedance, R

OUT

30

k

Output Capacitance, C

OUT

I

OUT

= 0 mA

30

pF

POWER REQUIREMENTS

3, 7

V

AA

3.0

3.3

3.6

V

Normal Power Mode

I

DAC

(max)

8

R

SET

= 150

, R

L

= 37.5

150

155

mA

I

DAC

(min)

8

R

SET

= 1041

, R

L

= 262.5

20

mA

I

CCT

9

35

mA

Low Power Mode

I

DAC

(max)

8

80

mA

I

DAC

(min)

8

20

mA

I

CCT

9

35

mA

Sleep Mode

I

DAC

10

0.1

µ

A

I

CCT

11

0.001

µ

A

Power Supply Rejection Ratio

COMP = 0.1

µ

F

0.01

0.5

%/%

NOTES

1

1

The max/min specifications are guaranteed over this range. The max/min values are typical over 3.0 V to 3.6 V.

1

2

Temperature range T

MIN

to T

MAX

: 0

°

C to +70

°

C.

1

3

Guaranteed by characterization.

1

4

Full

drive into 37.5

load.

1

5

DACs can output 35 mA typically at 3.3 V (R

SET

= 150

and R

L

= 37.5

), optimum performance obtained at 18 mA DAC current (R

SET

= 300

and R

L

= 75

).

1

6

Minimum drive current (used with buffered/scaled output load).

1

7

Power measurements are taken with Clock Frequency = 27 MHz. Max T

J

= 110

°

C.

1

8

I

DAC

is the total current (min corresponds to 5 mA output per DAC, max corresponds to 38 mA output per DAC) to drive all four DACs. Turning off individual

DACs reduces I

DAC

correspondingly.

1

9

I

CCT

(Circuit Current) is the continuous current required to drive the device.

10

Total DAC current in Sleep Mode.

11

Total continuous current during Sleep Mode.

Specifications subject to change without notice.

3.3 V SPECIFICATIONS

(V

AA

= +3.0 V 3.6 V

1

, V

REF

= 1.235 V, R

SET

= 150

. All specifications T

MIN

to T

MAX

2

unless otherwise noted.)

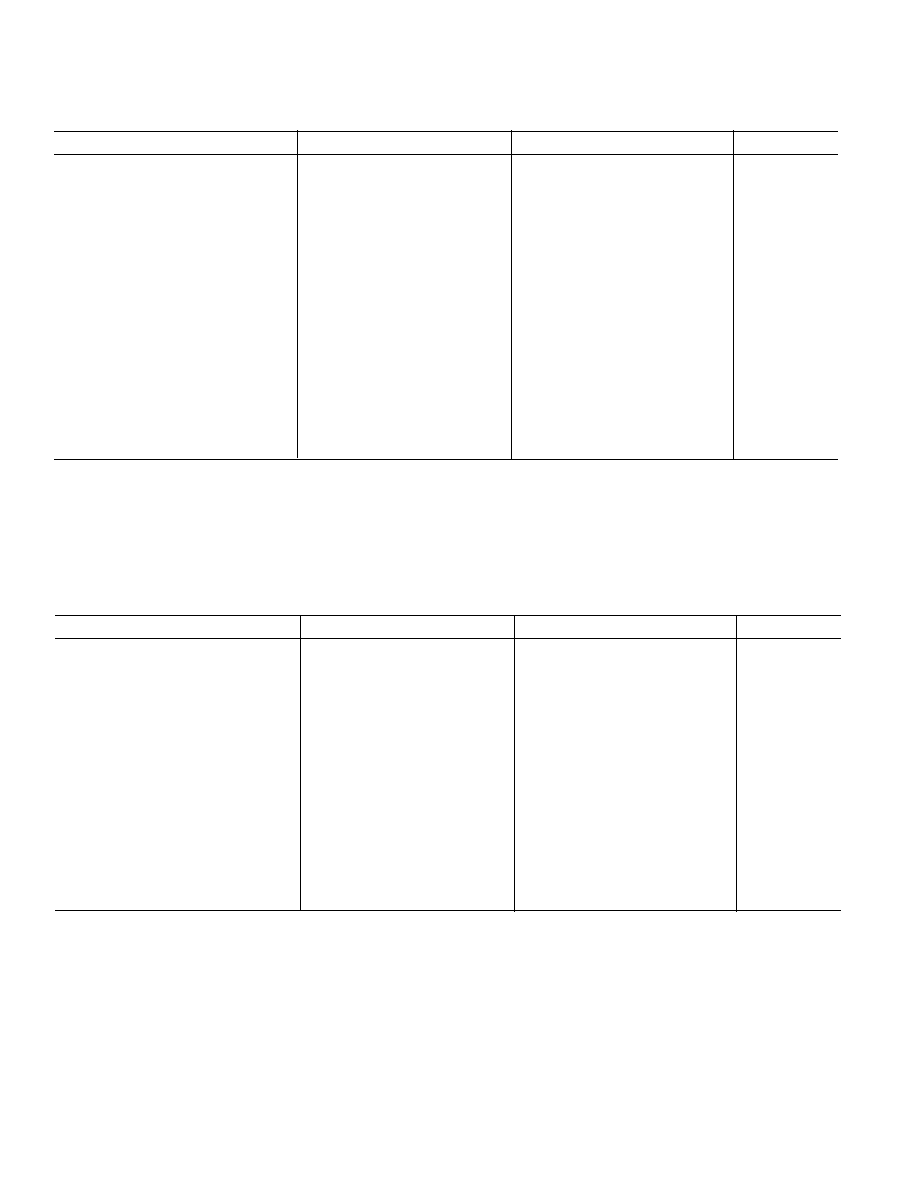

4

REV. 0

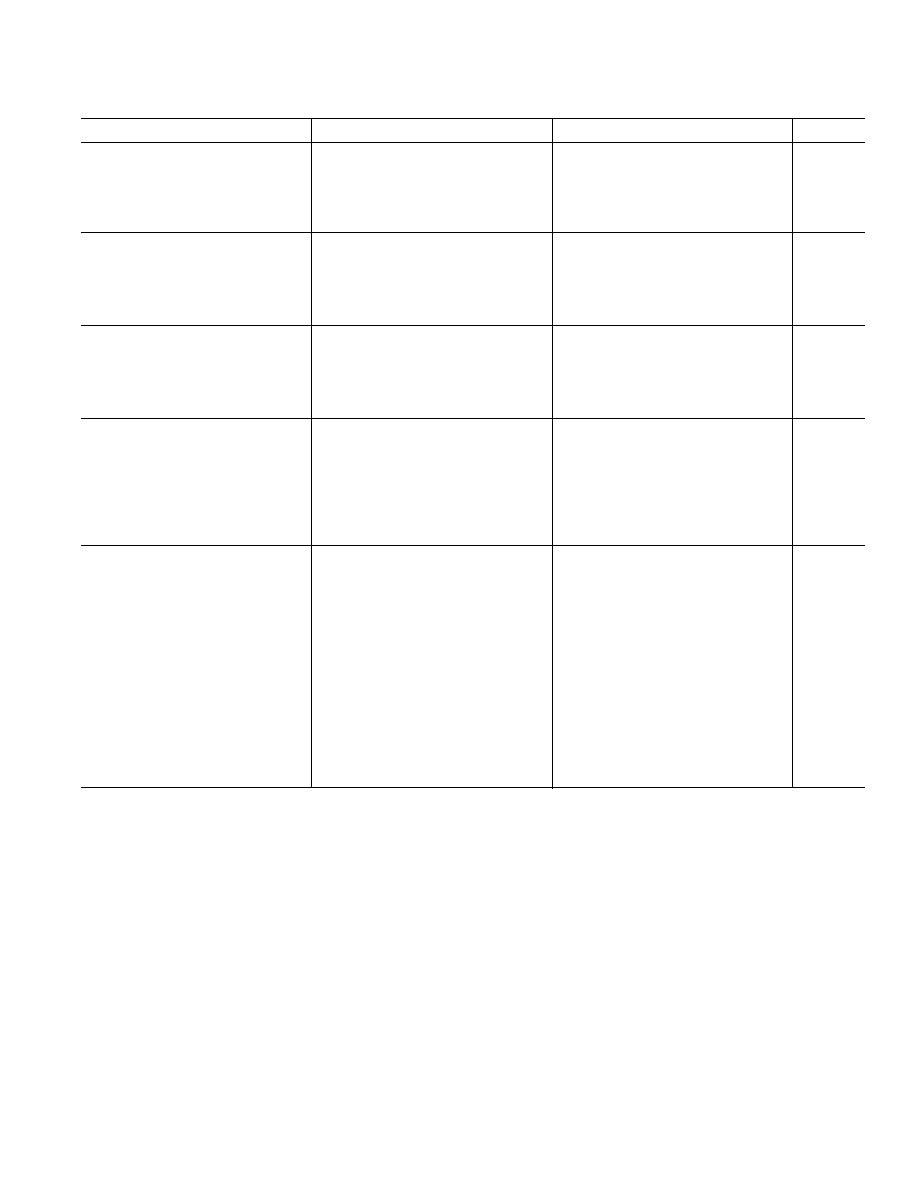

ADV7170/ADV7171SPECIFICATIONS

Parameter

Conditions

1

Min

Typ

Max

Units

Differential Gain

3, 4

Normal Power Mode

0.3

0.7

%

Differential Phase

3, 4

Normal Power Mode

0.4

0.7

Degrees

Differential Gain

3, 4

Lower Power Mode

1.0

2.0

%

Differential Phase

3, 4

Lower Power Mode

1.0

2.0

Degrees

SNR

3, 4

(Pedestal)

RMS

80

dB rms

SNR

3, 4

(Pedestal)

Peak Periodic

70

dB p-p

SNR

3, 4

(Ramp)

RMS

60

dB rms

SNR

3, 4

(Ramp)

Peak Periodic

58

dB p-p

Hue Accuracy

3, 4

0.7

1.2

Degrees

Color Saturation Accuracy

3, 4

0.9

1.4

%

Chroma Nonlinear Gain

3, 4

Referenced to 40 IRE

0.6

±

%

Chroma Nonlinear Phase

3, 4

0.3

0.5

±

Degrees

Chroma/Luma Intermod

3, 4

0.2

0.4

±

%

Chroma/Luma Gain Inequality

3, 4

1.0

1.4

±

%

Chroma/Luma Delay Inequality

3, 4

0.5

2.0

ns

Luminance Nonlinearity

3, 4

0.8

1.4

±

%

Chroma AM Noise

3, 4

82

85

dB

Chroma PM Noise

3, 4

79

81

dB

NOTES

1

The max/min specifications are guaranteed over this range. The max/min values are typical over 4.75 V to 5.25 V.

2

Temperature range T

MIN

to T

MAX

: 0

°

C to +70

°

C.

3

Guaranteed by characterization.

4

The low pass filter only and guaranteed by design.

Specifications subject to change without notice.

5 V DYNAMIC SPECIFICATIONS

(V

AA

= +5 V 5%

1

, V

REF

= 1.235 V, R

SET

= 150

. All specifications T

MIN

to T

MAX

2

unless

otherwise noted.)

Parameter

Conditions

1

Min

Typ

Max

Units

Differential Gain

3

Normal Power Mode

1.0

%

Differential Phase

3

Normal Power Mode

0.5

Degrees

Differential Gain

3

Lower Power Mode

0.6

%

Differential Phase

3

Lower Power Mode

0.5

Degrees

SNR

3

(Pedestal)

RMS

78

dB rms

SNR

3

(Pedestal)

Peak Periodic

70

dB p-p

SNR

3

(Ramp)

RMS

60

dB rms

SNR

3

(Ramp)

Peak Periodic

58

dB p-p

Hue Accuracy

3

1.0

Degrees

Color Saturation Accuracy

3

1.0

%

Luminance Nonlinearity

3, 4

1.4

±

%

Chroma AM Noise

3, 4

80

dB

Chroma PM Noise

3, 4

79

dB

Chroma Nonlinear Gain

3, 4

Referenced to 40 IRE

0.6

±

%

Chroma Nonlinear Phase

3, 4

0.3

0.5

±

Degrees

Chroma/Luma Intermod

3, 4

0.2

0.4

±

%

NOTES

1

The max/min specifications are guaranteed over this range. The max/min values are typical over 4.75 V to 5.25 V.

2

Temperature range T

MIN

to T

MAX

: 0

°

C to +70

°

C.

3

Guaranteed by characterization.

4

These specifications are for the low-pass filter only and guaranteed by design. For other internal filters, see Figure 4.

Specifications subject to change without notice.

3.3 V DYNAMIC SPECIFICATIONS

(V

AA

= +3.0 V 3.6 V

1

, V

REF

= 1.235 V, R

SET

= 150 . All specifications T

MIN

to T

MAX

2

unless

otherwise noted.)

ADV7170/ADV7171

5

REV. 0

5 V TIMING SPECIFICATIONS

(V

AA

= 4.75 V 5.25 V

1

, V

REF

= 1.235 V, R

SET

= 150

. All specifications T

MIN

to T

MAX

2

unless

otherwise noted.)

Parameter

Conditions

Min

Typ

Max

Units

MPU PORT

3, 4

SCLOCK Frequency

0

400

kHz

SCLOCK High Pulsewidth, t

1

0.6

µ

s

SCLOCK Low Pulsewidth, t

2

1.3

µ

s

Hold Time (Start Condition), t

3

After This Period the First Clock Is Generated

0.6

µ

s

Setup Time (Start Condition), t

4

Relevant for Repeated Start Condition

0.6

µ

s

Data Setup Time, t

5

100

ns

SDATA, SCLOCK Rise Time, t

6

300

ns

SDATA, SCLOCK Fall Time, t

7

300

ns

Setup Time (Stop Condition), t

8

0.6

µ

s

ANALOG OUTPUTS

3, 5

Analog Output Delay

7

ns

DAC Analog Output Skew

0

ns

CLOCK CONTROL AND

PIXEL PORT

5, 6

f

CLOCK

27

MHz

Clock High Time, t

9

8

ns

Clock Low Time, t

10

8

ns

Data Setup Time, t

11

3.5

ns

Data Hold Time, t

12

4

ns

Control Setup Time, t

11

4

ns

Control Hold Time, t

12

3

ns

Digital Output Access Time, t

13

11

16

ns

Digital Output Hold Time, t

14

4

8

ns

Pipeline Delay, t

15

4

48

Clock Cycles

TELETEXT

3, 4, 7

Digital Output Access Time, t

16

20

ns

Data Setup Time, t

17

2

ns

Data Hold Time, t

18

6

ns

RESET CONTROL

3, 4

RESET Low Time

6

ns

NOTES

1

The max/min specifications are guaranteed over this range. The max/min values are typical over 4.75 V to 5.25 V range.

2

Temperature range T

MIN

to T

MAX

: 0

o

C to +70

o

C.

3

TTL input values are 0 to 3 volts, with input rise/fall times

3 ns, measured between the 10% and 90% points. Timing reference points at 50% for inputs and

outputs. Analog output load

10 pF.

4

Guaranteed by characterization.

5

Output delay measured from the 50% point of the rising edge of CLOCK to the 50% point of full-scale transition.

6

Pixel Port consists of the following:

Pixel Inputs:

P15P0

Pixel Controls:

HSYNC, FIELD/VSYNC, BLANK

Clock Input:

CLOCK

7

Teletext Port consists of the following:

Teletext Output:

TTXREQ

Teletext Input:

TTX

Specifications subject to change without notice.